Novel Dynamic Resistance Equalizer for Parallel-Connected Battery Configurations

Abstract

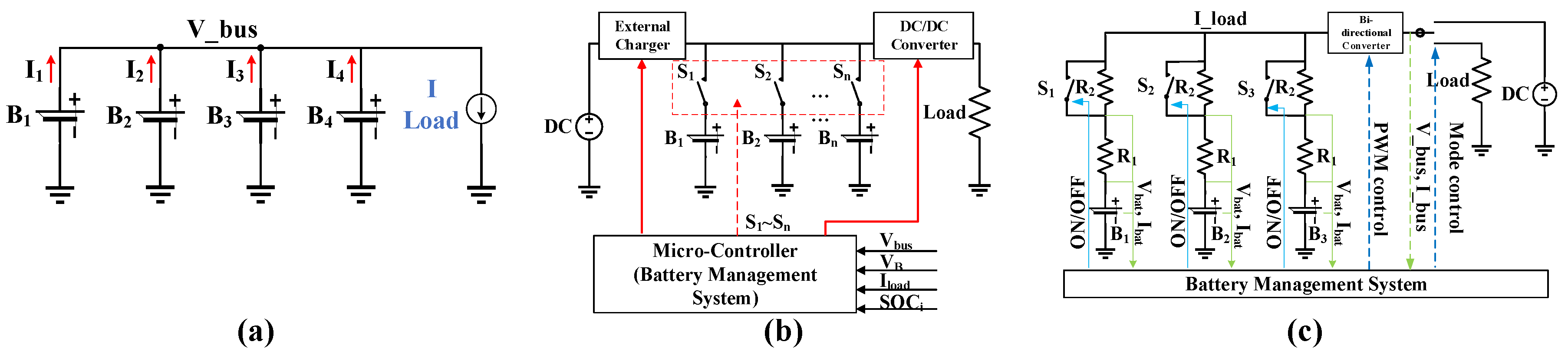

1. Introduction

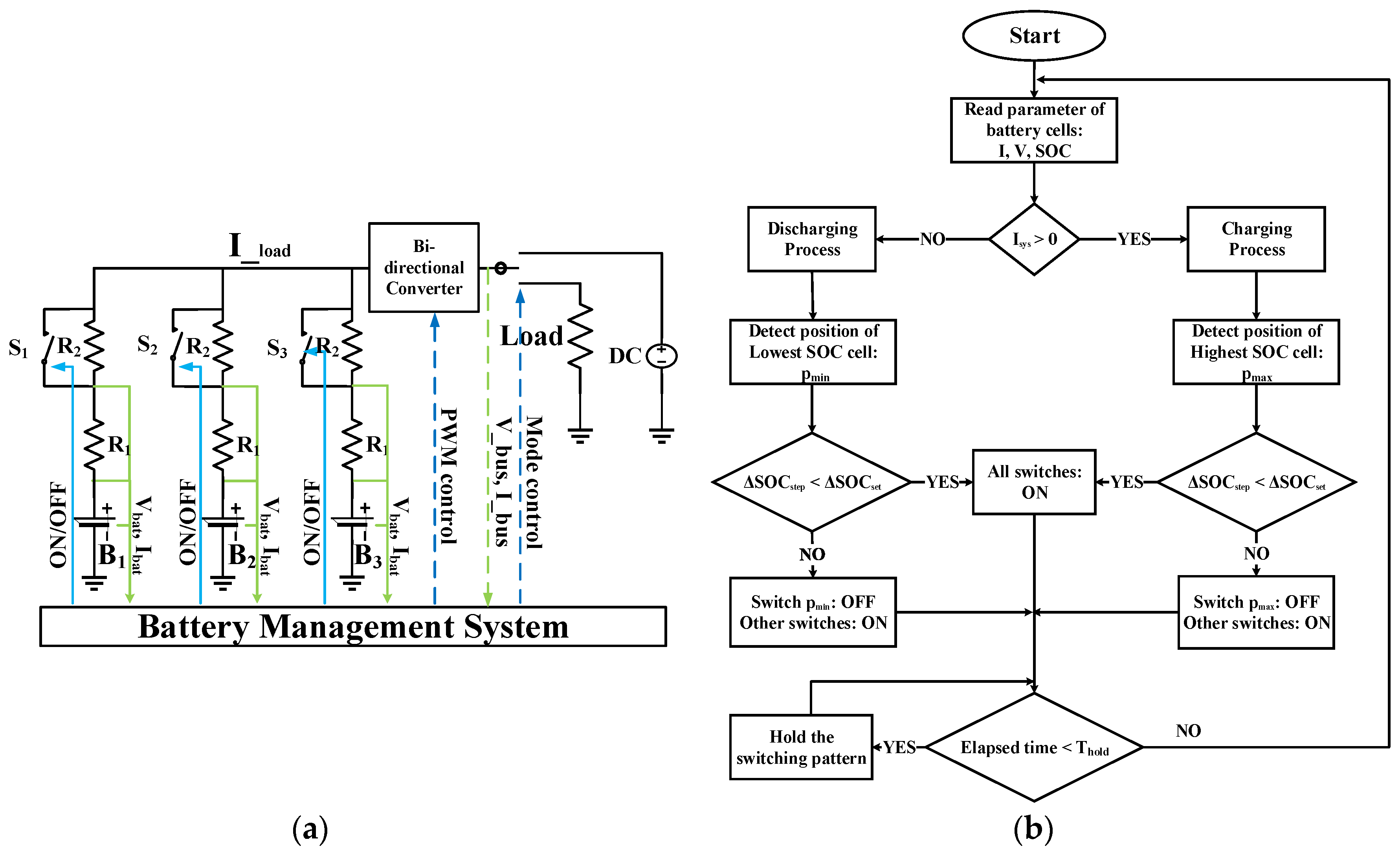

2. Proposed Equalizer

3. Equalization Process Analysis and Design Optimization

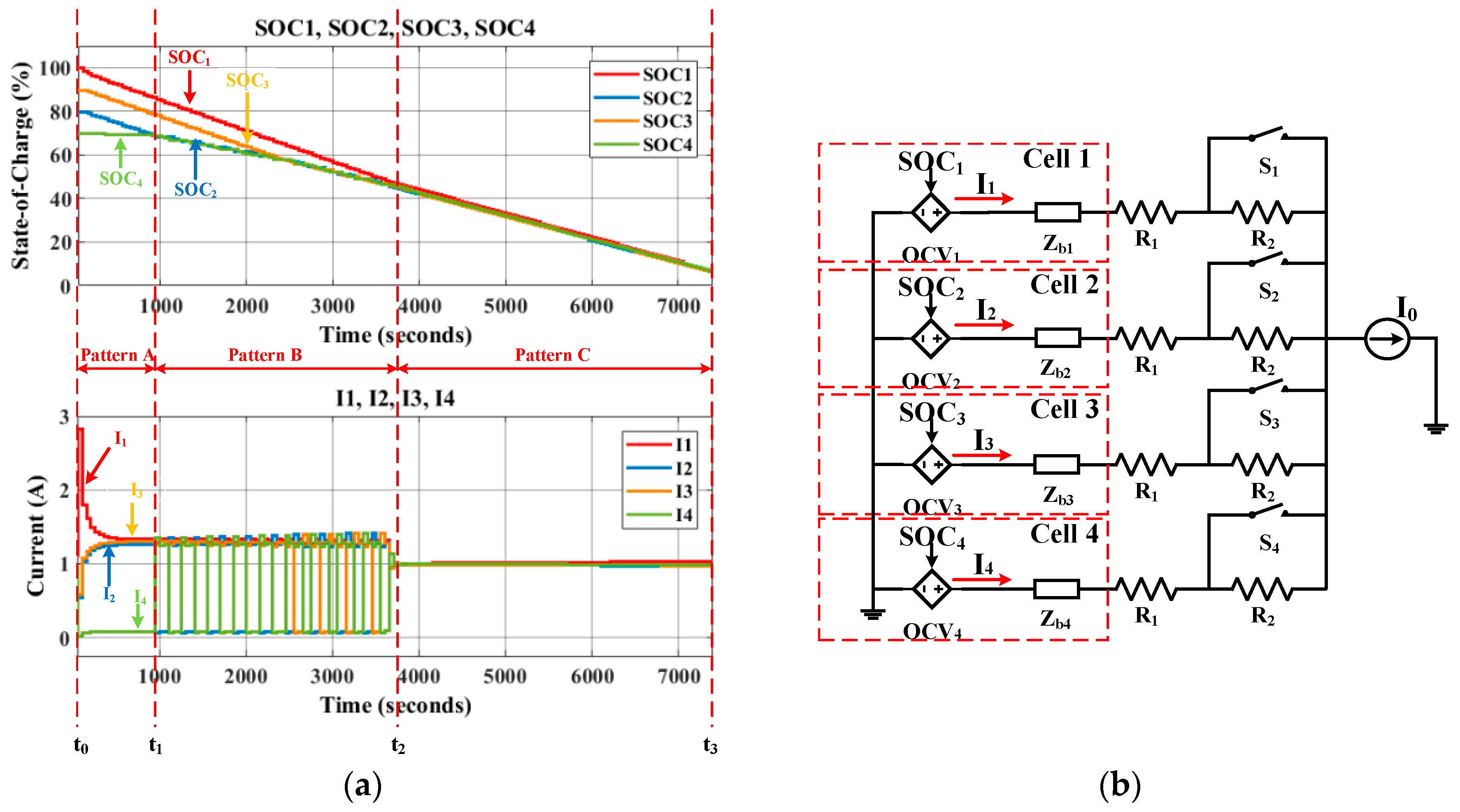

3.1. Equalization Process Analysis

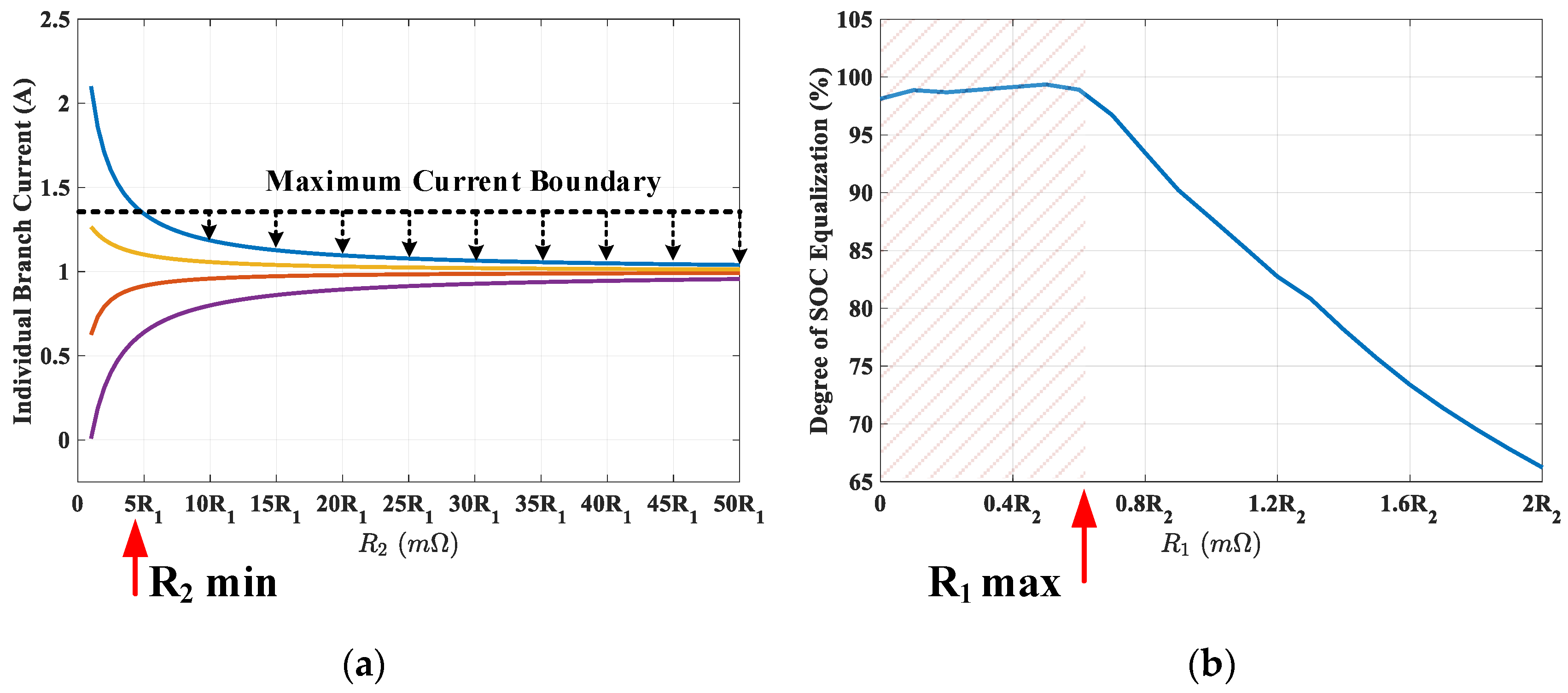

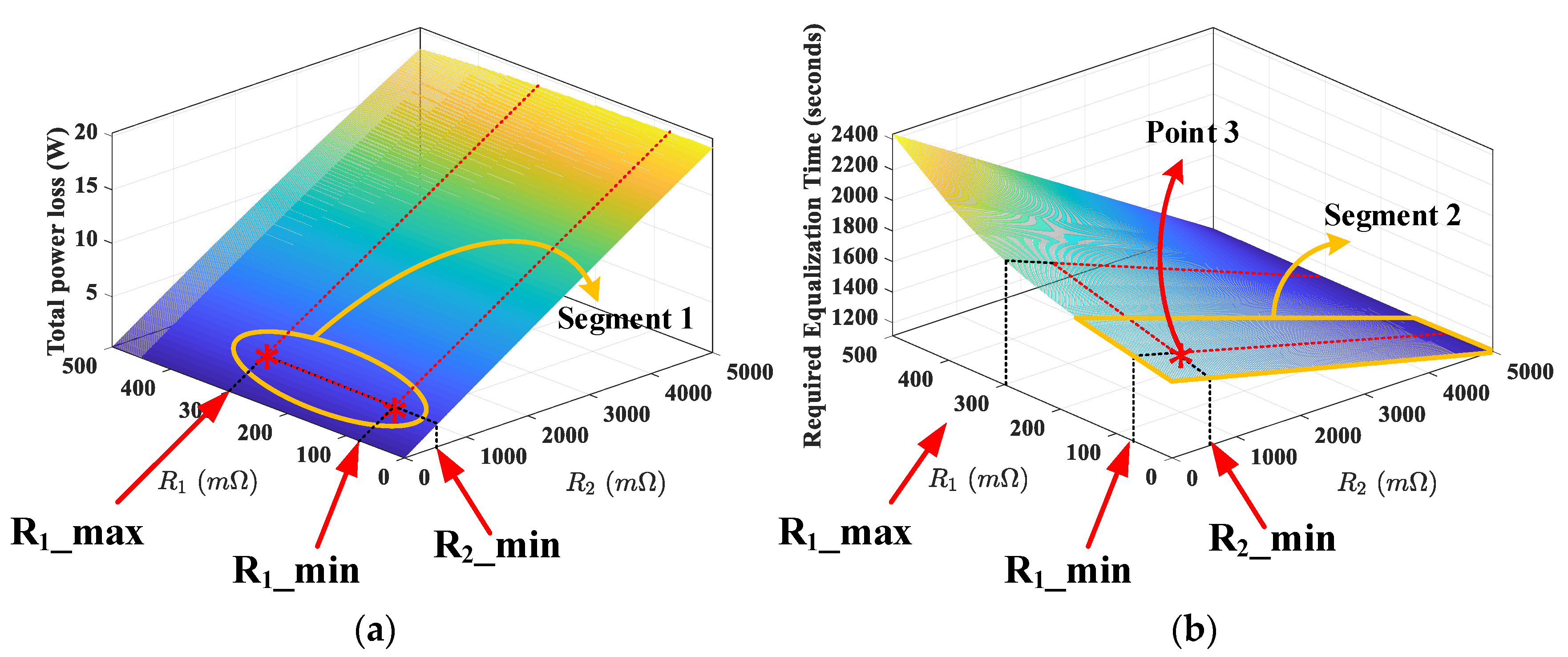

3.2. Design Optimization

- Step 0: Initial assumption

- Step 1: Determine R1min

- Step 2: Determine R2min from the initial current difference.

- Step 3: Determine R1max from the DoSE requirement.

- Step 4: Choose R1 and R2 by considering the total power loss and the equalization time.

4. Verification

4.1. Experiment Setup

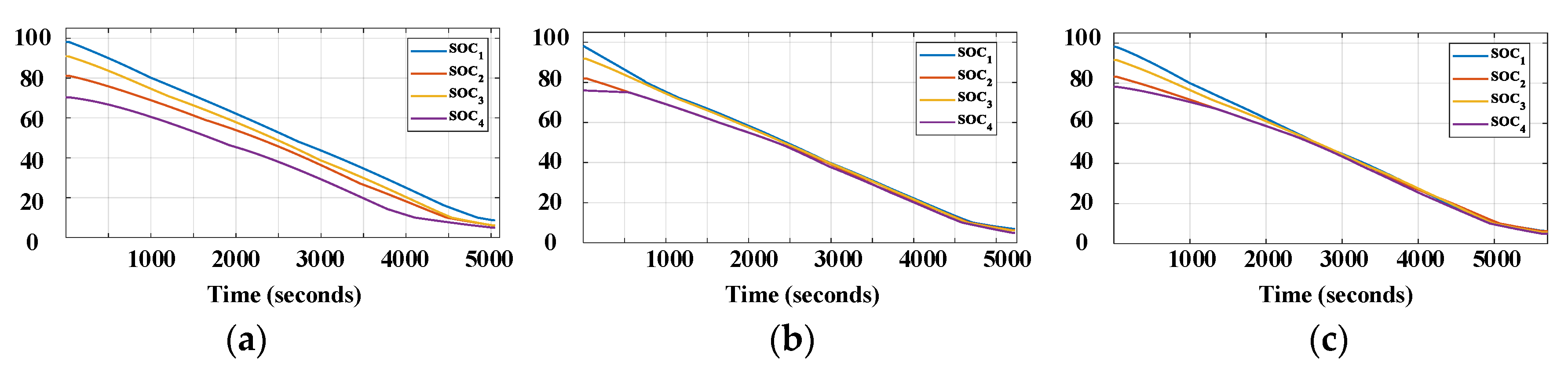

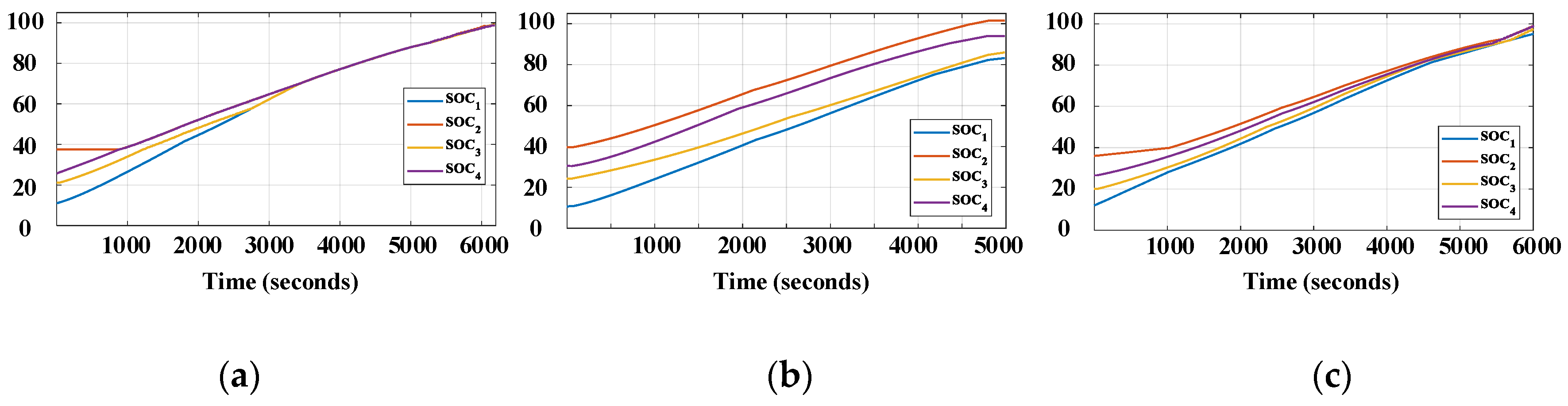

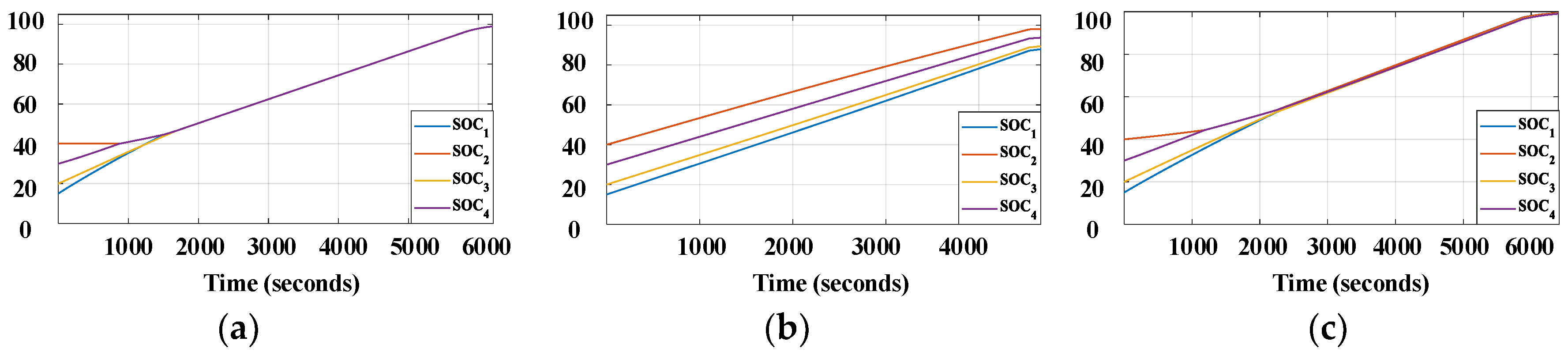

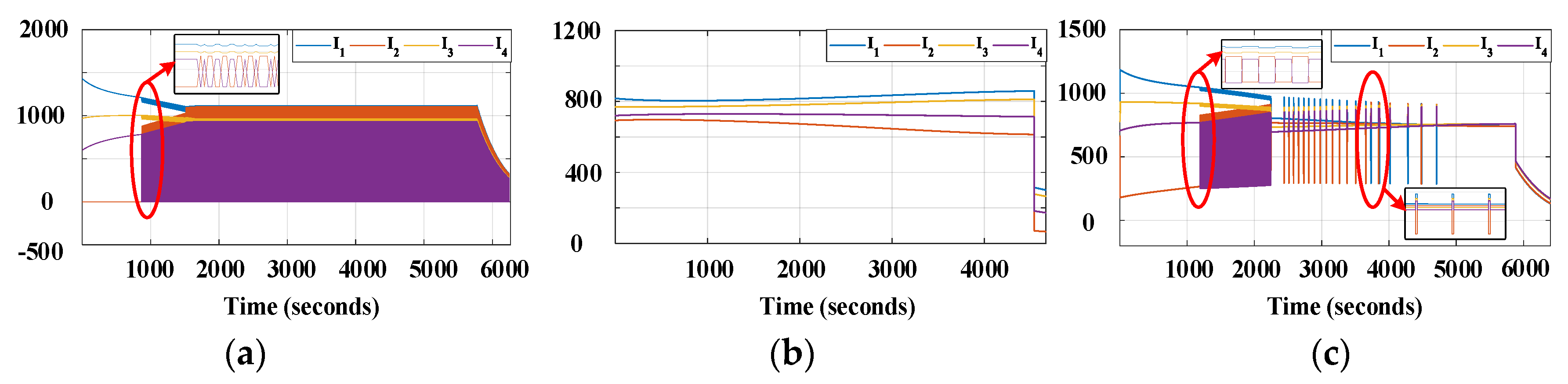

4.2. Performance Optimization by Different Design Scenario

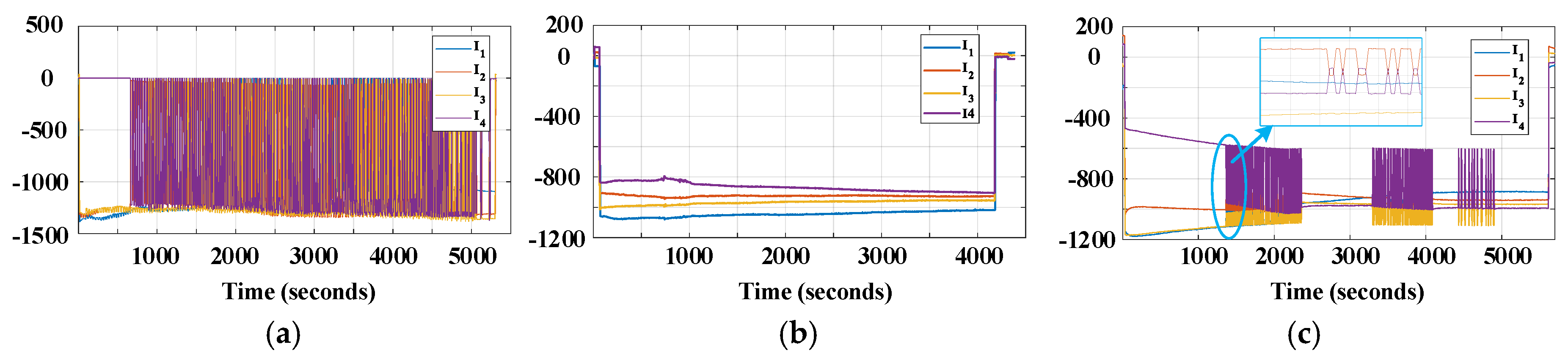

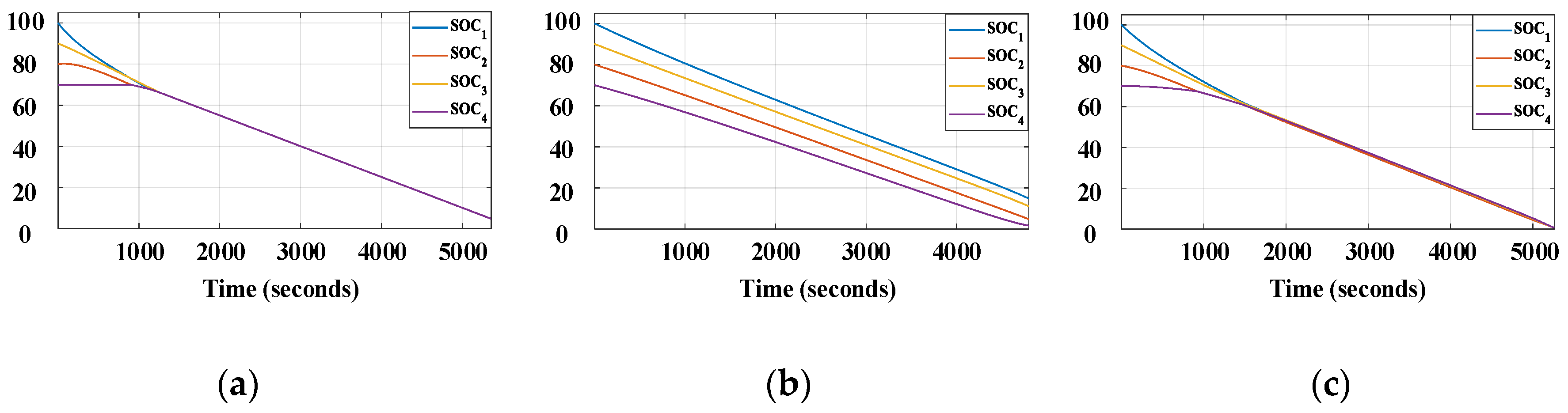

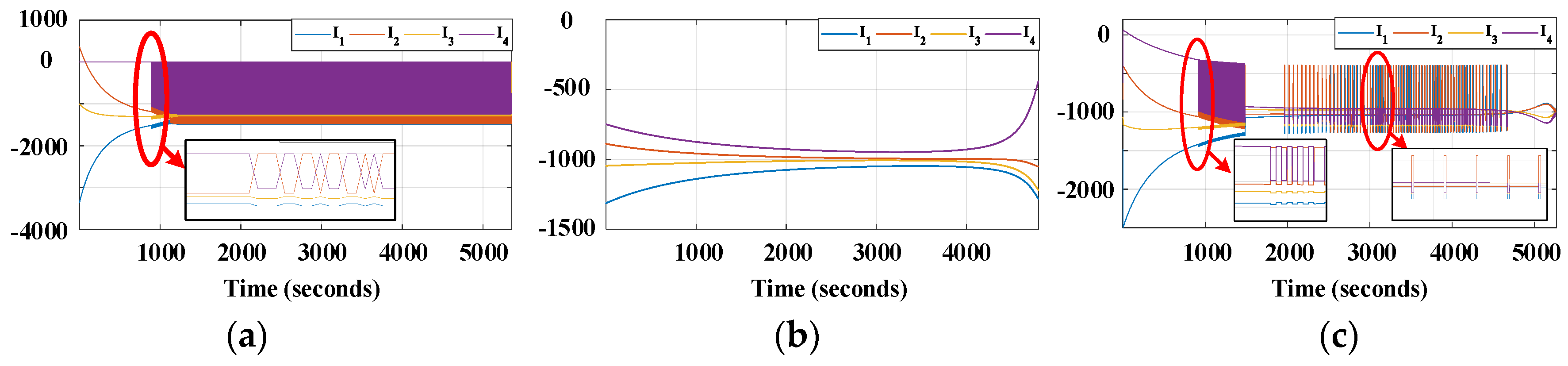

4.3. Equalization Performance of Different Methods in 2S4P Configuration

4.4. Efficiency Assessment of Different Methods in Various Configuration

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- European Commission. A Roadmap for Moving to a Competitive Low Carbon Economy in 2050; European Commission: Brussels, Belgium, 2011; Available online: https://eur-lex.europa.eu/legal-content/EN/ALL/?uri=CELEX%3A52011DC0112 (accessed on 28 June 2020).

- International Energy Agency (IEA), “Global EV Outlook”. 2019. Available online: https://webstore.iea.org/global-ev-outlook-2019 (accessed on 17 June 2019).

- Hunt, G. USABC Electric Vehicle Battery Test Procedures; United States Department of Energy: Washington, DC, USA, 1996.

- Weil, M.; Ziemann, S. Recycling of Traction Batteries as a Challenge and Chance for Future Lithium. In Lithium-Ion Batteries Advances and Applications; Pistoia, G., Ed.; Elsevier: Amsterdam, The Netherlands, 2014; pp. 509–528. [Google Scholar]

- Herrmann, C.; Raatz, A.; Andrew, S.; Schmitt, J. Scenario-Based of Disassembly Systems for Automotive Lithium-Ion Battery Systems. Adv. Mater. Res. 2014, 907, 391–401. [Google Scholar]

- Laserna, E.M.; Gandiaga, I.; Zabala, E.S.; Badeda, J.; Stroe, D.I.; Swierczynski, M.; Goikoetxea, A. Battery second life: Hype, hope, or reality? A critical review of the state of the art. Renew. Sustain. Energy Rev. 2018, 93, 701–718. [Google Scholar] [CrossRef]

- Qi, L.; Lu, D.D.C. Review of Battery Cell Balancing Techniques. In Proceedings of the Australasian Universities Power Engineering Conference, AUPEC 2014, Curtin University, Perth, Australia, 28 September–1 October 2014; pp. 1–6. [Google Scholar]

- Omariba, Z.B.; Zhang, L.J.; Sun, D.B. Review of Battery Cell Balancing Methodologies for Optimizing Battery Pack Performance in Electric Vehicles. IEEE Access 2019, 7, 129335–129352. [Google Scholar] [CrossRef]

- Li, H.; Peng, J.; He, J.P.; Huang, Z.W.; Pan, J.P.; Wang, J. Synchronized Cell-Balancing Charging of Supercapacitors: A Consensus-Based Approach. IEEE Trans. Ind. Electron. 2018, 65, 8030–8040. [Google Scholar] [CrossRef]

- Lim, C.-S.; Lee, K.-J.; Ku, N.-J.; Hyun, D.-S.; Kim, R.-Y. A modularized equalization method based on magnetizing energy for a series-connected Lithium-ion battery string. IEEE Trans. Power Electron. 2014, 29, 1791–1799. [Google Scholar] [CrossRef]

- Shang, Y.L.; Cui, N.; Duan, B.; Zhang, C. Analysis and Optimization of Star-Structured Switched-Capacitor Equalizer for Series-Connected Battery Strings. IEEE Trans. Power Electron. 2018, 33, 9631–9646. [Google Scholar] [CrossRef]

- Yarlagadda, S.; Hartley, T.T.; Husain, I. A Battery Management System Using an Active Charge Equalization Technique Based on a DC/DC Converter Topology. IEEE Trans. Ind. Appl. 2013, 49, 2720–2729. [Google Scholar] [CrossRef]

- U.S. Department of Energy; Idaho National Laboratory. 2011 Nissan Leaf—VIN 0356 Advanced Vehicle Testing—Beginning-of-Test Battery Testing Results. Available online: https://avt.inl.gov/sites/default/files/pdf/fsev/batteryrpt2011NissanLeaf0356.pdf (accessed on 28 June 2020).

- U.S. Department of Energy; Idaho National Laboratory. 2013 Chevrolet Volt Advanced Vehicle Testing—Beginning-of-Test Battery Testing Results. Available online: https://www.energy.gov/sites/prod/files/2014/02/f7/battery_volt_3929.pdf (accessed on 28 June 2020).

- Yang, N.; Zhang, X.; Shang, B.; Li, G. Unbalanced discharging and aging due to temperature differences among the cells in a lithium-ion battery pack with parallel combination. J. Power Sour. 2016, 306, 733–741. [Google Scholar] [CrossRef]

- Gong, X.; Xiong, R.; Mi, C.C. Study of the Characteristics of Battery Packs in Electric Vehicles with Parallel-Connected Lithium-ion Battery Cells. IEEE Trans. Ind. Appl. 2015, 51, 3218–3224. [Google Scholar] [CrossRef]

- Castano-Solis, S.; Serrano-Jimenez, D.; Gauchia, L.; Sanz, J. The Influence of BMSs on the Characterization and Modeling of Series and Parallel Li-ion Packs. Energies 2017, 10, 273. [Google Scholar] [CrossRef]

- Pastor-Fernandez, C.; Bruen, T.; Widanage, W.D.; Gama-Valdez, M.A.; Marco, J. A Study of Cell-to-Cell Interactions and Degradation in Parallel Strings: Implications for the Battery Management System. J. Power Sour. 2016, 329, 574–585. [Google Scholar] [CrossRef]

- Gogoana, R.; Pinson, M.B.; Bazant, M.Z.; Sarma, S.E. Internal Resistance Matching for Parallel-connected Lithium-ion Cells and Impacts on Battery Pack Cycle Life. J. Power Sour. 2014, 252, 8–13. [Google Scholar] [CrossRef]

- Guo, R.; Lu, L.; Ouyang, M.; Feng, X. Mechanism of the entire over-discharge process and over-discharge-induced internal short circuit in lithium-ion batteries. Sci. Rep. 2016, 6, 30248. [Google Scholar] [CrossRef] [PubMed]

- Ye, M.; Song, X.; Xiong, R.; Sun, F. A Novel Dynamic Performance Analysis and Evaluation Model of Series-Parallel Connected Battery Pack for Electric Vehicles. IEEE Access 2019, 7, 14256–14265. [Google Scholar] [CrossRef]

- Hahnsang, K.; Shin, K.G. DESA: Dependable, Efficient, Scalable Architecture for Management of Large-Scale Batteries. IEEE Trans. Ind. Inform. 2012, 8, 406–417. [Google Scholar]

- Kim, T.; Qiao, W.; Qu, L. Power Electronics-Enabled Self-X Multicell Batteries: A Design Toward Smart Batteries. IEEE Trans. Power Electron. 2012, 27, 4723–4733. [Google Scholar]

- Song, C.; Shao, Y.; Song, S.; Chang, C.; Zhou, F.; Peng, S.; Xiao, F. Energy Management of Parallel-Connected Cells in Electric Vehicles Based on Fuzzy Logic Control. Energies 2017, 10, 404. [Google Scholar] [CrossRef]

- Kuo, K.C.; Hsiao, S.H. Battery Balancing Circuit and Balancing Method Thereof and Battery Activation Method. U.S. Patent 8,643,334, 18 October 2012. [Google Scholar]

- La, P.H.; Tin, T.C.; Choi, S.J. Dynamic Resistance Battery Equalization for Capacity Optimization of Parallel-Connected Cells. In Proceedings of the IEEE 10th International Conference on Power Electronic—ECCE Asia, Busan, Korea, 27–30 May 2019. [Google Scholar]

- Meng, J.; Ricco, M.; Luo, G.; Swierczynski, M.; Stroe, D.I.; Stroe, A.I.; Teodorescu, R. An Overview and Comparison of Online Implementable SOC Estimation Methods for Lithium-ion Battery. IEEE Trans. Ind. Appl. 2018, 54, 1583–1591. [Google Scholar] [CrossRef]

- LG Chemical. LG 18650HD2 2000mAh Datasheet. Available online: https://voltaplex.com/media/whitepapers/specification-sheet/LG_HD2_Specification_Sheet.pdf (accessed on 28 June 2020).

- Choi, S.S.; Lim, H.S. Factors that Affect Cycle-life and Possible Degradation Mechanisms of a Li-ion Cell Based on LiCoO2. J. Power Sour. 2012, 111, 130–136. [Google Scholar] [CrossRef]

- Savoye, F.; Venet, P.; Millet, M.; Groot, J. Impact of periodic current pulses on Li-ion battery performance. IEEE Trans. Ind. Electron. 2012, 59, 3481–3488. [Google Scholar] [CrossRef]

| Component | Part Number | Quantity |

|---|---|---|

| Switches | IRF8313PbF | 4 |

| Gate driver | TC4429 | 4 |

| Opto-coupler | 4N25 | 4 |

| Fuel gauge | MAX17205G | 4 |

| Scenario 1 | Scenario 2 | Scenario 3 | |

|---|---|---|---|

| ΔSOCinitial (%) | 30 | 30 | 30 |

| ΔSOCfinal (%) | 5 | <1 | <1 |

| R1 & R2 (Ω) | 0.1 & 0.33 | 0.1 & 1 | 0.1 & 0.5 |

| DoSE (%) | 83.3 | >98 | >98 |

| t2 (s) | N/A | 2300 | 2500 |

| ∑Ploss_external (W) | 1.57 | 3.59 | 1.96 |

| Mode | Performance Index | Fixed-Resistor Method | Proposed Method | SOC Sequencing Method |

|---|---|---|---|---|

| Charging mode | DoSE (%) | 40 | 98 | 98 |

| t2 (seconds) | N/A | 4500 | 3400 | |

| Discharging mode | DoSE (%) | 46 | 98 | 98 |

| t2 (seconds) | N/A | 2500 | 2000 |

| Mode | Performance Index | Fixed-Resistor Method | Proposed Method | SOC Sequencing Method |

|---|---|---|---|---|

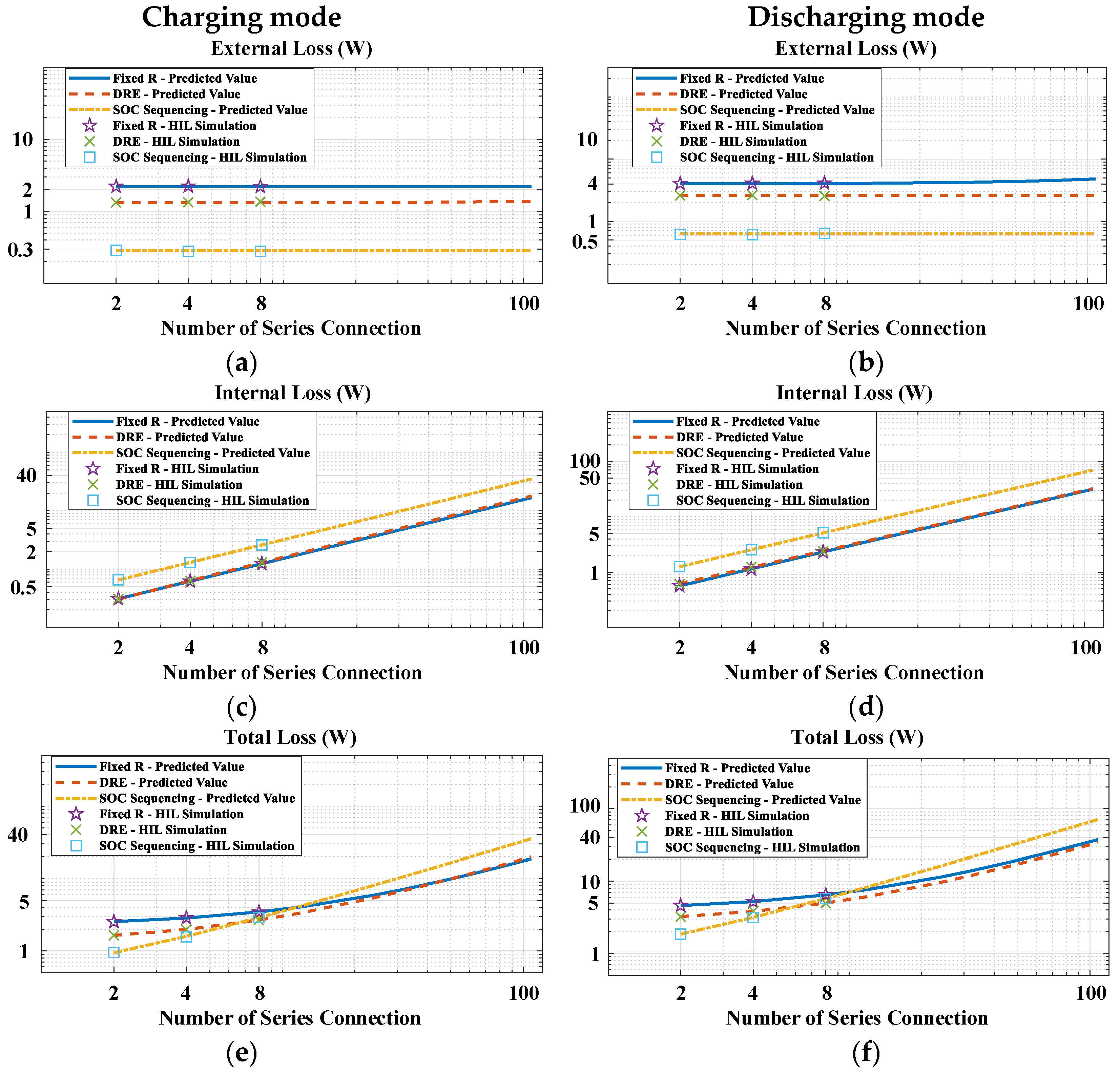

| 2S4P Configuration | ||||

| Charging | ∑Ploss_external (W) | 2.22 | 1.33 | 0.29 |

| ∑Ploss_internal (W) | 0.31 | 0.31 | 0.66 | |

| Total Loss (W) | 2.53 | 1.64 | 0.95 | |

| Discharging | ∑Ploss_external (W) | 4.04 | 2.6 | 0.62 |

| ∑Ploss_internal (W) | 0.57 | 0.61 | 1.26 | |

| Total Loss (W) | 4.61 | 3.21 | 1.86 | |

| 4S4P Configuration | ||||

| Charging | ∑Ploss_external (W) | 2.24 | 1.34 | 0.28 |

| ∑Ploss_internal (W) | 0.62 | 0.63 | 1.29 | |

| Total Loss (W) | 2.86 | 1.97 | 1.57 | |

| Discharging | ∑Ploss_external (W) | 4.07 | 2.63 | 0.61 |

| ∑Ploss_internal (W) | 1.14 | 1.24 | 2.54 | |

| Total Loss (W) | 5.21 | 3.87 | 3.14 | |

| 8S4P Configuration | ||||

| Charging | ∑Ploss_external (W) | 2.21 | 1.37 | 0.28 |

| ∑Ploss_internal (W) | 1.24 | 1.30 | 2.6 | |

| Total Loss (W) | 3.45 | 2.67 | 2.89 | |

| Discharging | ∑Ploss_external (W) | 4.14 | 2.56 | 0.64 |

| ∑Ploss_internal (W) | 2.32 | 2.41 | 5.13 | |

| Total Loss (W) | 6.46 | 4.97 | 5.77 | |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

La, P.-H.; Choi, S.-J. Novel Dynamic Resistance Equalizer for Parallel-Connected Battery Configurations. Energies 2020, 13, 3315. https://doi.org/10.3390/en13133315

La P-H, Choi S-J. Novel Dynamic Resistance Equalizer for Parallel-Connected Battery Configurations. Energies. 2020; 13(13):3315. https://doi.org/10.3390/en13133315

Chicago/Turabian StyleLa, Phuong-Ha, and Sung-Jin Choi. 2020. "Novel Dynamic Resistance Equalizer for Parallel-Connected Battery Configurations" Energies 13, no. 13: 3315. https://doi.org/10.3390/en13133315

APA StyleLa, P.-H., & Choi, S.-J. (2020). Novel Dynamic Resistance Equalizer for Parallel-Connected Battery Configurations. Energies, 13(13), 3315. https://doi.org/10.3390/en13133315