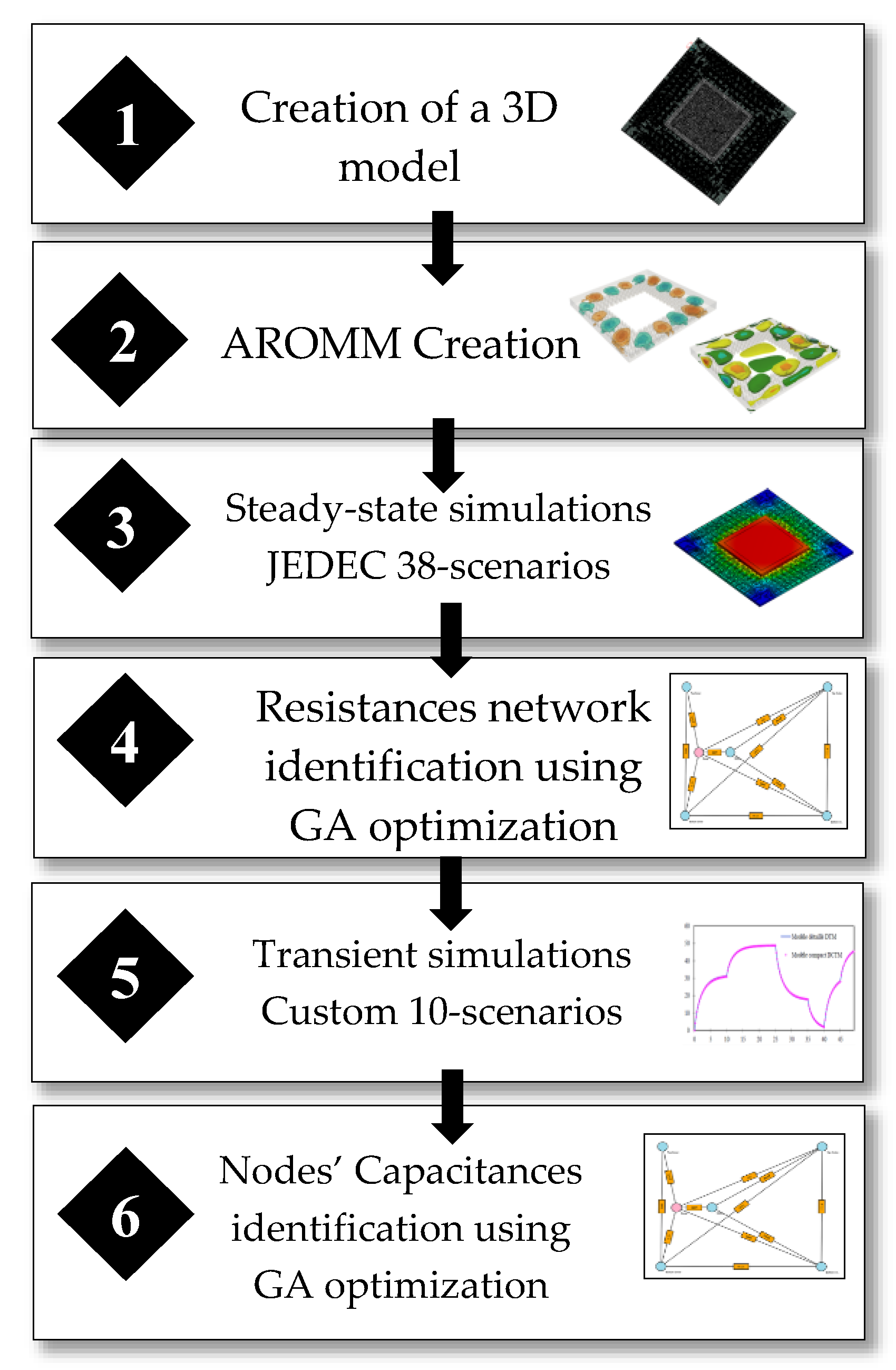

8.4. Steady-State Results

Two cases are presented. They highlight the component thermal behavior when:

Test 1: A power dissipation of 2.6 watts is applied on zone 2

Test 2: Zones 3, 5, and 8 are respectively submitted to a power dissipation of 0.41, 0.675, and 0.0975 watts.

The mathematical calculations assume the boundary conditions on package external surfaces presented in

Table 6.

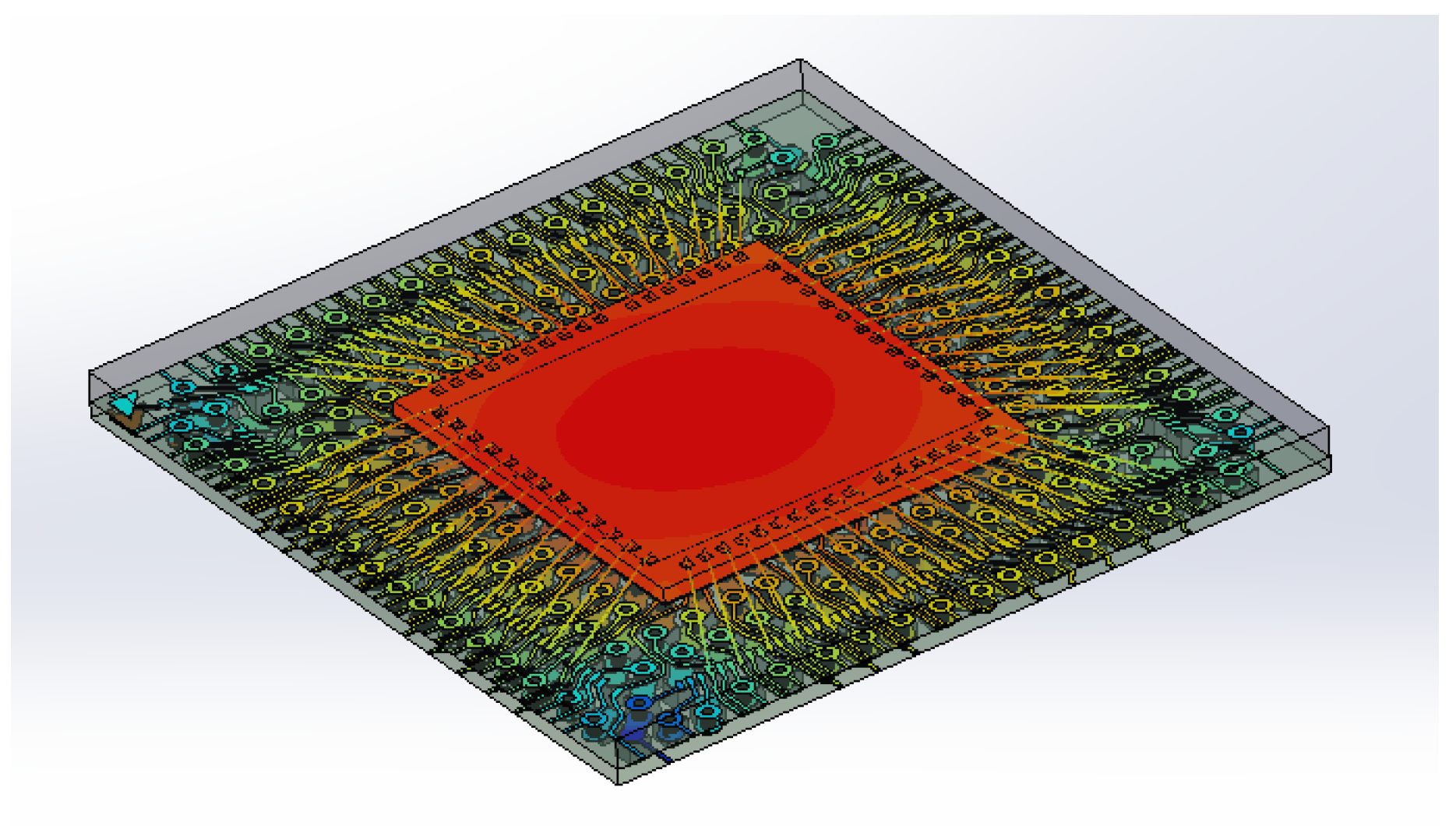

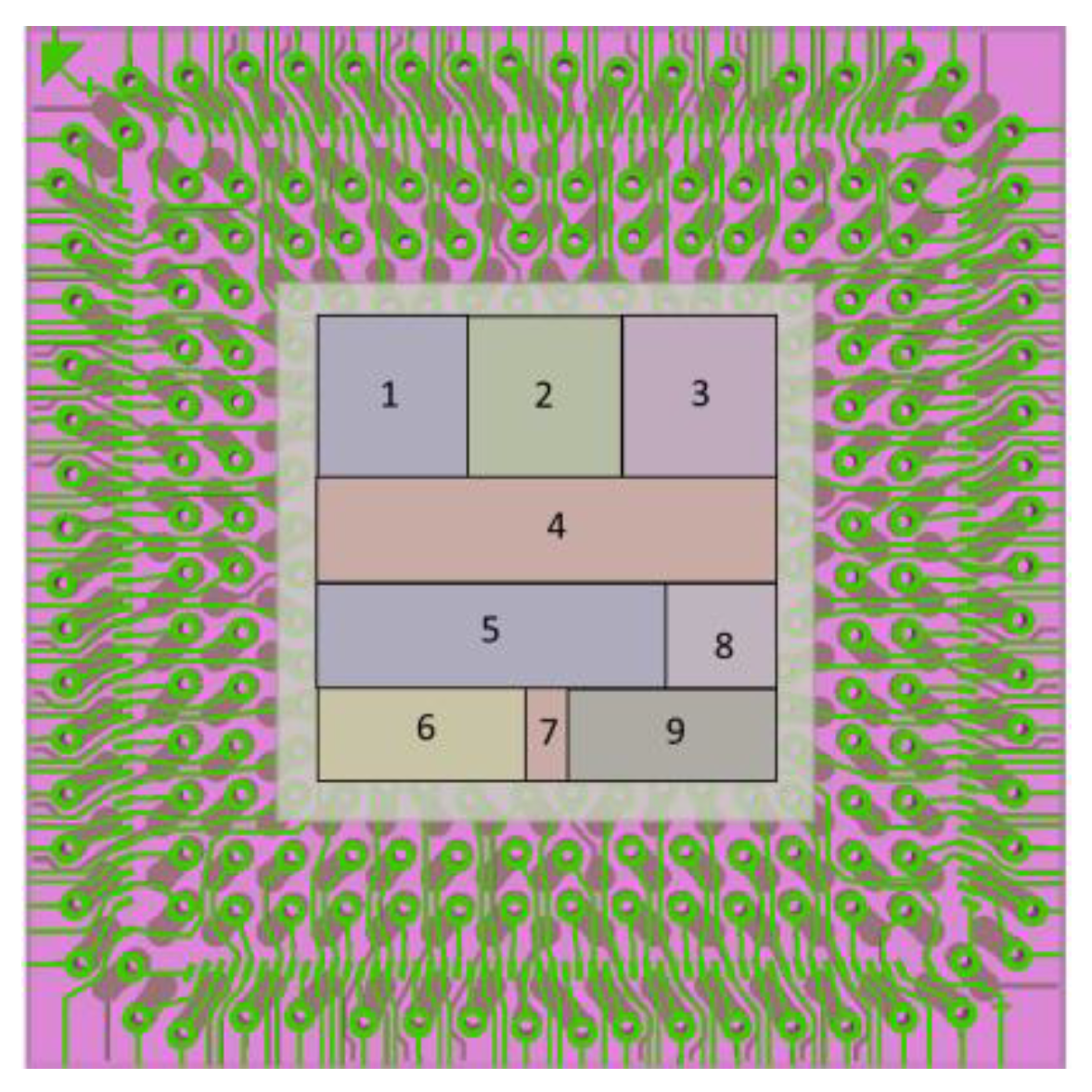

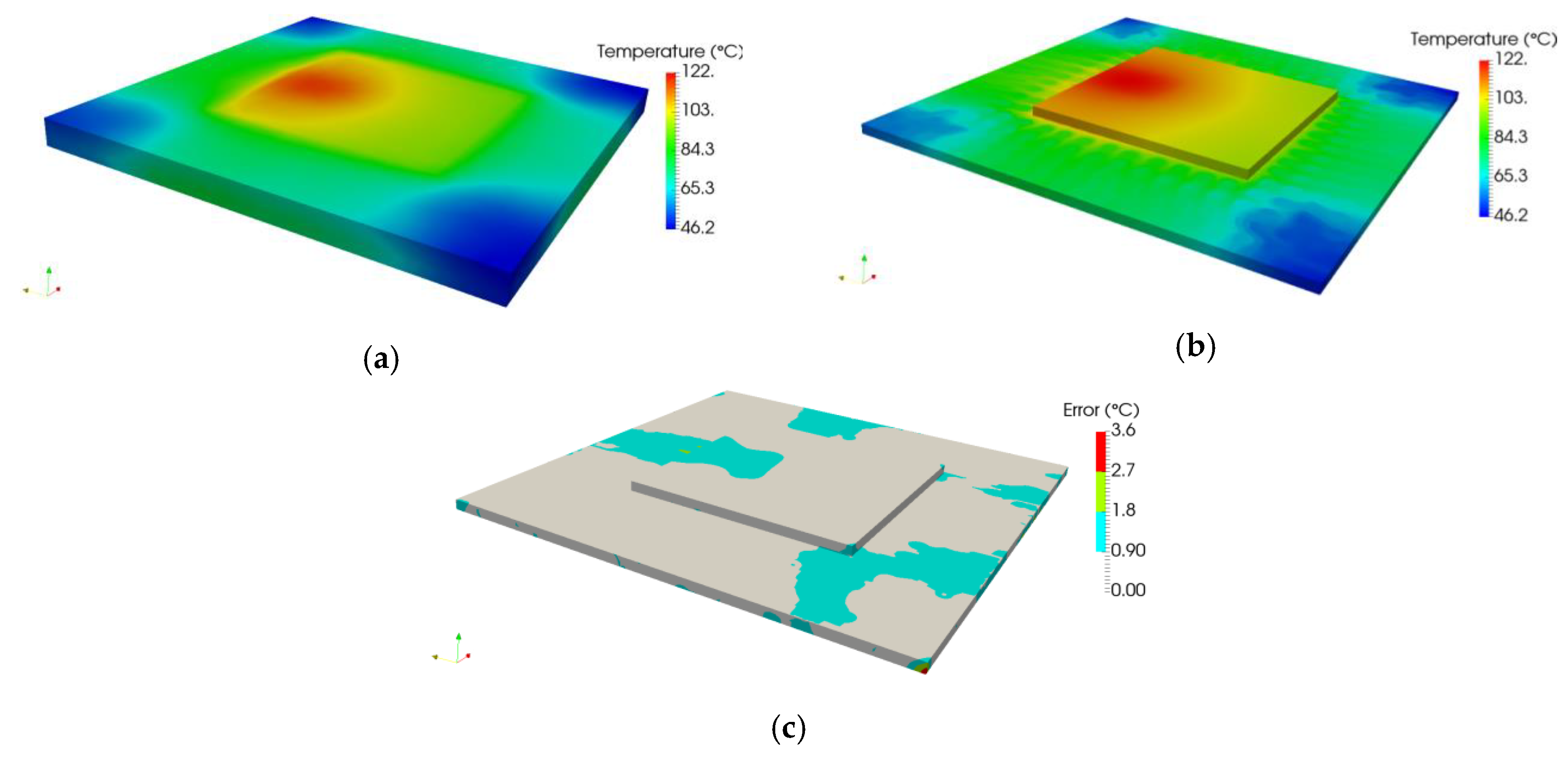

Figure 10 presents the temperature field calculated by the reduced model for the whole package, as well as for the chip on the BGA substrate. The computation time of the derived ROM is lower than 0.5 s for a temporal simulation of 60 s (the time required to reach steady state). The main interest of the modal method lies in its ability to compute, at low cost, the whole temperature field, even for complex geometries such as the BGA packages family. Then, 4.5 s are needed to rebuild the whole temperature field for 101 snapshots. The hot-spot location on the chip, our concern, is properly identified, but fine details are also recovered as the temperature elevation on the copper tracks. The error between the reduced and the finite elements model is also displayed in

Figure 10c. In most of the chip, and copper track, the error is below 1 °C (0.8%), which is a very interesting result for this preliminary investigation.

The temperature distribution at steady state for test 2 is presented in

Figure 11 As the boundary conditions differ significantly from test 1 and the dissipated power is reduced, the maximum temperature reached by the chip is much lower and is predicted by the modal model with a maximum error of 0.36 °C (1.6%). Obviously, the hot-spot location moves as the different zones are activated, which is well predicted.

Finally, as the temperature field on the chip is different, it substantially affects the heat spreading on the tracks and, thus, the heat distribution on the ball array. The knowledge of the whole temperature field enables the computation of temperature gradients, and opens the way to thermomechanical consideration.

8.5. Transient Results

Dynamic simulations are conducted to compare the thermal prediction of the computed ROM with the FEM simulation (assumed to be the reference) on two test cases. FEM simulations need roughly 47 min to perform a 50 s transient simulation with multi-activations.

Two sets of boundary conditions (different from those presented in

Table 6) were chosen and are summarized in

Table 7.

Boundary conditions of Case 1 correspond to a component mounted on a PCB in vertical natural convection plus radiation. Case 2 corresponds to a component sandwiched between the PCB and thermal drain reported on top of the component ( integrates all thermal paths: Contact resistances, thermal interface material, and aluminum drain).

Two power transient scenarios are defined: One in which different zones are successively activated, as presented in

Table 8, and a second one in which different zones are simultaneously activated, as presented in

Table 9. This latter describes a realistic operating case of a BGA. Indeed, power Input-Outputs and firmware are always on and the other functional areas have dynamic activation imposed by software operations.

The computation time required by the reduced model is 4.5 s, which is 600 times faster than that of the finite elements model.

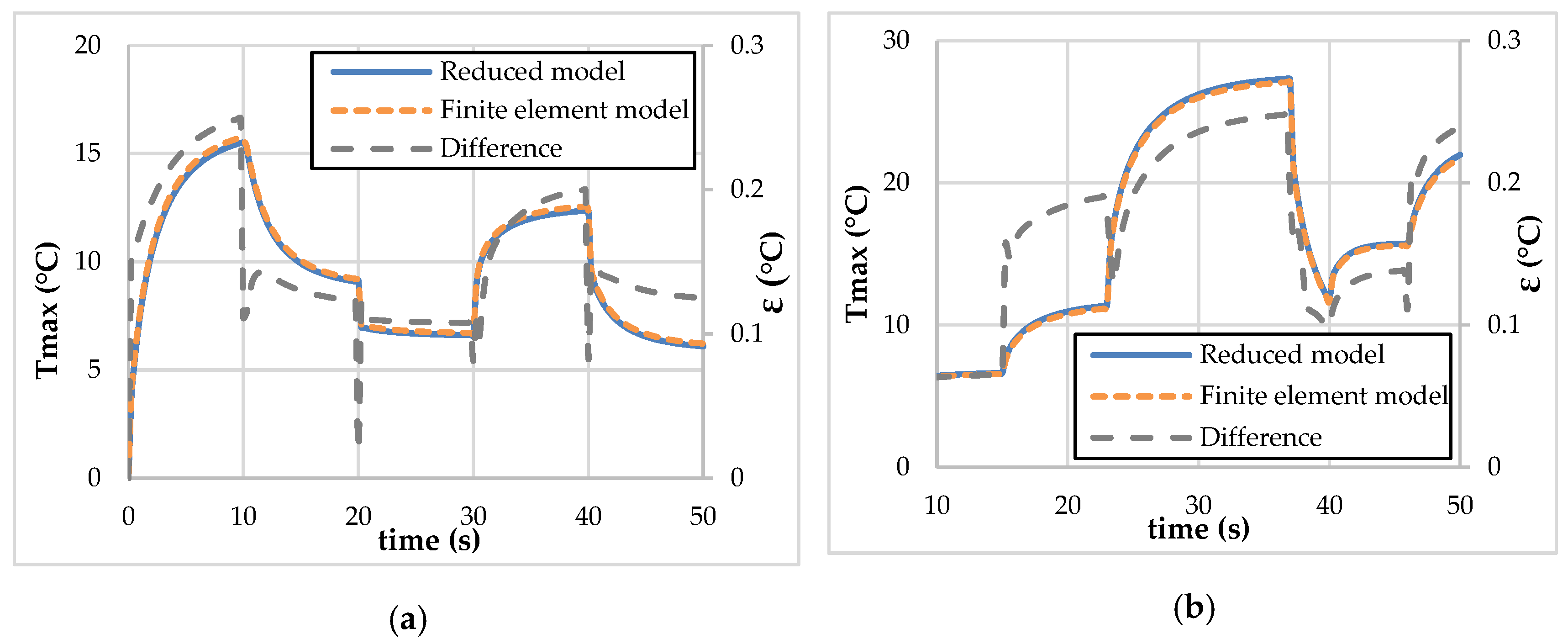

The maximum temperature reached by the chip computed by the amalgamated reduced-order modal model (AROMM) and by the finite elements model has been compared for both cases.

Figure 12a,b present the comparison for boundary conditions case 1 with activation profile 1 (

Table 8) and boundary conditions case 2 with activation profile 2 (

Table 9), respectively.

The agreement on this critical parameter is very good, as it never outreaches 0.25 °C, i.e., a relative difference less than 1.6% for the first case and 1% for the second. A sudden rise in the difference between models is noticed when the power changes. This effect is induced by modal reduction as modes with a high time constant have been discarded.

This very good accuracy on the maximal temperature is accompanied by a satisfying precision on the entire chip.

Figure 13 presents the temperature field computed by the reduced model at

t = 37 s, i.e., at the time where the error is the most important. The maximal temperature difference on the chip between the reduced model and the FE one is less than 0.5 °C. On most of the chip (and the copper etches), the error is below 0.2 °C, yielding an average error (in time and space) of 0.08 °C.

The error field is erratic, which is characteristic of modal reduction. Thus, the location of the maximum error cannot be known a priori with this method.

Thus, both test cases using different boundary conditions and power profiles confirm the very good accuracy of the ROM, as the error is below 2% for each time step on the chip. Those results validate the new substructuring model order reduction approach to create an AROMM of complex components.

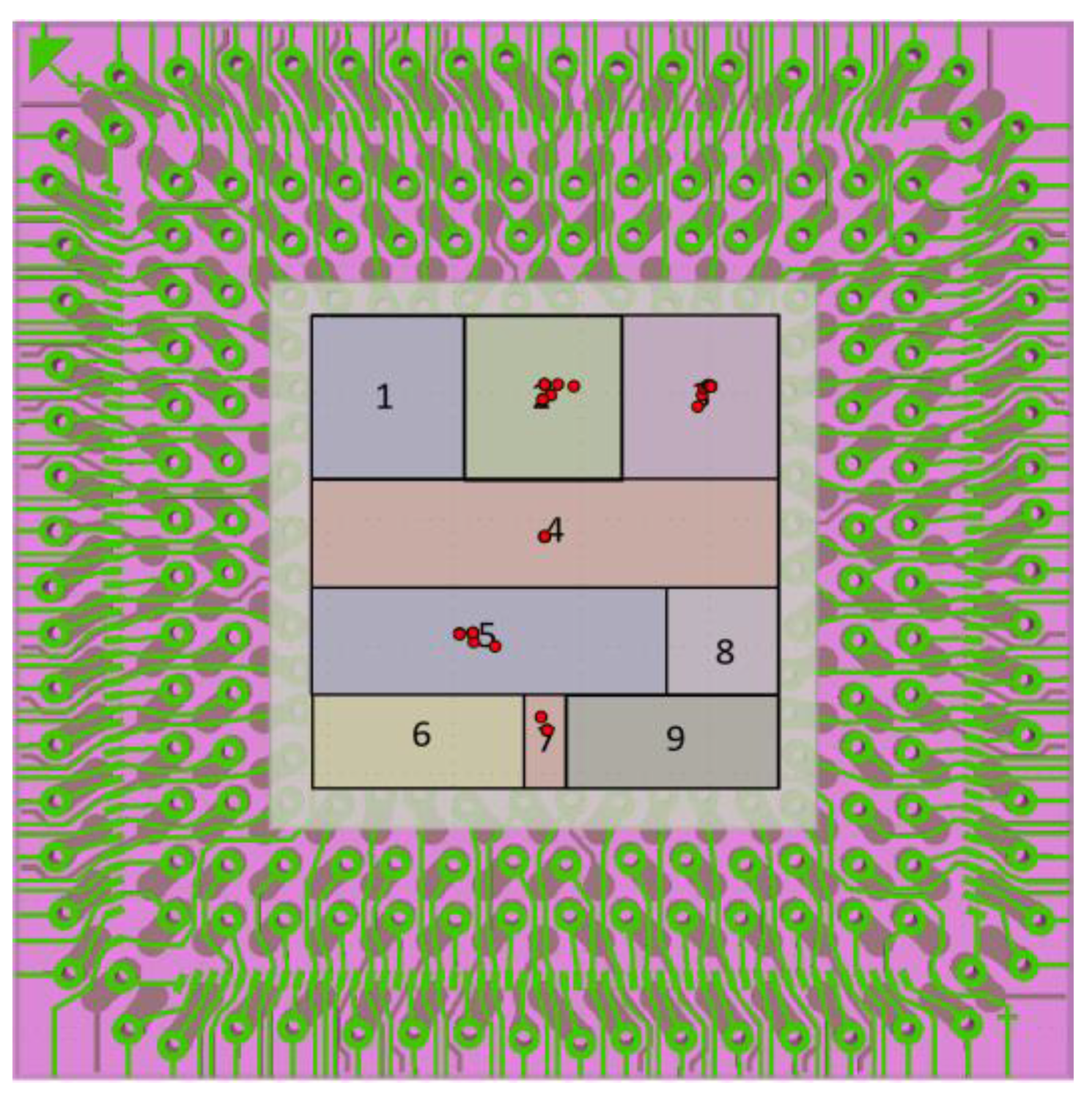

Moreover, as modal methods compute the temperature field in its integrality, there is no need for an a priori definition of the outputs. Indeed, the localizations of the hottest spot of the chip during the transient simulation (depicted by circles) are highlighted in

Figure 14.

Obviously, the hot spot moves as the different zones are activated. This simple fact questions the notion of junction temperature. This is confirmed by

Figure 15, which compares the maximum temperature reached by the chip to the temperature at the center of the chip: An output at the center of the chip would underestimate the temperature by up to 4 °C, i.e., a relative error of 25%, which is by far greater than the temperature prediction error of the reduced model.

Another main interest of this substructuring modal approach is to have two distinct models, one for the chip and one for all the other parts of the BGA. If one of them is modified, only the latter must be regenerated. In the case of the component, all constituting parts except the die are imposed by the manufacturer, so this model is realized only once. Then, the model of the chip can be easily regenerated to take into account the new spatial power profile or correction of semiconductor thermal properties.

The substructuring modal approach offers a solution to integrate the real spatial power distribution of the component without additional creation and simulation time. Indeed, this power distribution evolves during the development cycle from the uniform power distribution to the real profile based on electric simulation.