Reliability Characterization of Gallium Nitride MIS-HEMT Based Cascode Devices for Power Electronic Applications

Abstract

1. Introduction

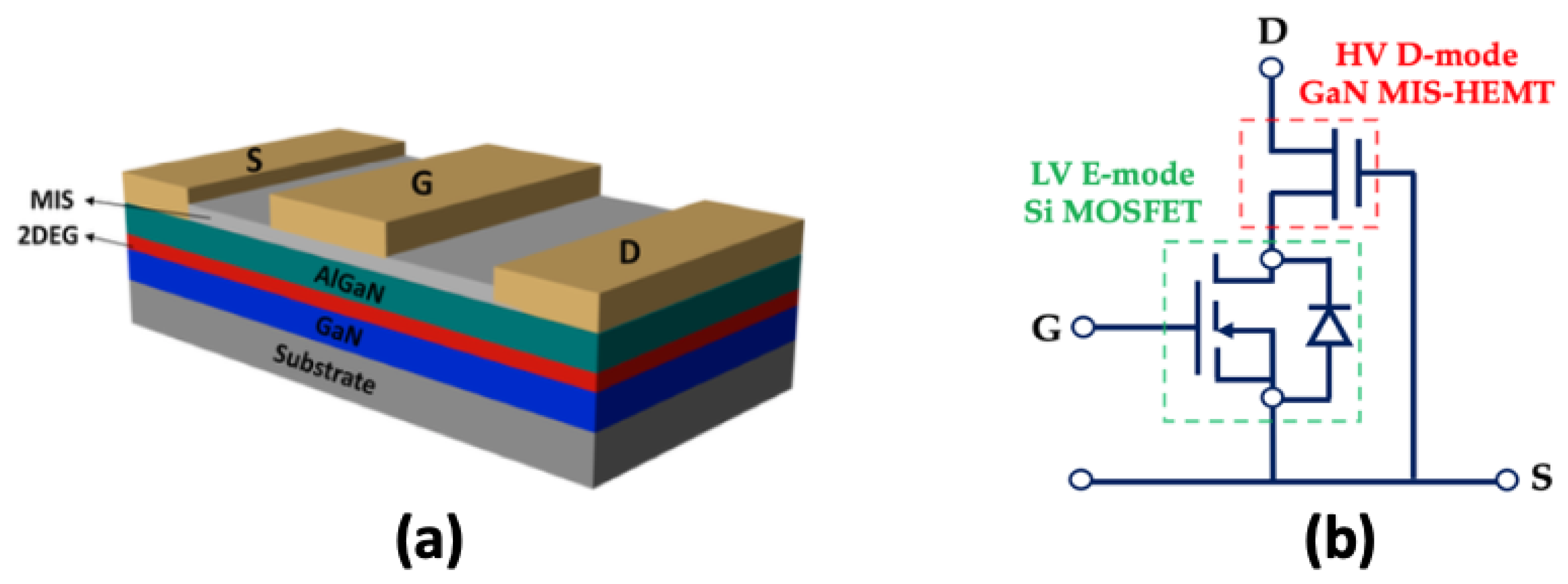

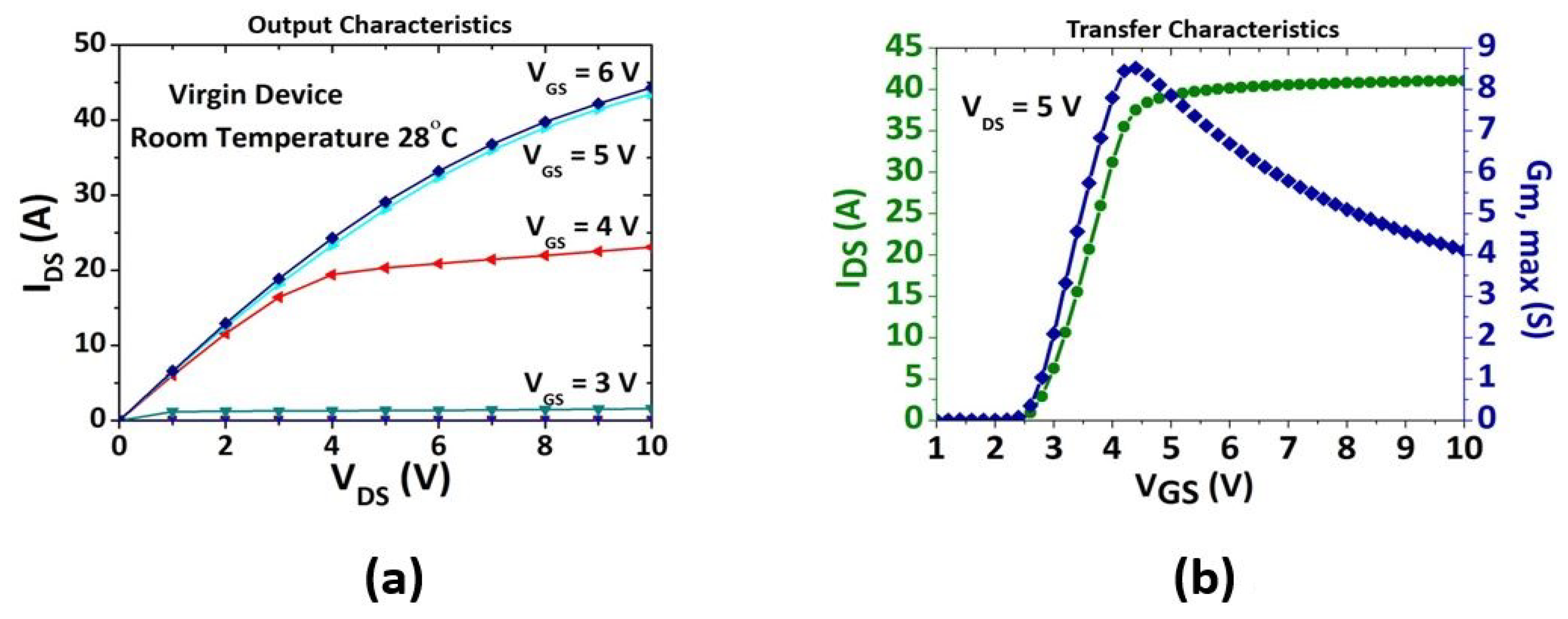

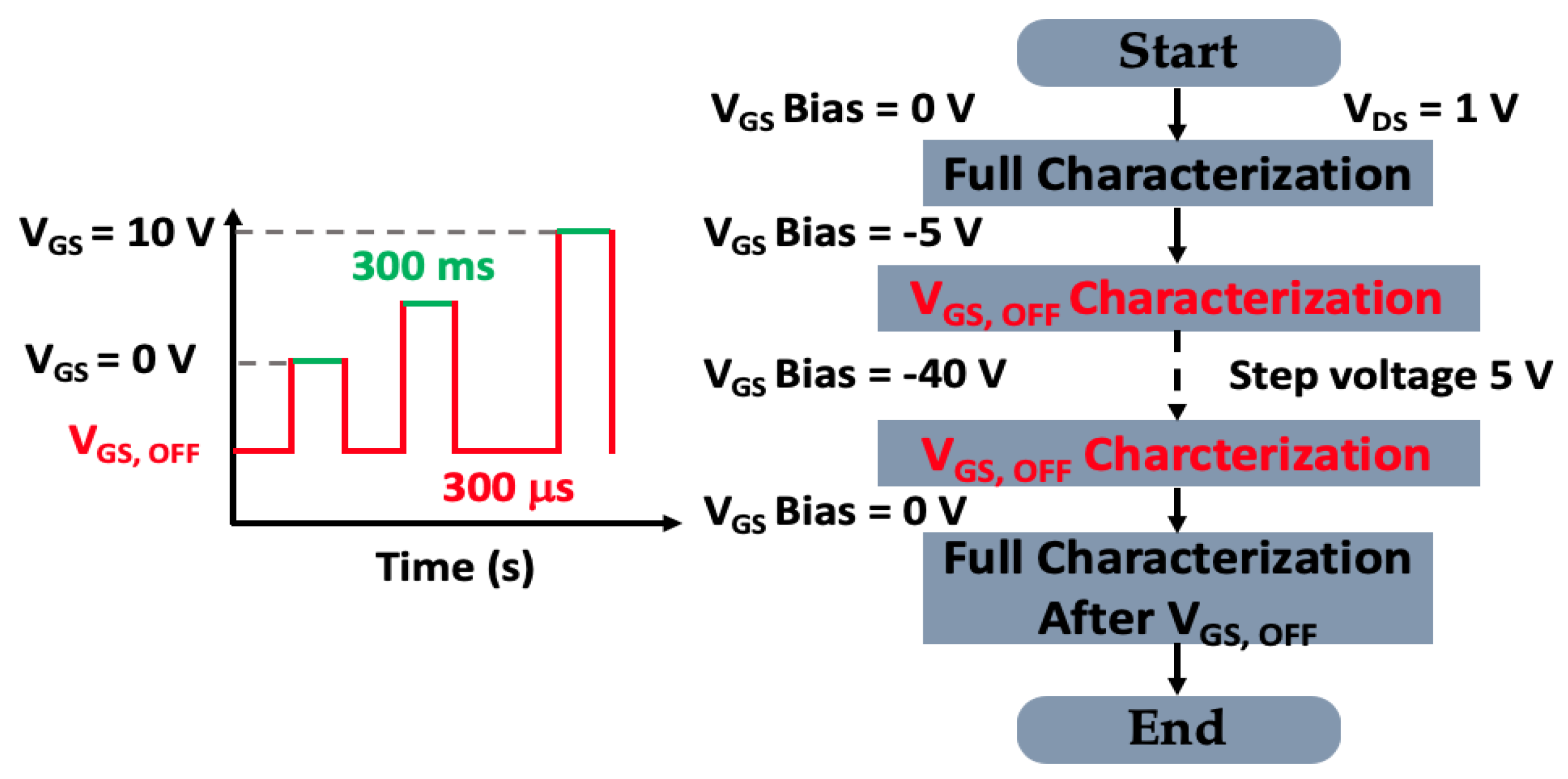

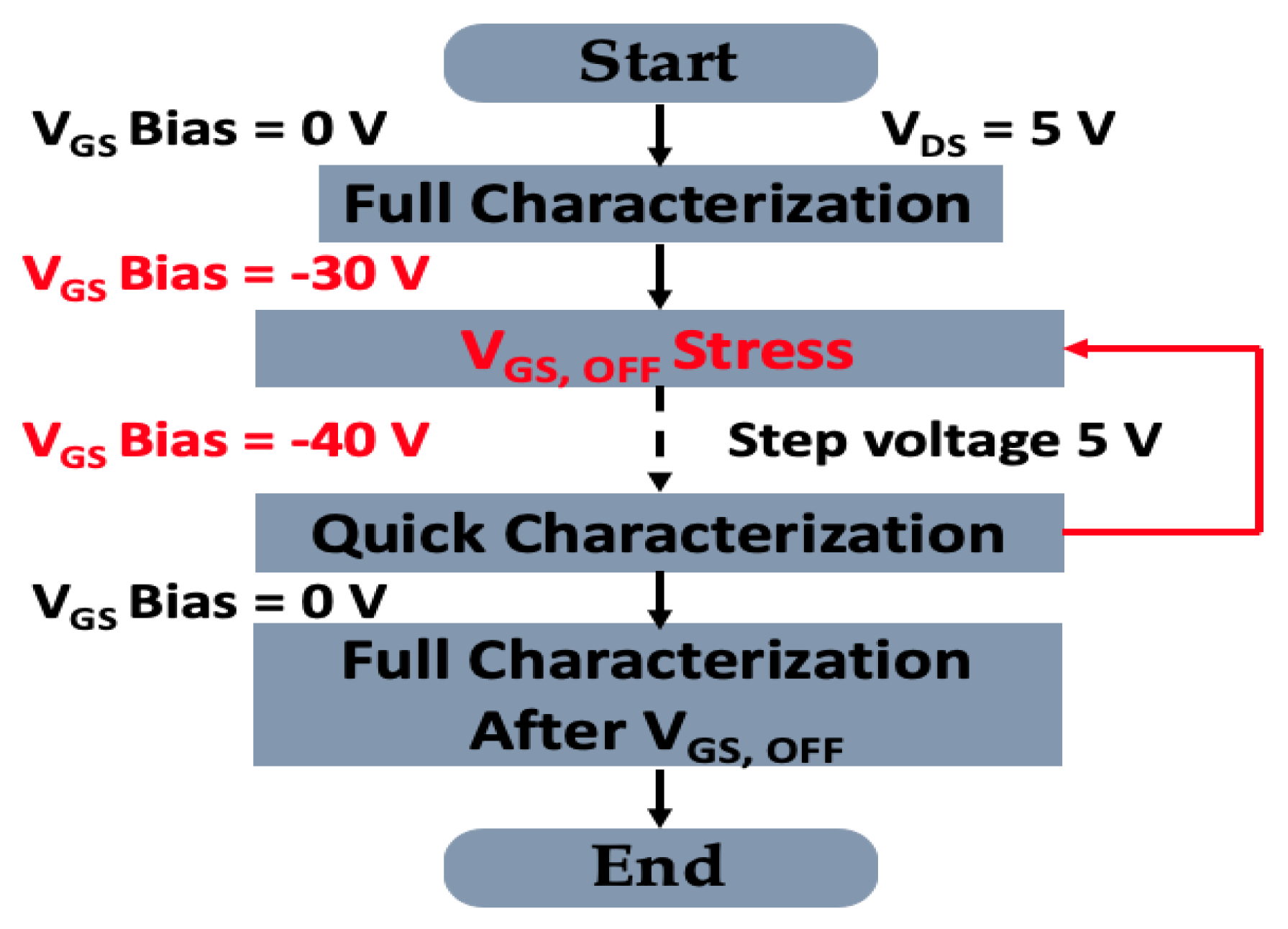

2. Experimental Details

3. Results and Discussion

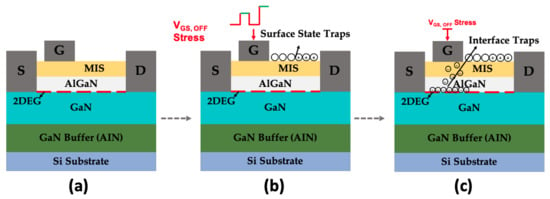

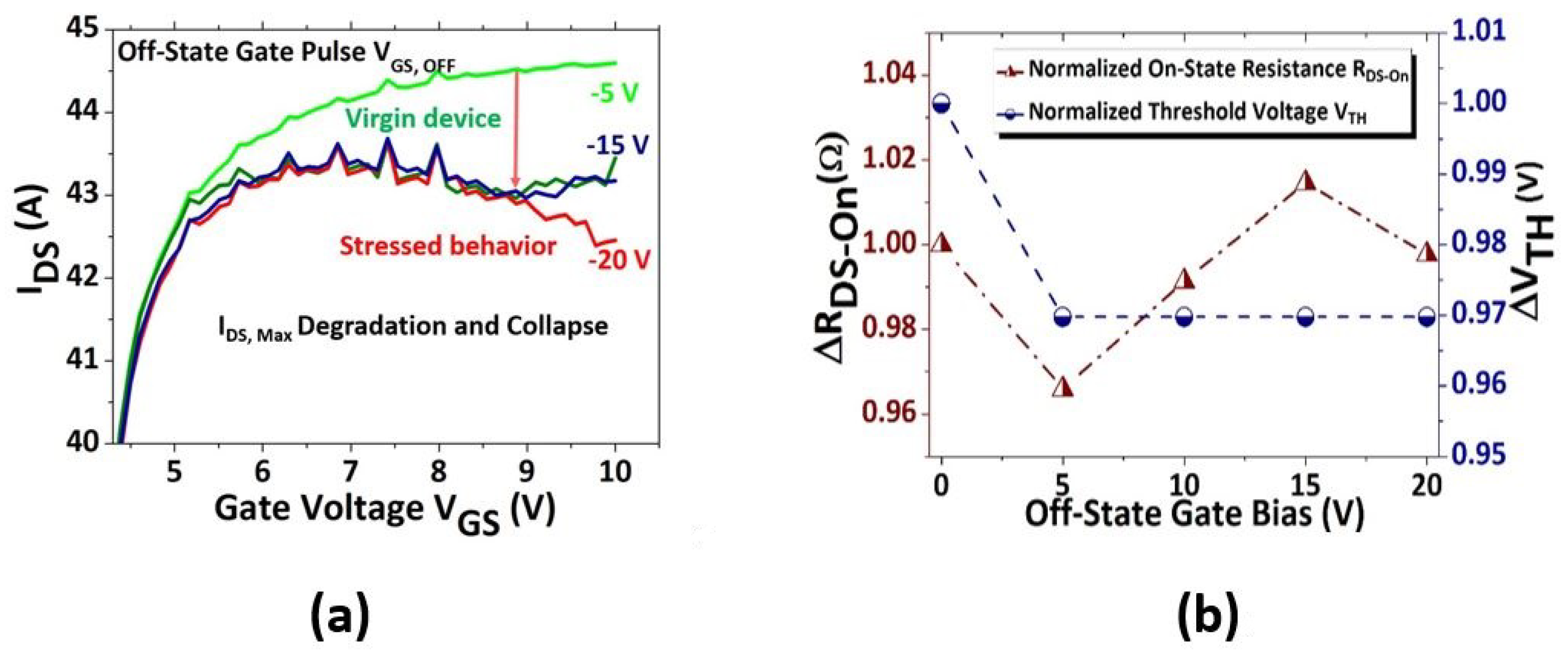

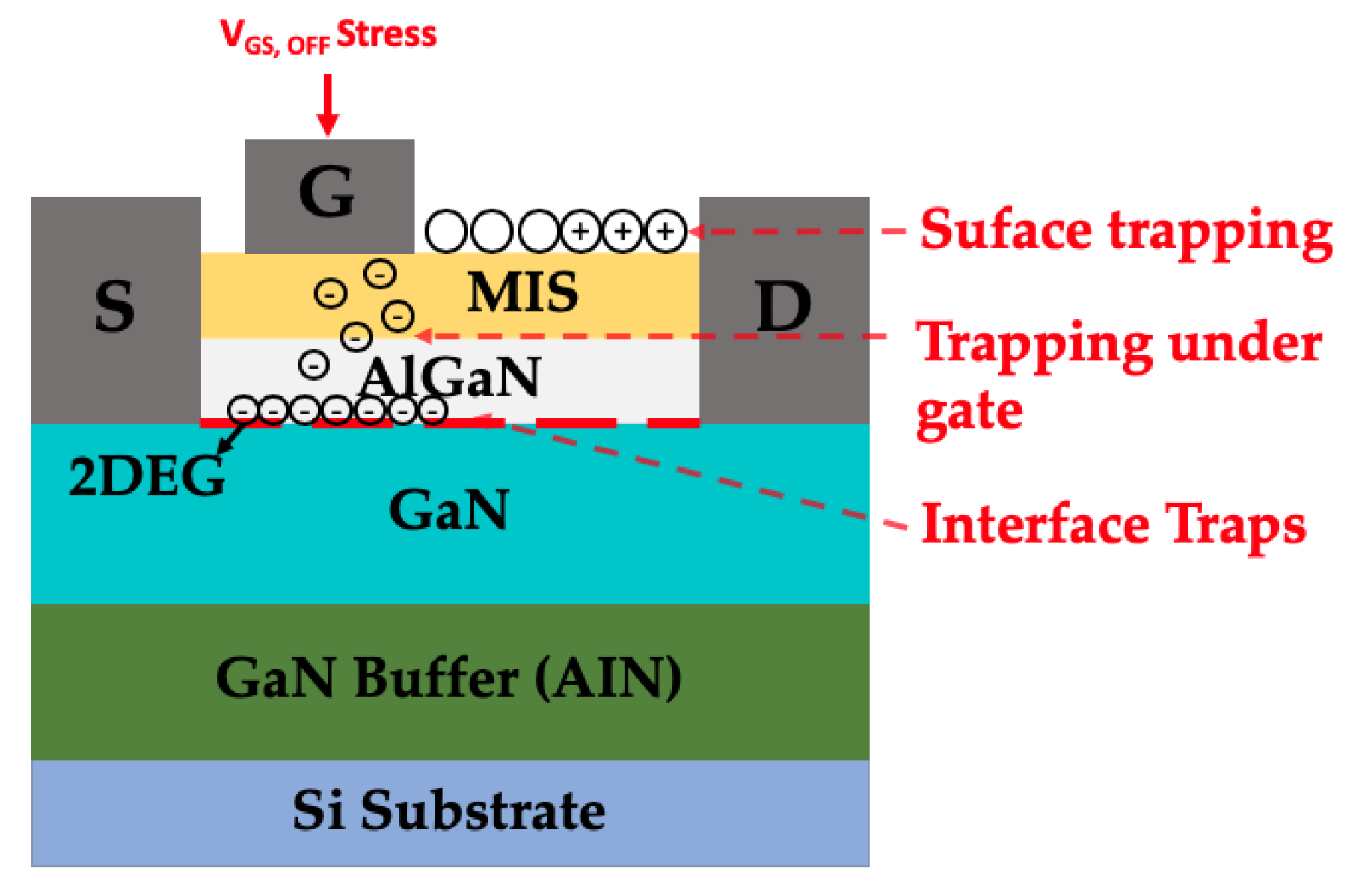

3.1. Pulsed Negative Gate Bias Stress (Gate Lag)

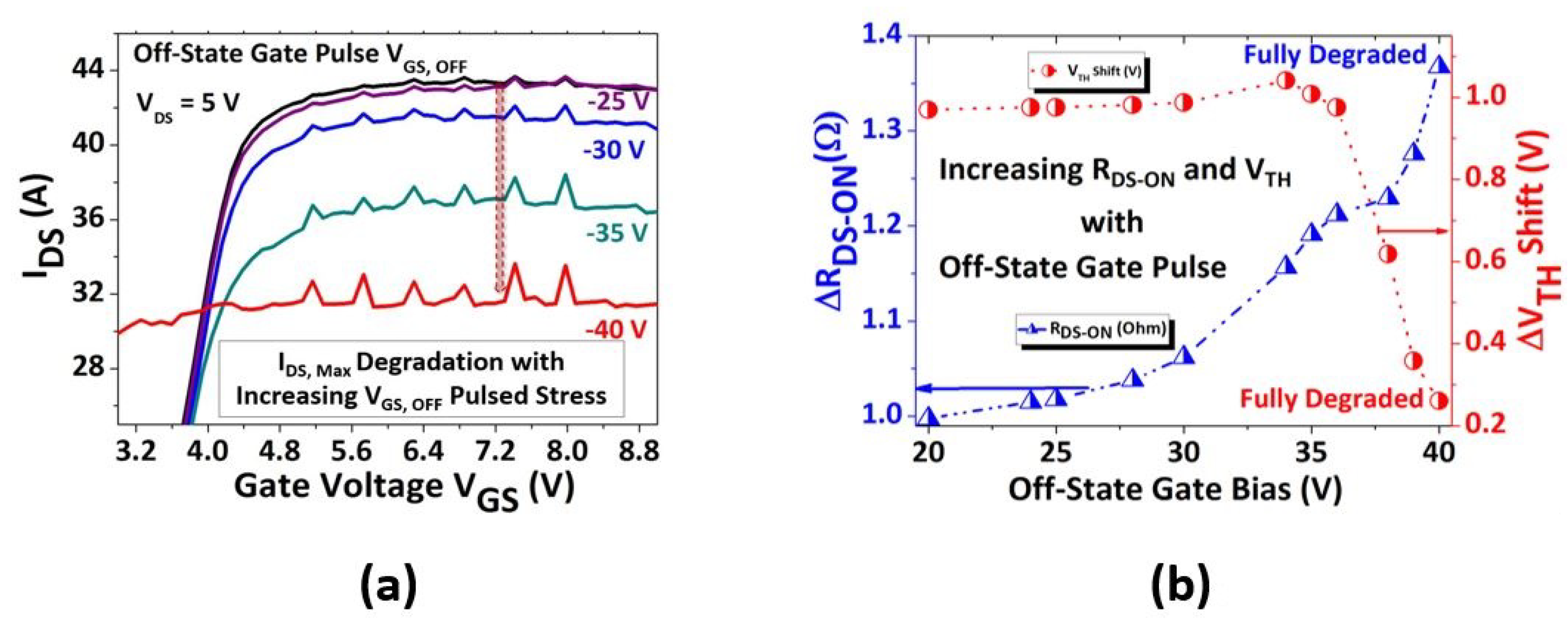

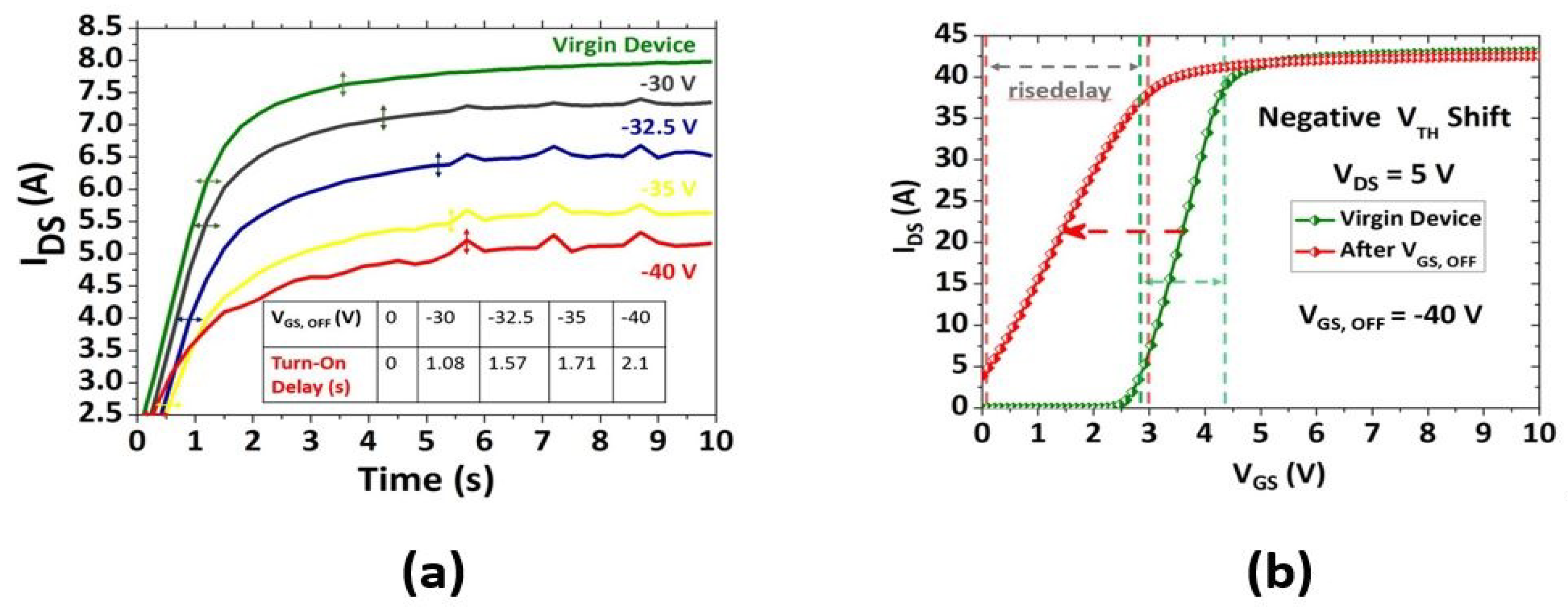

3.2. Prolonged Off-State Gate Bias Stress

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chen, W.; Wong, K.Y.; Huang, W.; Chen, K.J. High-performance Al Ga N/ Ga N lateral field-effect rectifiers compatible with high electron mobility transistors. Appl. Phys. Lett. 2008, 92, 253501. [Google Scholar] [CrossRef]

- Zhang, N.Q.; Moran, B.; Denbaars, S.; Mishra, U.; Wang, X.; Ma, T. Kilovolt AlGaN/GaN HEMTs as switching devices. Physica Status Solidi (a) 2001, 188, 213–217. [Google Scholar] [CrossRef]

- Chou, P.C.; Cheng, S. Performance characterization of gallium nitride HEMT cascode switch for power conditioning applications. Mater. Sci. Eng. B 2015, 198, 43–50. [Google Scholar] [CrossRef]

- Tan, W.; Uren, M.; Fry, P.; Houston, P.; Balmer, R.; Martin, T. High temperature performance of AlGaN/GaN HEMTs on Si substrates. Solid-State Electron. 2006, 50, 511–513. [Google Scholar] [CrossRef]

- Gaska, R.; Chen, Q.; Yang, J.; Osinsky, A.; Khan, M.A.; Shur, M.S. High-temperature performance of AlGaN/GaN HFETs on SiC substrates. IEEE Electron Device Lett. 1997, 18, 492–494. [Google Scholar] [CrossRef]

- Micovic, M.; Brown, D.; Regan, D.; Wong, J.; Tang, Y.; Herrault, F.; Santos, D.; Burnham, S.; Tai, J.; Prophet, E.; et al. High frequency GaN HEMTs for RF MMIC applications. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. IEDM16-59–IEDM16-62. [Google Scholar]

- Sheridan, D.C.; Lee, D.; Ritenour, A.; Bondarenko, V.; Yang, J.; Coleman, C. Ultra-low loss 600V–1200V GaN power transistors for high efficiency applications. In Proceedings of the PCIM Europe 2014, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 20–22 May 2014; VDE: Frankfurt, Germany, 2014; pp. 1–7. [Google Scholar]

- Mishra, U.K.; Parikh, P.; Wu, Y.F. AlGaN/GaN HEMTs-an overview of device operation and applications. Proc. IEEE 2002, 90, 1022–1031. [Google Scholar] [CrossRef]

- Van Hove, M.; Boulay, S.; Bahl, S.R.; Stoffels, S.; Kang, X.; Wellekens, D.; Geens, K.; Delabie, A.; Decoutere, S. CMOS process-compatible high-power low-leakage AlGaN/GaN MISHEMT on silicon. IEEE Electron Device Lett. 2012, 33, 667–669. [Google Scholar] [CrossRef]

- Wu, T.L.; Marcon, D.; Zahid, M.B.; Van Hove, M.; Decoutere, S.; Groeseneken, G. Comprehensive investigation of on-state stress on D-mode AlGaN/GaN MIS-HEMTs. In Proceedings of the 2013 IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 14–18 April 2013; pp. 3C.5.1–3C.5.7. [Google Scholar]

- Letellier, A.; Dubois, M.R.; Trovao, J.P.; Maher, H. Gallium nitride semiconductors in power electronics for electric vehicles: Advantages and challenges. In Proceedings of the 2015 IEEE Vehicle Power and Propulsion Conference (VPPC), Montreal, QC, Canada, 19–22 October 2015; pp. 1–6. [Google Scholar]

- Stubbe, T.; Mallwitz, R.; Rupp, R.; Pozzovivo, G.; Bergner, W.; Haeberlen, O.; Kunze, M. GaN power semiconductors for PV inverter applications-Opportunities and risks. In Proceedings of the CIPS 2014—8th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 25–27 February 2014; VDE: Frankfurt, Germany, 2014; pp. 1–6. [Google Scholar]

- Su, M.; Chen, C.; Rajan, S. Prospects for the application of GaN power devices in hybrid electric vehicle drive systems. Semicond. Sci. Technol. 2013, 28, 074012. [Google Scholar] [CrossRef]

- Delaine, J.; Jeannin, P.O.; Frey, D.; Guepratte, K. High frequency DC-DC converter using GaN device. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 1754–1761. [Google Scholar]

- Wrzecionko, B.; Bortis, D.; Biela, J.; Kolar, J.W. Novel AC-coupled gate driver for ultrafast switching of normally off SiC JFETs. IEEE Trans. Power Electron. 2011, 27, 3452–3463. [Google Scholar] [CrossRef]

- Reusch, D.; Lee, F.C.; Gilham, D.; Su, Y. Optimization of a high density gallium nitride based non-isolated point of load module. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 2914–2920. [Google Scholar]

- Kampitsis, G.; Papathanassiou, S.; Manias, S. Performance consideration of an AC coupled gate drive circuit with forward bias for normally-on SiC JFETs. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013; pp. 3224–3229. [Google Scholar]

- Cheng, S.; Chou, P.C. Power conditioning applications of 700V GaN-HEMTs cascode switch. In Proceedings of the IECON 2015-41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015; pp. 004796–004801. [Google Scholar]

- Huang, X.; Liu, Z.; Li, Q.; Lee, F.C. Evaluation and application of 600 V GaN HEMT in cascode structure. IEEE Trans. Power Electron. 2013, 29, 2453–2461. [Google Scholar] [CrossRef]

- Verzellesi, G.; Mazzanti, A.; Basile, A.F.; Boni, A.; Zanoni, E.; Canali, C. Experimental and numerical assessment of gate-lag phenomena in AlGaAs-GaAs heterostructure field-effect transistors (FETs). IEEE Trans. Electron Devices 2003, 50, 1733–1740. [Google Scholar] [CrossRef]

- Yeats, R.; D’Avanzo, D.; Chan, K.; Fernandez, N.; Taylor, T.; Vogel, C. Gate slow transients in GaAs MESFETs-causes, cures, and impact on circuits. In Proceedings of the Technical Digest—International Electron Devices Meeting, San Francisco, CA, USA, 11–14 December 1988; pp. 842–845. [Google Scholar]

- Vetury, R.; Zhang, N.Q.; Keller, S.; Mishra, U.K. The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs. IEEE Trans. Electron Devices 2001, 48, 560–566. [Google Scholar] [CrossRef]

- Nguyen, C.; Nguyen, N.; Grider, D. Drain current compression in GaN MODFETs under large-signal modulation at microwave frequencies. Electron. Lett. 1999, 35, 1380–1382. [Google Scholar] [CrossRef]

- Binari, S.C.; Ikossi, K.; Roussos, J.A.; Kruppa, W.; Park, D.; Dietrich, H.B.; Koleske, D.D.; Wickenden, A.E.; Henry, R.L. Trapping effects and microwave power performance in AlGaN/GaN HEMTs. IEEE Trans. Electron Devices 2001, 48, 465–471. [Google Scholar] [CrossRef]

- Mitrofanov, O.; Manfra, M. Mechanisms of gate lag in GaN/AlGaN/GaN high electron mobility transistors. Superlattices Microstruct. 2003, 34, 33–53. [Google Scholar] [CrossRef]

- Meneghini, M.; Bisi, D.; Marcon, D.; Stoffels, S.; Van Hove, M.; Wu, T.L.; Decoutere, S.; Meneghesso, G.; Zanoni, E. Trapping and reliability assessment in D-mode GaN-based MIS-HEMTs for power applications. IEEE Trans. Power Electron. 2013, 29, 2199–2207. [Google Scholar] [CrossRef]

- Schroder, D.K.; Babcock, J.A. Negative bias temperature instability: Road to cross in deep submicron silicon semiconductor manufacturing. J. Appl. Phys. 2003, 94, 1–18. [Google Scholar] [CrossRef]

- Kimizuka, N.; Yamaguchi, K.; Imai, K.; Iizuka, T.; Liu, C.; Keller, R.; Horiuchi, T. NBTI enhancement by nitrogen incorporation into ultrathin gate oxide for 0.10-/spl mu/m gate CMOS generation. In Proceedings of the 2000 Symposium on VLSI Technology. Digest of Technical Papers (Cat. No. 00CH37104), Honolulu, HI, USA, 13–15 June 2000; pp. 92–93. [Google Scholar]

- Marinella, M.; Schroder, D.; Isaacs-Smith, T.; Ahyi, A.; Williams, J.; Chung, G.; Wan, J.; Loboda, M. Evidence of negative bias temperature instability in 4 H-SiC metal oxide semiconductor capacitors. Appl. Phys. Lett. 2007, 90, 253508. [Google Scholar] [CrossRef]

- Sang, F.; Wang, M.; Zhang, C.; Tao, M.; Xie, B.; Wen, C.P.; Wang, J.; Hao, Y.; Wu, W.; Shen, B. Investigation of the threshold voltage drift in enhancement mode GaN MOSFET under negative gate bias stress. Jpn. J. Appl. Phys. 2015, 54, 044101. [Google Scholar] [CrossRef]

- Yen, C.T.; Hung, H.T.; Hung, C.C.; Lee, C.Y.; Lee, H.Y.; Lee, L.S.; Huang, Y.F.; Cheng, C.Y.; Chuang, P.J.; Hsu, F.J. Negative Bias Temperature Instability of SiC MOSFET. Mater. Sci. Forum 2016, 858, 595–598. [Google Scholar] [CrossRef]

- Santarelli, A.; Cignani, R.; Niessen, D.; Gibiino, G.P.; Traverso, P.A.; Di Giacomo, V.; Chang, C.; Floriot, D.; Schreurs, D.; Filicori, F. Evaluation of gan fet power performance reduction due to nonlinear charge trapping effects. In Proceedings of the 2014 9th European Microwave Integrated Circuit Conference, Rome, Italy, 6–7 October 2014; pp. 198–201. [Google Scholar]

- Nunes, L.C.; Gomes, J.M.; Cabral, P.M.; Pedro, J.C. A new nonlinear model extraction methodology for GaN HEMTs subject to trapping effects. In Proceedings of the 2015 IEEE MTT-S International Microwave Symposium, Phoenix, AZ, USA, 17–22 May 2015; pp. 1–4. [Google Scholar]

- Santarelli, A.; Cignani, R.; Gibiino, G.P.; Niessen, D.; Traverso, P.A.; Florian, C.; Schreurs, D.M.P.; Filicori, F. A double-pulse technique for the dynamic I/V characterization of GaN FETs. IEEE Microw. Wirel. Compon. Lett. 2013, 24, 132–134. [Google Scholar] [CrossRef]

- Li, R.; Wu, X.; Yang, S.; Sheng, K. Dynamic on-state resistance test and evaluation of GaN power devices under hard-and soft-switching conditions by double and multiple pulses. IEEE Trans. Power Electron. 2018, 34, 1044–1053. [Google Scholar] [CrossRef]

- Liu, S.; Yang, S.; Tang, Z.; Jiang, Q.; Liu, C.; Wang, M.; Shen, B.; Chen, K.J. Interface/border trap characterization of Al2O3/AlN/GaN metal-oxide-semiconductor structures with an AlN interfacial layer. Appl. Phys. Lett. 2015, 106, 051605. [Google Scholar] [CrossRef]

- Ťapajna, M.; Jurkovič, M.; Válik, L.; Haščík, Š.; Gregušová, D.; Brunner, F.; Cho, E.M.; Kuzmík, J. Bulk and interface trapping in the gate dielectric of GaN based metal-oxide-semiconductor high-electron-mobility transistors. Appl. Phys. Lett. 2013, 102, 243509. [Google Scholar] [CrossRef]

- Deng, X.; Zhang, B.; Li, Z.; Chen, Z. Two-dimensional analysis of the surface state effects in 4H-SiC MESFETs. Microelectron. Eng. 2008, 85, 295–299. [Google Scholar] [CrossRef]

- Bisi, D.; Meneghini, M.; De Santi, C.; Chini, A.; Dammann, M.; Brueckner, P.; Mikulla, M.; Meneghesso, G.; Zanoni, E. Deep-level characterization in GaN HEMTs-Part I: Advantages and limitations of drain current transient measurements. IEEE Trans. Electron Devices 2013, 60, 3166–3175. [Google Scholar] [CrossRef]

- Jin, D.; Joh, J.; Krishnan, S.; Tipirneni, N.; Pendharkar, S.; Del Alamo, J. Total current collapse in High-Voltage GaN MIS-HEMTs induced by Zener trapping. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. IEDM13-148–IEDM13-151. [Google Scholar]

- Guo, A.; del Alamo, J.A. Negative-bias temperature instability of GaN MOSFETs. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016; pp. 4A-1-1–4A-1-6. [Google Scholar]

- Guo, A.; del Alamo, J.A. Unified mechanism for positive-and negative-bias temperature instability in GaN MOSFETs. IEEE Trans. Electron Devices 2017, 64, 2142–2147. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Elangovan, S.; Cheng, S.; Chang, E.Y. Reliability Characterization of Gallium Nitride MIS-HEMT Based Cascode Devices for Power Electronic Applications. Energies 2020, 13, 2628. https://doi.org/10.3390/en13102628

Elangovan S, Cheng S, Chang EY. Reliability Characterization of Gallium Nitride MIS-HEMT Based Cascode Devices for Power Electronic Applications. Energies. 2020; 13(10):2628. https://doi.org/10.3390/en13102628

Chicago/Turabian StyleElangovan, Surya, Stone Cheng, and Edward Yi Chang. 2020. "Reliability Characterization of Gallium Nitride MIS-HEMT Based Cascode Devices for Power Electronic Applications" Energies 13, no. 10: 2628. https://doi.org/10.3390/en13102628

APA StyleElangovan, S., Cheng, S., & Chang, E. Y. (2020). Reliability Characterization of Gallium Nitride MIS-HEMT Based Cascode Devices for Power Electronic Applications. Energies, 13(10), 2628. https://doi.org/10.3390/en13102628