Parametric Compact Thermal Models of Power LEDs

Abstract

:1. Introduction

2. Measurement Results

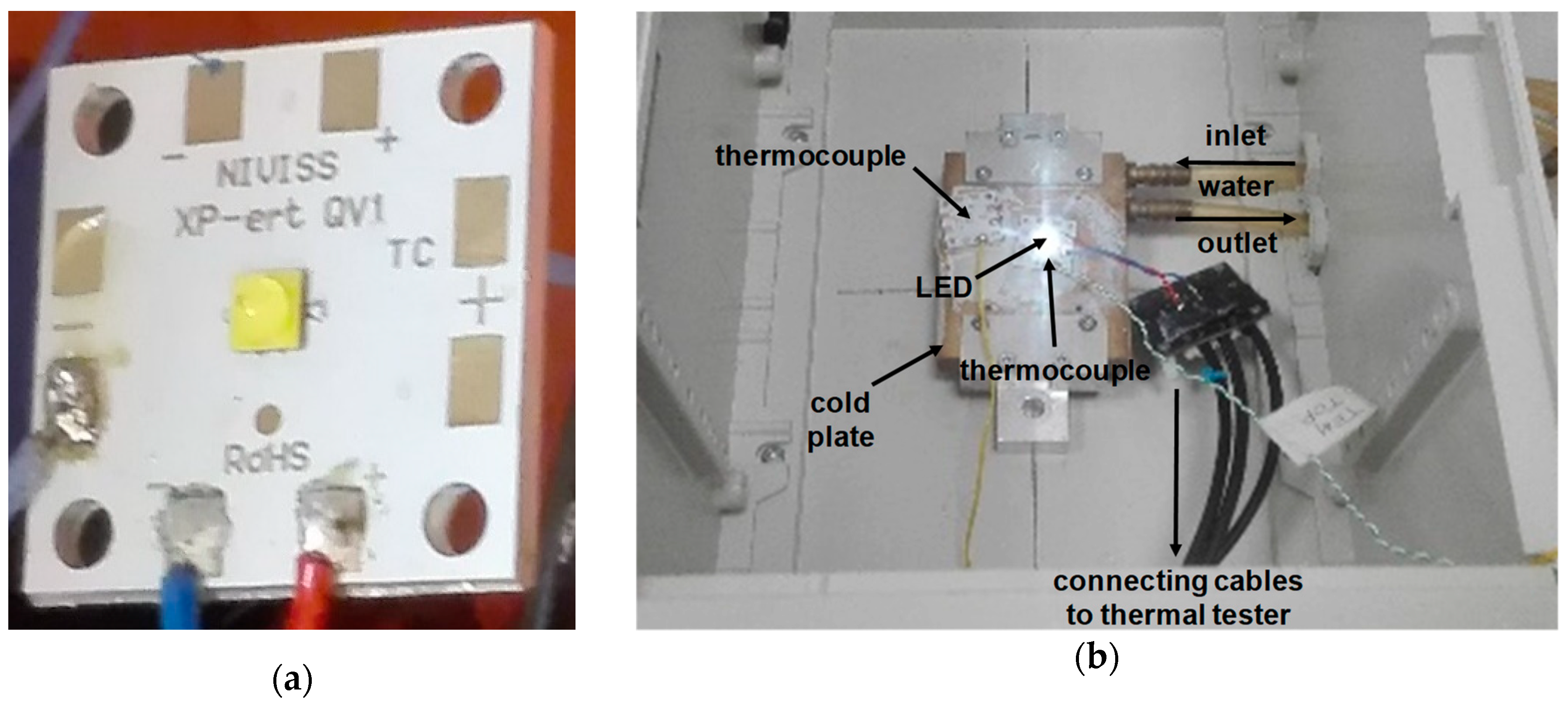

2.1. Measurement Equipment and Experimental Setup

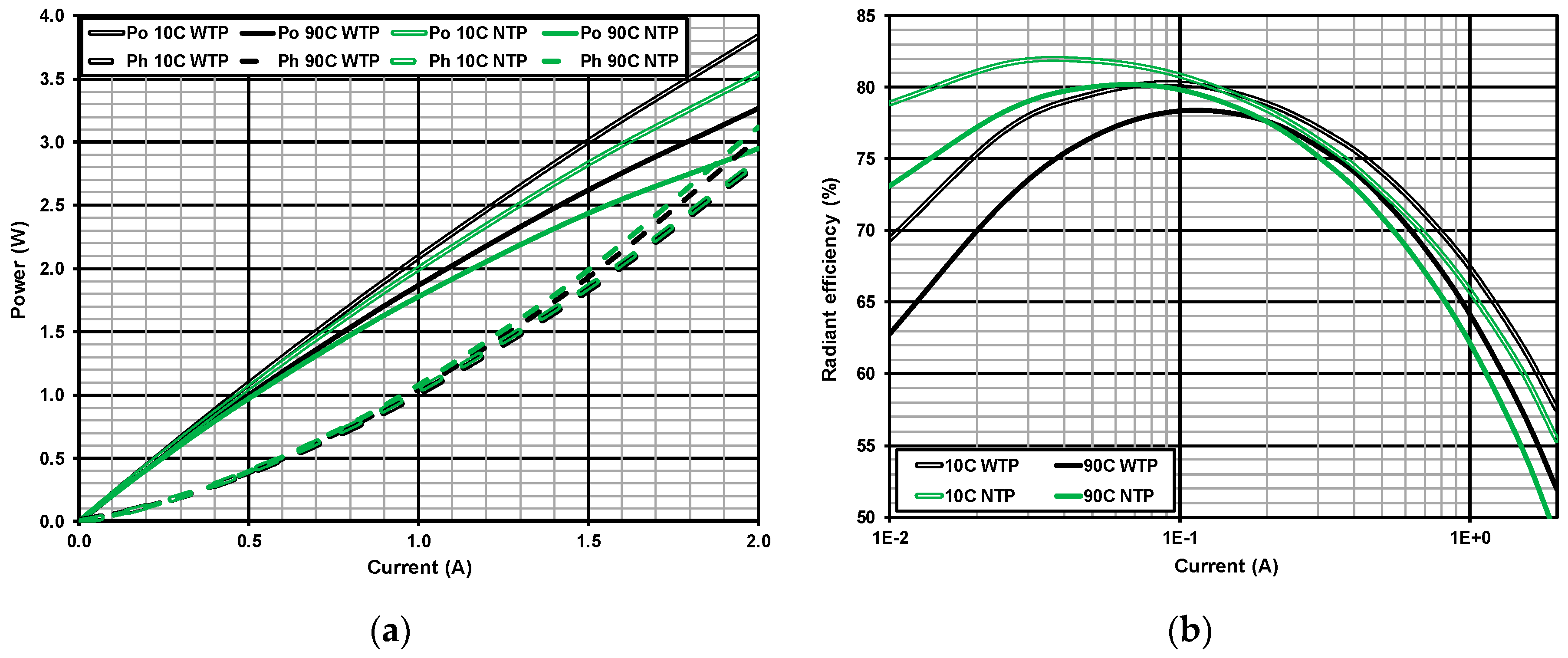

2.2. Results of Electrical Measurements

2.3. Optical Measurements

3. Thermal Modeling and Simulations

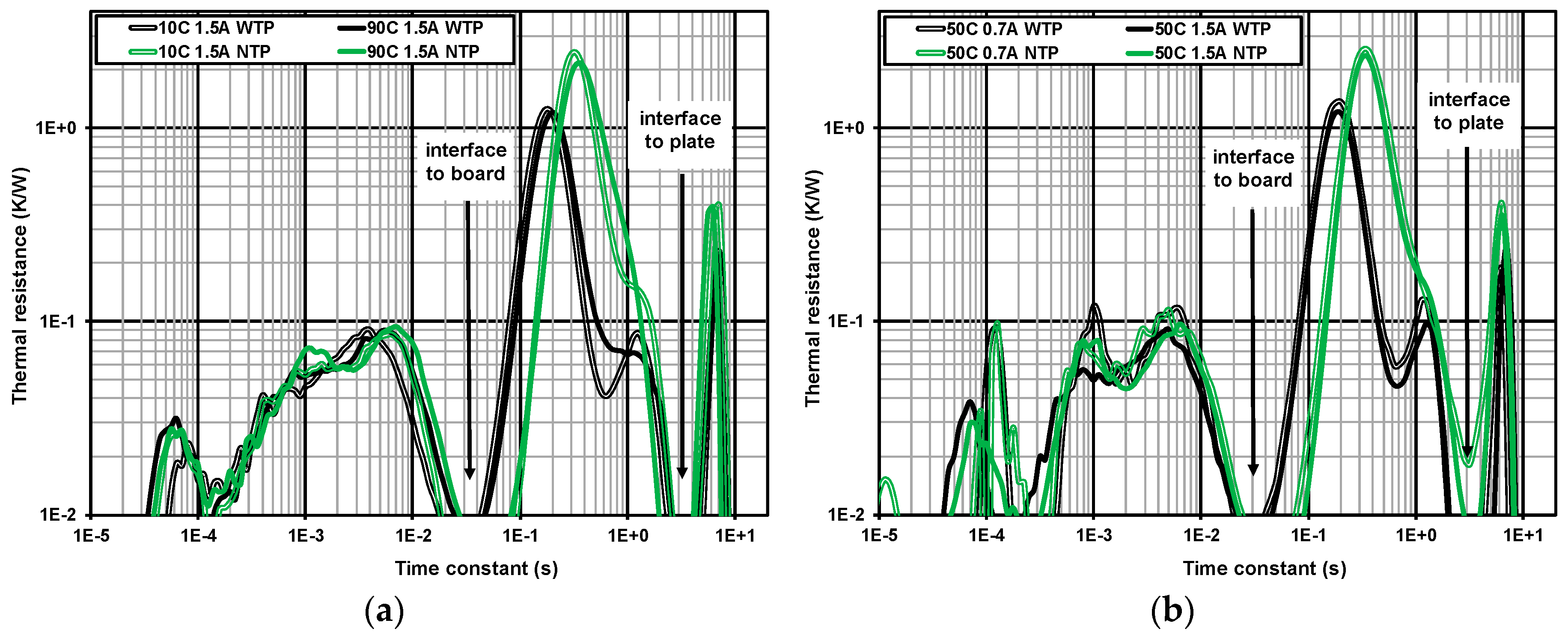

3.1. Time Constant Spectra

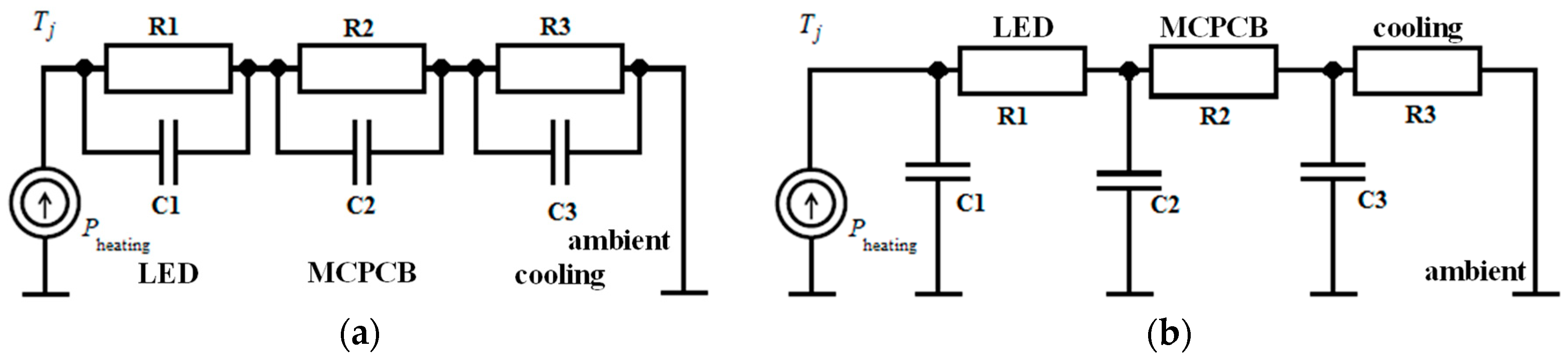

3.2. Compact Thermal Models

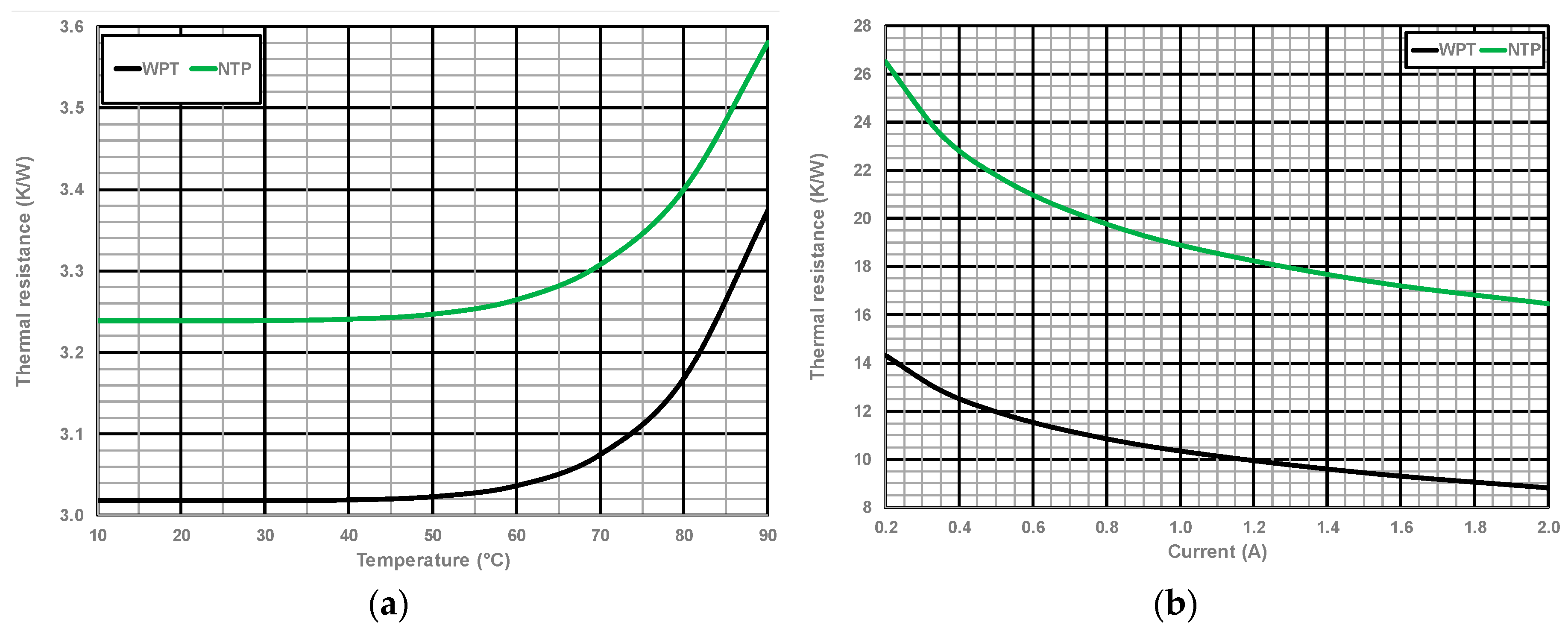

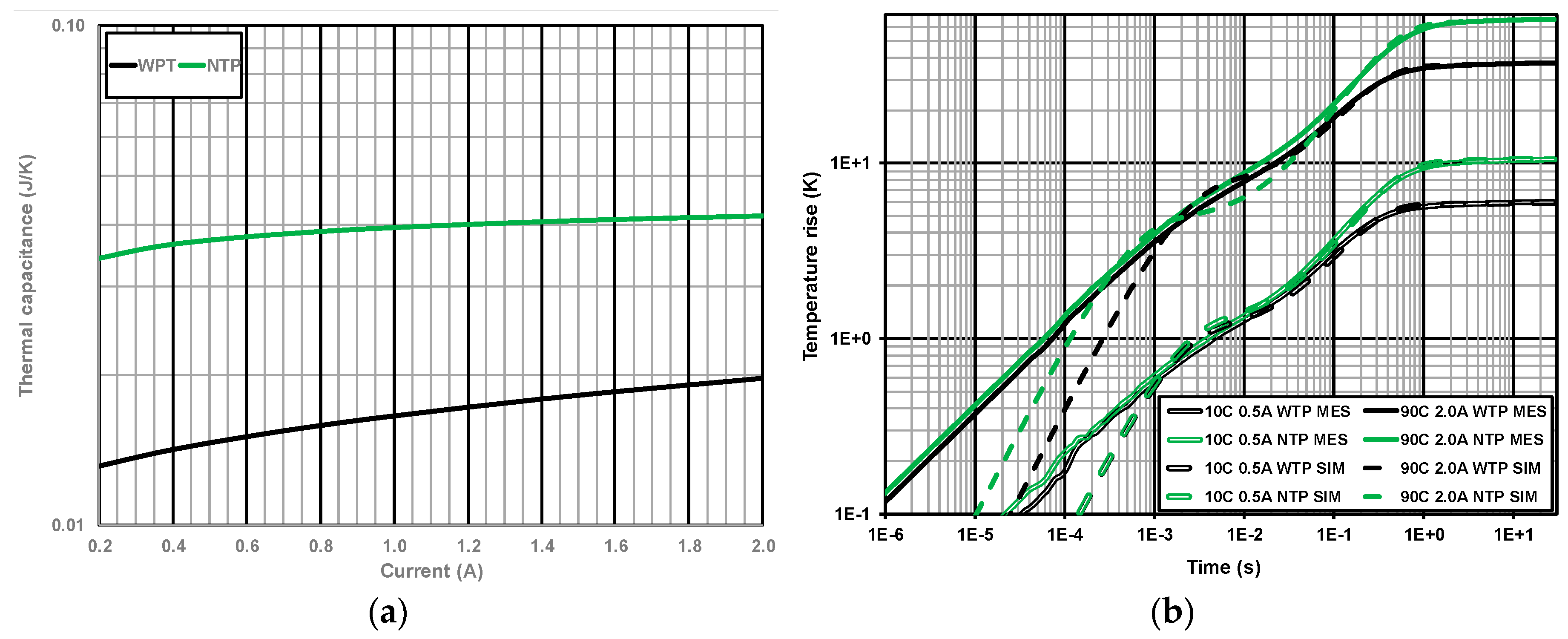

3.3. Parametric Model

3.4. Thermal Simulations

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Weir, B. Driving the 21st century’s lights. IEEE Spectr. 2012, 49, 42–47. [Google Scholar] [CrossRef]

- Schubert, E.F. Light Emitting Diodes, 3rd ed.; Rensselaer Polytechnic Institute: Troy, NY, USA, 2018. [Google Scholar]

- Biber, C. LED Light Emission as A Function of Thermal Conditions. In Proceedings of the 24th IEEE Semiconductor Thermal Measurement and Management Symposium, San Jose, CA, USA, 16–20 March 2008; pp. 180–184. [Google Scholar] [CrossRef]

- Górecki, K.; Ptak, P.; Janicki, M.; Torzewicz, T. Influence of Cooling Conditions of Power LEDs on Their Electrical, Thermal and Optical Parameters. In Proceedings of the 25th International Conference Mixed Design of Integrated Circuits and Systems, Gdynia, Poland, 21–23 June 2018; pp. 237–242. [Google Scholar]

- Lasance, C.J.M.; Poppe, A. (Eds.) Thermal Management for LED Applications; Springer: Dordrecht, Holland, 2014. [Google Scholar]

- Bender, V.C.; Iaronka, O.; Marchesan, T.B. Study on The Thermal Performance of LED Luminaire using Finite Element Method. In Proceedings of the 39th Annual Conference of the IEEE Industrial Electronics Society IECON, Vienna, Austria, 10–13 November 2013; pp. 6099–6104. [Google Scholar] [CrossRef]

- Leng, L.S.; Retnasamy, V.; Sauli, Z.; Vairavan, R.; Shahimin, M.M.; Ong, N.R.; Kirtsaeng, S. Finite Element Modelling of Thermal Performance of LED Lamp using Open Source Software - Salome and Elmer. In Proceedings of the IEEE Symposium on Computer Applications & Industrial Electronics ISCAIE, Langkawi, Malaysia, 24–25 April 2017; pp. 65–68. [Google Scholar] [CrossRef]

- Lee, H.E.; Lee, D.; Lee, T.I.; Shin, J.H.; Choi, G.M.; Kim, C.; Lee, S.H.; Lee, J.H.; Kim, Y.H.; Kang, S.M.; et al. Wireless powered wearable micro light-emitting diodes. Nano Energy 2019, 55, 454–462. [Google Scholar] [CrossRef]

- Tandon, S.; Liu, E.; Zahner, T.; Besold, S.; Kalb, W.; Elger, G. Transient Thermal Simulation of High Power LEDs and Its Challenges. In Proceedings of the 18th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems, Dresden, Germany, 3–5 April 2017; pp. 45–52. [Google Scholar] [CrossRef]

- Sabry, M.N. Compact thermal models for electronic systems. IEEE Trans. Compon. Packag. 2003, 26, 179–185. [Google Scholar] [CrossRef]

- Mawby, P.A.; Igic, P.M.; Towers, M.S. Physically based compact device models for circuit modelling applications. Microelectr. J. 2001, 32, 433–447. [Google Scholar] [CrossRef]

- Menozzi, R.; Cova, P.; Delmonte, N.; Giuliani, F.; Sozzi, G. Thermal and electrothermal modeling of components and systems: Review of the research at the University of Parma. Facta Univ. Ser.: Electron. Energetics 2015, 28, 325–344. [Google Scholar] [CrossRef]

- Lasance, C.J.M. Ten years of BCI compact thermal modeling of electronic parts: Review. Heat Transf. Eng. 2008, 29, 149–168. [Google Scholar] [CrossRef]

- Standard JESD15-4. DELPHI Compact Thermal Model Guideline; JEDEC: Arlington, VA, USA, 2008. [Google Scholar]

- Sofia, J.W. Analysis of thermal transient data with synthesized dynamic models for semiconductor devices. IEEE Trans. Compon. Packag. A 1995, 18, 39–47. [Google Scholar] [CrossRef]

- Masana, F.N. A new approach to the dynamic thermal modelling of semiconductor packages. Microelectron. Reliab. 2001, 41, 901–912. [Google Scholar] [CrossRef]

- Górecki, K. Modelling mutual thermal interactions between power LEDs in SPICE. Microelectron. Reliab. 2015, 55, 389–395. [Google Scholar] [CrossRef]

- Górecki, K.; Ptak, P. Modelling mutual thermal coupling in LED modules. Microelectron. Int. 2015, 32, 152–157. [Google Scholar] [CrossRef]

- Górecki, K.; Ptak, P. Modeling LED lamps in SPICE with thermal phenomena taken into account. Microelectron. Reliab. 2017, 79, 440–447. [Google Scholar] [CrossRef]

- Poppe, A. Simulation of LED based luminaires by using multi-domain compact models of LEDs and compact thermal models of their thermal environment. Microelectron. Reliab. 2017, 72, 65–74. [Google Scholar] [CrossRef]

- Standard JESD51-51. Implementation of the Electrical Test Method for the Measurement of Real Thermal Resistance and Impedance of Light-Emitting Diodes with Exposed Cooling Surface; JEDEC: Arlington, VA, USA, 2012. [Google Scholar]

- Standard JESD51-52. Guidelines for Combining CIE 127-2007 Total Flux Measurement with Thermal Measurement of LED with Exposed Cooling Surface; JEDEC: Arlington, VA, USA, 2012. [Google Scholar]

- Górecki, K.; Ptak, P. Simple Method of Measuring Photometric and Radiometry Parameters of Power LEDs. In Proceedings of the 2018 Baltic URSI Symposium (URSI), Poznan, Poland, 15–17 May 2018; pp. 121–124. [Google Scholar] [CrossRef]

- Standard JESD51-14. Transient Dual Interface Test Method for The Measurement of The Thermal Resistance Junction-to-Case of Semiconductor Devices with Heat Flow through A Single Path; JEDEC: Arlington, VA, USA, 2010. [Google Scholar]

- Szekely, V. A new evaluation method of thermal transient measurement results. Microelectr. J. 1997, 28, 277–292. [Google Scholar] [CrossRef]

- Janicki, M.; Torzewicz, T.; Samson, A.; Raszkowski, T.; Napieralski, A. Experimental identification of LED compact thermal model element values. Microelectron. Reliab. 2018, 86, 20–26. [Google Scholar] [CrossRef]

- Marquardt, D. Algorithm for least-squares estimation of non-linear parameters. SIAM J. Appl. Math. 1963, 11, 431–441. [Google Scholar] [CrossRef]

- Gerstenmaier, Y.C.; Kiffe, W.; Wachutka, G. Combination of Thermal Subsystem Modeled by Rapid Circuit Transformation. In Proceedings of the 13th International Workshop on Thermal Investigation of ICs and Systems, Budapest, Hungary, 17–19 September 2007; pp. 115–120. [Google Scholar] [CrossRef]

- Torzewicz, T.; Ptak, P.; Samson, A.; Raszkowski, T.; Janicki, M.; Górecki, K. Parametric Compact Thermal Modeling of Power LEDs. In Proceedings of the 18th Intersociety Conference on Thermal and Thermo-mechanical Phenomena in Electronic Systems, Las Vegas, NV, USA, 28–31 May 2019. in press. [Google Scholar]

| Thermal Resistances R (K/W) | Thermal Capacitances C (J/K) |

|---|---|

| C1 = 0.00144 | |

| R3 = 0.48 | C3 = 14.71 |

| Thermal Resistances R (K/W) | Thermal Capacitances C (J/K) |

|---|---|

| C1 = 0.002 | |

| R3 = 0.95 | C3 = 7.07 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Janicki, M.; Torzewicz, T.; Ptak, P.; Raszkowski, T.; Samson, A.; Górecki, K. Parametric Compact Thermal Models of Power LEDs. Energies 2019, 12, 1724. https://doi.org/10.3390/en12091724

Janicki M, Torzewicz T, Ptak P, Raszkowski T, Samson A, Górecki K. Parametric Compact Thermal Models of Power LEDs. Energies. 2019; 12(9):1724. https://doi.org/10.3390/en12091724

Chicago/Turabian StyleJanicki, Marcin, Tomasz Torzewicz, Przemysław Ptak, Tomasz Raszkowski, Agnieszka Samson, and Krzysztof Górecki. 2019. "Parametric Compact Thermal Models of Power LEDs" Energies 12, no. 9: 1724. https://doi.org/10.3390/en12091724

APA StyleJanicki, M., Torzewicz, T., Ptak, P., Raszkowski, T., Samson, A., & Górecki, K. (2019). Parametric Compact Thermal Models of Power LEDs. Energies, 12(9), 1724. https://doi.org/10.3390/en12091724