Extraction of Boundary Condition Independent Dynamic Compact Thermal Models of LEDs—A Delphi4LED Methodology

Abstract

:1. Introduction

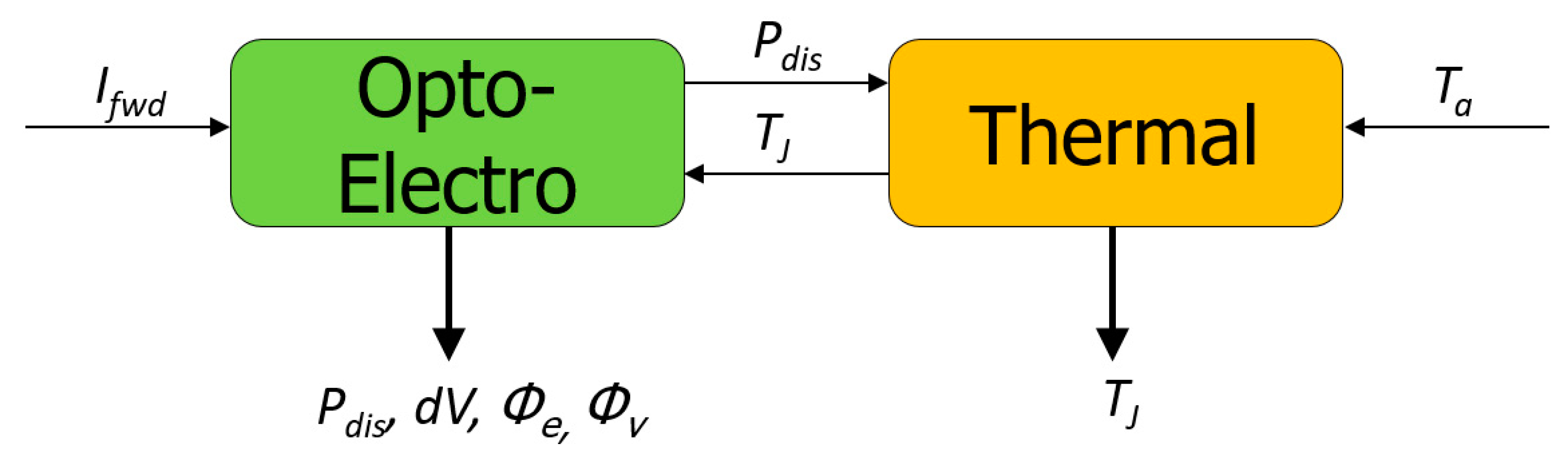

2. Materials and Methods

- Perform thermal measurements of an IC package.

- Calibrate a ‘detailed’ 3D thermal model of the IC package so that it replicates the measurements.

- Simulate the detailed model in several different expected thermal operating environments (peripheral heat transfer coefficient boundary conditions) and note the resulting junction temperatures and surface heat fluxes.

- Propose a CTM nodal network topology with assumed inter-node thermal resistance values.

- Define an objective cost function that quantifies the difference between detailed model and compact model predicted junction temperatures and surface heat fluxes.

- Optimize the CTM thermal resistance values until such time as the objective cost function has been minimized for all heat transfer coefficient conditions.

- Quantify the accuracy of the CTM by validation.

- To accommodate transient effects by the inclusion of thermal capacitances in the CTM network.

- To allow for the possibility of multiple heat sources due to additional phosphor conversion and optical reflection losses.

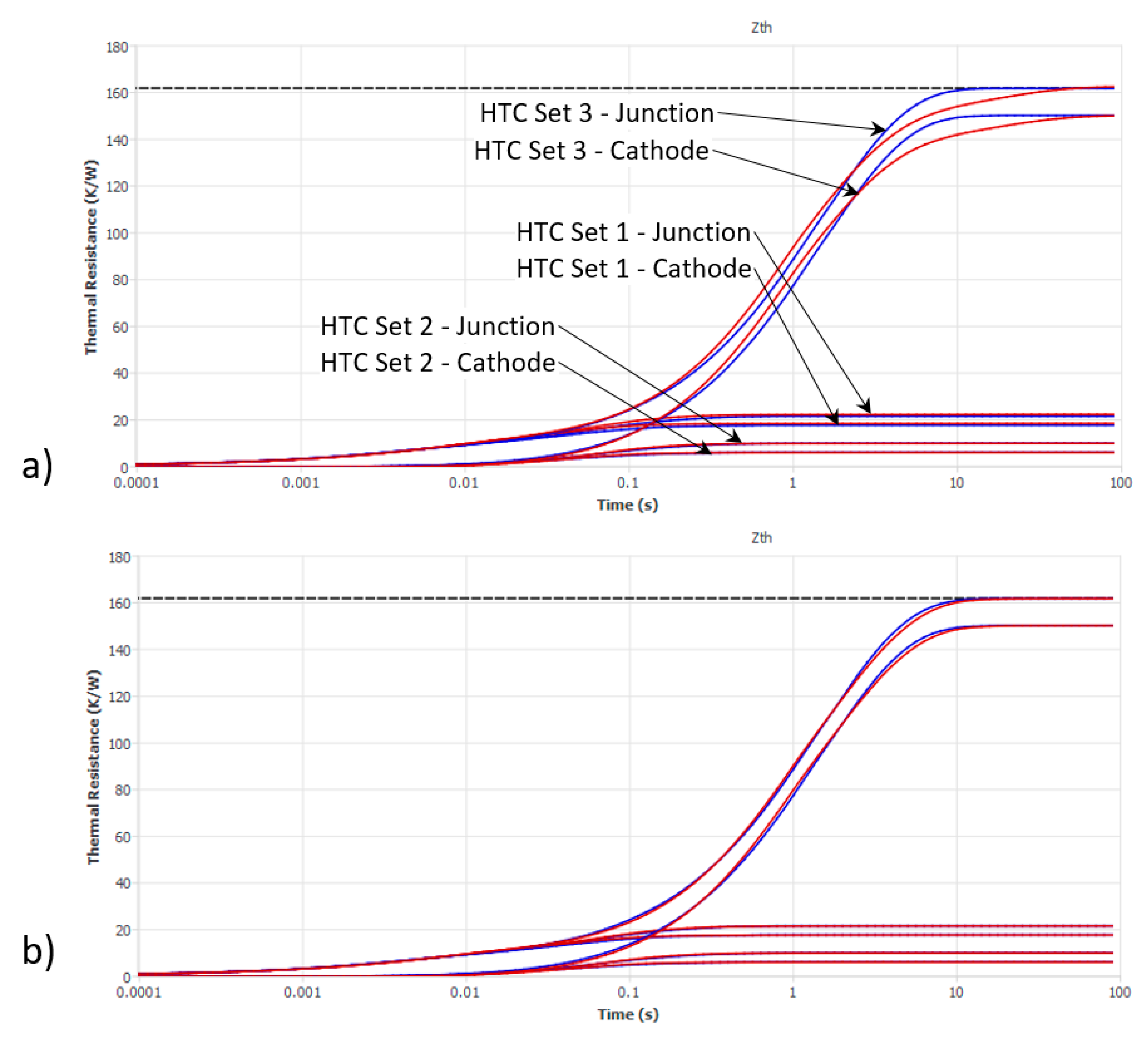

- To consider an objective cost function that quantifies the difference in transient Zth thermal response curves (responses to a step change in power dissipation).

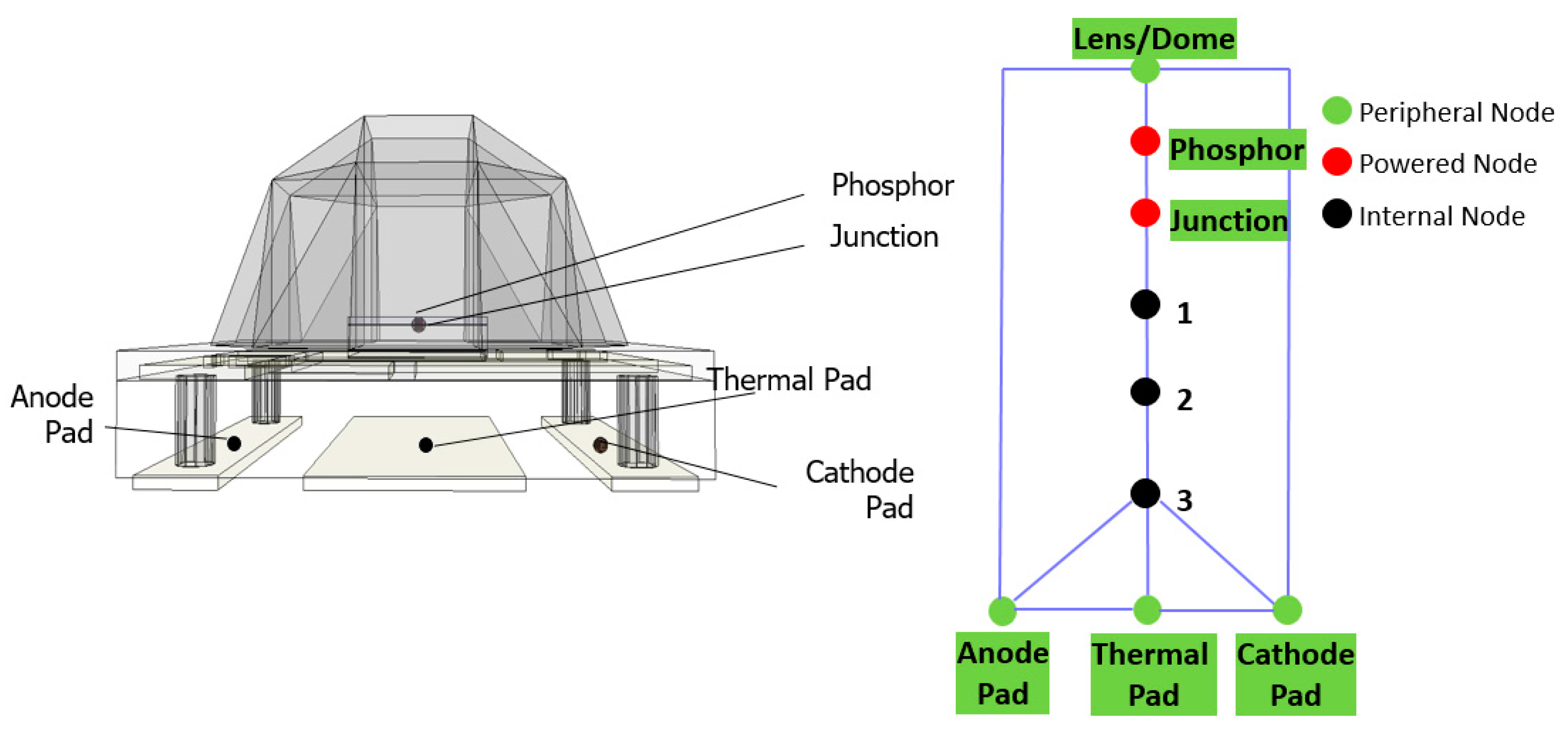

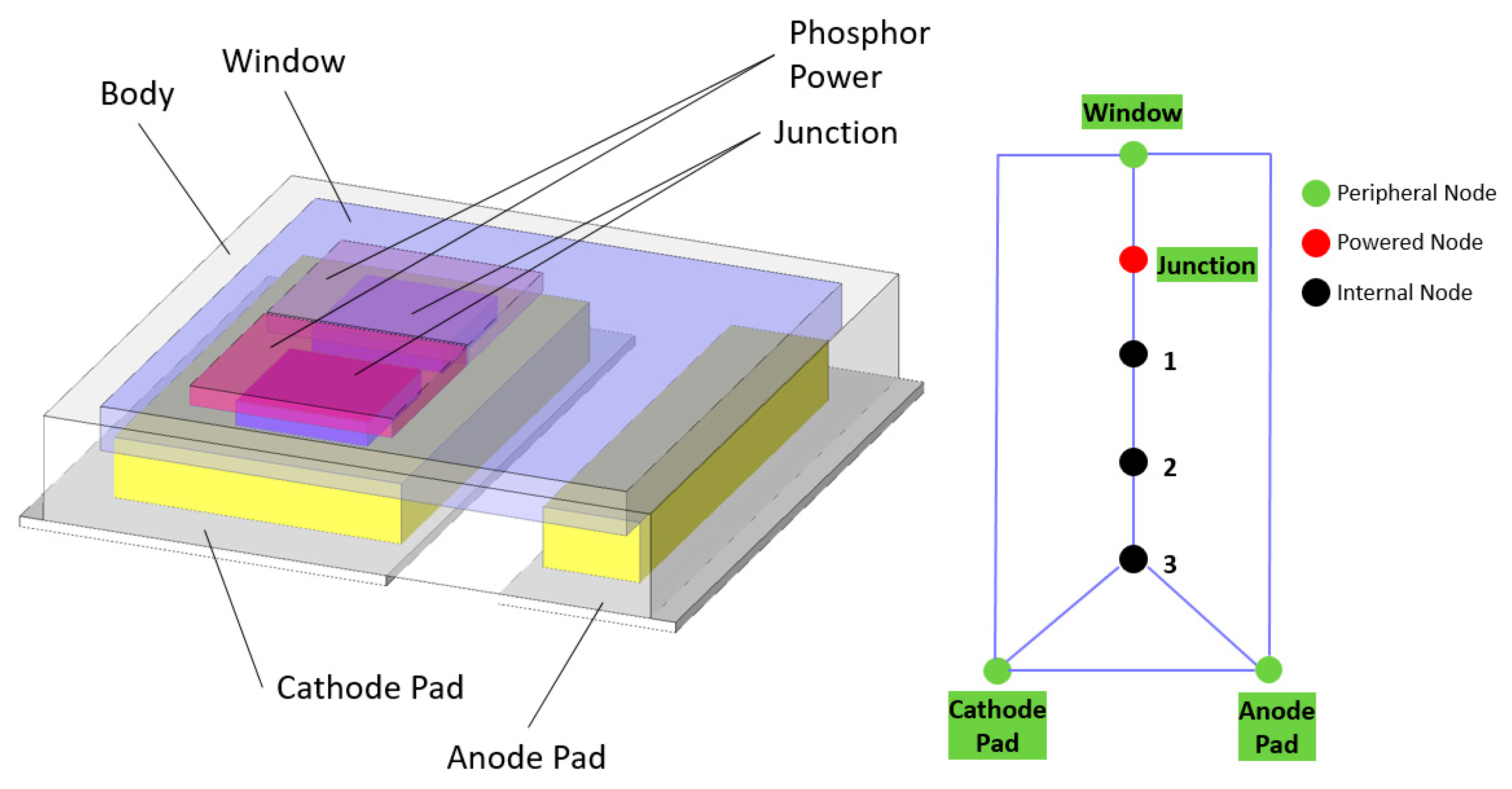

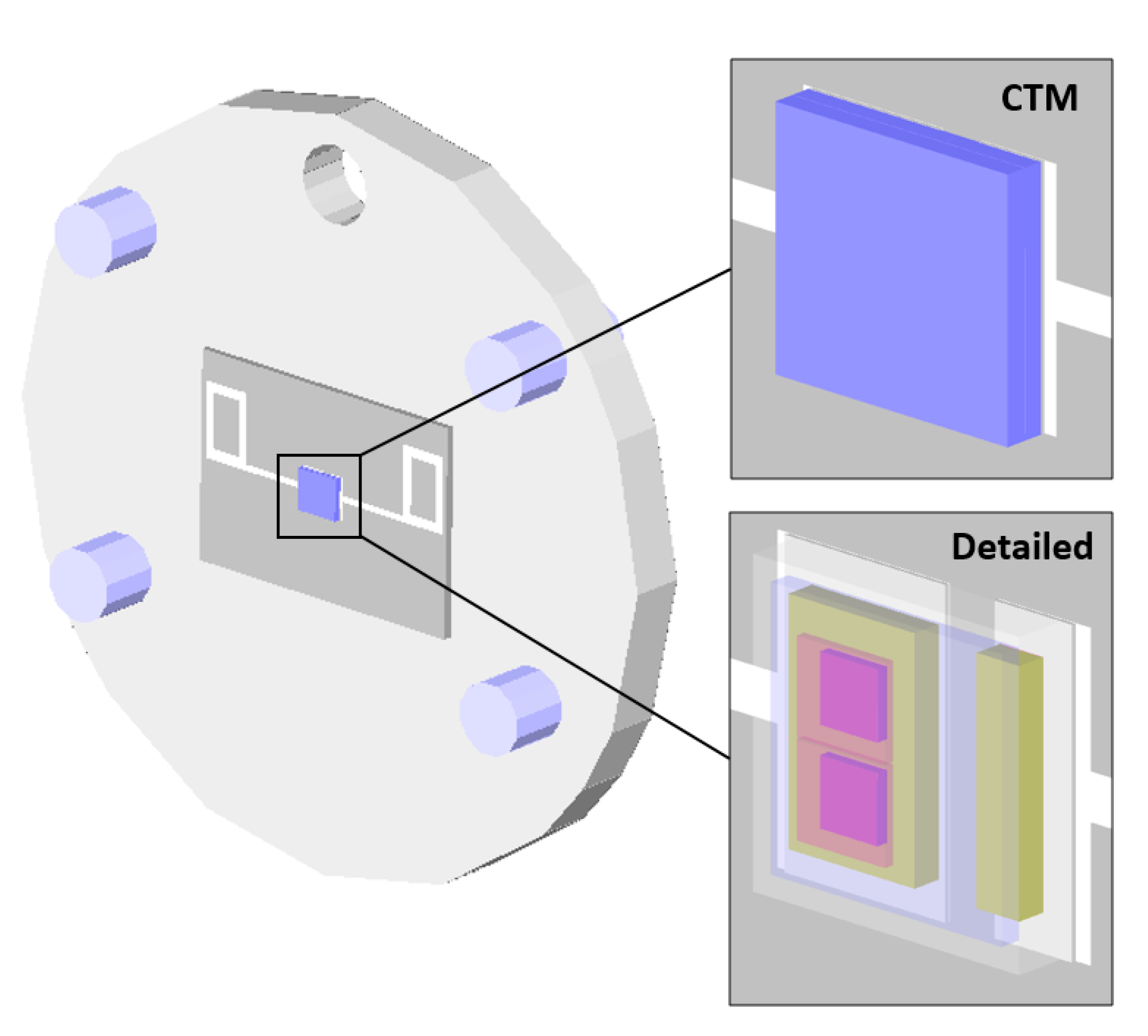

- To propose a nodal network topology that is tailored to and representative of LED devices (Figure 2).

3. Results

3.1. Compact Thermal Model Extraction

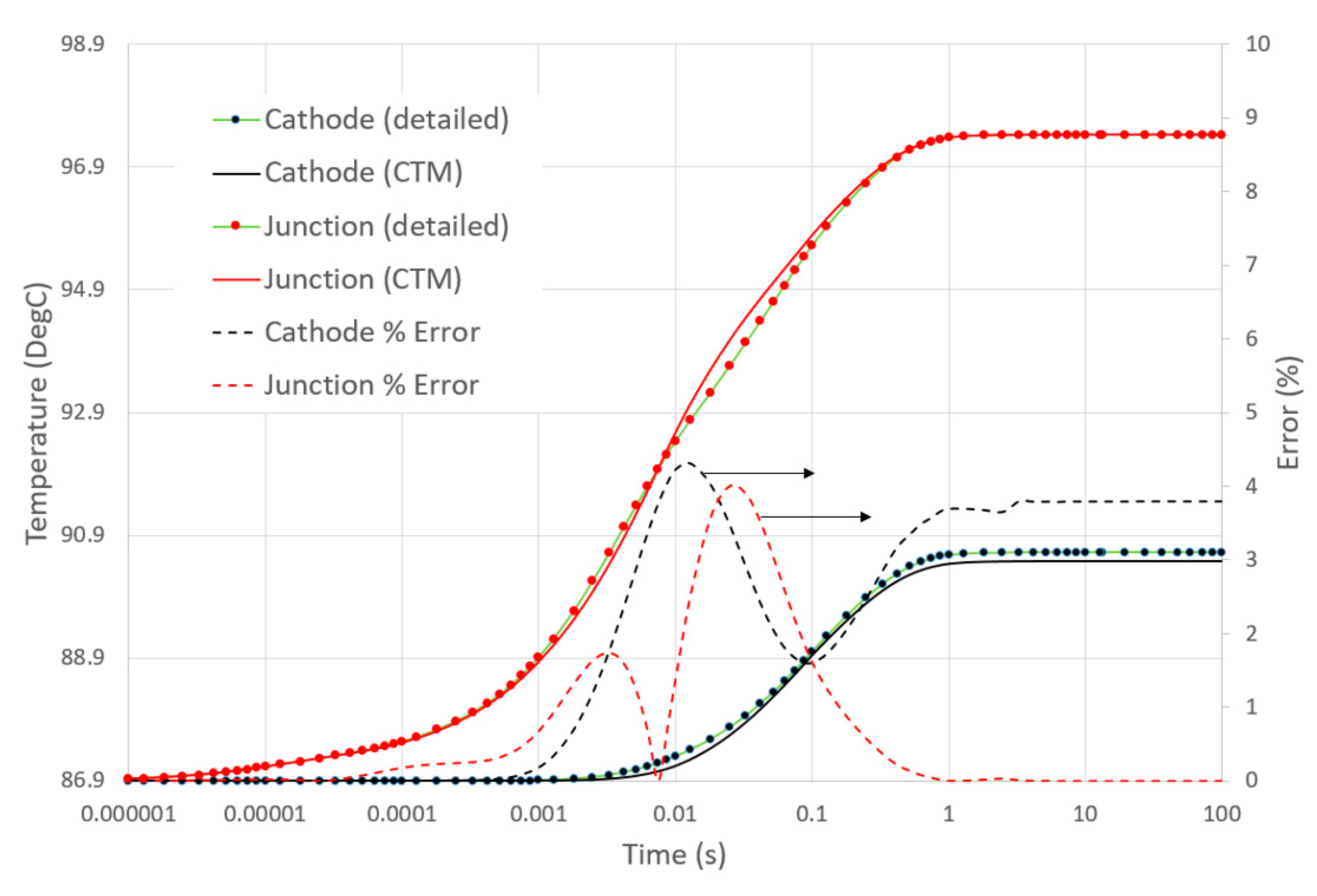

3.2. Validation of the Extracted CTM

4. Discussion

- Having sufficient nodes and inter-nodal resistance links to accommodate changes to the internal heat flow paths that occur due to changes in the peripheral HTCs.

- Having sufficient nodes to accurately discretize the thermal capacitance of those heat flow paths to ensure the correct transient thermal responses.

- Extraction of the CTM using a sufficient number of external HTC boundary condition sets to reflect the potential variation of end-user operating environments.

Funding

Acknowledgments

Conflicts of Interest

Nomenclature

| CFD | computational fluid dynamics |

| CIE | Commission internationale de l’éclairage |

| CTM | compact thermal model |

| HTC | heat transfer coefficient |

| IC | integrated circuit |

| Ifwd | forward current |

| IP | intellectual property |

| JEDEC | Joint Electron Device Engineering Council |

| LED | light emitting diode |

| Pdis | power dissipation |

| Tj | junction temperature |

| Ta | ambient temperature |

| dV | voltage drop |

| Zth | transient thermal impedance curve |

| Φe | emitted optical power |

| Φv | luminous flux |

References

- Lasance, C.J.M.; Rosten, H.I.; Vinke, H.; Weiner, K.-L. A Novel Approach for the Thermal Characterization of Electronic Parts. In Proceedings of the Eleventh IEEE SEMI-THERM Symposium, San Jose, CA, USA, 7–9 February 1995. [Google Scholar]

- Rosten, H.; Parry, J.; Lasance, C.J.M.; Vinke, H.; Temmerman, W.; Nelemans, W.; Assouad, Y.; Gautier, T.; Slattery, O.; Cahill, C.; et al. Final Report to SEMI-THERM XIII on the European-Funded Project DELPHI—The Development of Libraries and Physical Models for an Integrated Design Environment. In Proceedings of the Thirteenth IEEE SEMI-THERM Symposium, Austin, TX, USA, 28–30 January 1997. [Google Scholar]

- Rosten, H.; Lasance, C.J.M.; Parry, J. The World of Thermal Characterization According to DELPHI—Part I: Background to DELPHI. IEEE Trans. CHMT 1997, 20, 384–391. [Google Scholar] [CrossRef]

- Bornoff, R.; Hildenbrand, V.; Lugten, S.; Martin, G.; Marty, C.; Poppe, A.; Rencz, M.; Schilders, W.; Yu, J. Delphi4LED—From Measurements to Standardized Multi-Domain Compact Models of LEDs: A New European R&D Project for Predictive and Efficient Multidomain Modeling and Simulation of LEDs at all Integration Levels Along the SSL Supply Chain. In Proceedings of the Therminic 2016, Budapest, Hungary, 21–23 September 2016. [Google Scholar]

- Poppe, A. Simulation of LED Based Luminaires by Using Multi-Domain Compact Models of LEDs and Compact Thermal Models of their Thermal Environment. Microelectron. Reliab. 2017, 72, 65–74. [Google Scholar] [CrossRef]

- Farkas, G.; Gaál, L.; Bein, M.; Poppe, A.; Ress, S.; Rencz, M. LED Characterization within the Delphi4LED Project. In Proceedings of the ITHERM’18, San Diego, CA, USA, 29 May–1 June 2018; p. 393. [Google Scholar]

- Farkas, G.; Gaál, L.; Poppe, A.; Rencz, M.; Bornoff, R. LED multiphysics modeling for “Industry 4.0”, an approach proposed by the Delphi4LED European project. In Proceedings of the 2018 IEEE Electronics Packaging Technology Conference (EPTC), Singapore, 4–7 December 2018; p. 268. [Google Scholar]

- Farkas, G.; Poppe, A.; Gaál, L.; Hantos, G.; Berényi, C.; Rencz, M. Structural analysis and modelling of packaged light emitting devices by thermal transient measurements at multiple boundaries. In Proceedings of the 24th International Workshop on THERMal INvestigation of ICs and Systems (THERMINIC 2018), Stockholm, Sweden, 26–28 September 2018; p. 152. [Google Scholar]

- Bornoff, R.; Farkas, G.; Gaal, L.; Rencz, M.; Poppe, A. LED 3D thermal model calibration against measurement. In Proceedings of the 2018 19th International Conference on Thermal Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE) Toulouse, Toulouse, France, 15–18 April 2018; pp. 1–7. [Google Scholar]

- Van Bien, T.; Szekely, V. Fine structure of heat flow path in semiconductor devices: A measurement and identification method. Solid State Electron. 1988, 31, 1363–1368. [Google Scholar]

- Technical Specifications. Available online: https://www.mentor.com/products/mechanical/flotherm/flotherm/technical-specifications (accessed on 21 April 2019).

- Alexeev, A.; Martin, G.; Onushkin, G.; Linnartz, J. Accurate Thermal Transient Measurements Interpretation of Monochromatic LEDs. In Proceedings of the Thirty Fifth IEEE SEMI-THERM Symposium, San Jose, CA, USA, 18–22 March 2019. [Google Scholar]

- Marty, C.; Poppe, A.; Martin, G. LED Luminaire Design Using Virtual Twin: Development of a Multidomain Compact Model in the Delphi4LED European Project. In Proceedings of the Strategies in Light, Las Vegas, NV, USA, 27 February–1 March 2019. [Google Scholar]

- Codecasa, L.; d’Alessandro, V.; Magnani, A.; Rinaldi, N. Matrix Reduction Tool for Creating Boundary Condition Independent Dynamic Compact Thermal Models. In Proceedings of the 21st International Workshop on Thermal Investigations of ICs and Systems (THERMINIC 2015), Paris, France, 30 September–2 October 2015. [Google Scholar]

- Sabry, M.N. Dynamic Compact Thermal Models Used for Electronic Design: A Review of Recent Progress. In Proceedings of the Interpack, Maui, HI, USA, 6–11 July 2003. [Google Scholar]

| W/m2K | HTC Set 1 | HTC Set 2 | HTC Set 3 |

|---|---|---|---|

| Anode | 6000 | 5000 | 200 |

| Cathode | 30,000 | 50,000 | 2000 |

| From Node | To Node | Thermal Resistance (K/W) |

|---|---|---|

| Junction | 1 | 0.6593 |

| 1 | 2 | 1.8364 |

| 2 | 3 | 4.2061 |

| 3 | Cathode | 5.0598 |

| 3 | Anode | 351.1 |

| Cathode | Anode | 12549 |

| Junction | Window | 8799 |

| Window | Cathode | 5000 |

| Window | Anode | 9969 |

| Node | Thermal Capacitance (J/K) |

|---|---|

| Junction | 1.673 × 10−5 |

| 1 | 0.0001639 |

| 2 | 0.000268 |

| 3 | 0.00075 |

| Cathode | 0.00588 |

| Anode | 0.0025 |

| Window | 0.0005 |

© 2019 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bornoff, R. Extraction of Boundary Condition Independent Dynamic Compact Thermal Models of LEDs—A Delphi4LED Methodology. Energies 2019, 12, 1628. https://doi.org/10.3390/en12091628

Bornoff R. Extraction of Boundary Condition Independent Dynamic Compact Thermal Models of LEDs—A Delphi4LED Methodology. Energies. 2019; 12(9):1628. https://doi.org/10.3390/en12091628

Chicago/Turabian StyleBornoff, Robin. 2019. "Extraction of Boundary Condition Independent Dynamic Compact Thermal Models of LEDs—A Delphi4LED Methodology" Energies 12, no. 9: 1628. https://doi.org/10.3390/en12091628

APA StyleBornoff, R. (2019). Extraction of Boundary Condition Independent Dynamic Compact Thermal Models of LEDs—A Delphi4LED Methodology. Energies, 12(9), 1628. https://doi.org/10.3390/en12091628