An Innovative Dual-Boost Nine-Level Inverter with Low-Voltage Rating Switches

Abstract

1. Introduction

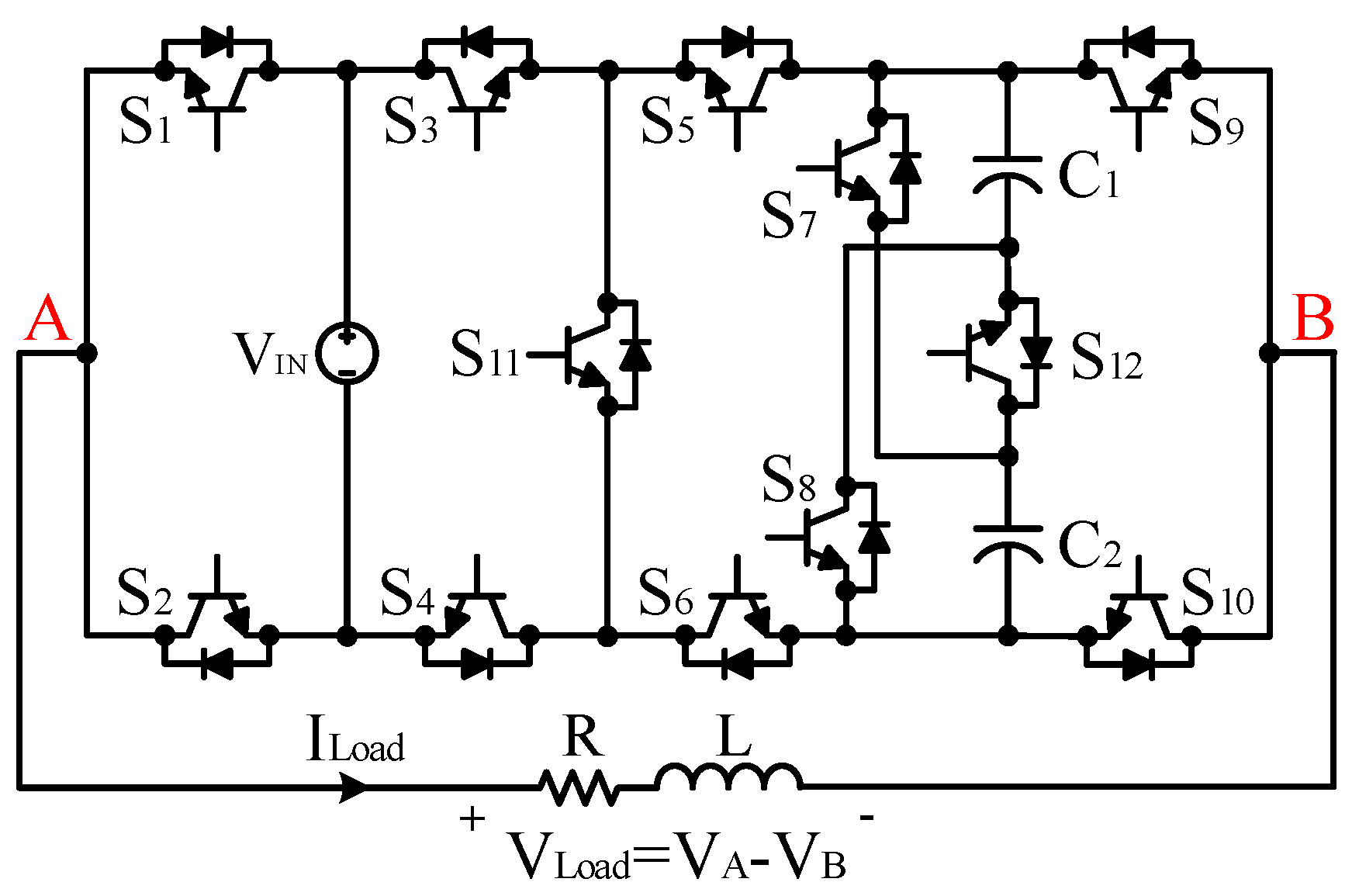

2. Analysis of the Proposed Nine-Level Inverter

2.1. Circuit Description

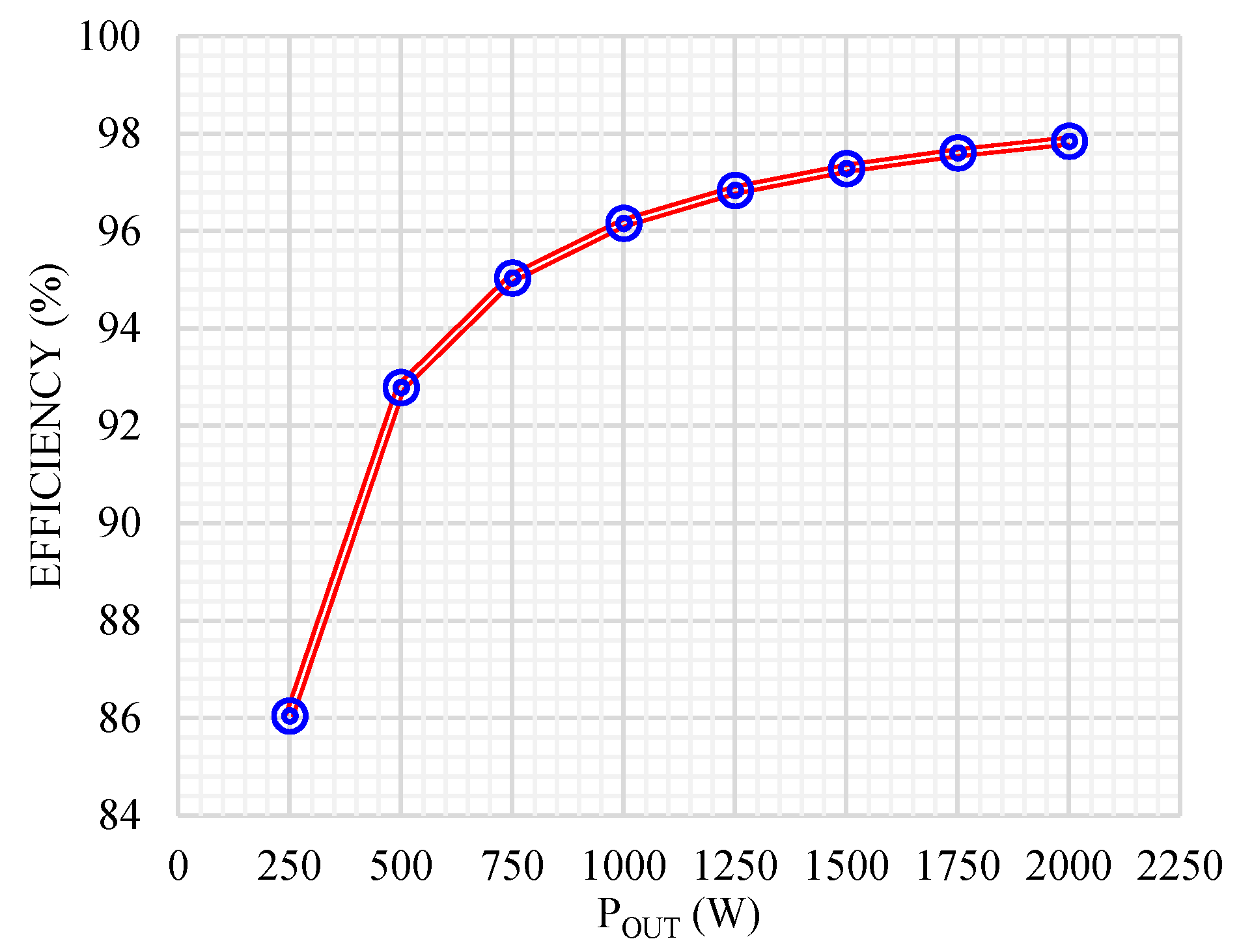

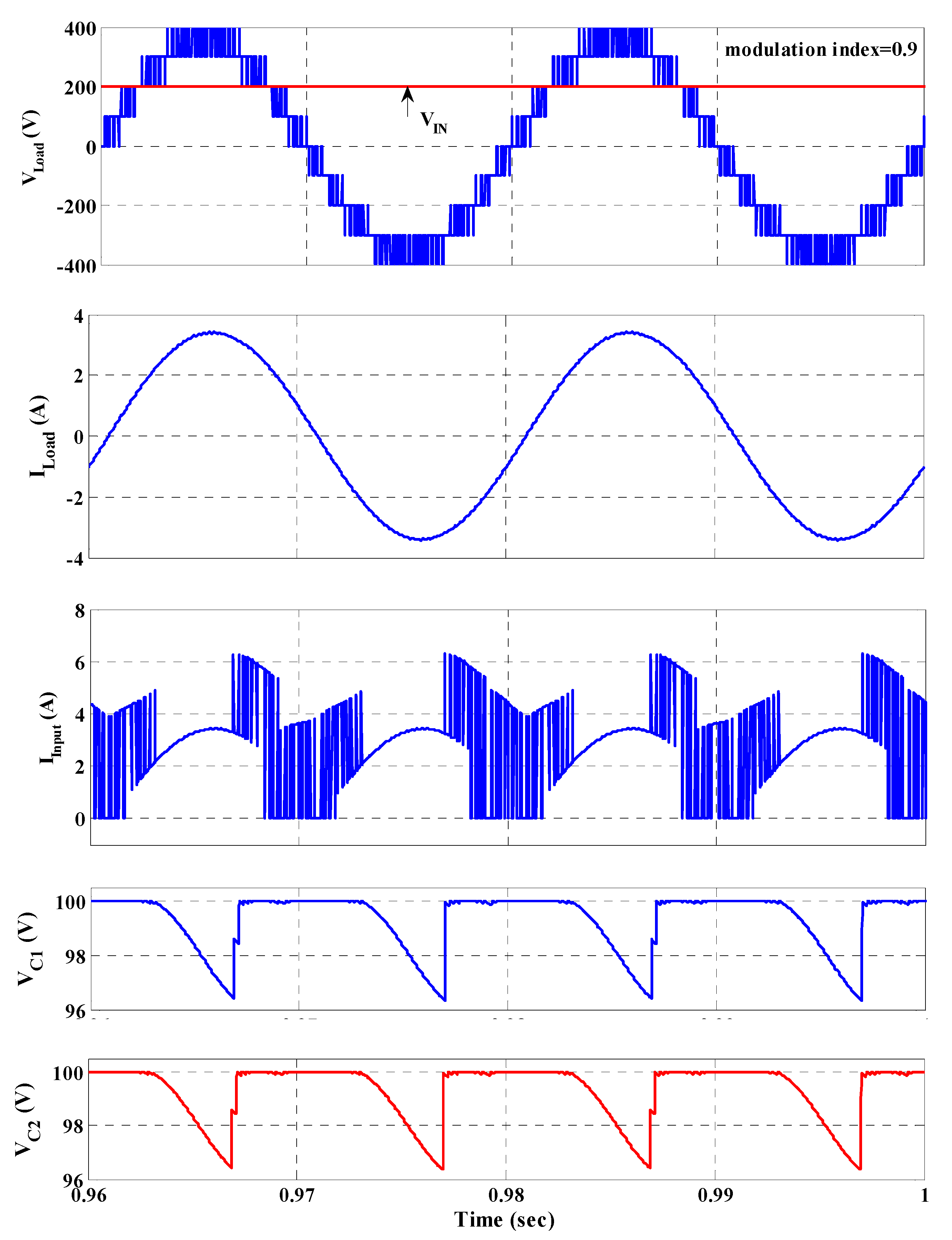

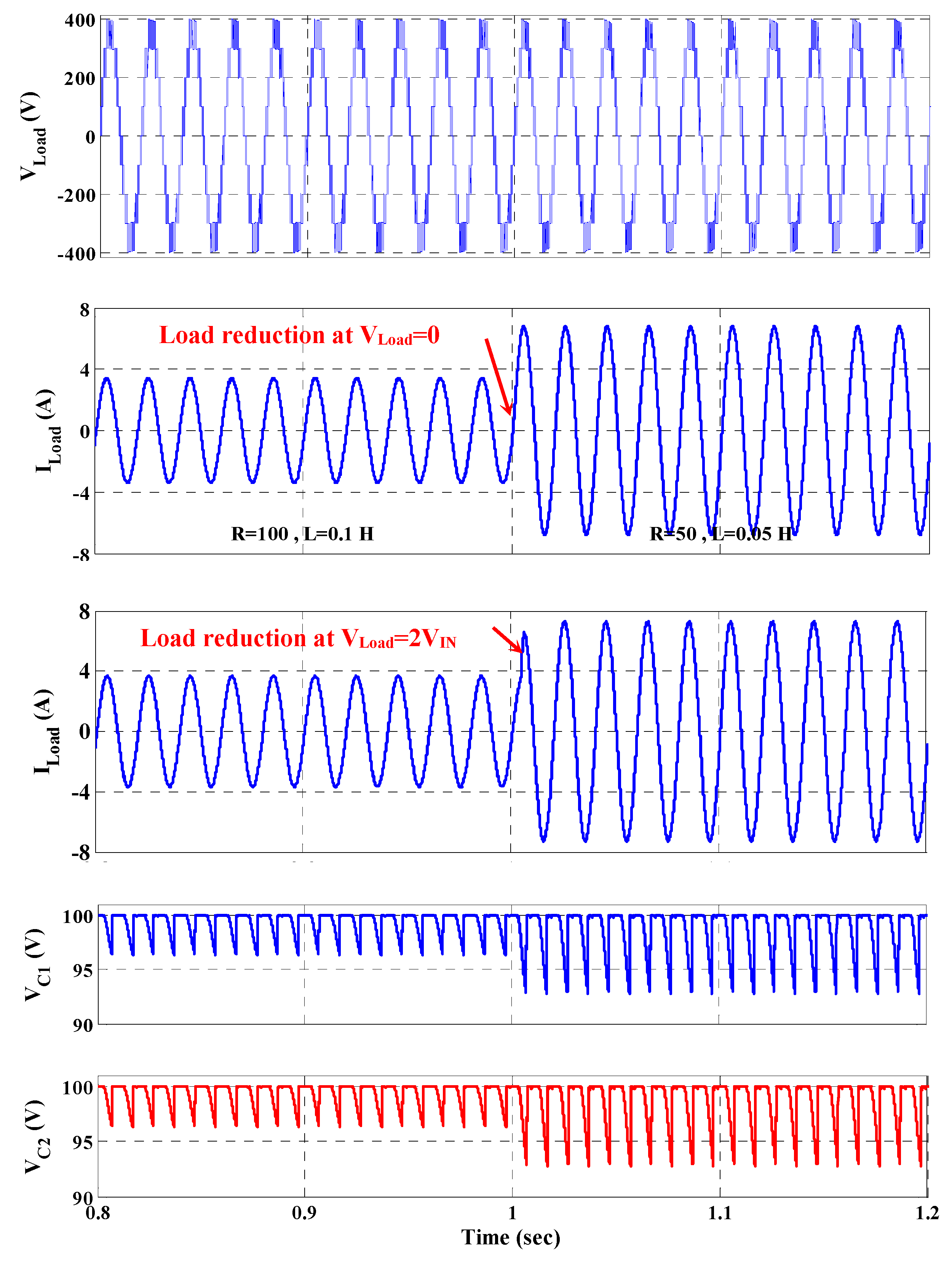

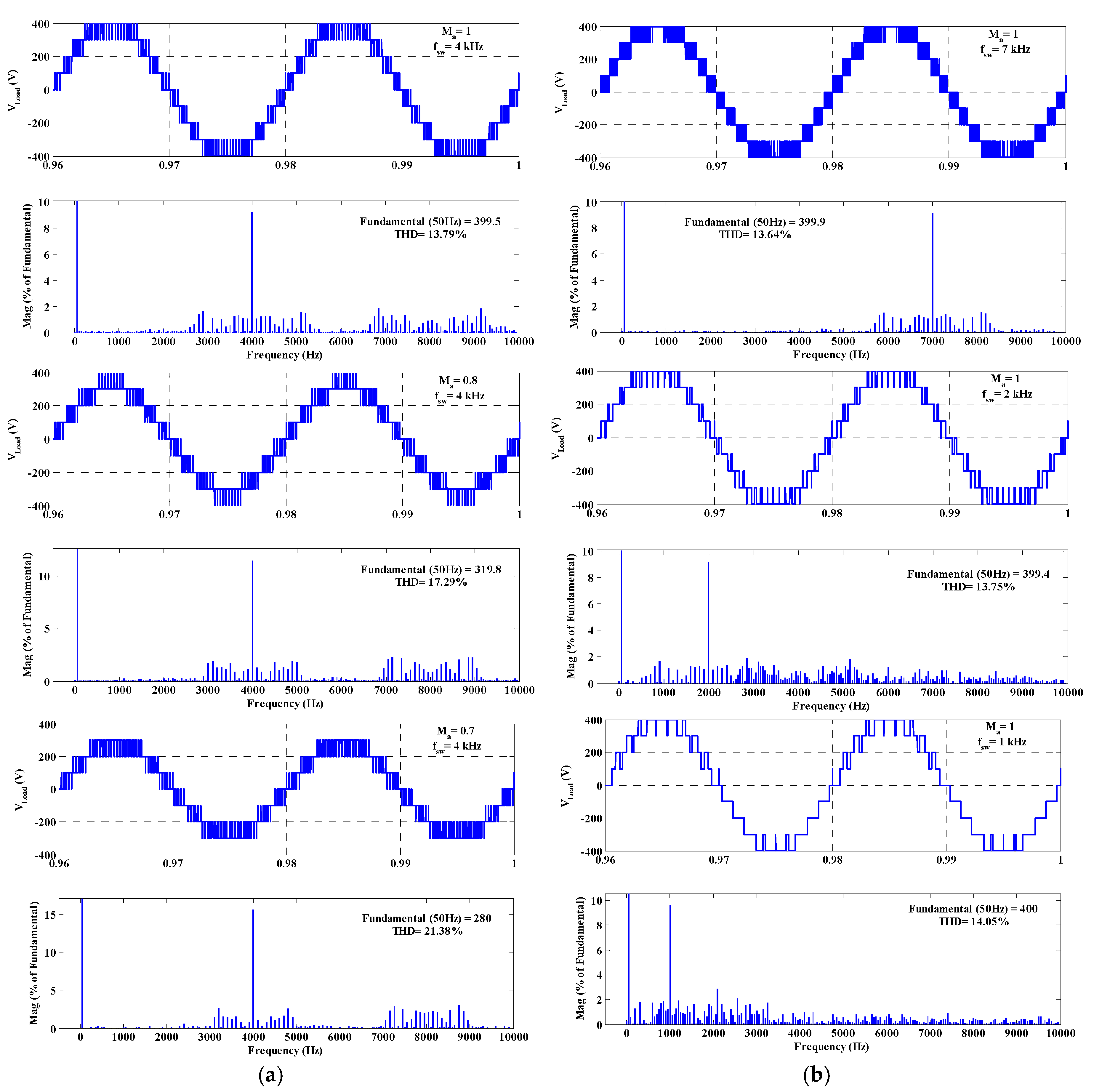

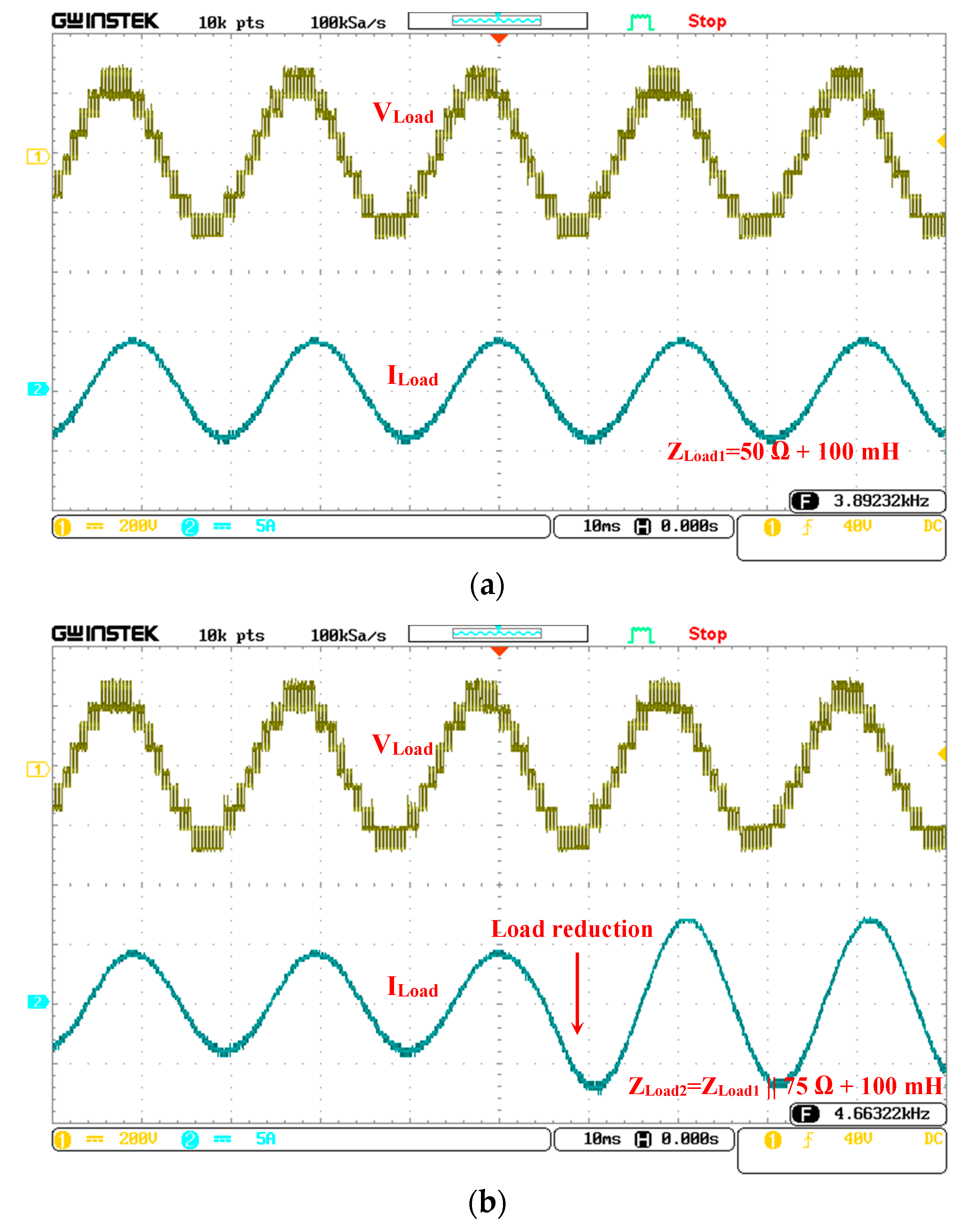

2.2. Comparative Assessment

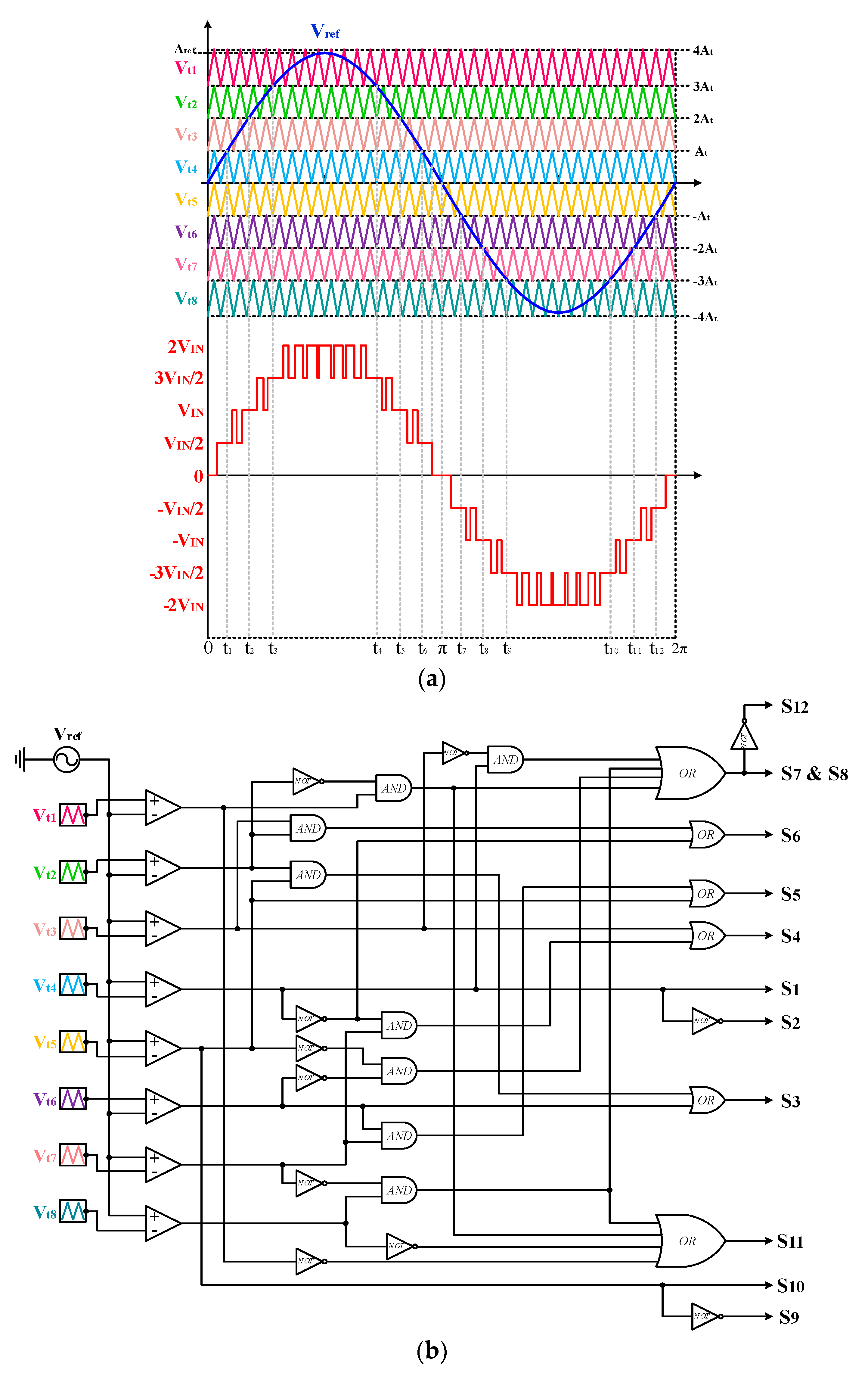

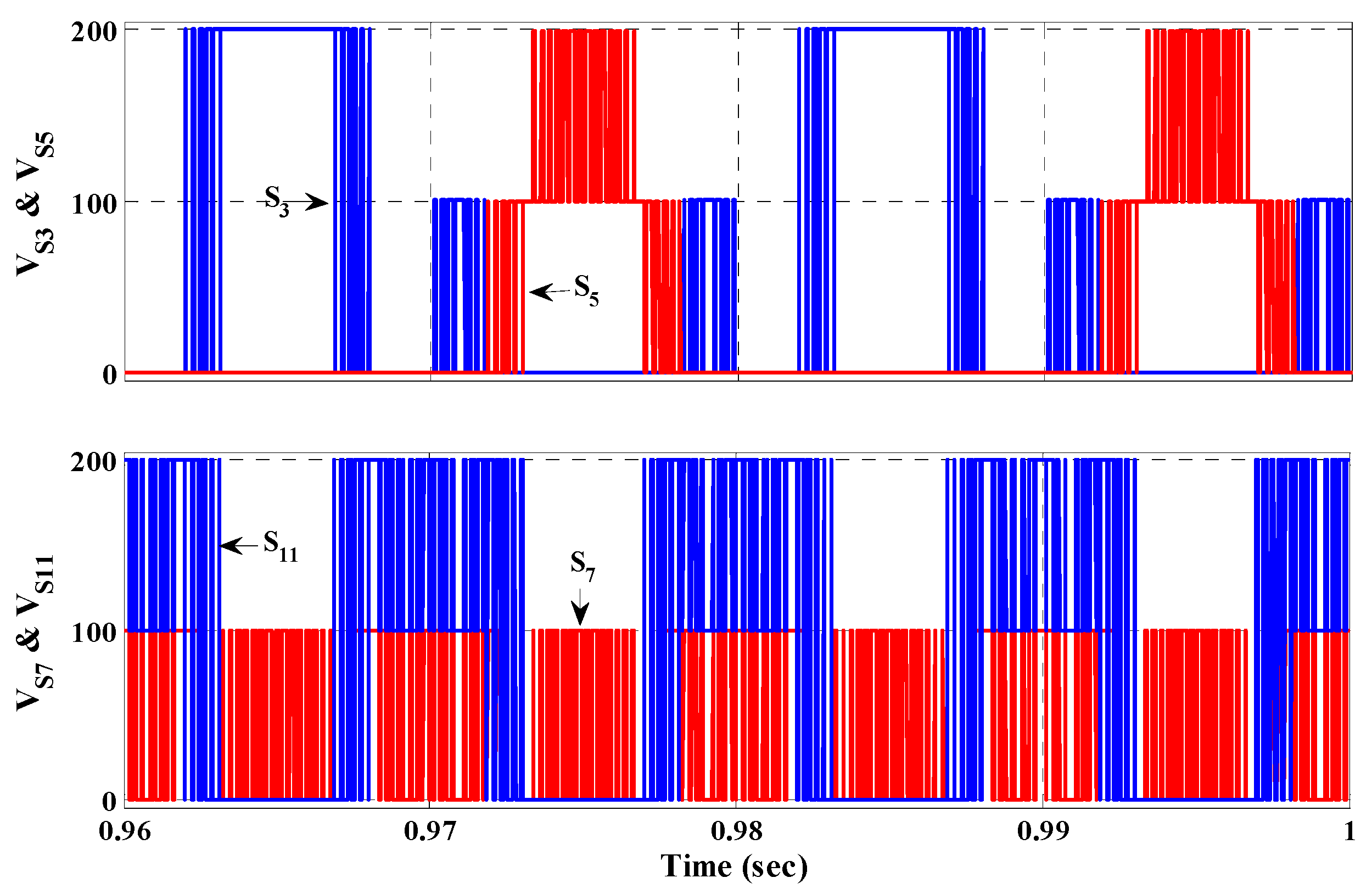

3. Multicarrier PWM Strategy

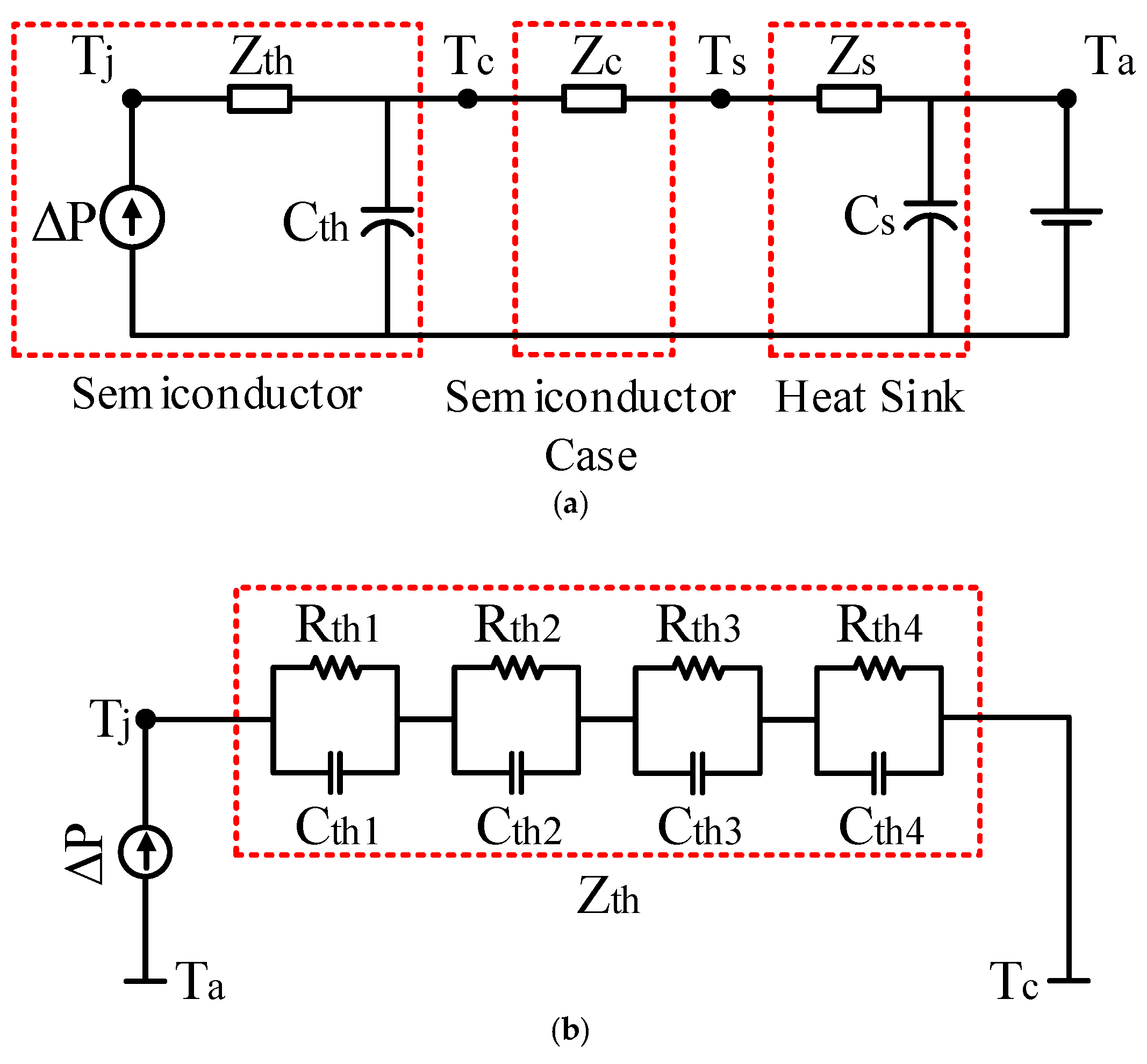

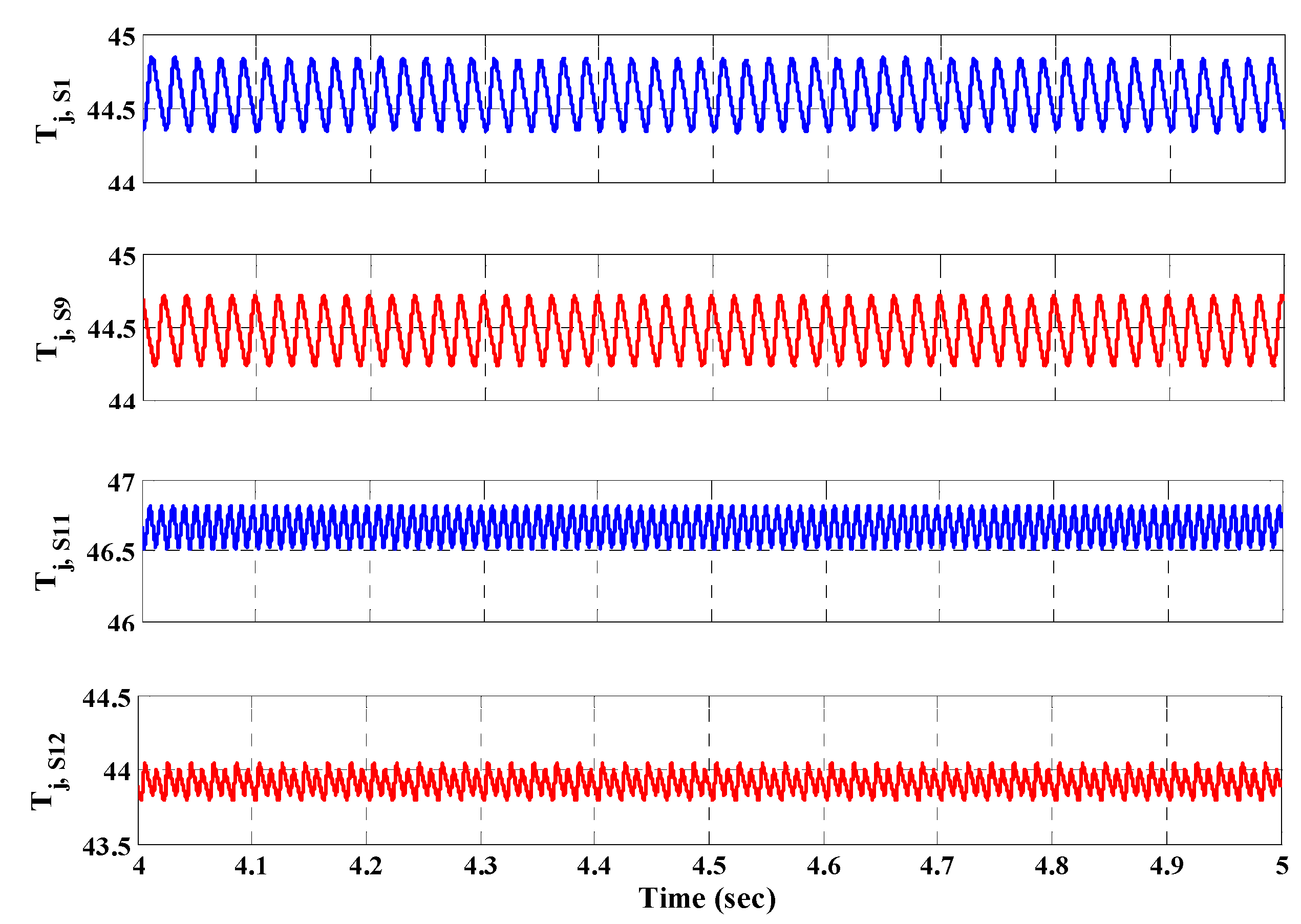

4. Loss Distribution and Thermal Modeling

4.1. Power Loss Analysis

4.1.1. Conduction Loss (PC)

4.1.2. Switching Loss (PS)

4.1.3. Power Loss Generated by Capacitor Voltage Ripple (PR)

4.2. Thermal Model

5. Simulation and Experimental Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

Nomenclature

| MLIs | Multilevel inverters |

| CHB | Cascaded H-bridge |

| NPC | Neutral point clamped |

| FC | Flying capacitor |

| TSV | Total standing voltage (V) |

| PIV | Peak inverse voltage (V) |

| PWM | Pulse width modulation |

| DSP | Digital signal processor |

| VIN and IIN | Input voltage (V) and current (A) of the inverter |

| VLoad and ILoad | Maximum load voltage (V) and current (A) |

| Vt | Triangular carrier of the PWM modulation |

| Vref | Reference waveform of the PWM modulation |

| VS and IS | Voltage (V) and current (A) of the switch S |

| ΔVripple | Voltage ripple across each capacitor (V) |

| ΔQC | Maximum discharging value of the capacitor C |

| N | Number of power switches with the same PIV |

| M | Number of cascaded modules |

| At and ft | Amplitude and frequency of the triangular carriers (Vt) |

| Aref and fref | Amplitude and frequency of the reference waveform (Vref) |

| PC | Conduction loss (W) |

| PS | Switching loss (W) |

| PR | Power loss caused by capacitor voltage ripple (W) |

| PS, on and PS, off | Turn-on and turn-off power loss of the switch S (W) |

| Pout | Inverter output power (W) |

| RS and RD | ON-state resistance of the switch S and its parallel diode (Ω) |

| RC | Capacitor internal resistance (Ω) |

| Req | Equivalent value of the parasitic resistance in each voltage level (Ω) |

| R and L | Resistance (Ω) and inductance (H) of the load |

| ton and toff | Rise and fall times of the switch S (s) |

| fS | Switching frequency (Hz) |

| Tj | Semiconductor junction temperature (°C) |

| Tc | Semiconductor case temperature (°C) |

| Ts | Heat sink temperature (°C) |

| Ta | Ambient temperature (°C) |

| Zth | Thermal impedance between junction and case of the semiconductor |

| Zc | Thermal impedance between semiconductor case and its heat sink |

| Zs | Thermal impedance between heat sink and ambient |

References

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Yuan, X. Derivation of Voltage Source Multilevel Converter Topologies. IEEE Trans. Ind. Electron. 2017, 64, 966–976. [Google Scholar] [CrossRef]

- Rodriguez, J.; Franquelo, L.G.; Kouro, S.; Leon, J.I.; Portillo, R.C.; Prats, M.A.M.; Perez, M.A. Multilevel Converters: An Enabling Technology for High-Power Applications. Proc. IEEE 2009, 97, 1786–1817. [Google Scholar] [CrossRef]

- Gupta, K.K.; Ranjan, A.; Bhatnagar, P.; Kumar Sahu, L.; Jain, S. Multilevel Inverter Topologies with Reduced Device Count: A Review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar] [CrossRef]

- Leon, J.I.; Vazquez, S.; Franquelo, L.G. Multilevel Converters: Control and Modulation Techniques for Their Operation and Industrial Applications. Proc. IEEE 2017, 105, 2066–2081. [Google Scholar] [CrossRef]

- Akagi, H. Multilevel Converters: Fundamental Circuits and Systems. Proc. IEEE 2017, 105, 2048–2065. [Google Scholar] [CrossRef]

- Wu, B.; Narimani, M. Diode-Clamped Multilevel Inverters. In High-Power Converters and AC Drives; Wiley-IEEE Press: New York, NY, USA, 2017. [Google Scholar]

- Khounjahan, H.; Abapour, M.; Zare, K. Switched-Capacitor Based Single Source Cascaded H-bridge Multilevel Inverter Featuring Boosting Ability. IEEE Trans. Power Electron. 2018, 34, 1113–1124. [Google Scholar] [CrossRef]

- Lee, S. Single-Stage Switched-Capacitor Module (S3CM) Topology for Cascaded Multilevel Inverter. IEEE Trans. Power Electron. 2018, 33, 8204–8207. [Google Scholar] [CrossRef]

- Choi, J.S.; Kang, F.S. Seven-Level PWM Inverter Employing Series-Connected Capacitors Paralleled to a Single DC Voltage Source. IEEE Trans. Ind. Electron. 2015, 62, 3448–3459. [Google Scholar]

- Hinago, Y.; Koizumi, H. A Switched-Capacitor Inverter Using Series/Parallel Conversion. IEEE Int. Symp. Circuits Syst. 2010, 62, 3188–3191. [Google Scholar]

- Wang, K.; Zheng, Z.; Wei, D.; Fan, B.; Li, Y. Topology and Capacitor Voltage Balancing Control of a Symmetrical Hybrid Nine-Level Inverter for High-Speed Motor Drives. IEEE Trans. Ind. Appl. 2017, 53, 5563–5572. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A Self-Balanced Step-Up Multilevel Inverter Based on Switched-Capacitor Structure. IEEE Trans. Power Electron. 2018, 33, 199–209. [Google Scholar] [CrossRef]

- Lee, S.S.; Sidorov, M.; Lim, C.S.; Idris, N.R.N.; Heng, Y.E. Hybrid Cascaded Multilevel Inverter (HCMLI) With Improved Symmetrical 4-level Submodule. IEEE Trans. Power Electron. 2018, 33, 932–935. [Google Scholar] [CrossRef]

- Lee, S.S. A Single-Phase Single-Source 7-Level Inverter with Triple Voltage Boosting Gain. IEEE Access 2018, 6, 30005–30011. [Google Scholar] [CrossRef]

- McGrath, B.P.; Holmes, D.G. Multicarrier PWM Strategies for Multilevel Inverters. IEEE Trans. Ind. Electron. 2002, 49, 858–867. [Google Scholar] [CrossRef]

- Mei, J.; Xiao, B.; Shen, K.; Tolbert, L.M.; Zheng, J.Y. Modular Multilevel Inverter with new Modulation Method and its Application to Photovoltaic Grid-Connected Generator. IEEE Trans. Power Electron. 2013, 28, 5063–5073. [Google Scholar] [CrossRef]

- Tsunoda, A.; Hinago, Y.; Koizumi, H. Level-and Phase-Shifted PWM for Seven-Level Switched-Capacitor Inverter Using Series/Parallel Conversion. IEEE Trans. Ind. Electron. 2014, 61, 4011–4021. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Moradzadeh, M.; Zamiri, E.; Kojabadi, H.M.; Blaabjerg, F. A new Boost Switched-Capacitor Multilevel Converter with Reduced Circuit Devices. IEEE Trans. Power Electron. 2018, 33, 6738–6754. [Google Scholar] [CrossRef]

- Albarbar, A.; Batunlu, C. Thermal Analysis of Power Electronic Devices Used in Renewable Energy Systems; Springer-Cham: Cham, Switzerland, 2018. [Google Scholar]

- Ma, K.; Muñoz-Aguilar, R.S.; Rodriguez, P.; Blaabjerg, F. Thermal and Efficiency Analysis of Five-Level Multilevel-Clamped Multilevel Converter Considering Grid Codes. IEEE Trans. Ind. Appl. 2014, 50, 415–423. [Google Scholar]

- Lixiang, W.; McGuire, J.; Lukaszewski, R.A. Analysis of PWM Frequency Control to Improve the Lifetime of PWM Inverter. IEEE Trans. Ind. Electron. 2011, 47, 922–929. [Google Scholar] [CrossRef]

- Ma, K.; Bahman, A.S.; Beczkowski, S.; Blaabjerg, F. Complete Loss and Thermal Model of Power Semiconductors Including Device Rating Information. IEEE Trans. Power Electron. 2015, 30, 2556–2569. [Google Scholar] [CrossRef]

- Rajapakse, A.; Gole, A.; Jayasinghe, R. An Improved Representation of FACTS Controller Semiconductor Losses in EMTP-Type Programs Using Accurate Loss-Power Injection Into Network Solution. IEEE Trans. Power Del. 2009, 24, 381–389. [Google Scholar] [CrossRef]

- Tu, Q.; Xu, Z. Power Losses Evaluation for Modular Multilevel Converter with Junction Temperature Feedback. In Proceedings of the IEEE Power and Energy Society General Meeting, Detroit, MI, USA, 24–29 July 2011; pp. 1–7. [Google Scholar]

| Comparison Item | CHB (Con.) | [11] (2010) | [12] (2017) | [13] (2018) | [14] (2018) | [15] (2018) | Proposed | |

|---|---|---|---|---|---|---|---|---|

| Level | 9 | 9 | 9 | 9 | 9 | 7 | 9 | 8M * + 1 |

| Switch | 16 | 13 | 12 | 19 | 10 | 16 | 12 | 12M |

| Capacitor | - | 3 | 4 | 3 | - | 2 | 2 | 2M |

| DC source | 4 | 1 | 1 | 1 | 4 | 1 | 1 | M |

| N * × PIV | 16 × 1VIN | 4 × 4VIN 9 × 1VIN | 4 × 4VIN 8 × 1VIN | 19 × 1VIN | 4 × 4VIN 2 × 3VIN 4 × 1VIN | 16 × 1VIN | 9 × VIN 3 × VIN/2 | 9M × VIN 3M × VIN/2 |

| TSV | 16VIN | 25VIN | 24VIN | 19VIN | 26VIN | 16VIN | 21VIN/2 | M × (21VIN/2) |

| Part | Part Number | Voltage Rating (V) | Unit Price * (€) | [11] | [12] | [13] | [15] | Proposed |

|---|---|---|---|---|---|---|---|---|

| MOSFETs | STW40NF20 | 200 | 3.53 | 9 | 8 | 19 | - | 3 |

| SUP40N25-60-E3 | 250 | 4.43 | - | - | - | 16 | 9 | |

| FQL40N50 | 450 | 7.73 | - | - | - | - | - | |

| SIHG47N60AEFGE3 | 600 | 7.82 | 4 | 4 | - | - | - | |

| Capacitors | E32D151HPN472TEE3M | 150 | 23.00 | 3 | 2 | 4 | - | 2 |

| B43713F2478M000 | 250 | 39.39 | - | - | - | 2 | - | |

| ALS31A472NF350 | 350 | 48.83 | - | 2 | - | - | - | |

| Gate driver | IRS21271SPBF | - | 1.34 | 13 | 12 | 19 | 14 | 12 |

| Total cost (€) | 149.47 | 219.26 | 184.53 | 168.42 | 112.54 |

| Relationship between the Carriers and Vref | ON-State IGBTs | Levels |

|---|---|---|

| Vref > Vt1 | S1-S4-S5-S10-S11-S12 | +4VIN |

| Vt2 < Vref < Vt1 | S1-S4-S5-S7-S8-S10-S11 | +3VIN |

| Vt3 < Vref < Vt2 | S1-S3-S4-S5-S6-S10-S12 | +2VIN |

| Vt4 < Vref < Vt3 | S1-S3-S5-S7-S8-S10 | +1VIN |

| Vt5 < Vref < Vt4 | S2-S3-S4-S5-S6-S10-S12 | 0 |

| Vt6 < Vref < Vt5 | S2-S4-S6-S7-S8-S9 | −1VIN |

| Vt7 < Vref < Vt6 | S2-S3-S4-S5-S6-S9-S12 | −2VIN |

| Vt8 < Vref < Vt7 | S2-S3-S6-S7-S8-S9-S11 | −3VIN |

| Vref < Vt8 | S2-S3-S6-S9-S11-S12 | −4VIN |

| Output Level | Req (Ω) |

|---|---|

| 0 | 2RS + 2RD = 0.64 |

| ±VIN/2 | 3RS + 2RD + RC = 0.94 |

| ±VIN | 3RS + RD = 0.86 |

| ±3VIN/2 | 5RS + RD + RC = 1.43 |

| ±2VIN | 6RS + 2RC = 1.68 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Saeedian, M.; Pouresmaeil, E.; Samadaei, E.; Manuel Godinho Rodrigues, E.; Godina, R.; Marzband, M. An Innovative Dual-Boost Nine-Level Inverter with Low-Voltage Rating Switches. Energies 2019, 12, 207. https://doi.org/10.3390/en12020207

Saeedian M, Pouresmaeil E, Samadaei E, Manuel Godinho Rodrigues E, Godina R, Marzband M. An Innovative Dual-Boost Nine-Level Inverter with Low-Voltage Rating Switches. Energies. 2019; 12(2):207. https://doi.org/10.3390/en12020207

Chicago/Turabian StyleSaeedian, Meysam, Edris Pouresmaeil, Emad Samadaei, Eduardo Manuel Godinho Rodrigues, Radu Godina, and Mousa Marzband. 2019. "An Innovative Dual-Boost Nine-Level Inverter with Low-Voltage Rating Switches" Energies 12, no. 2: 207. https://doi.org/10.3390/en12020207

APA StyleSaeedian, M., Pouresmaeil, E., Samadaei, E., Manuel Godinho Rodrigues, E., Godina, R., & Marzband, M. (2019). An Innovative Dual-Boost Nine-Level Inverter with Low-Voltage Rating Switches. Energies, 12(2), 207. https://doi.org/10.3390/en12020207