Double Stage Double Output DC–DC Converters for High Voltage Loads in Fuel Cell Vehicles

Abstract

1. Introduction

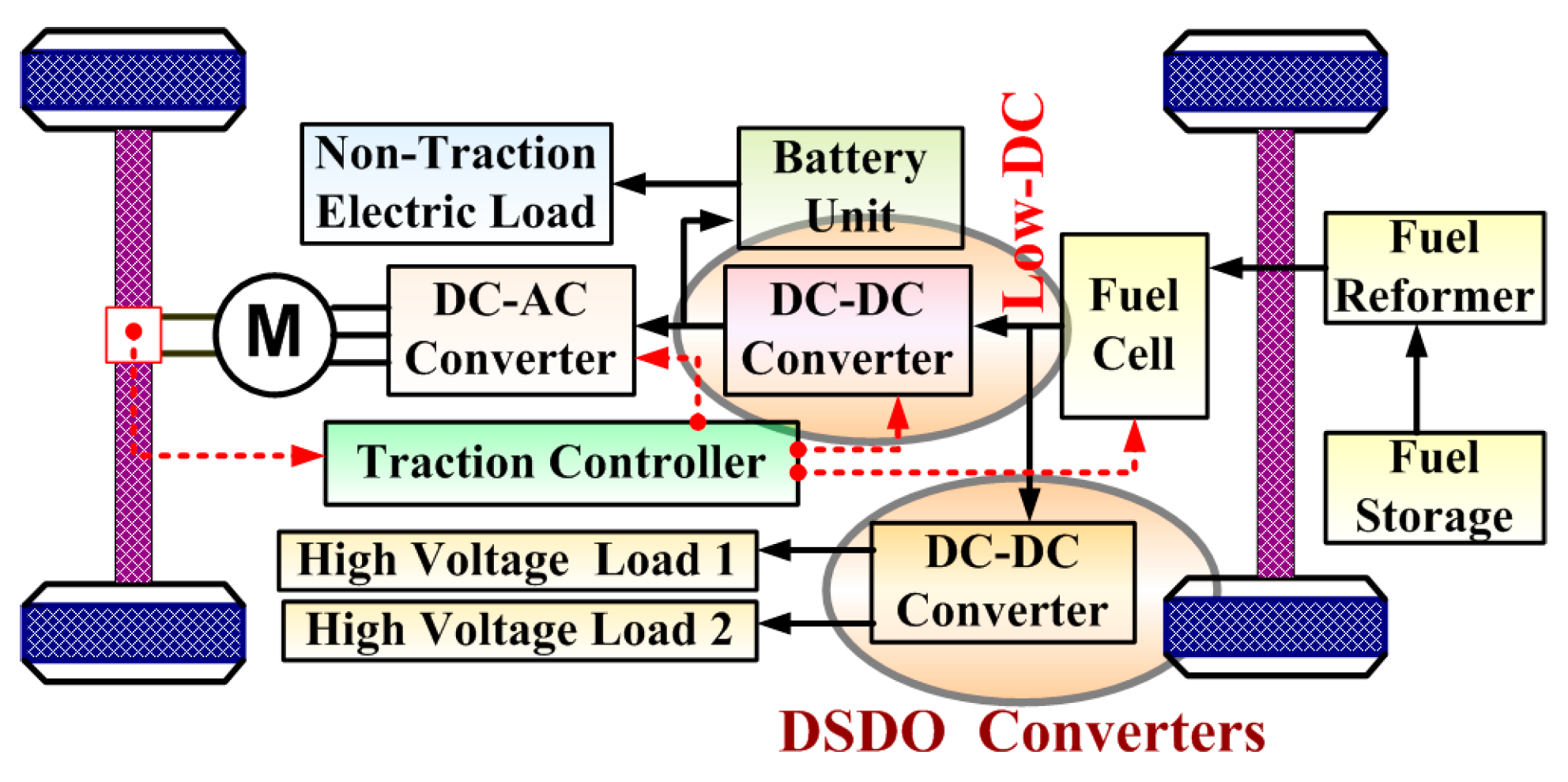

- The L–Y converters, i.e., an expanded member of the XY converter family that feeds power to two different high voltage loads. At same time, the proposed converter provides high voltage conversion ratio. A diagram of a typical fuel-cell vehicle (FCV) with a DSDO converter is shown Figure 3, where low FC voltage is fed to two high voltage loads.

- Four new original converter configurations (DSDO L–L, DSDO L-2L, DSDO, L-2LC, and DSDO, L-2LCm) are derived from a single switch.

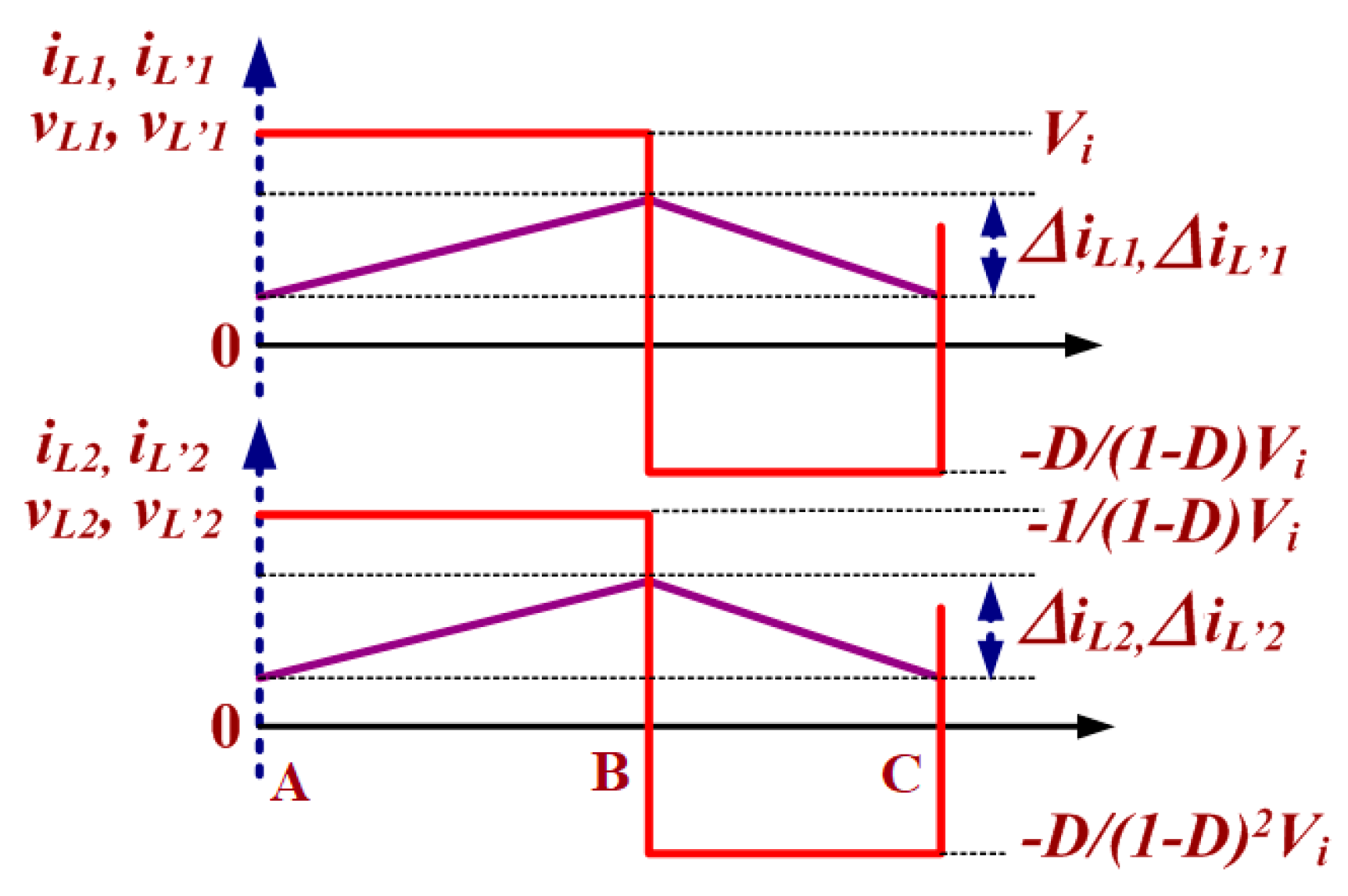

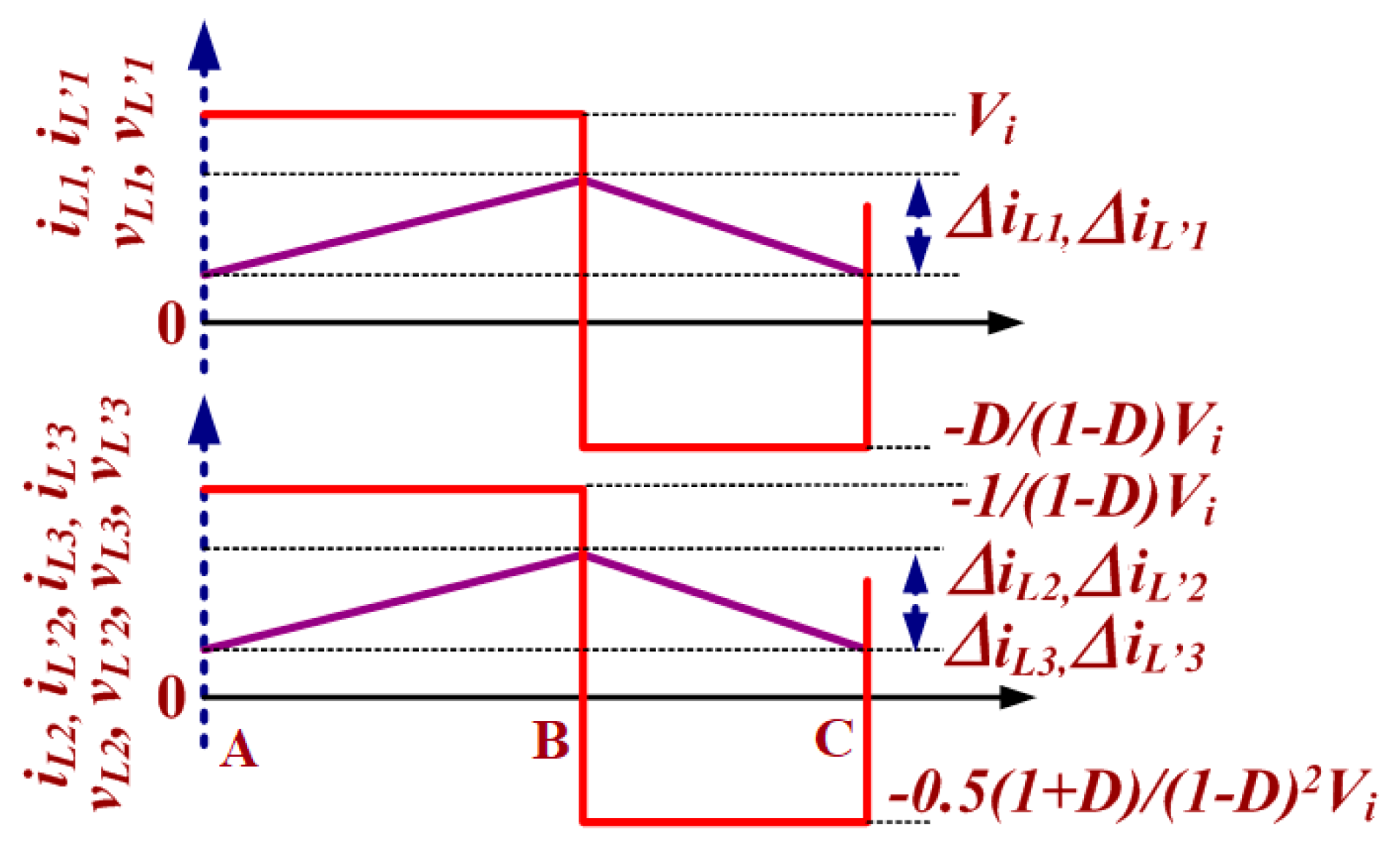

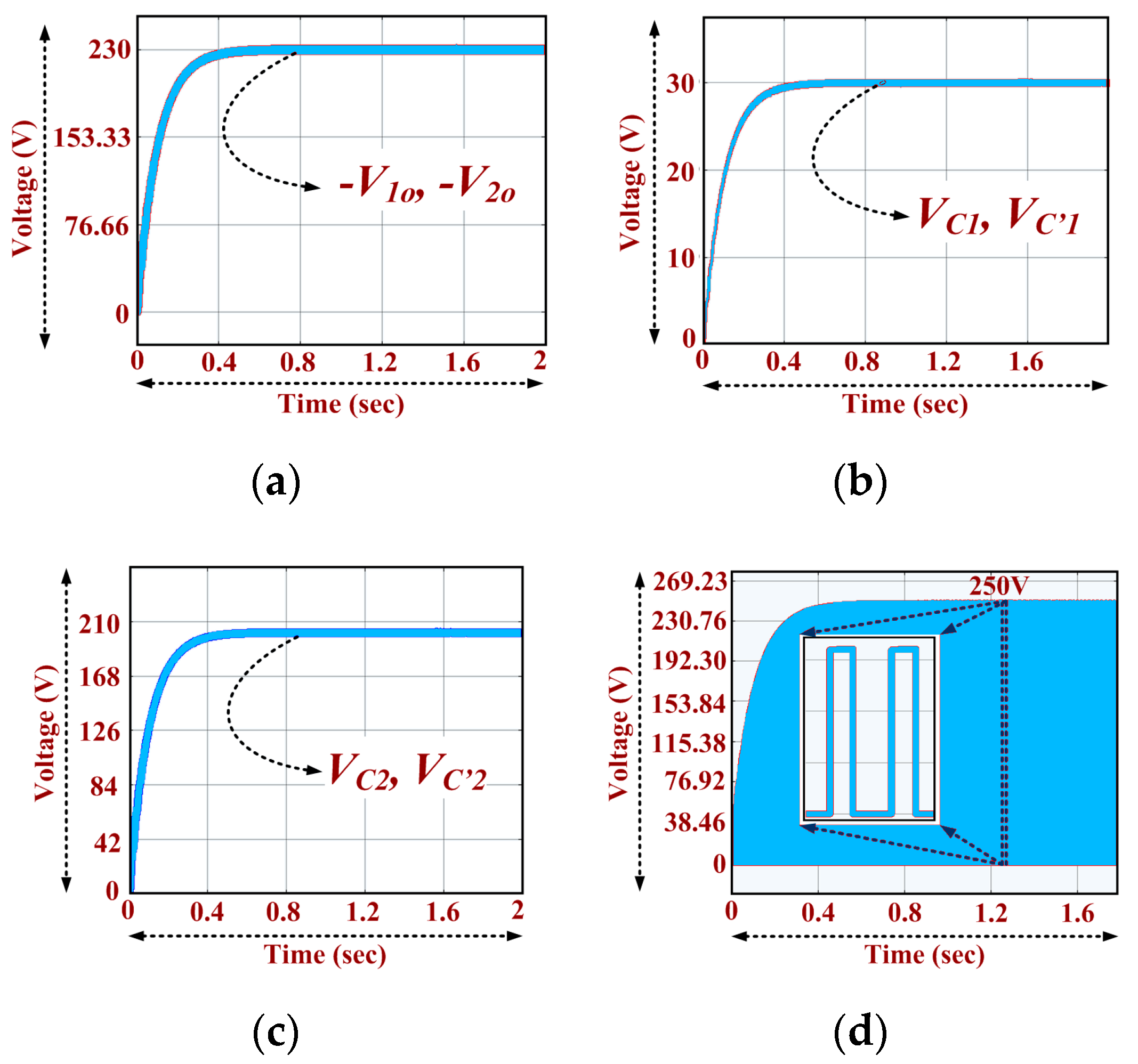

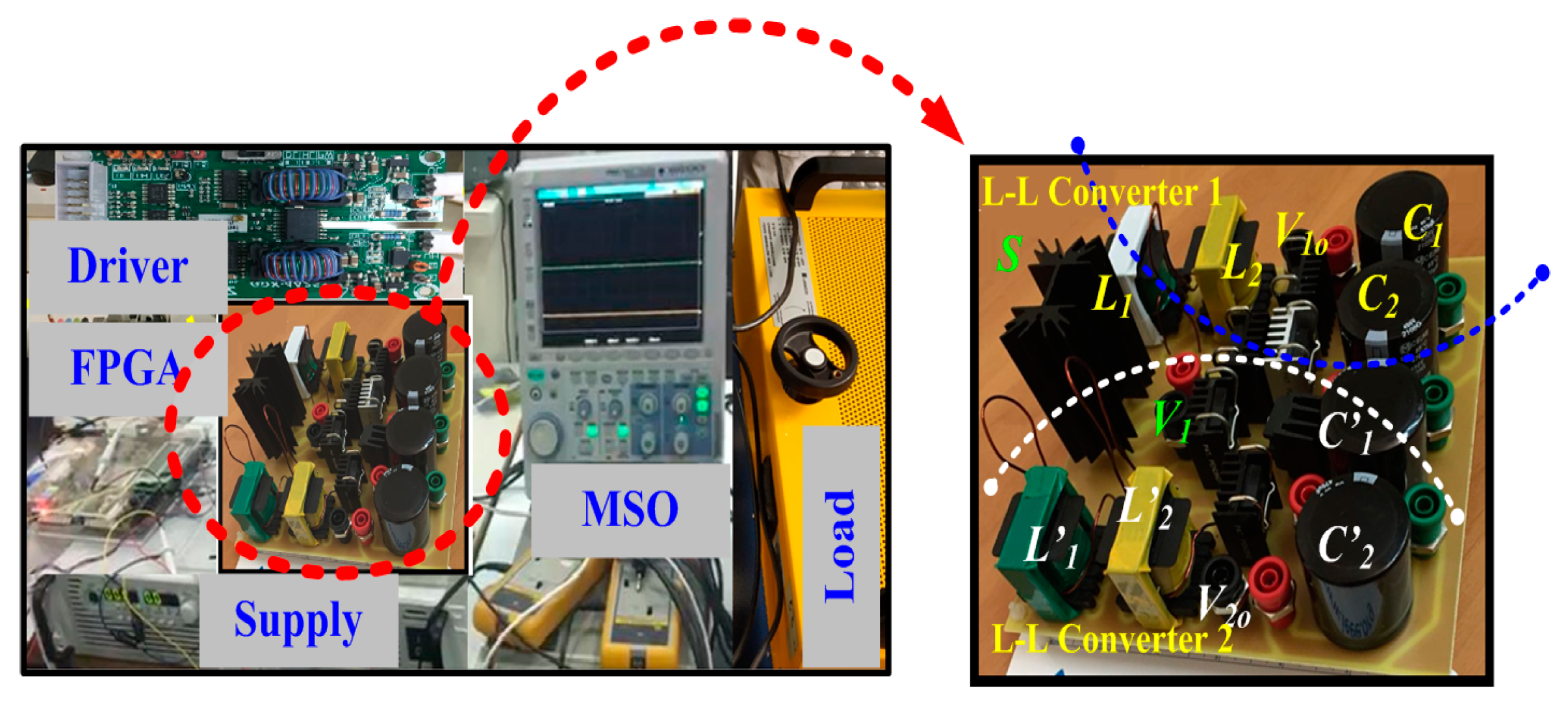

- The modes of operation, characteristics waveform, and voltage gain analysis for each proposed configuration are discussed in detail.

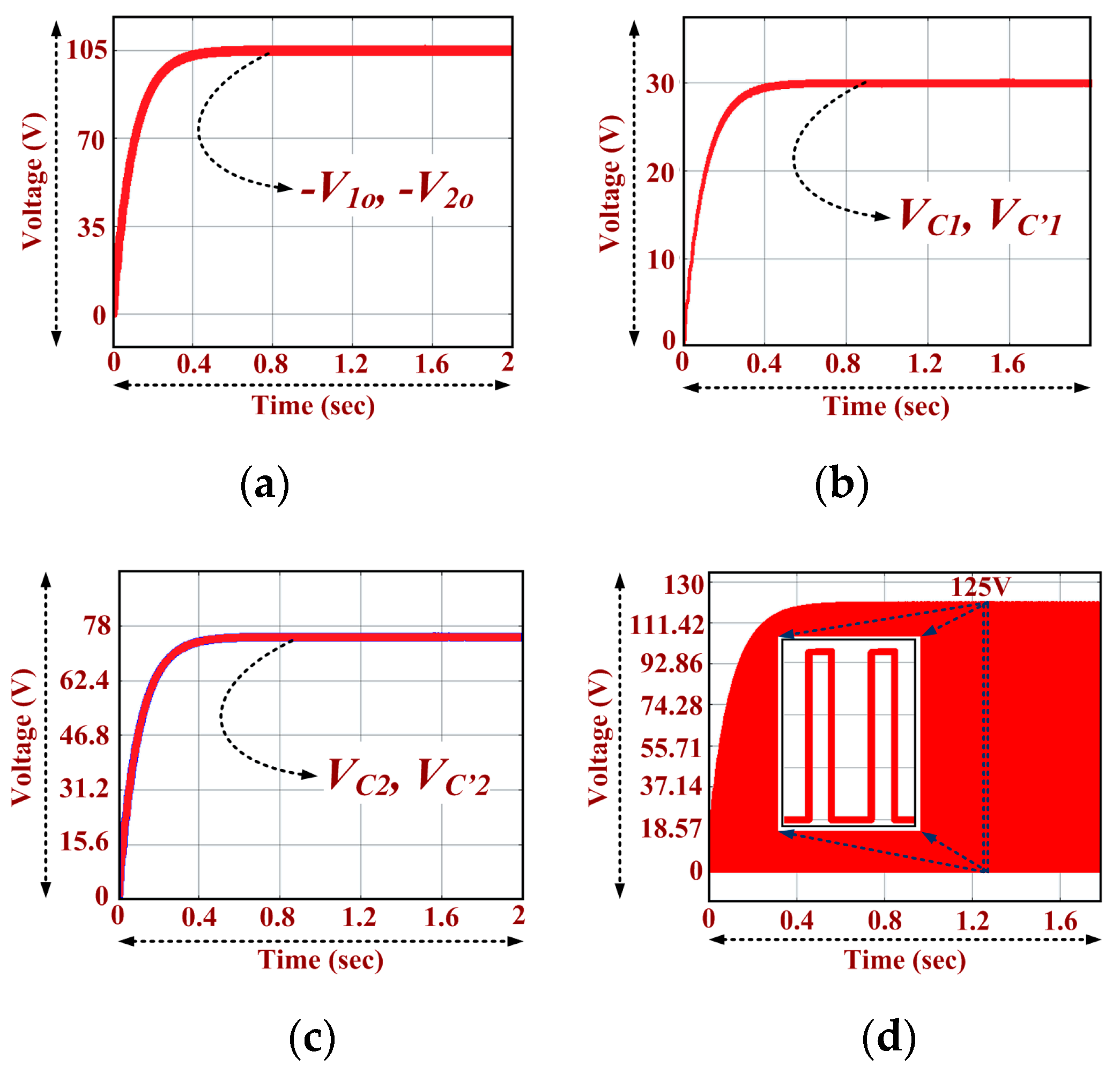

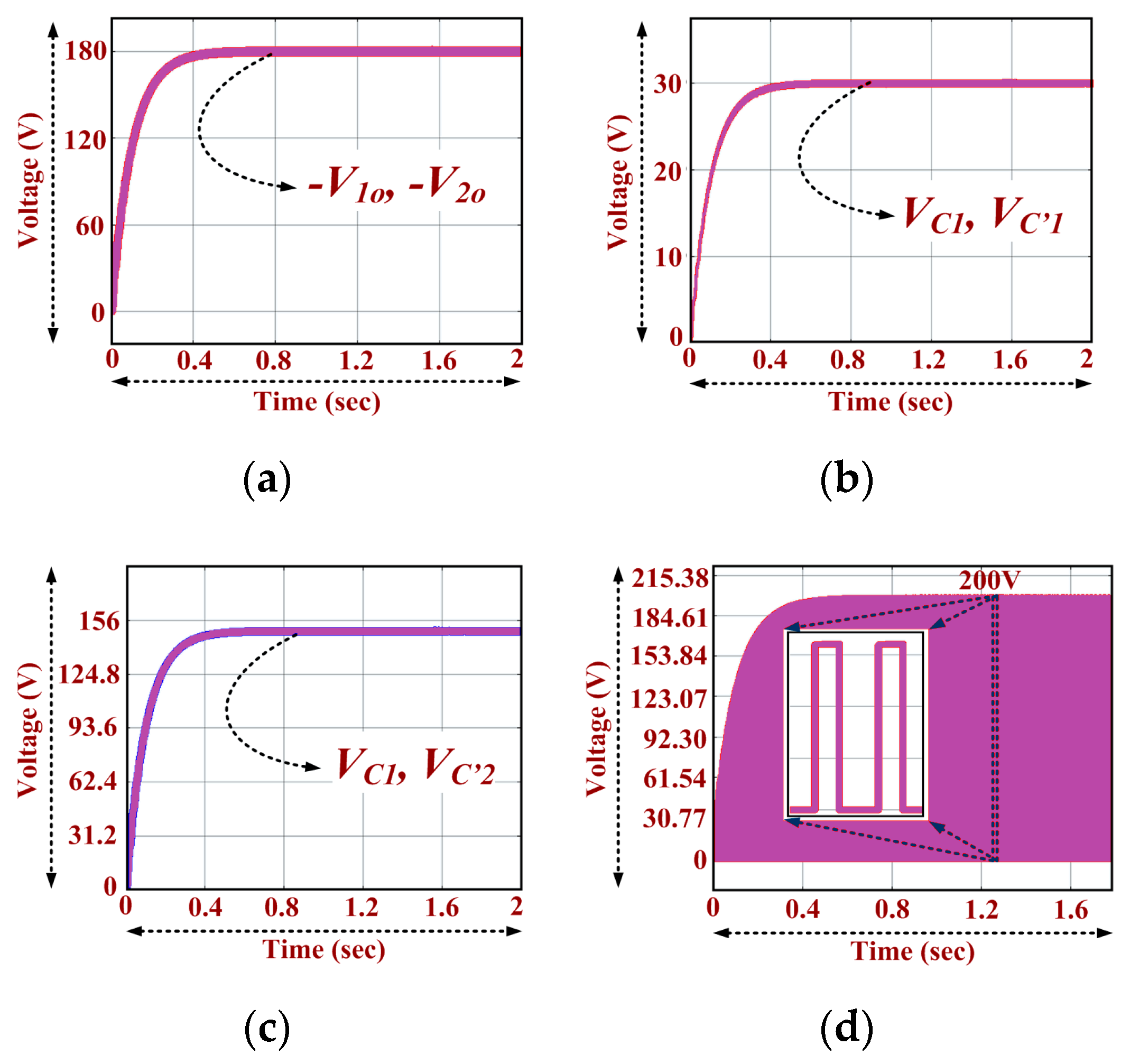

- The performance of the proposed converters is validated through numerical simulation and experimental prototype results.

2. Double Stage Double Output Converters

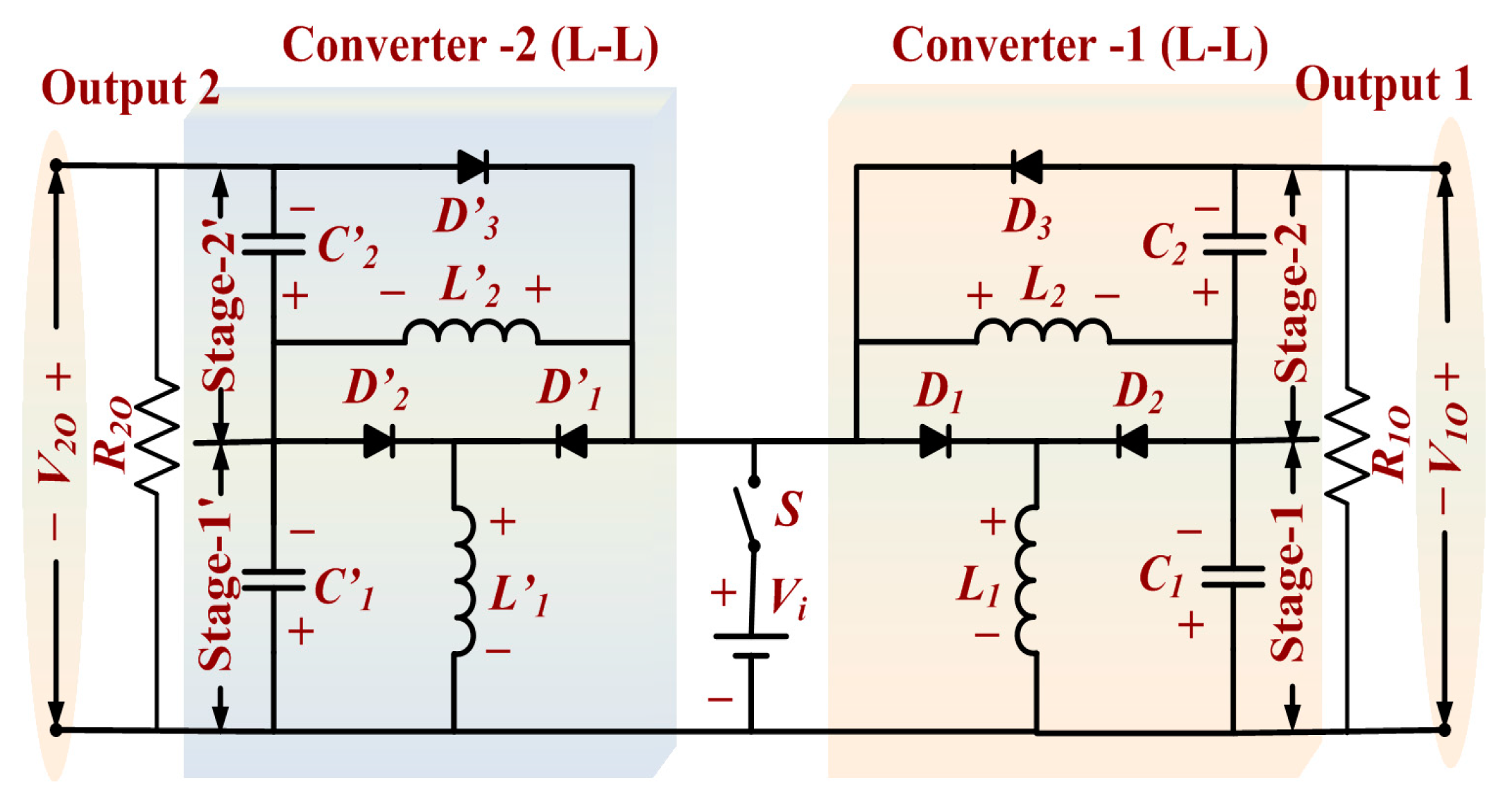

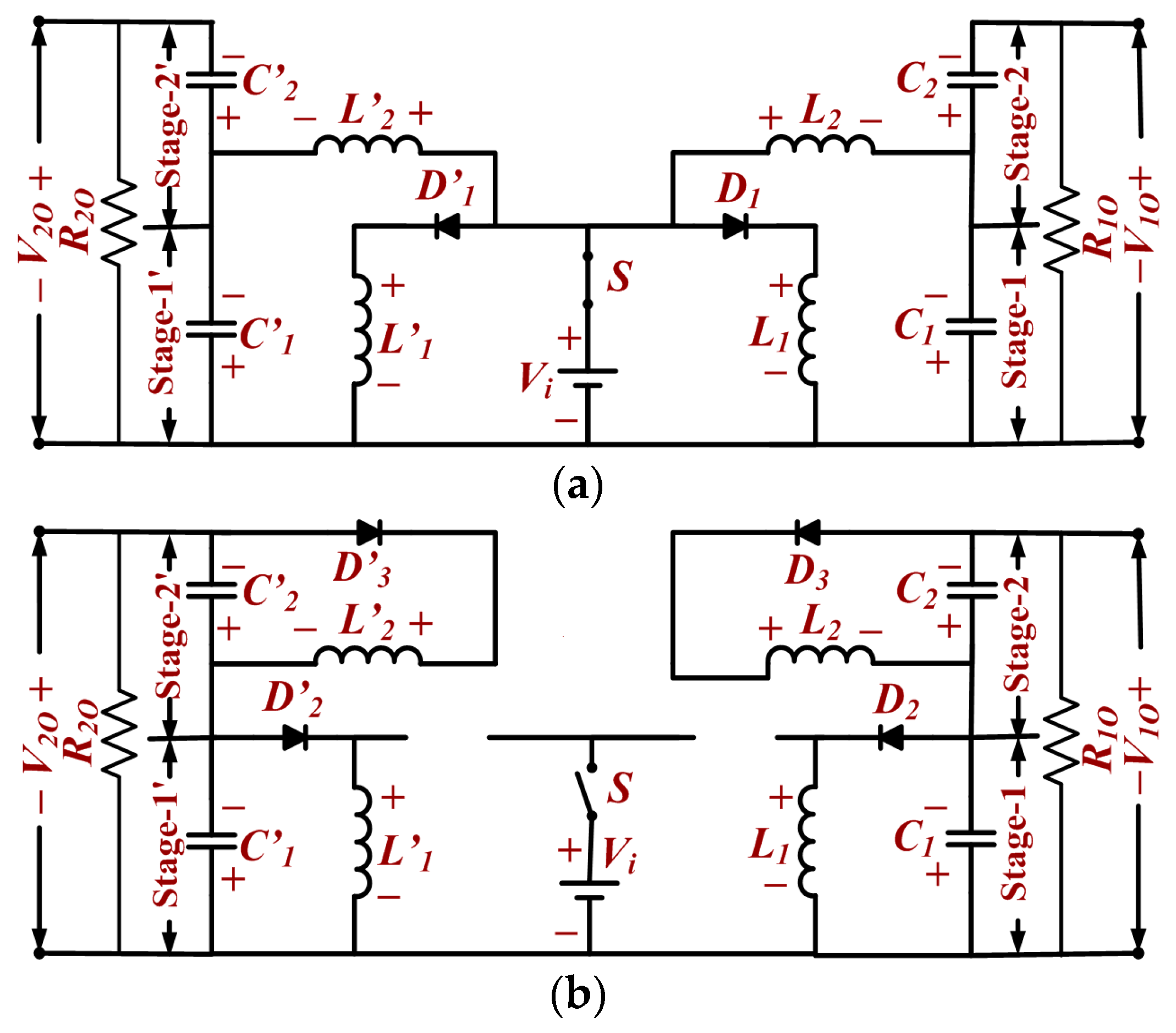

2.1. DSDO L–L Converter

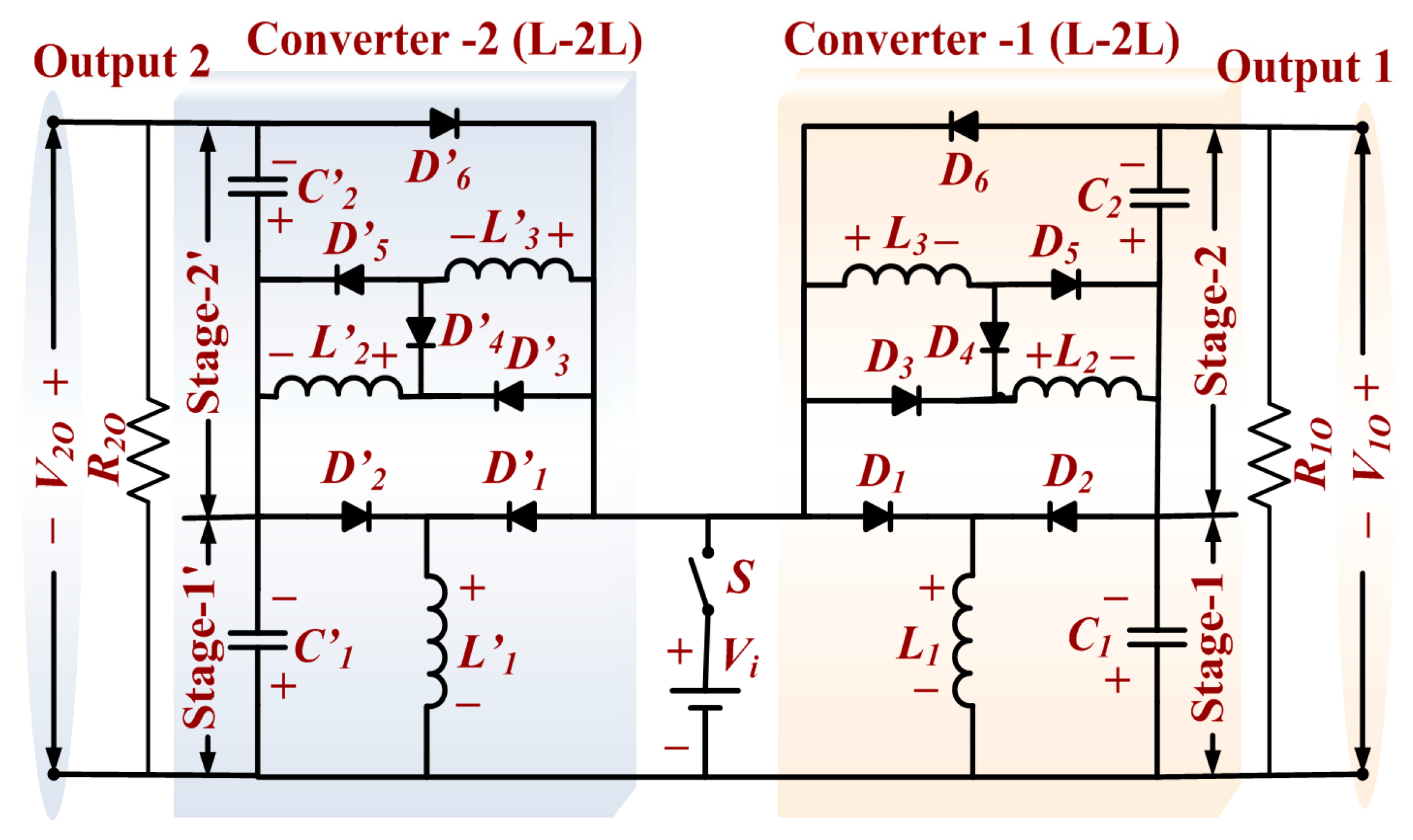

2.2. DSDO L–2L Converter

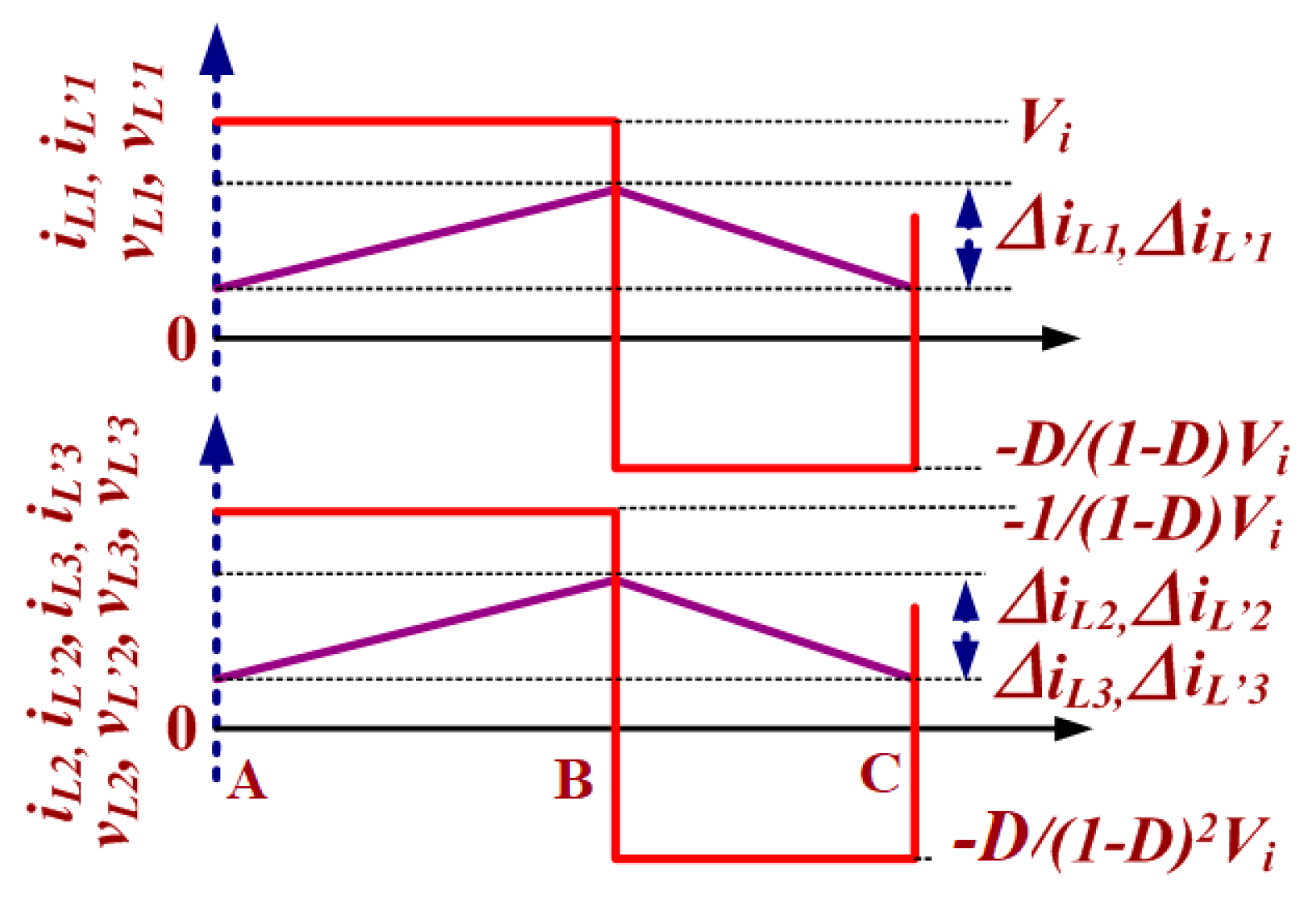

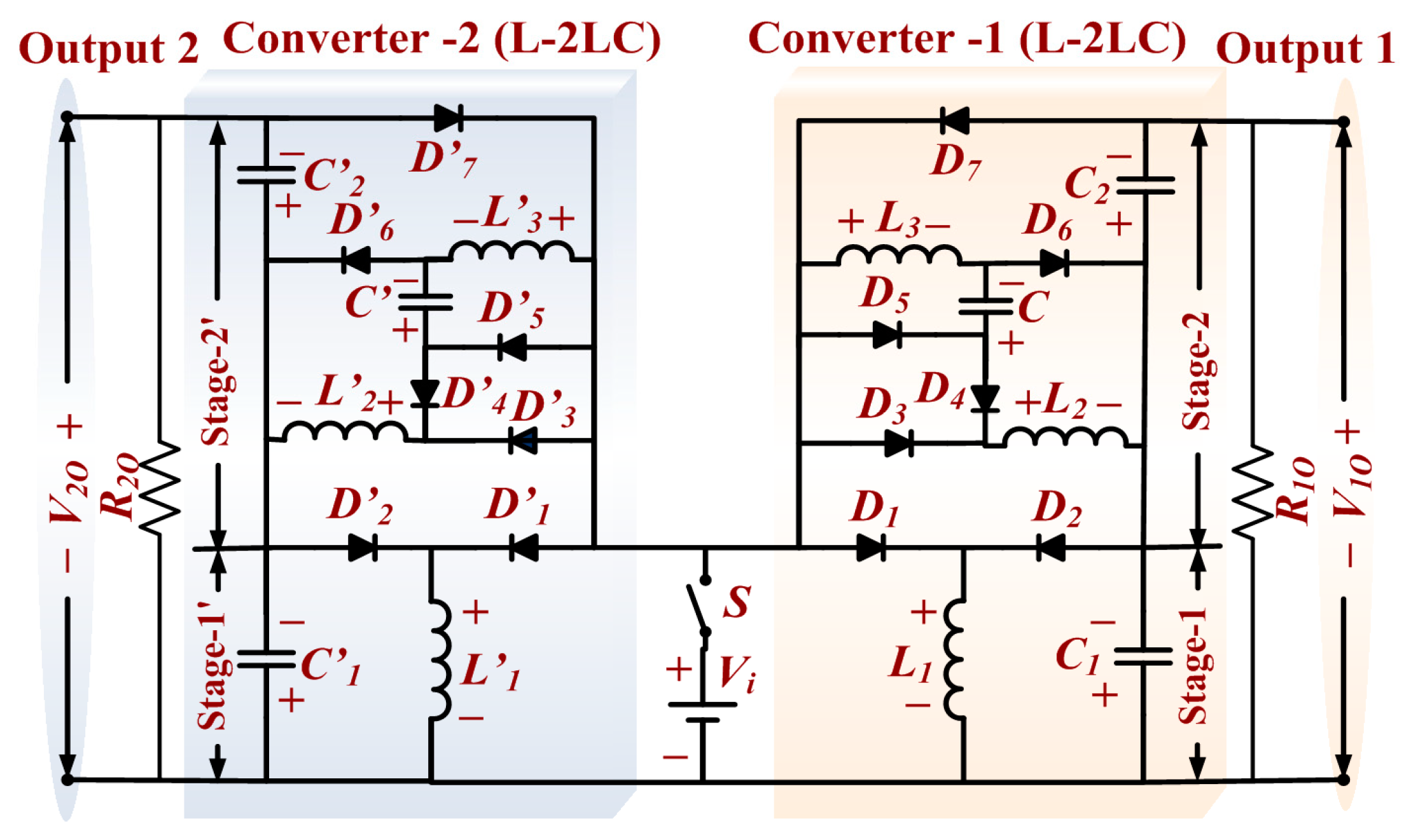

2.3. DSDO L–2LC Converter

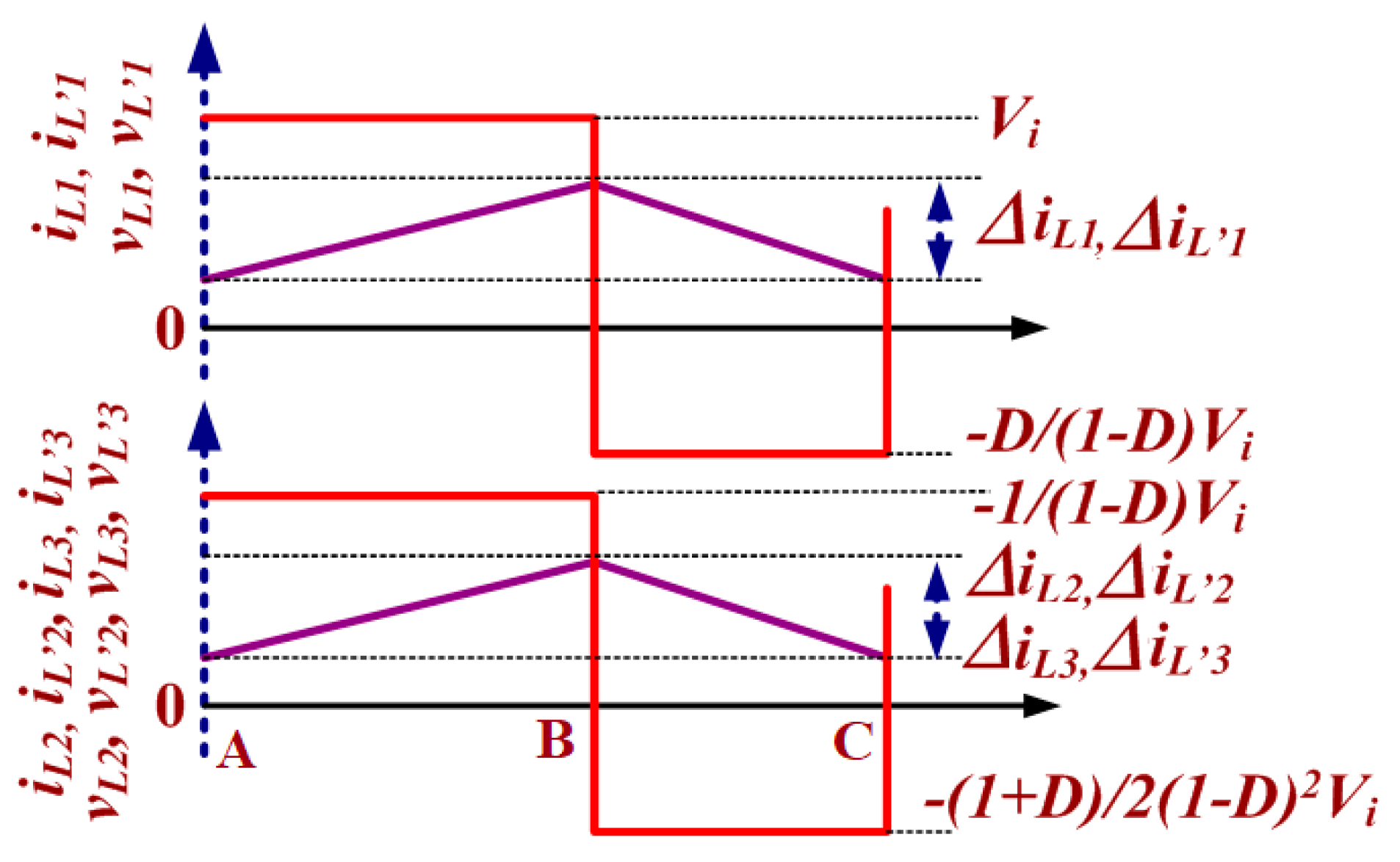

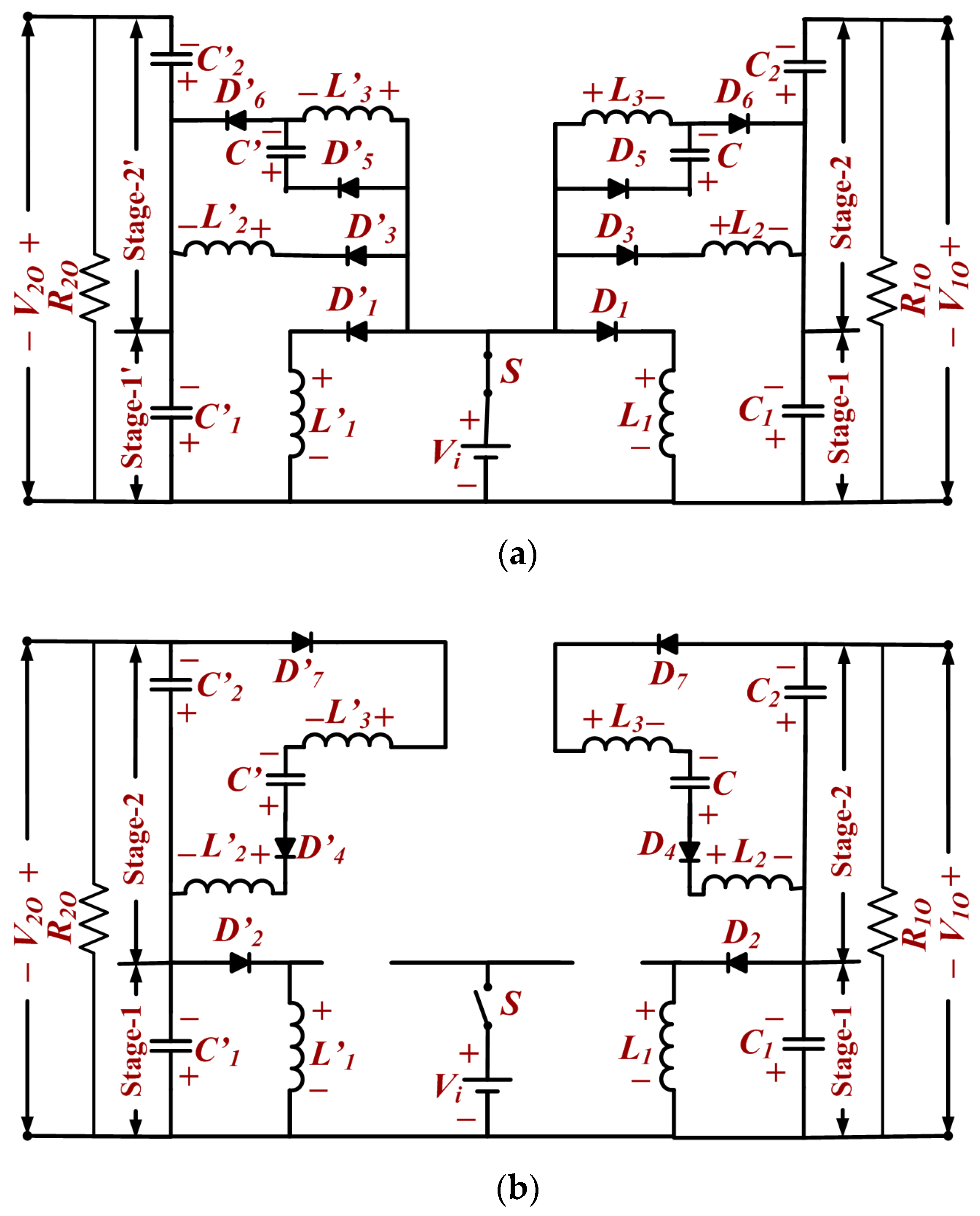

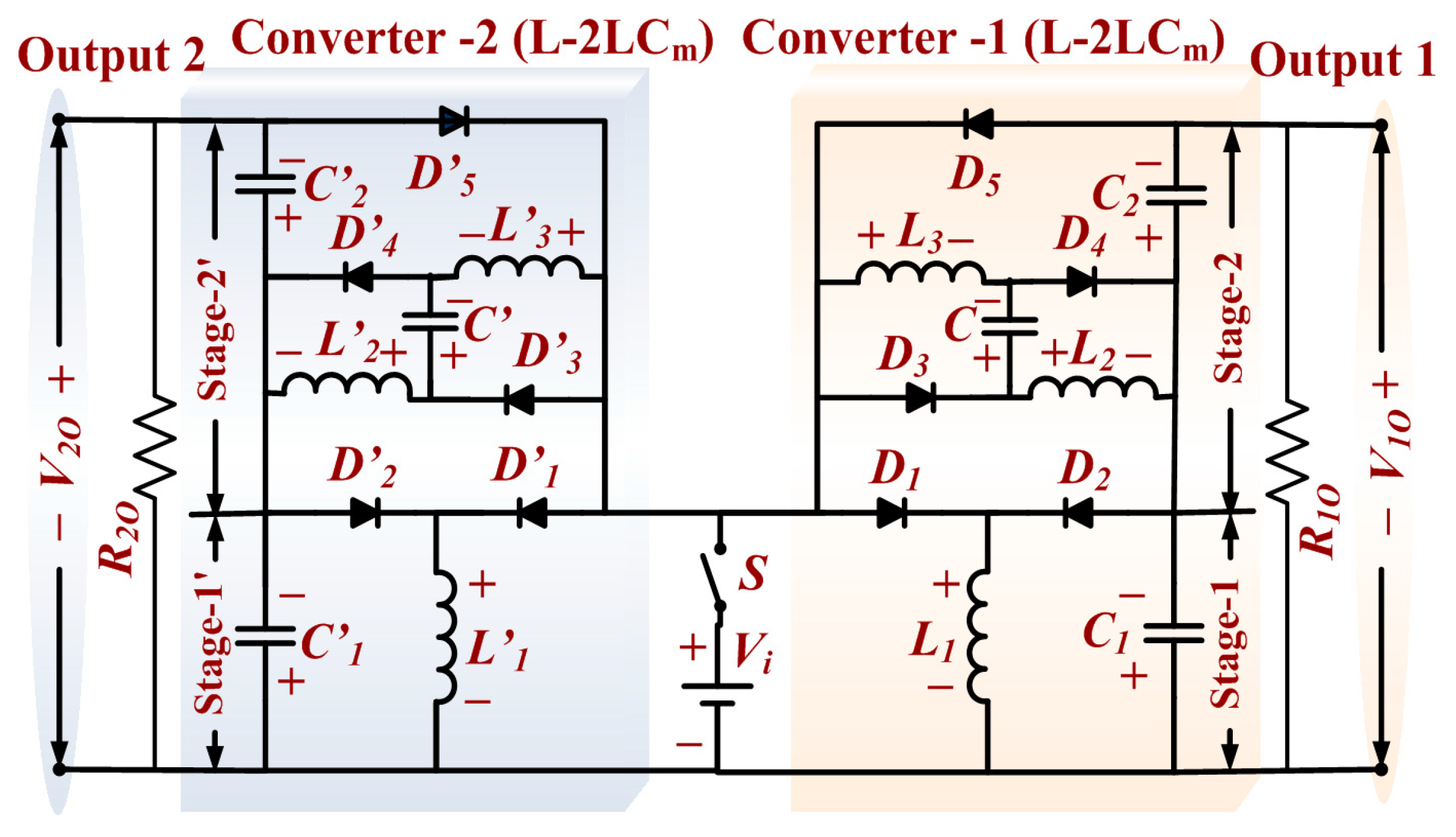

2.4. DSDO L–2LCm Converter

3. Comparative Study

4. Simulation and Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Rezaee, S.; Farjah, E. A DC–DC Multiport Module for Integrating Plug-In Electric Vehicles in a Parking Lot: Topology and Operation. IEEE Trans. Power Electron 2014, 29, 5688–5695. [Google Scholar] [CrossRef]

- Mercorelli, P.; Kubasiak, N.; Liu, S. Model predictive control of an electromagnetic actuator fed by multilevel PWM inverter. In Proceedings of the IEEE International Symposium on Industrial Electronics, Ajaccio, France, 4–7 May 2004; pp. 531–535. [Google Scholar]

- Mercorelli, P.; Kubasiak, N.; Liu, S. Multilevel bridge governor by using model predictive control in wavelet packets for tracking trajectories. In Proceedings of the IEEE International Conference on Robotics and Automation, New Orleans, LA, USA, 26 April–1 May 2004; pp. 4079–4084. [Google Scholar]

- Faraji, R.; Adib, E.; Farzanehfard, H. Soft-switched non-isolated high step-up multi-port DC-DC converter for hybrid energy system with minimum number of switches. Intl. J. Electr. Power Energy Sys. 2019, 106, 511–519. [Google Scholar] [CrossRef]

- Mercorelli, P. A Multilevel Inverter Bridge Control Structure with Energy Storage Using Model Predictive Control for Flat Systems. J. Eng. 2019, 1–15. [Google Scholar] [CrossRef]

- Kubasiak, N.; Mercorelli, P.; Liu, S. Model Predictive Control of Transistor Pulse Converter for Feeding Electromagnetic Valve Actuator with Energy Storage. In Proceedings of the IEEE 44th Conference on Decision and Control, Seville, Spain, 12–15 December 2005; pp. 6794–6799. [Google Scholar]

- Lucia, U. Overview on fuel cells. Renew. Sustain. Energy Rev. 2014, 30, 164–169. [Google Scholar] [CrossRef]

- Peighambardoust, S.J.; Rowshanzamir, S.; Amjadi, M. Review of the proton exchange membranes for fuel cell applications. Intl. J. Hydrog. Energy 2010, 35, 9349–9384. [Google Scholar] [CrossRef]

- Zhang, Z.; Pittini, R.; Andersen, M.A.E.; Thomsena, O.C. A Review and Design of Power Electronics Converters for Fuel Cell Hybrid System Applications. Energy Procedia 2012, 20, 301–310. [Google Scholar] [CrossRef]

- Cheng, S.; Lo, Y.; Chiu, H.; Kuo, S. High-Efficiency Digital-Controlled Interleaved Power Converter for High-Power PEM Fuel-Cell Applications. IEEE Trans. Ind. Electron. 2013, 60, 773–780. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Al-ammari, R.; Mohammad, M.; Padmanaban, S.; Iqbal, A. A New Triple-Switch-Triple-Mode High Step-Up Converter with Wide Range of Duty Cycle for DC Microgrid Applications. IEEE Trans. Ind. Appl. 2019, 1. [Google Scholar] [CrossRef]

- Maroti, P.K.; Al-Ammari, R.; Bhaskar, M.S.; Meraj, M.; Iqbal, A.; Padmanaban, S.; Rahman, S. New tri-switching state non-isolated high gain DC–DC boost converter for microgrid application. IET Power Electron 2019, 12, 2741–2750. [Google Scholar] [CrossRef]

- Yang, L.; Liang, T.; Chen, J. Transformerless DC–DC Converters with High Step-Up Voltage Gain. IEEE Trans. Ind. Electron. 2009, 56, 3144–3152. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Meraj, M.; Iqbal, A.; Padmanaban, S.; Maroti, P.K.; Alammari, R. High Gain Transformer-Less Double-Duty-Triple-Mode DC/DC Converter for DC Microgrid. IEEE Access 2019, 7, 36353–36370. [Google Scholar] [CrossRef]

- Muranda, C.; Ozsoy, E.; Padmanaban, S.; Bhaskar, M.S.; Fedak, V.; Ramachandaramurthy, V.K. Modified SEPIC DC-to-DC boost converter with high output-gain configuration for renewable applications. In Proceedings of the IEEE Conference on Energy Conversion CENCON’17, Kuala Lumpur, Malaysia, 30–31 October 2017; pp. 317–322. [Google Scholar]

- Oluwafemi, A.W.; Ozsoy, E.; Padmanaban, S.; Bhaskar, M.S.; Ramachandaramurthy, V.K.; Fedak, V. A modified high output-gain cuk converter circuit configuration for renewable applications—A comprehensive investigation. In Proceedings of the IEEE Conference on Energy Conversion CENCON’17, Kuala Lumpur, Malaysia, 30–31 October 2017; pp. 117–122. [Google Scholar]

- Morales-Saldana, A.; Gutierrez, E.E.C.; Leyva-Ramos, J. Modeling of switch-mode dc-dc cascade converters. IEEE Trans. Aerosp. Electron. Syst. 2002, 38, 295–299. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Padmanaban, S.; Blaabjerg, F.; Wheeler, P.W. An Improved Multistage Switched Inductor Boost Converter (Improved M-SIBC) for Renewable Energy Applications: A key to Enhance Conversion Ratio. In Proceedings of the IEEE 19th Workshop on Control and Modeling for Power Electronics COMPEL’18, Padua, Italy, 25–28 June 2018. [Google Scholar]

- De Novaes, Y.R.; Rufer, A.; Barbi, I. A New Quadratic, Three-Level, DC/DC Converter Suitable for Fuel Cell Applications. In Proceedings of the IEEE Power Conversion Conference-Nagoya, Nagoya, Japan, 2–5 April 2007; pp. 601–607. [Google Scholar]

- Iqbal, A.; Bhaskar, M.S.; Meraj, M.; Padmanaban, S. DC-Transformer Modelling, Analysis and Comparison of the Experimental Investigation of a Non-Inverting and Non-Isolated Nx Multilevel Boost Converter (Nx MBC) for Low to High DC Voltage Applications. IEEE Access 2018, 6, 70935–70951. [Google Scholar] [CrossRef]

- Iqbal, A.; Bhaskar, M.S.; Meraj, M.; Padmanaban, S.; Rahman, S. Closed-Loop Control and Boundary for CCM and DCM of Non-Isolated Inverting Nx Multilevel Boost Converter for High Voltage Step-Up Applications. IEEE Trans. Ind. Electron. 2019, 1. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Padmanaban, S.; Blaabjerg, F. A Multistage DC-DC Step-Up Self-Balanced and Magnetic Component-Free Converter for Photovoltaic Applications: Hardware Implementation. Energies 2017, 10, 719. [Google Scholar] [CrossRef]

- Ranjana, M.S.B.; Alammari, R.; Meraj, M.; Iqbal, A.; Padmanaban, S. Modified Multilevel Buck-Boost Converter with Equal Voltage across Each Capacitor: Analysis and Experimental Investigations. IET Power Electron. 2019. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Meraj, M.; Iqbal, A.; Padmanaban, S. Non-isolated Symmetrical Interleaved Multilevel Boost Converter with Reduction in Voltage Rating of Capacitors for High Voltage Microgrid Applications. IEEE Trans. Ind. Appl. 2019, 1. [Google Scholar] [CrossRef]

- Tahan, M.; Bamgboje, D.; Hu, T. Flyback-Based Multiple Output dc-dc Converter with Independent Voltage Regulation. In Proceedings of the 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems, PEDG, Charlotte, NC, USA, 25–28 June 2018; pp. 1–8. [Google Scholar]

- Wai, R.J.; Liaw, J.J. High-Efficiency-Isolated Single-Input Multiple-Output Bidirectional Converter. IEEE Trans. Power Electron. 2015, 30, 4914–4930. [Google Scholar] [CrossRef]

- Kim, J.K.; Choi, S.W.; Kim, C.E.; Moon, G.W. A New Standby Structure Using Multi-Output Full-Bridge Converter Integrating Flyback Converter. IEEE Trans. Ind. Electron. 2011, 58, 4763–4767. [Google Scholar] [CrossRef]

- Ferrera, M.; Litrán, S.; Aranda, E.; Márquez, J.A. A Converter for Bipolar DC Link Based on SEPIC-Cuk Combination. IEEE Trans. Power Electron. 2015, 30, 6483–6487. [Google Scholar] [CrossRef]

- Durán, E.; Litrán, S.P.; Ferrera, M.B.; Andújar, J.M. A Zeta-Buck-Boost converter combination for Single-Input Multiple-Output applications. In Proceedings of the 42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016; pp. 1251–1256. [Google Scholar]

- Pires, V.F.; Foito, D.; Baptista, F.B.; Silva, J. A photovoltaic generator system with a DC/DC converter based on an integrated Boost-Ćuk topology. Sol. Energy 2016, 136, 1–9. [Google Scholar] [CrossRef]

- Liu, X.; Xu, J.; Chen, Z.; Wang, N. Single-Inductor Dual-Output Buck-Boost Power Factor Correction Converter. IEEE Trans. Ind. Electron. 2015, 62, 943–952. [Google Scholar] [CrossRef]

- Sanjeevikumar, P.; Bhaskar, M.S.; Dhond, P.; Blaabjerg, F.; Pecht, M. Non-isolated Sextuple Output Hybrid Triad Converter Configurations for High Step-Up Renewable Energy Applications. In Power Systems and Energy Management; Springer: Berlin/Heidelberg, Germany, 2018; pp. 1–12. [Google Scholar]

- Patra, P.; Patra, A.; Misra, N. A Single-Inductor Multiple-Output Switcher with Simultaneous Buck, Boost, and Inverted Outputs. IEEE Trans. Power Electron. 2011, 27, 1936–1951. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Padmanaban, S.; Kulkarni, R.; Blaabjerg, F.; Seshagiri, S.; Hajizadeh, A. Novel LY converter topologies for high gain transfer ratio: A new breed of XY family. In Proceedings of the 4th IET Clean Energy and Technology Conference, IET-CEAT, Kuala Lumpur, Malaysia, 14–15 November 2016; pp. 1–8. [Google Scholar]

- Mahajan, S.B.; Sanjeevikumar, P.; Wheeler, P.; Blaabjerg, F.; Rivera, M.; Kulkarni, R. X-Y converter family: A new breed of buck boost converter for high step-up renewable energy applications. In Proceedings of the IEEE International Conference on Automatica IEEE-ICA-ACCA, Curico, Chile, 19–21 October 2016; pp. 1–8. [Google Scholar]

- Bhaskar, M.S.; Sanjeevikumar, P.; Iqbal, A.; Meraj, M.; Howeldar, A.; Kamuruzzaman, J. L-L Converter for Fuel Cell Vehicular Power Train Applications: Hardware Implementation of Primary Member of X-Y Converter Family. In Proceedings of the IEEE Power Electronics, Drives and Energy Systems PEDES’18, Chennai, India, 18–21 December 2018. [Google Scholar]

- Maroti, P.K.; Padmanaban, S.; Bhaskar, M.S.; Blaabjerg, F.; Ramachandaramurthy, K.V.; Siano, P.; Fedak, V. A novel 2L-Y DC-DC converter topologies for high conversion ratio renewable application. In Proceedings of the IEEE Conference on Energy Conversion CENCON’17, Kuala Lumpur, Malaysia, 30 October 2017; pp. 323–328. [Google Scholar]

- Padmanaban, S.; Bhaskar, M.S.; Blaabjerg, F.; Yang, Y. A New DC-DC Multilevel Breed of XY Converter Family for Renewable Energy Applications: LY Multilevel Structured Boost Converter. In Proceedings of the 44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018; pp. 6110–6115. [Google Scholar]

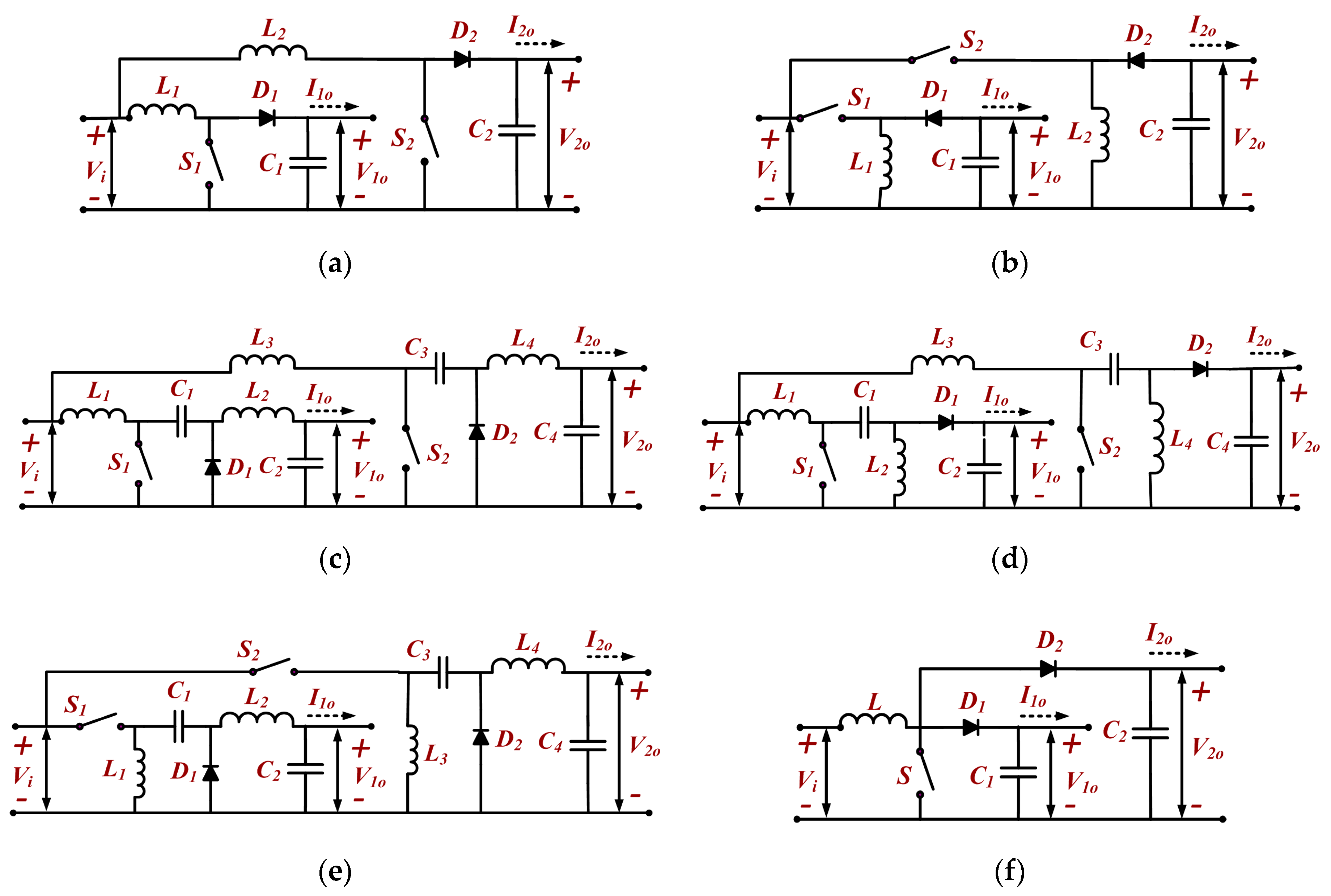

| Converter | Switches | Inductors | Diodes | Capacitors | Voltage Conversion Ratio (V1o,V2o) | Voltage Stress across Switch (Vs/Vi) |

|---|---|---|---|---|---|---|

| Converter without common front-end structure | ||||||

| Boost-Boost converter (Figure 1a) | 2 | 2 | 2 | 2 | 1/1-D, 1/1-D | 1/1-D |

| Buck-Boost-Buck-Boost converter (Figure 1b) | 2 | 2 | 2 | 2 | -D/1-D, -D/1-D | 1/1-D |

| Cuk-Cuk Converter (Figure 1c) | 2 | 4 | 2 | 4 | -D/1-D, -D/1-D | 1/1-D |

| SEPIC-SEPIC Converter (Figure 1d) | 2 | 4 | 2 | 4 | D/1-D, D/1-D | 1/1-D |

| ZETA-ZETA Converter (Figure 1e) | 2 | 4 | 2 | 4 | D/1-D, D/1-D | 1/1-D |

| Converter with common front-end structure | ||||||

| Boost-Boost converter (Figure 1f) | 1 | 1 | 2 | 2 | 1/1-D, 1/1-D | 1/1-D |

| Buck-Boost-Buck-Boost converter (Figure 1g) | 1 | 1 | 2 | 2 | -D/1-D, -D/1-D | 1/1-D |

| Cuk-Cuk converter (Figure 1h) | 1 | 3 | 2 | 4 | -D/1-D, -D/1-D | 1/1-D |

| SEPIC-SEPIC converter (Figure 1i) | 1 | 3 | 2 | 4 | D/1-D, D/1-D | 1/1-D |

| ZETA-ZETA converter (Figure 1j) | 1 | 3 | 2 | 4 | D/1-D, D/1-D | 1/1-D |

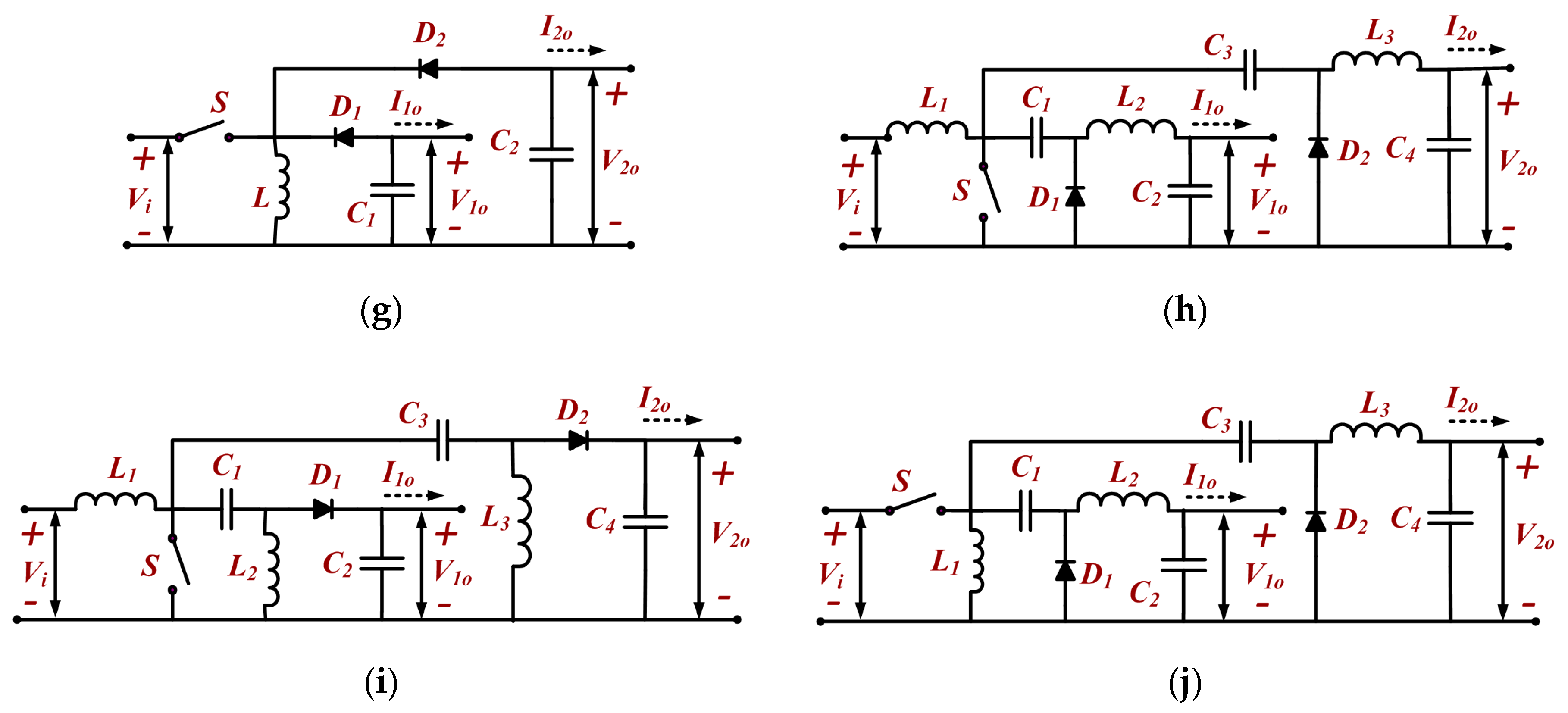

| Hybrid multi-output converter with common front-end structure | ||||||

| SEPIC-Cuk converter (Figure 2a) | 1 | 3 | 2 | 4 | -D/1-D, D/1-D | 1/1-D |

| ZETA–Buck-boost converter (Figure 2b) | 1 | 2 | 2 | 3 | D/1-D, -D/1-D | 1/1-D |

| Boost-Cuk converter (Figure 2c) | 1 | 2 | 2 | 3 | -D/1-D, 1/1-D | 1/1-D |

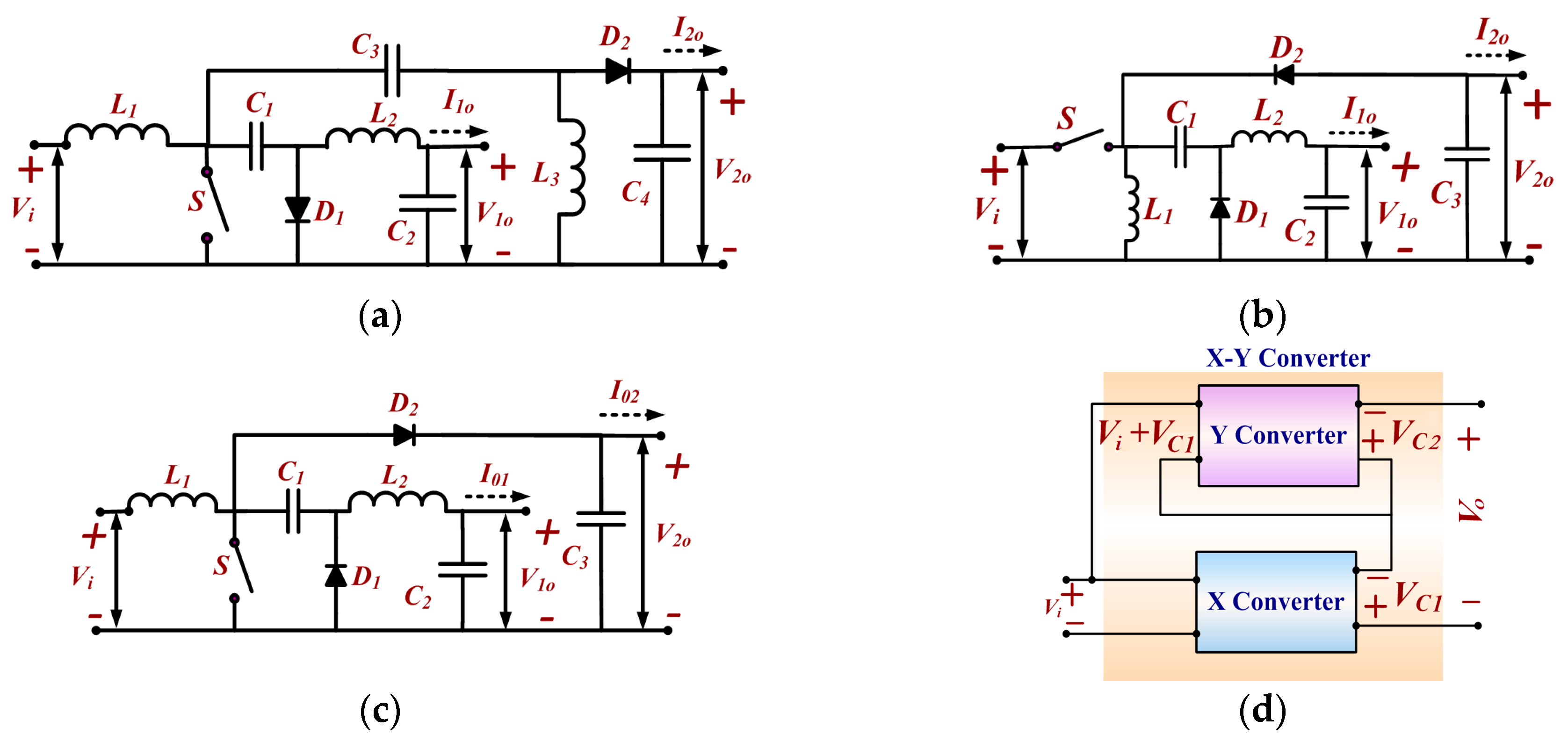

| Proposed DSDO converter configurations | ||||||

| DSDO L–L converters (Figure 4) | 1 | 4 | 6 | 4 | D(1-D)−1 + D(1-D)−2 | 1+ D(1-D)−1 + D(1-D)−2 |

| DSDO L–2L converters (Figure 7) | 1 | 6 | 12 | 4 | D(1-D)−1 + 2D(1-D)−2 | 1+ D(1-D)−1 + 2D(1-D)−2 |

| DSDO L–2LC converters (Figure 10) | 1 | 6 | 14 | 6 | D(1-D)−1 + (1 + D)(1-D)−2 | 1+ D(1-D)−1 + (1 + D)(1-D)−2 |

| DSDO L–2LCm converters (Figure 13) | 1 | 6 | 10 | 6 | D(1-D)−1 + (1 + D)(1-D)−2 | 1+ D(1-D)−1 + (1 + D)(1-D)−2 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bhaskar, M.S.; Padmanaban, S.; Holm-Nielsen, J.B. Double Stage Double Output DC–DC Converters for High Voltage Loads in Fuel Cell Vehicles. Energies 2019, 12, 3681. https://doi.org/10.3390/en12193681

Bhaskar MS, Padmanaban S, Holm-Nielsen JB. Double Stage Double Output DC–DC Converters for High Voltage Loads in Fuel Cell Vehicles. Energies. 2019; 12(19):3681. https://doi.org/10.3390/en12193681

Chicago/Turabian StyleBhaskar, Mahajan Sagar, Sanjeevikumar Padmanaban, and Jens Bo Holm-Nielsen. 2019. "Double Stage Double Output DC–DC Converters for High Voltage Loads in Fuel Cell Vehicles" Energies 12, no. 19: 3681. https://doi.org/10.3390/en12193681

APA StyleBhaskar, M. S., Padmanaban, S., & Holm-Nielsen, J. B. (2019). Double Stage Double Output DC–DC Converters for High Voltage Loads in Fuel Cell Vehicles. Energies, 12(19), 3681. https://doi.org/10.3390/en12193681