1. Introduction

With the recent advancements in low power circuit design, packaging and battery technologies, the volumes of computing systems have been significantly reduced. With such a trend, numerous mm-scale miniature sensors have been demonstrated over the last decade [

1,

2,

3]. These miniature sensors have been drawing attention since they can make traditional sensor systems more effective and energy-efficient. At the same time they also enable new volume-constrained applications such as implanted medical diagnostic sensors and monitoring sensors for an access-limited environment. However, the biggest concern for such miniature systems is the operation lifetime. Therefore, optimizing the use of energy stored in a battery is a key design goal for battery powered miniature sensor systems [

1].

Miniature sensor systems are typically designed to spend most of their time in standby mode to minimize power consumption and maximize battery lifetime [

1,

2] but are periodically activated for short periods of time to perform their designated functions. During standby mode, the current consumption of such systems is on the order of sub-microamperes. On the other hand, the active mode current consumption ranges from a few microamperes to hundreds of microamperes depending on the task being performed [

3]. Therefore, the power management unit in miniature sensor systems should be able to efficiently handle a load current ranging from sub-microamperes to hundreds of microamperes.

To minimize standby power, the supply voltage needs to be reduced to the minimum voltage level at which data can be retained in standby mode. Conversely, in active mode, the supply voltage should be increased for better performance and stable operation [

4,

5]. This implies that the power management unit in miniature sensor systems should also be capable of handling a wide voltage range.

Providing a wide range of voltage conversion ratios for DC–DC conversion is also an important feature for the power management unit in miniature sensors. To enable dynamic voltage scaling (DVS) for energy efficient operation, a range of output voltages should be generated from the fixed battery voltage. Moreover, since the battery voltage can also vary over time, various conversion ratios are also required to provide constant regulated voltage.

Switched capacitor (SC) DC–DC converters are good candidates for power management units in miniature systems. By utilizing integrated capacitors as passive elements, they can provide fully integrated solutions that are capable of handling microwatts of power. This enables a cost-effective small form factor, which typically cannot be offered with inductor-based buck converters, where one of the following is required: a bulky off-chip inductor [

6,

7,

8]; an expensive on-chip inductor [

9,

10]; or a complicated post-fabrication process [

11]. The large conversion ratio requirement also prohibits the use of low dropout regulators (LDOs) in such systems since the efficiency of an LDO is proportional to its conversion ratio [

12,

13,

14].

However, some challenges must be overcome for SC converters to fulfill the aforementioned requirements. SC converters can provide only rational conversion ratios, which can be represented as

where ‘

n’ and ‘

m’ are integers determined by the converter topology. This implies that SC converters can only provide limited resolution on regulated voltage, which complicates the implementation of DVS for efficient operation. Moreover, maintaining efficient operation in both active and standby modes is also non-trivial: it requires efficient clock generation over a wide frequency range and driving switches with limited voltage swing may be required since the switching loss with full battery voltage swing can be significant in standby modes.

A number of SC DC–DC converter topologies applicable to miniature systems have been reported in recent years [

15,

16,

17,

18,

19,

20,

21,

22]. Many single-stage SC structures [

15,

16,

17,

18,

19] have been introduced that provide very high efficiency but only at a few ratios, which limits their application to a narrow voltage range. A few multi-stage SC converters, such as successive approximation (SAR) [

20], recursive-tertiary [

21], and recursive-binary [

22] DC–DC converters, have been reported that provide high efficiency over a wide output voltage range. However, these converters are only optimized for active operation state, and the minimum load current is on the order of a few microamperes. Therefore, the efficiency of these architectures in standby mode is low. For example, the efficiency of SAR [

20] at near threshold voltage (0.4–0.7 V) degrades drastically to less than 40% when the load current reaches 1 μA or less. A reconfigurable SC structure presented in [

21] achieves a higher number of conversion ratios with fewer SC stages, but with full input voltage (2.5 V) swing switch driving. Such full-swing switch-driving is acceptable with heavy load condition, since conduction loss is the dominant loss. However, with a light load condition in standby mode, which could be the dominant operating mode in heavy duty-cycled wireless sensor nodes (WSN) and IoT systems, switching loss become the dominant loss contributor and driving switches with voltages significantly higher than their threshold voltage can be a waste of power, resulting in inefficient operation in standby mode. Since the WSNs often utilize high energy density batteries with high output voltage (~4 V), unnecessary loss with full-swing switch-driving can be significant.

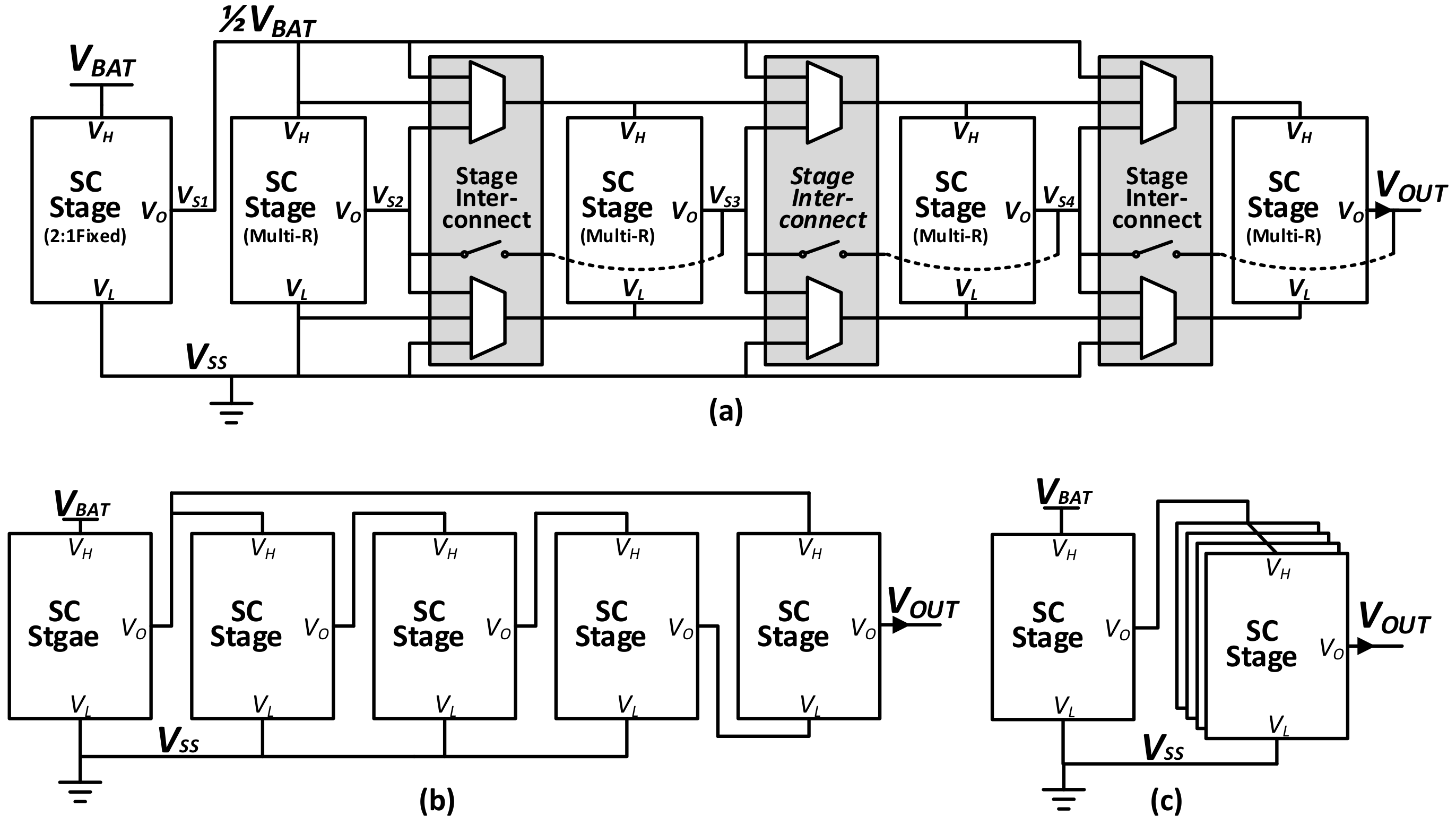

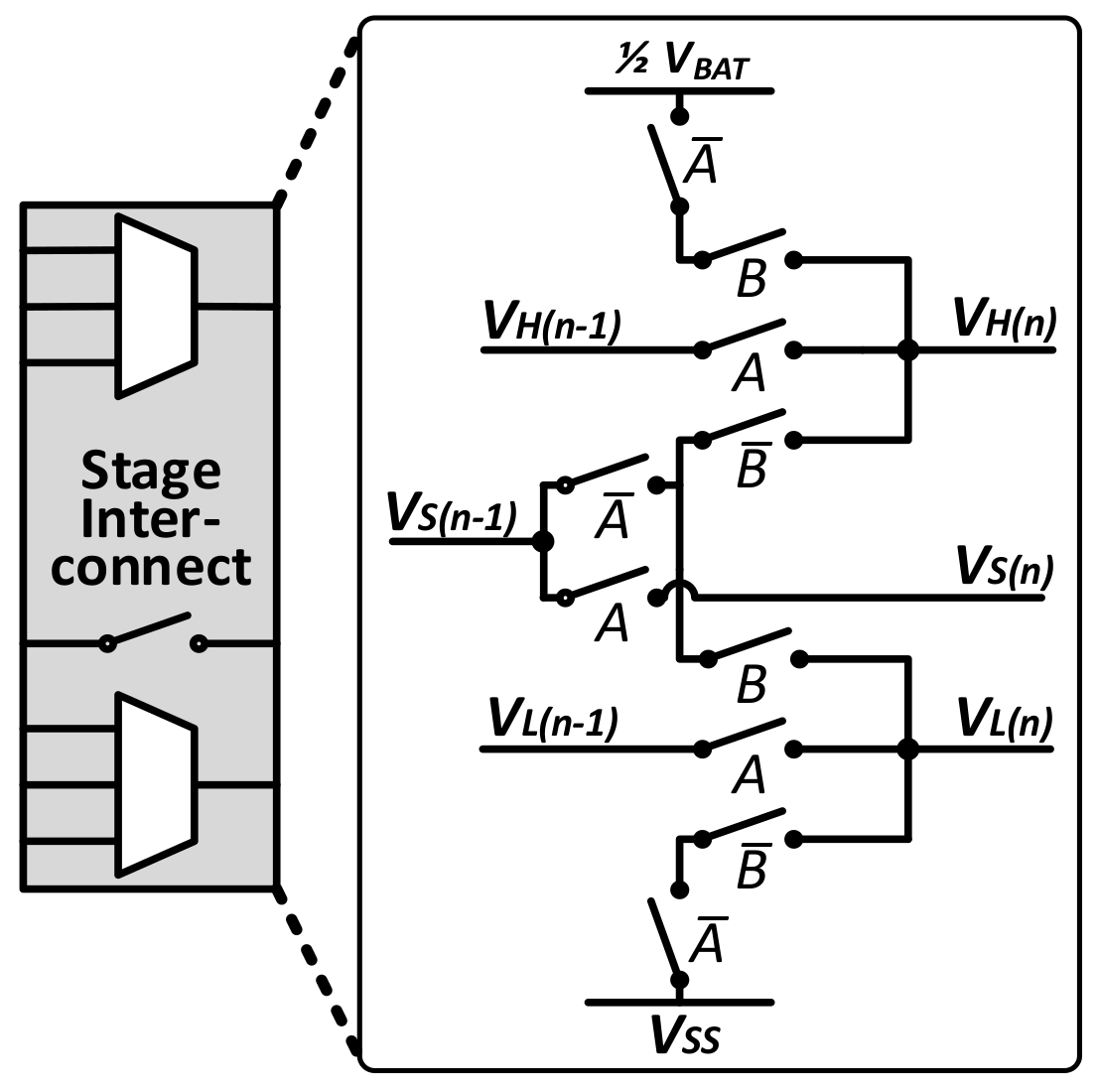

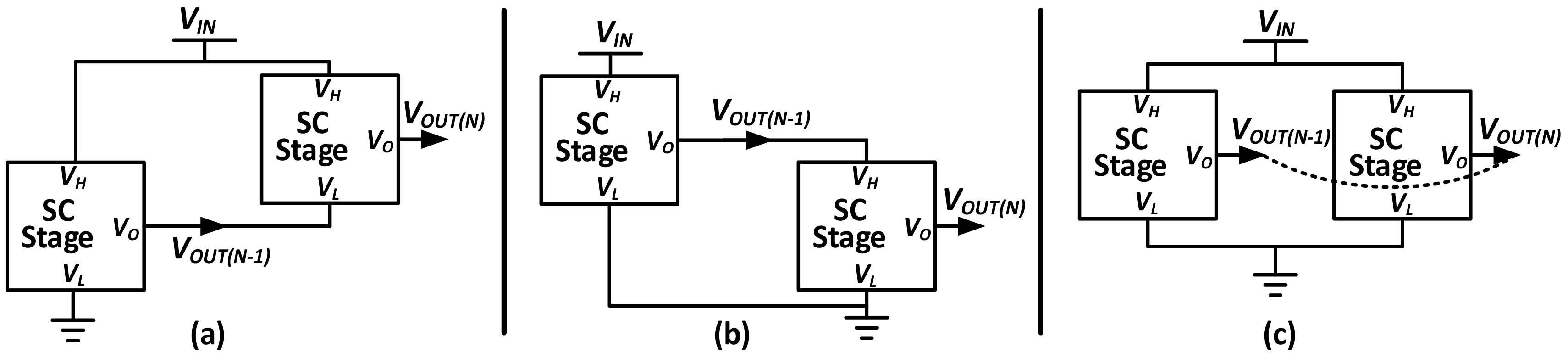

In this paper, a multi-stage and multi-leaf reconfigurable SC converter with load-dependent reconfigurability and limited-swing switch-driving scheme [

23] is presented. The proposed converter consists of multi-ratio multi-leaf SC stages and reconfigurable interconnect, enabling fine voltage resolution with switch width modulation, which is required for DVS over a broad load current range. The reconfigurable stage interconnect (RSI) scheme allows cascaded or parallel connection of stages depending on the output voltage and current demand. The multi-leaf structure allows load-dependent switch size selection, offering a better trade-off between conduction loss and switching loss over a broad current range. A symmetric leakage-based clock generator allows efficient clock generation over a wide frequency range with balanced duty cycle. As switching loss is proportional to the square of the driving voltage, the full input voltage swing driving scheme degrades efficiency at the voltage conversion from high battery voltage. The proposed SC converter switches are driven by a limited voltage swing driving scheme, which makes switching loss independent of input voltage, enabling efficient voltage conversion with high battery voltage.

Various types of batteries can be used for powering miniature systems. Depending upon the battery type, the output voltage may vary from 1.2 to 4.0 V [

15,

16,

17,

18,

19,

20,

21,

22]. This work uses a Li-ion battery where the voltage can vary from 3.6 to 4.2 V. This is typically the maximum voltage level used for stand-alone miniature systems and thus represents the worst case scenario. The same structure applied at a lower input voltage (e.g., 2.0 V) can result in improved efficiency.

For power electronics applications with at least a few milli-watts of power, electromagnetic interference (EMI) analysis, like that presented in [

24,

25,

26] is essential to determine compliance to the EMI regulations for satisfactory operation of nearby circuits. However, the proposed SC converter is implemented for low power applications, where maximum power demand is less than 1 mW, and fully integrated implementation makes EMI negligible. Therefore, EMI analysis of the proposed SC converter has not been considered in this work.

The remainder of this paper is organized as follows:

Section 2 provides a detailed analysis of the loss mechanisms in the SC converter at varying operating conditions. Then the detailed architecture of the proposed converter is presented in

Section 3. In

Section 4, the measurement results are shown to verify the effectiveness of the proposed approach, and

Section 5 concludes the paper.

2. Loss Analysis and Power Delivery Capability of an SC Converter

In SC converters, there are two fundamental loss mechanisms, namely conduction loss and switching loss. As the output load current and voltage change, both of these losses can vary drastically; hence, careful balancing between these losses is required for optimized power delivery. Therefore, analyzing the trade-off between these losses is the first step in implementing an efficient SC converter suitable for operation over wide voltage and current ranges.

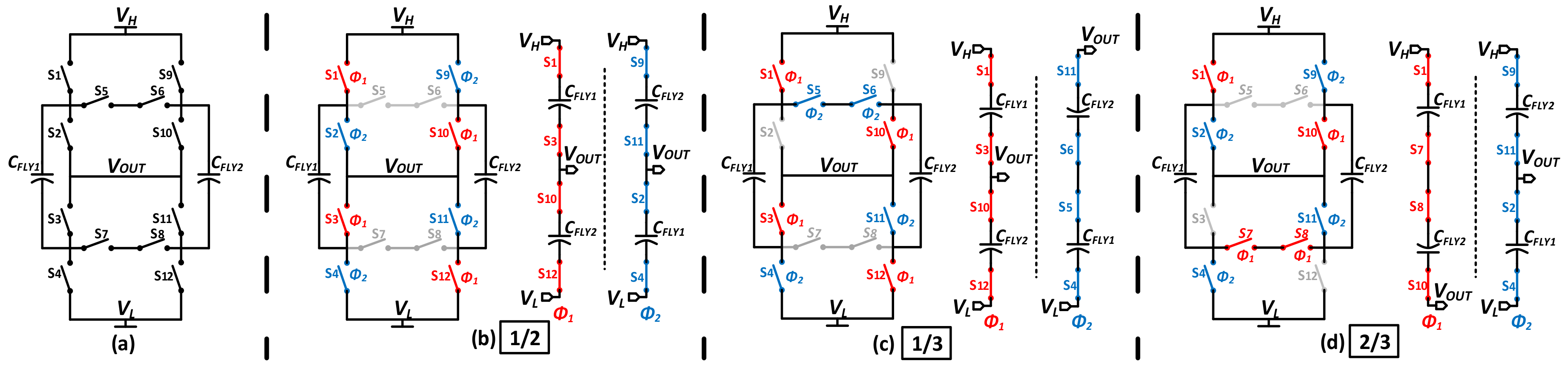

SC converters rely on energy and charge transfer between flying capacitors, which act as voltage sources. Since the voltage conversion is achieved by connecting flying capacitors in series or parallel, the voltage generated by an SC stage is determined by its topology and the summation or subtraction of flying capacitor voltages. Therefore, unlike the inductor-based converters where conversion ratios can be continuously adjusted by controlling the switching frequency or duty cycle, only discrete conversion ratios can be generated with SC converters.

The number of available conversion ratios in an SC stage is determined by the number of flying capacitors and charge transfer phases per operation cycle. For a given number of flying capacitors, more voltage conversion ratios can be implemented by increasing the number of charge transfer phases [

21]. However, this limits the net conduction time of each transistor, resulting in reduced efficiency. For example, each phase lasts up to 50% in a 2-phase operation and up to 33% in a 3-phase operation. Therefore, assuming the same operation frequency, a 3-phase operation requires a larger switch to conduct the same amount of charge in a shorter conduction time, resulting in greater switching loss.

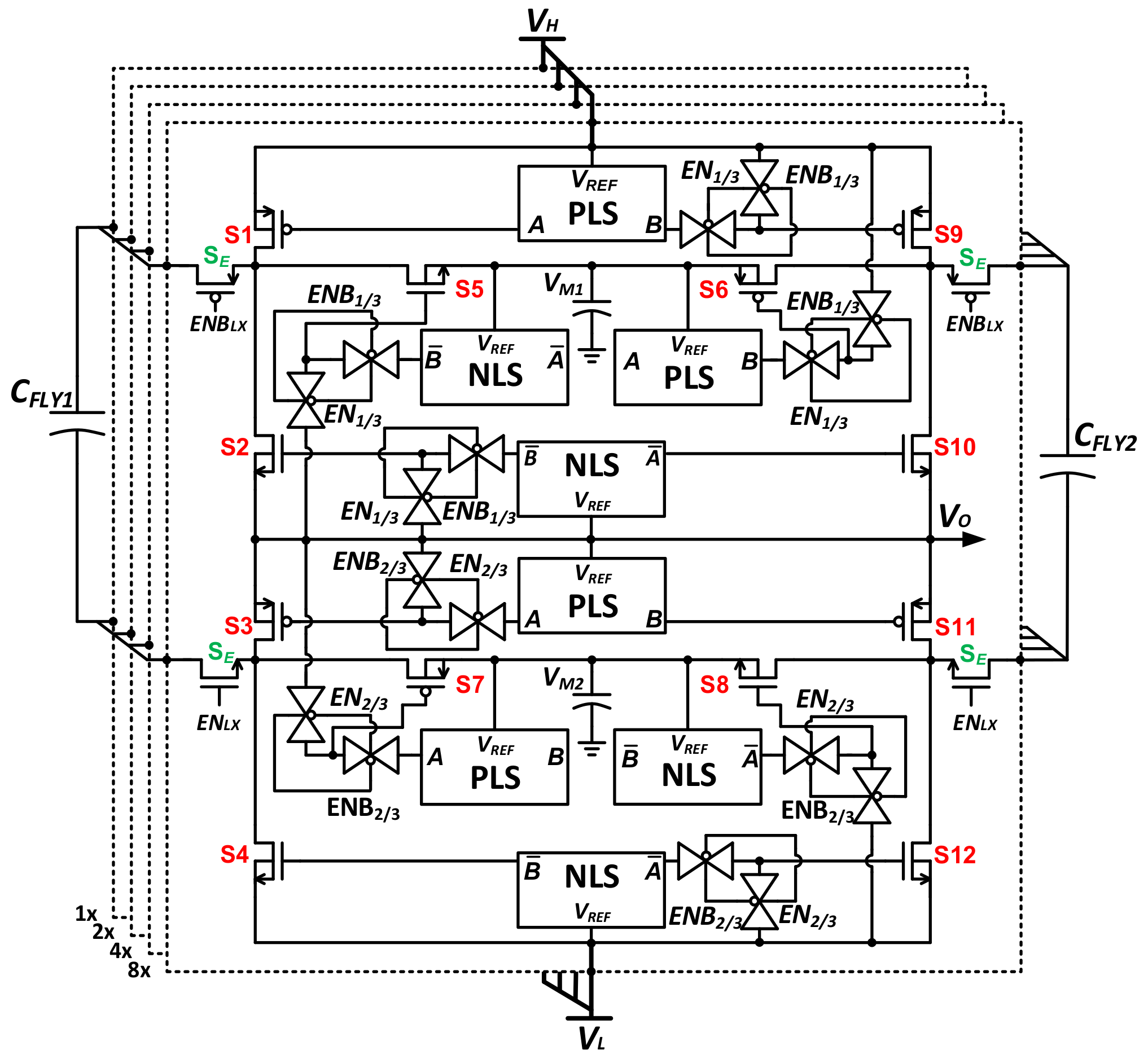

This work focuses on the efficient operation of an SC converter over varying load currents and voltages, including light load cases where the control and drivers are the dominant loss. A 2-phase clock is used owing to the simple drivers and control schemes.

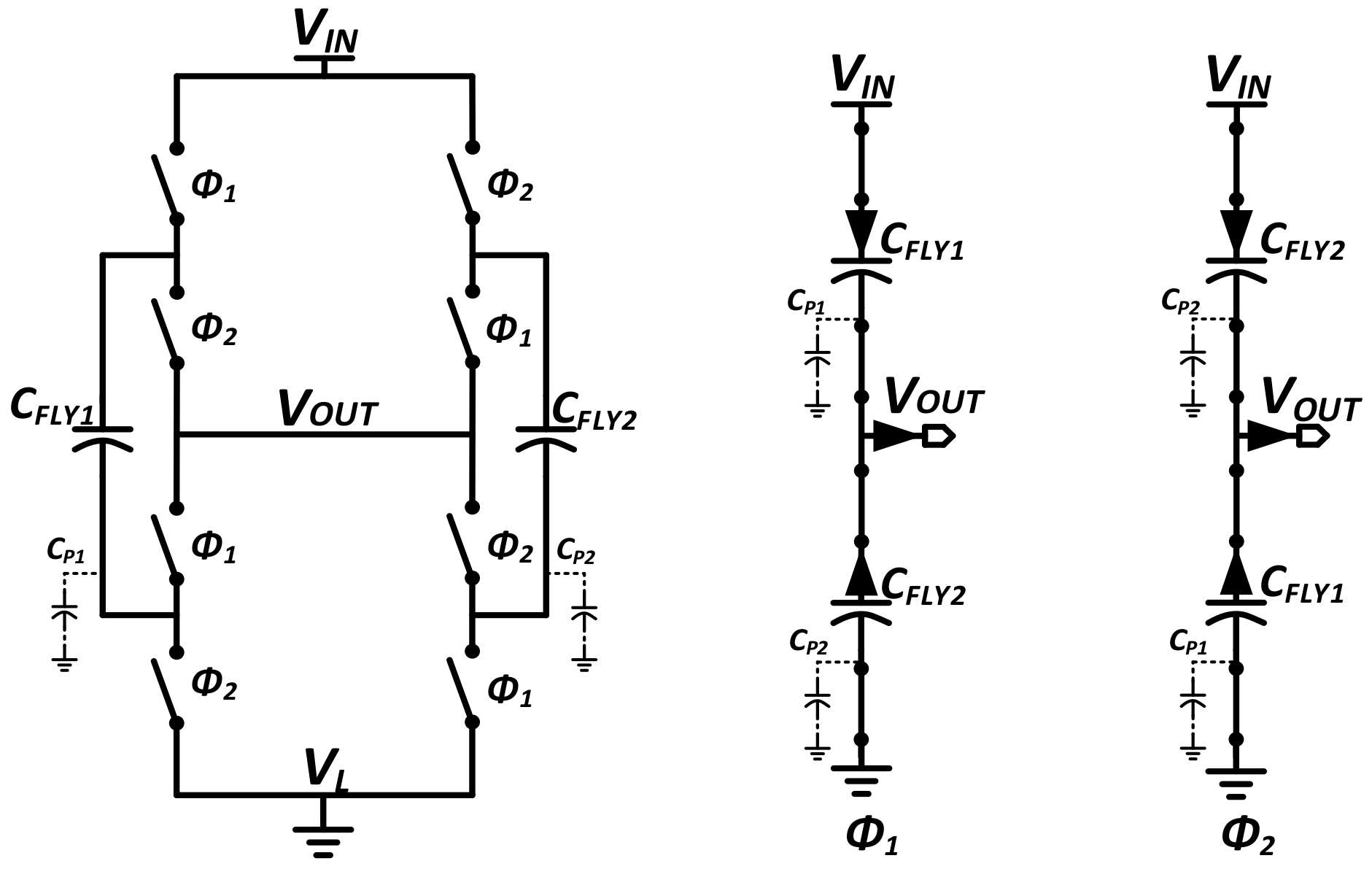

To illustrate the basic tradeoff between switching and conduction loss, a simple 2:1 step-down SC converter, shown in

Figure 1, was analyzed at light and heavy load conditions.

Table 1 provides a list of the parameters used in analysis and their measurement units. The converter presented in

Figure 1 operates with a 2-phase non-overlapping clock. During phase

ϕ1, the top and bottom terminals of

CFLY1 are connected to the battery (

VIN) and output (

VOUT), respectively; thus, drawing charge from the battery as charges are taken at the output node. On the other hand,

CFLY2 is connected between

VOUT and ground (

VSS), supplying charge to the output node. During phase

ϕ2, the flying capacitors switch their positions such that

CFLY2 is charged, and

CFLY1 is discharged. Periodic charging and discharging of the flying capacitors results in ripple voltage (

ΔV) at the flying capacitors, which can be written as

where

ILOAD is the load current, and

fSW is the switching frequency. Such ripple incurs power loss, which can be categorized as conduction loss. This is an inevitable loss in SC converters because power is delivered through charge transfer via transistors, and a voltage difference between source and drain is required for charge transfer to be enabled. The conduction loss due to ripple voltage, as investigated in detail in [

27,

28], can be given as

where

KC is the loss coefficient related to the converter topology. Ideally, switches in SC converters are assumed to have zero resistance, but real switches have finite resistance, which leads to additional conductance loss. Conduction loss due to switch resistance is given in [

27] as

where

RON is the switch resistance per unit width during the “on” state,

WSW is the total width of the switches, and

KSW is the topology-dependent loss coefficient. Therefore, the total conduction loss can be calculated by adding the loss due to voltage ripple and the switch conduction loss as follows:

The other type of loss in SC converters is switching loss. One of the major contributors to switching loss is the parasitic capacitance associated with flying capacitors. For on-chip capacitors, both the top and bottom plates have associated parasitic capacitances. For simplicity, the switching loss associated with the top and bottom plate parasitic capacitances is referred to as bottom plate switching loss (

PSw.Bot) since the bottom plate parasitic capacitance is much larger than the top plate parasitic capacitance in most integrated capacitors. For the converter in

Figure 1, the parasitic capacitor

CP1 associated with

CFLY1 is charged to the output voltage (

VOUT) during

ϕ1. During the following phase,

ϕ2,

CP1 is discharged to ground, resulting in bottom plate switching loss defined as

where

KP is the topology-dependent loss coefficient.

Another type of switching loss is the power consumed for the driving gate capacitances of all of the switches. This loss can be written as

where

VSW is the voltage swing at the gate, and

CGate is the total gate capacitance. Adding Equations (6) and (7) yields the total switching loss (

PSW):

Therefore, adding Equations (5) and (8) provides the total loss in an SC converter (

PLOSS) as follows:

The above equation provides insight on the tradeoff between conduction loss and switching loss in an SC converter. For conduction loss, fSW and WSW are in the denominator, whereas for switching loss, fSW and CGate are in the numerator. Both WSW and CGate are proportional to the switch size. This implies that increasing the operation frequency and transistor width will reduce conduction loss and increase switching loss, whereas decreasing the frequency and transistor width will have the opposite effect.

Meanwhile, the power delivery capability (

PLOAD) of an SC converter can be defined as [

16]

where

KL is the loss coefficient that is dependent upon the SC converter topology, and

Vdrop is the deviation from the ideal no-load voltage (

VNL). Equation (10) indicates that a light load can be provided with a small

Vdrop at a low

fSW, resulting in an optimal operating voltage (

VOPT) near

VNL. In contrast, heavy load operation results in a large

Vdrop at a high

fSW, resulting in a

VOPT much lower than

VNL.

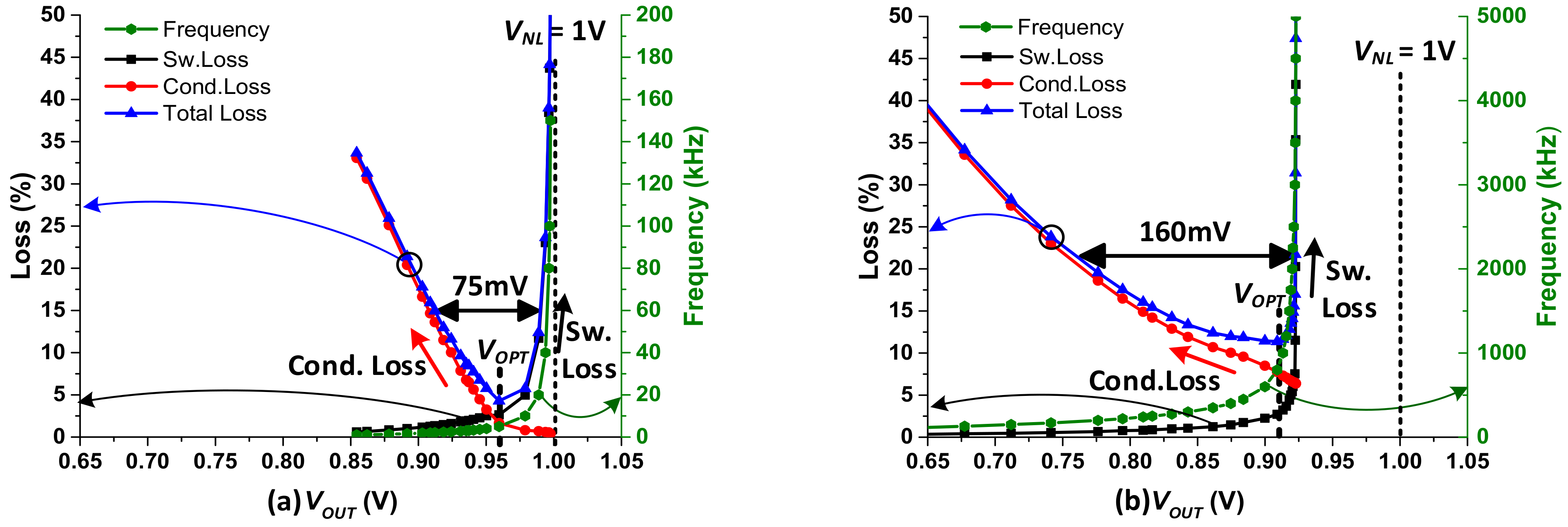

Figure 2 presents the simulation results for a 2:1 down-conversion with 2 V input (

VNL = 1 V) in a single stage of the SC converter shown in

Figure 1. The required operation frequency and power losses expressed as percentages are plotted as functions of the output voltage. For simulation, the parasitic capacitances

CP are kept at 3% of the flying capacitance, which is a typical value for high metal layer metal–insulator–metal (MIM) capacitors.

With a light load of 500 nA, the total loss is minimized at an output voltage of approximately 0.96 V (

VOPT), as shown in

Figure 2a. To increase the output

VOUT above

VOPT, the frequency must be increased exponentially, which results in an exponential increase in switching loss. On other hand, to reduce

VOUT below

VOPT, the frequency must be decreased, lowering the corresponding switching loss. However, under light load conditions, the optimal operation is achieved at low frequency (~8 kHz in the presented case), where the output voltage ripple is sensitive to change in frequency. As the frequency is reduced, the voltage ripple increases drastically, resulting in a sharp increase in conduction loss, as can be found in Equation (2). These factors result in a narrow convex-shaped total loss curve whose

VOPT is close to

VNL for an SC converter under light load scenarios.

When a heavy load of 100 μA is applied to the identical SC converter, the switching and conduction losses change as shown in

Figure 2b. The total loss is minimized at lower

VOPT, which is around 0.91 V with

fSW ≈ 830 kHz. To generate

VOUT higher than

VOPT, the frequency must be increased exponentially. This results in an exponential increase in switching loss, rendering the region between

VOPT and

VNL inefficient. However, under heavy load, the SC converter operates with a higher frequency (830 kHz vs. 8 kHz in this example), and the output ripple is less sensitive to change in frequency compared with the low load case. Therefore, as

VOUT is decreased with lower frequency, the voltage ripple and consequent conduction loss increase at a slower rate. The outcome is a wider convex-shaped loss curve, resulting in wider efficient region around

VOPT compared with the low load scenario.

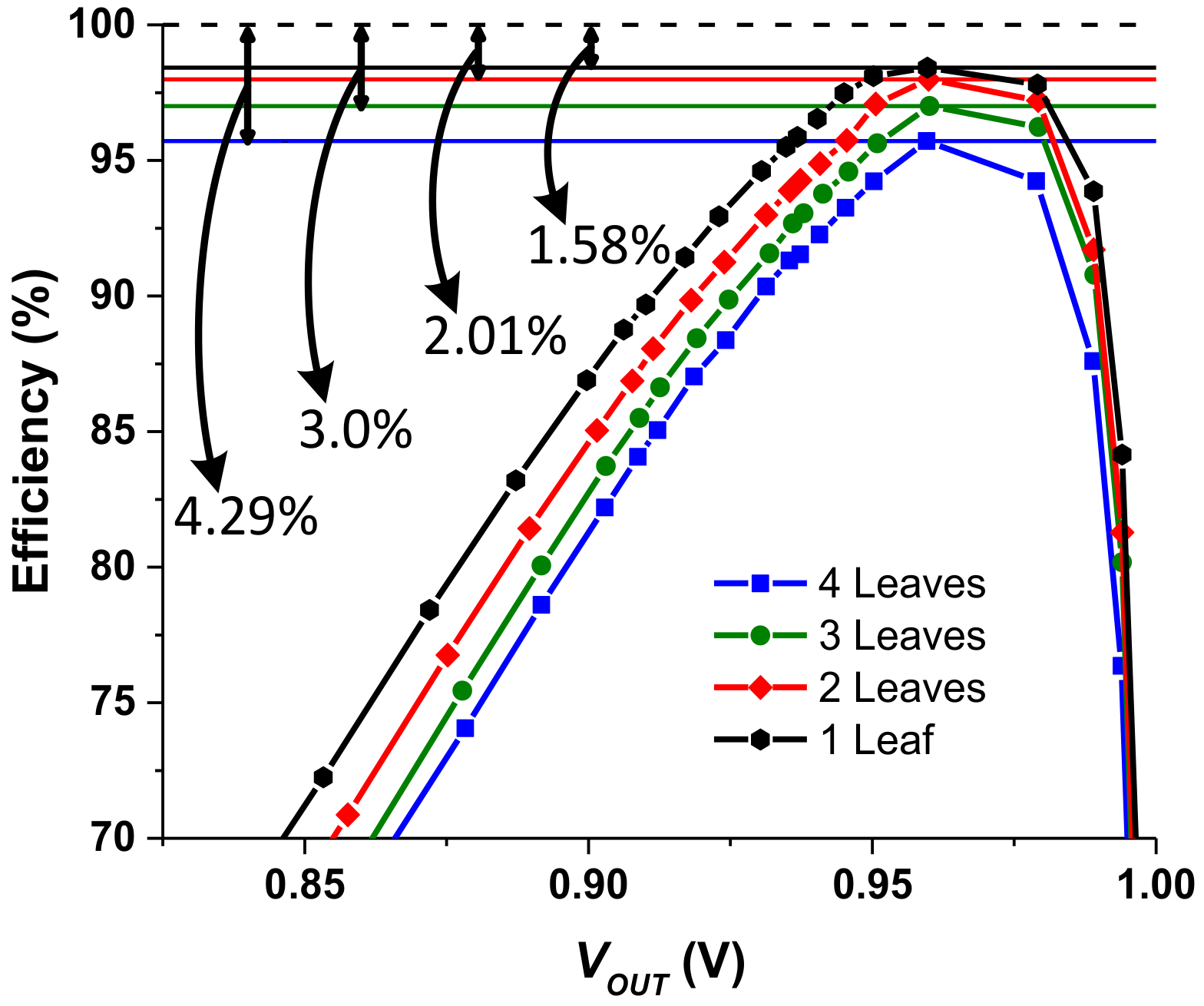

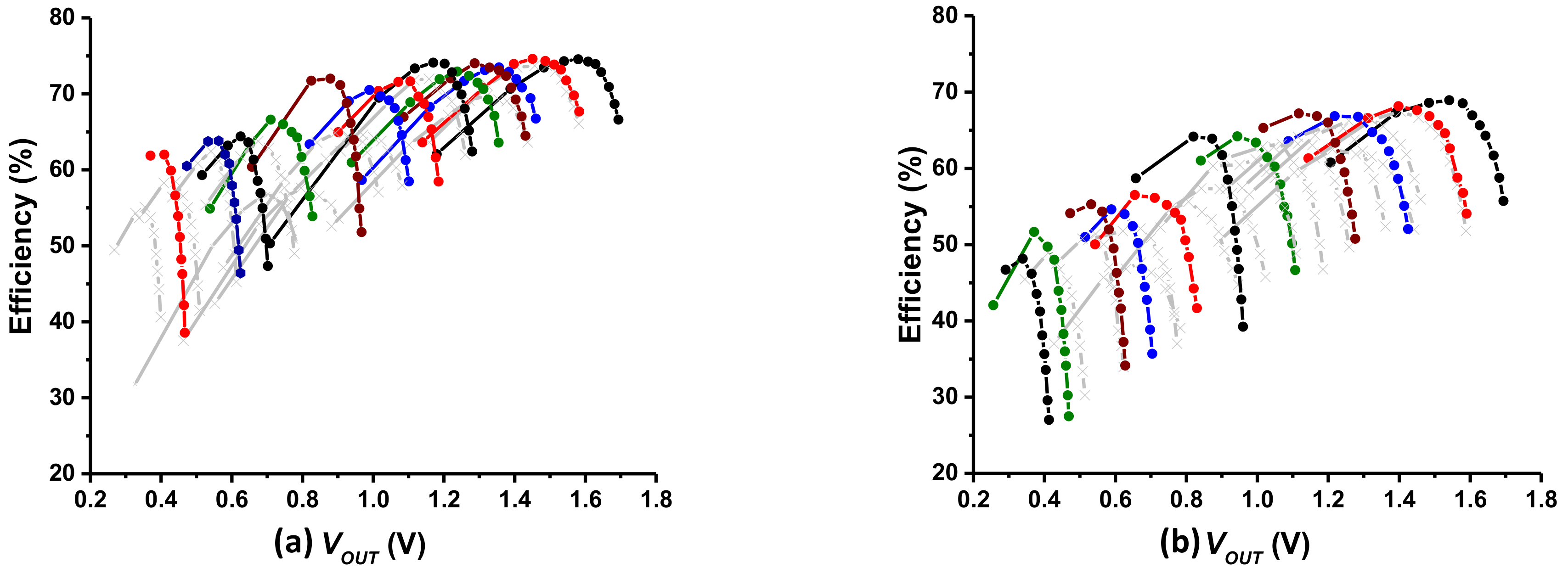

The loss curves in

Figure 2 can be translated into efficiency curves, as shown in

Figure 3 with additional simulation results for intermediate load conditions. The following conclusions can be drawn from these simulation results.

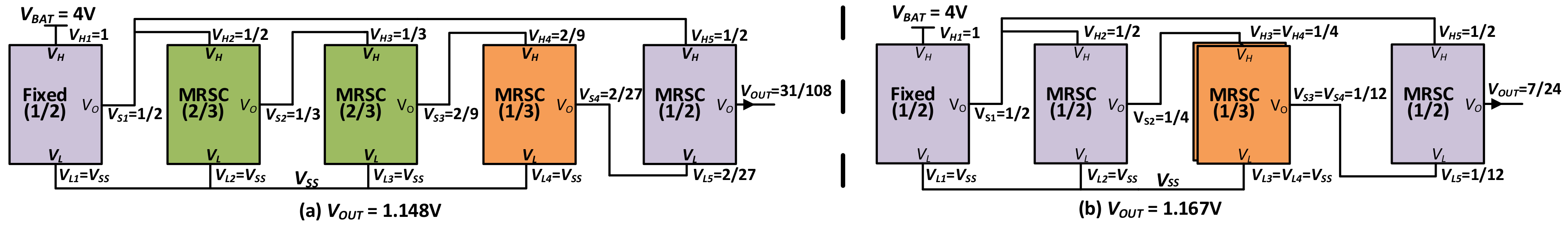

(1) The efficiency curves are narrower under light load conditions than under heavy load conditions. For example, the voltage range that keeps the efficiency within 10% of the peak efficiency is 75 mV for the 500 nA light load and 160 mV for the 100 µA heavy load. This implies that to maintain efficient operation over a given voltage range, more efficiency curves providing different VNL are required for light load conditions. Since VNL is determined by the conversion ratio, to maintain efficient operation for a given VOUT range, more conversion ratios should be provided for light load conditions, and relatively fewer conversion ratios are required for heavy load conditions.

(2) The power loss at the optimum operation voltage (VOPT) at a single stage of the SC converter is significantly higher (11.3%) with a heavy load (100 µA) and lower (4.3%) with a light load (500 nA). This implies that while cascading SC converter stages can provide finer voltage resolution, they result in significant loss under heavy load. Therefore, for heavy load conditions, the number of cascaded stages should be minimized.

Considering the efficiency trends stated above, the following operation strategies can be developed for an SC converter targeted for wide load current and voltage ranges:

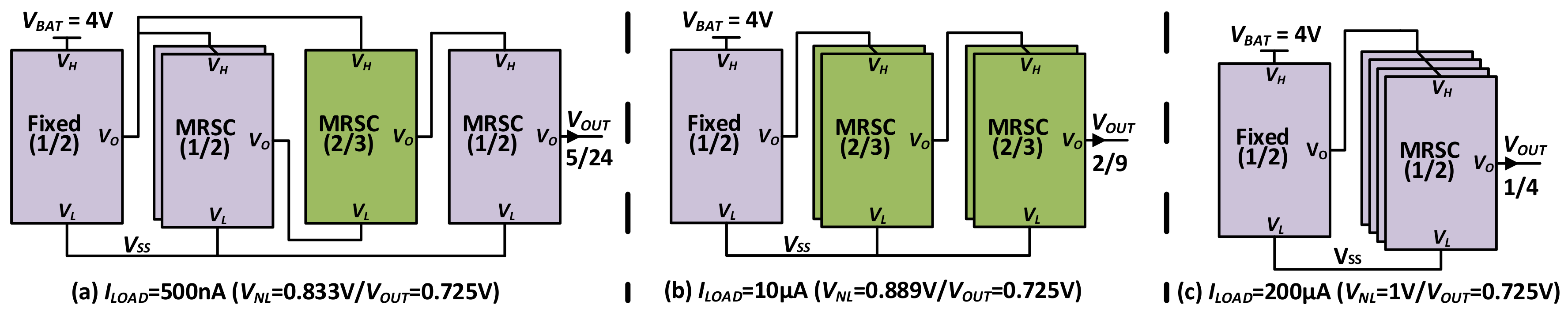

(1) For light load conditions, each conversion ratio is efficient only over a very small voltage range. Therefore, providing many conversion ratios and fine resolution by cascading SC converter stages is preferred since stage loss is small.

(2) For heavy load conditions, each conversion ratio is efficient over a relatively wider voltage range. Therefore, fewer conversion ratios are required, and the number of cascaded stages can be reduced. Since the stage loss is larger, the number of cascaded stages should be minimized. In this case, the stages that are cascaded for providing fine voltage resolution under light load conditions can now operate in parallel configuration. This approach increases the effective flying capacitor and switch size and reduces conduction loss, which is the dominant loss factor under heavy load conditions.

(3) To minimize the number of cascaded stages, an SC stage structure that can provide multiple conversion ratios is preferred over an SC stage with a fixed 2:1 ratio. The maximum number of achievable conversion ratios using a 2-phase clock and two flying capacitors is three [

29]. Therefore, an SC stage topology with three variable ratios is adopted, which can efficiently provide fine resolution with fewer SC stages by limiting conduction loss.

(4) To further optimize loss, especially with the light load conditions, it is desirable to adjust the switch size, i.e., the transistor width, of an SC converter, as shown in Equation (9). By adjusting WSW and CGate, efficiency can be improved by balancing conduction and switching losses.

In

Figure 3, where an identical switch size is used for various load currents, the peak efficiency at

ILOAD = 5 µA appears to be higher than at

ILOAD = 500 nA. This is because the switch size is too large for the 500 nA load, incurring unnecessary switching loss. Therefore, in addition to lowering the frequency for light load conditions, the switch size must also be reduced.

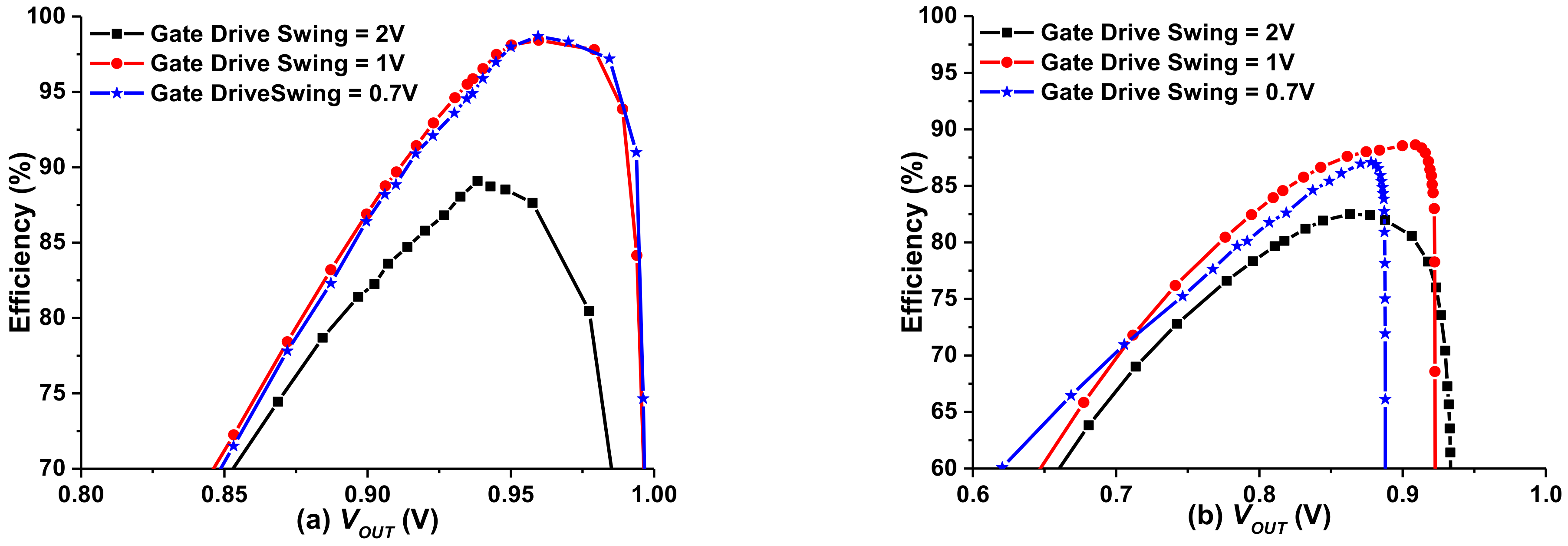

Figure 4 shows the simulation results for the 2:1 converter with binary-sized switches with

ILOAD = 500 nA. With the reduced switch size, peak efficiency improvement is observed under a light load by eliminating the excessive capacitance load of the power switch in Equation (7).

Since the switching loss for switch driving is proportional to the square of

VSW as shown in Equation (7), a switch driving scheme independent of input battery voltage

VIN is desirable and the optimal gate driving voltage depends upon the threshold voltage of switch.

Figure 5 shows how efficiency changes with varying switch driving voltage swing for a 2:1 converter at

ILOAD of 500 nA and 100 µA respectively. With both low and high load conditions, driving switches with unnecessarily high

VSW of 2 V significantly drops the efficiency due to a large switching loss. However, with a high 100 µA load, utilizing too low

VSW could also be a problem since the insufficient overdriving voltage can make

RON high, increasing conduction loss. Therefore, proper

VSW, which is technology dependent, should be carefully chosen to optimize both low and high load conditions.

4. Measurement Results

A prototype test chip was fabricated in a 180 nm complimentary metal-oxide-semiconductor (CMOS) process. An effective die area of 1.525 mm

2 was utilized by the converter, which is dominantly occupied by 2.09 nF of on-chip MIM capacitors. The micrograph for the fabricated test chip is presented in

Figure 17.

The prototype SC converter was examined over a wide load current and voltage range. The experimental results presented in

Figure 18 and

Figure 19 illustrate the importance of switch width modulation using multi-leaf structure under light load conditions. In these figures, the load current is fixed, and the operation frequency is swept for each conversion ratio configuration to measure the corresponding output voltage and efficiency. Colored curves represent the efficiency trend for configurations whose efficiency is the highest at least for one output voltage. Gray curves represent efficiency trends for configurations whose efficiency is never the optimal at any given output voltage and hence can be ignored. Under a light load (500 nA), minimum activation of switches is desired to minimize switching loss. Therefore, enabling only the smallest leaf is optimal (

Figure 18a) and delivers output with approximately 13–20% higher efficiency compared with enabling all of the leaves (

Figure 18b). However, under a higher load of 5 µA, two leaves are required to be activated to achieve comparable efficiency (

Figure 19a) since enabling only the smallest leaf now incurs significant conduction loss. If too many leaves are activated, the efficiency drops again due to a large switching loss, as shown in

Figure 19b, where all leaves are activated.

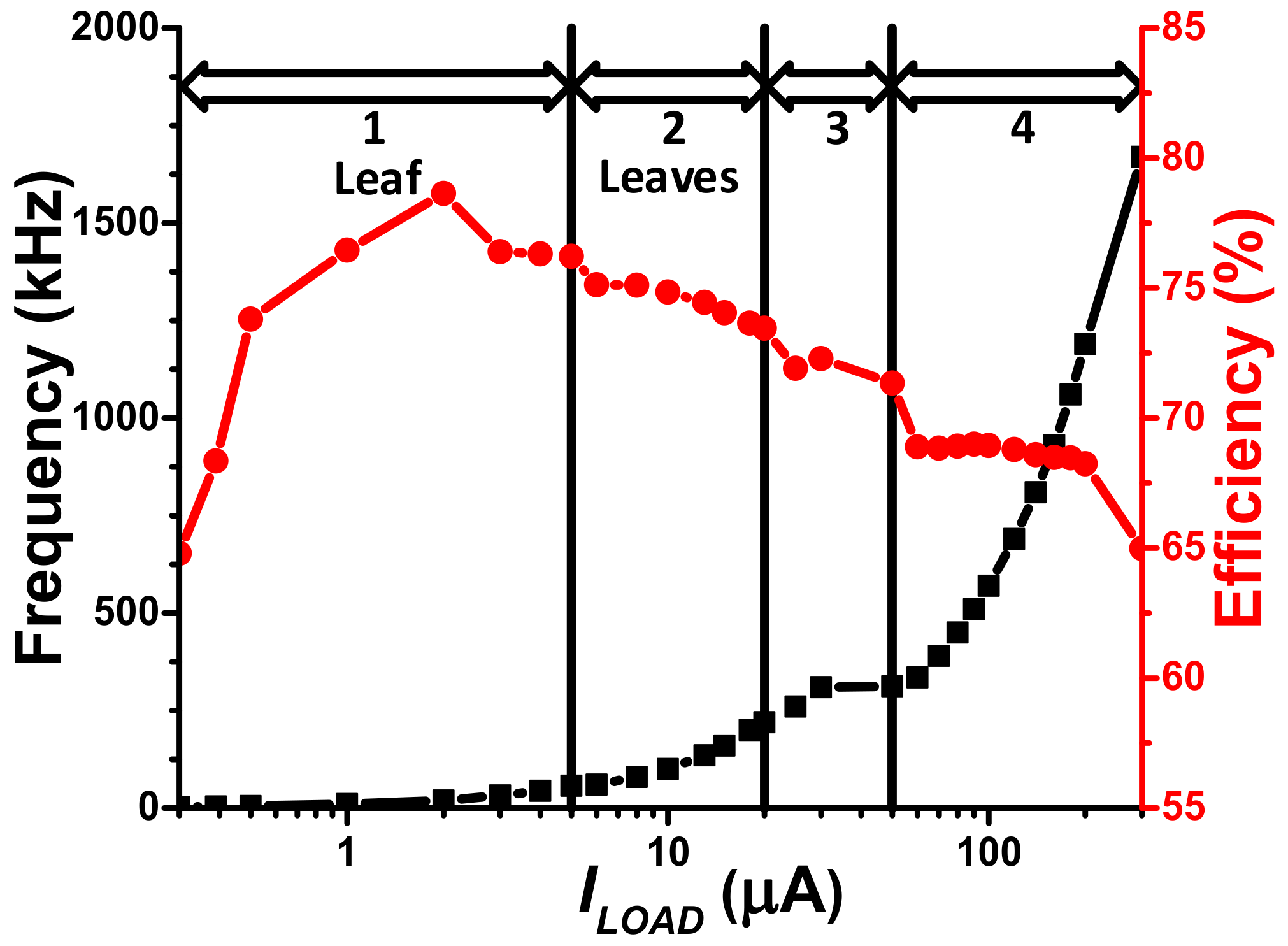

The effectiveness of switch width modulation by using multiple leaf structures is summarized in

Figure 20, where

VOUT = 1.2 V is generated from

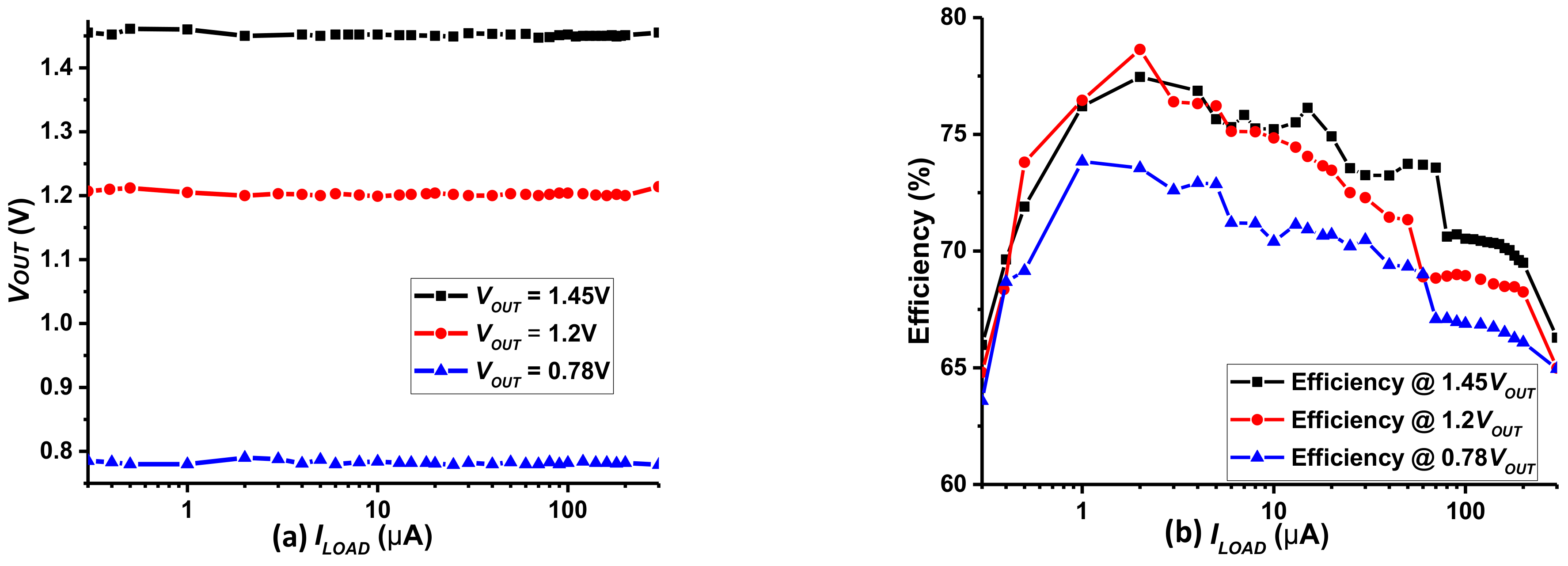

VBAT = 4.0 V. For each load current point ranging from 300 nA to 300 µA (1000×), the optimal conversion ratio, operating frequency and number of active leaves are selected, and the corresponding efficiency and operating frequency are plotted. As load current increases, the optimal operating frequency also increases, and additional leaves should be gradually added to compensate for the increasing conduction loss.

Figure 21a shows the experimental results for regulated output voltage levels when targeted for 0.78 V, 1.2 V, and 1.45 V with load current ranging from 300 nA to 300 µA. The optimal configuration is identified and measured for each load current point. The maximum regulation error was kept under ±16 mV thanks to the fine resolution provided with multi-ratio multi-stage topology.

Figure 21b shows the corresponding efficiency trends. The proposed SC converter could operate with peak efficiencies of 73.9%, 77.96%, and 77.5% and minimum efficiencies of 63.58%, 64.79%, and 65.98% for target output voltages of 0.78 V, 1.2 V, and 1.45 V, respectively.

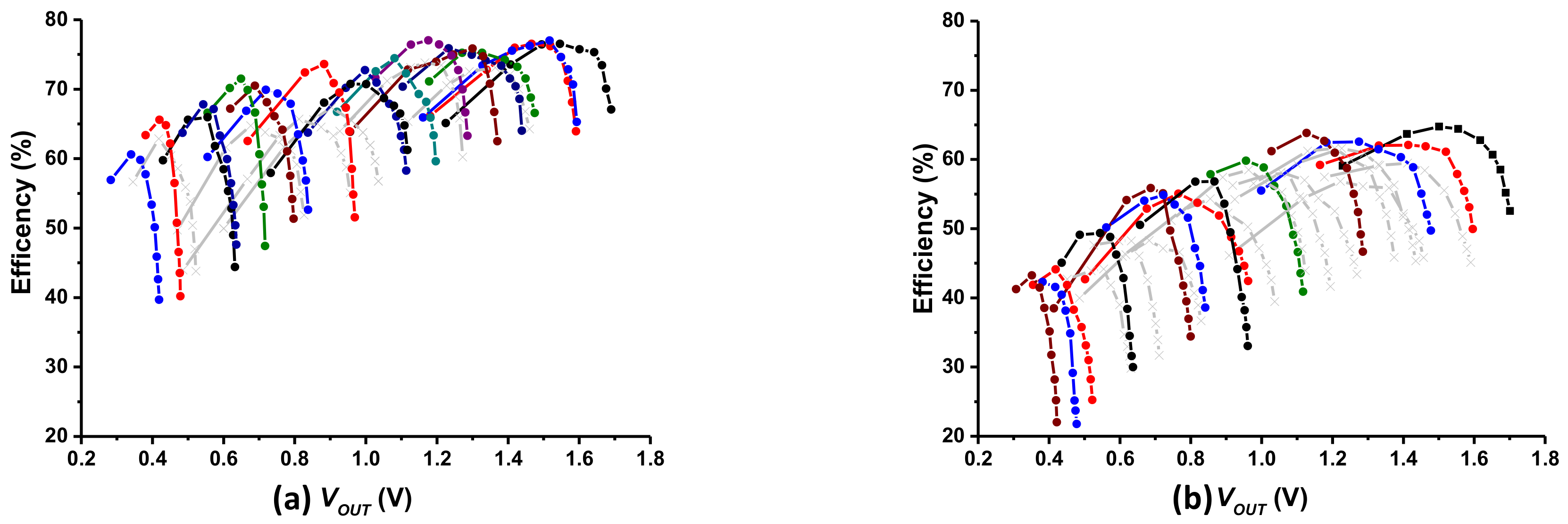

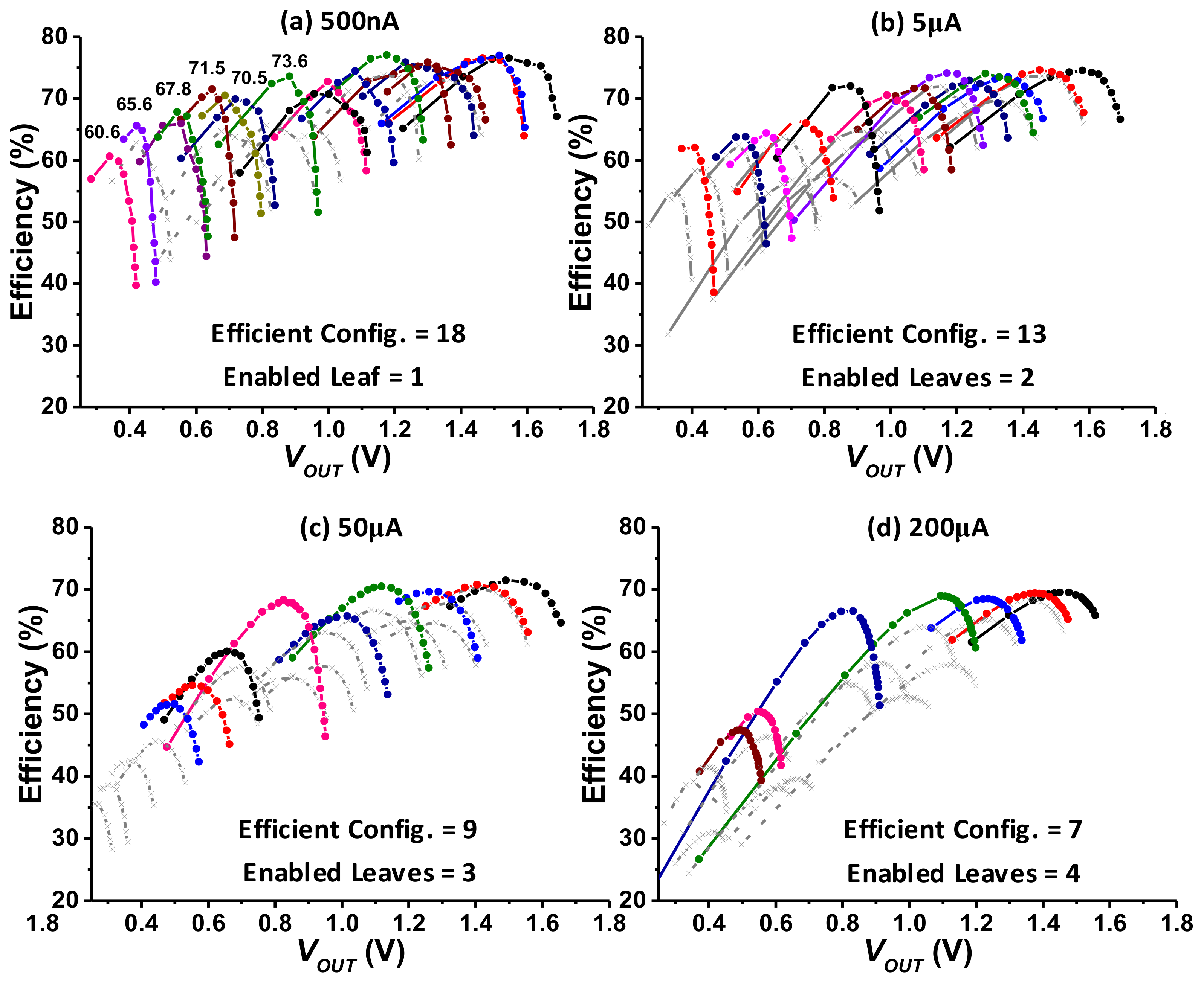

To verify the effectiveness of the proposed SC converter in providing dynamic voltage scalability in miniature sensors, the efficiency was measured over a target output voltage range of 0.4–1.6 V under various load conditions. The efficiency plots in

Figure 22 show the efficiency trend for each conversion ratio configuration. The same color/grey notation in

Figure 18 and

Figure 19 is used in these plots.

Under the light load condition of 500 nA, each configuration is only effective for a narrow output voltage range, resulting in narrow efficiency curves. This implies that many conversion ratio configurations are required to maintain high efficiency over a wide DVS range, validating the loss analysis discussion presented in

Section 2. With the fine voltage resolution, 18 configurations were required to keep conversion efficiency above 60% for the target voltage range, and the peak efficiency was >77% at

VOUT of 1.176 V and 1.517 V. Only the smallest leaf was enabled to deal with the light load. Efficient operation under such light load conditions is essential for efficient miniature system operation during typically long standby.

When the load current is increased to 5 µA, the efficiency curves become slightly wider, and the number of required ratio configurations is reduced to 13. A second binary sized leaf is enabled to balance conduction and switching losses. The minimum efficiency for the entire output range was 62%, and the peak efficiency was 74.1%, as shown in

Figure 22b.

As the load is further increased to 50 µA, three leaves need to be activated. Since the efficiency curves become even wider, fewer conversion ratios are required. This means less cascaded stages are required, and more stages can be parallel-connected to improve efficiency. Such parallelism facilitates high efficiency at high output voltages. However, for low output voltages, where many cascaded stages are required to form small conversion ratios, efficiency drops due to increased conduction loss. For a miniature sensor system, this is not a critical drawback since digital circuits with DVS tend to operate at high voltage when there is large current demand, i.e., computation demand. As shown in

Figure 22c, the proposed SC converter could operate with >64% efficiency for an output range of 0.7–1.6 V with 50 µA load. When the voltage drops to 0.4 V, the efficiency drops to 47%, which is still high compared with the state-of-the-art systems [

20,

21] thanks to multi-leaves stage structure, stage configurability and cascading SC stages or parallel interconnect control.

With a heavy load current of 200 µA, all available leaves are activated, and only a few configurations inheriting parallel interconnection of SC stages are used to cover the entire output range, as shown in

Figure 22d. From the detailed efficiency trend analysis for wide load current and voltage ranges, the observation made earlier in the loss analysis section that, “cascading SC stages are required for efficient operation under light loads, whereas parallelism is required for heavy loads” is confirmed.

A performance comparison of the proposed architecture with state-of-the-art structures including successive approximation (SAR) [

20], recursive tertiary (RTC) [

21], and recursive binary (RBC) [

22] converters is summarized in

Table 4. The proposed SC converter provides finer 16 mV effective voltage resolution as compared to the SAR with fewer stages, resulting in more efficient operation by limiting conduction loss. The peak efficiency of the proposed converter is lower than recursive architectures (RTC, RBC), but finer granularity and

VIN independent driving scheme results in significant efficiency improvement for light load conditions, which is crucial for duty-cycled miniature sensor systems. The proposed converter maintains efficient operation for very low output voltages even at higher

VIN level, which is the major contribution of this work. Other SC converters in [

15,

16,

17] are efficient SC converter designs but are based upon a single SC stage. Therefore, only few conversion ratios can be provided, making them unsuitable for DVS implementation.