Highlights

What are the main findings?

- An analysis of datasheets of power MOSFETs indicates that the accuracy of thermal resistance measurements depends on the shortest thermal time constants of the tested transistors.

- Measurements performed using the system built by the authors indicate that electrical transients and oscillations are observed for up to several milliseconds, which may significantly affect measurement accuracy.

- The measurement error of thermal resistance is generally higher for power MOSFETs made of silicon carbide and gallium nitride than for silicon transistors.

What is the implication of the main finding?

- The measurement of the thermal sensitive electrical parameter (TSEP) during thermal resistance measurements of power MOSFETs should start only after electrical transients and oscillations have faded out. In the investigated system, this occurs up to 2.5 ms after the switchover from transistor heating to TSEP recording.

- The measurement error of thermal resistance for power MOSFETs made of silicon carbide is higher than for devices made of silicon or gallium nitride.

Abstract

When designing power electronic systems, it is crucial to correctly estimate the junction temperature of semiconductor devices, particularly power MOSFETs, under actual operating conditions. Thermal resistance is a parameter that characterizes the ability of these devices to dissipate internally generated heat under steady-state conditions. Determining the value of this parameter under specific cooling conditions requires dedicated measurements. This paper considers the widely used indirect electrical method of measuring thermal resistance. The influence of the dynamic properties of the measurement system, including the A/D converter, on the measurement error of the thermal resistance of power MOSFETs was analyzed. Using the constructed measurement system, it was demonstrated that, depending on the semiconductor material of the tested transistors, different error values were obtained, even with the same system configuration. The largest errors were observed for transistors made of silicon carbide. It was further shown that, with the applied A/D converter module, the measurement error can be limited to a few percent if recording of the thermal sensitive electrical parameter (TSEP) begins soon enough after the transients caused by the switchover from heating to TSEP measurement have fully decayed.

1. Introduction

MOSFETs are currently the most widely used semiconductor devices in power electronic systems operating at voltages of up to several hundred volts [1,2]. These devices are fabricated from different semiconductor materials, such as silicon (Si), silicon carbide (SiC), and gallium nitride (GaN) [3,4]. During operation, their junction temperature (Tj) is higher than the ambient temperature (Ta) due to self-heating [5]. The difference between Tj and Ta under steady-state conditions is determined by the thermal resistance (Rth) [6,7,8] of the transistor and the power losses (P) within the device.

Thermal resistance characterizes the ability of a semiconductor device to dissipate internally generated heat to its surroundings [9]. Its value depends on the properties of the materials used in the device structure, the mounting method, and the cooling system, which may be passive or active [10,11]. Power MOSFET manufacturers provide thermal resistance values in datasheets; however, these values are limited to boundary conditions, i.e., ideal case cooling (Rthj-c) or operation at natural convection of the device case (Rthj-a) [12]. Under real operating conditions, the actual thermal resistance lies between these extremes. Determining the Rth value under specific conditions (mounting method, type of cooling system, etc.) is therefore necessary, for example, to optimize the cost and design of the cooling solution [13].

Typically, Rth is measured using the indirect electrical method [12,14]. This method relies on the dependence of a selected electrical parameter—the so-called thermal sensitive electrical parameter (TSEP)—on the junction temperature of the device [15,16]. The procedure involves heating the device under test until thermal steady state is reached, and then measuring the TSEP during the cooling process. Due to the step-like change in the operating point of the transistor, both electrical and thermal transients occur simultaneously in the system.

For power MOSFETs, the following parameters are used as TSEP [7]: the gate-source voltage VGS for the transistor operating in the saturation range at a fixed drain current, the voltage VF across the forward-biased diode at a fixed forward current, or the on-channel resistance RDSON. Each of the mentioned parameters has a different temperature dependence and sensitivity [17]. In particular, the use of RDSON as TSEP for transistors made of SiC or GaN is a significant problem due to the very low value of this parameter—comparable to the resistance of the leads and connections [18]. Therefore, further considerations are limited to the VGS voltage acting as TSEP.

Measuring the TSEP after heating requires a step change in the current flowing through the transistor [19,20]. Because this change induces both electrical and thermal transients, it is necessary to wait a certain period before measurement. This delay should be long enough to allow electrical transients to vanish, but short enough to minimize the reduction in junction temperature.

The problem of applying indirect electrical methods is widely described in the literature, e.g., in [21,22,23,24,25,26,27,28,29,30,31,32,33,34,35,36,37,38]. Paper [21] concerns high-resolution temperature mapping in a p-GaN HEMT die while dissipating high-density power in this die. Measurements were performed using thermoreflectance microscopy. Paper [22] concerns submicron temperature mapping of AlGaN/GaN HEMTs under low and high current conditions. The usefulness of Raman thermography for comparing the accuracy of optical and electrical methods was demonstrated. Paper [23] presents the results of dynamic thermoreflectance studies for the gate temperature in GaN HEMTs operating under switching conditions.

In turn, in [24], an indirect electrical method for determining the junction temperature and Rth in GaN HEMTs was presented. It was indicated that the proposed measurement method is useful when optical methods are difficult to use, e.g., for transistor dies mounted in packages. In [25], the problem of determining the thermal resistance of GaN HEMTs using an indirect electrical method is considered, which utilizes parameters such as the VGS voltage and the gate resistance RG. The cited paper also discusses the advantages and disadvantages of using other TSEPs and calibration procedures. Paper [26] describes a technique for measuring the transient thermal impedance Zth(t) of a GaN HEMT based on frequency separation of the thermal response by measuring the gate resistance. Paper [27] analyzes the problem of monitoring the transient thermal response of AlGaN/GaN HEMTs. The research used the transient thermoreflectance imaging method with a switched power supply.

In [28], the problem of measuring Zth(t) of GaN HEMTs was described. The transient thermal thermoreflectance method was used in the measurements. The studies were carried out over a wide range of ambient temperatures. The measurement results were compared with the results of FEM modeling and compact modeling. In [29], the analysis of thermal parameters (Rth, Zth(t)) of packaged GaN transistors is considered. The considerations are carried out for different cooling systems and also include studies of the quality of the semiconductor die assembly process in the packages.

Paper [30] presents a method for measuring Zth(t) of GaN HEMTs with a p-type gate. In the presented method, the VGS voltage is used as the TSEP. Paper [31] describes the methodology for measuring Zth(t) and determining the thermal time constants of GaN HEMTs using Raman microscopy. Paper [32] considers the problem of determining Rth of a GaN HEMT using de-trapping characteristics. Drain-current recovery times are used for this purpose. Paper [33] presents a fast method for measuring Rth of a GaN HEMT using TSEP. The studies were carried out for a high VDS value. Paper [34] indicates such thermally sensitive parameters of GaN HEMT transistors as threshold voltage, substrate diode forward voltage, and saturation voltage. The measurement sensitivity using each of the considered parameters was analyzed.

In [35], a method for measuring the thermal resistance of GaN HEMTs using the modulation method was described. The VGS voltage and the RDSON resistance were used as the TSEP. In [36], a method for monitoring the transistor junction temperature was described using the maximum value of the di/dt derivative as the TSEP. Paper [37] describes a method for determining the thermal resistance of GaN HEMTs based on measured dynamic characteristics of the transistor’s output conductance. Paper [38] proposes a high-accuracy thermal resistance measurement method for GaN HEMTs based on a heating power modulation strategy, called the harmonic pulse width sub-threshold (HPWS) method. The sensitive linear correlation between the sub-threshold swing of GaN HEMTs and temperature is utilized, and the turn-off transients of the heating power signal are sampled to extract the thermal resistance through frequency domain scanning of the heating signal modulation.

As it is visible from the presented literature review, very often VGS voltage is used as the TSEP. Classical studies [39,40] indicate that, for silicon transistors, the TSEP can reasonably be measured at two points in time (100 μs and 200 μs), with extrapolation of the TSEP(t) curve back to t = 0 using a square-root approximation. The classical square root extrapolation of the measured values of TSEP cannot be usable if the waveform TSEP(t) includes oscillations and the value of TSEP is measured in two moments only. Analysis of datasheets of power MOSFETs made of wide bandgap materials (GaN, SiC) [13,14,15] shows that thermal processes in these devices occur faster than in silicon transistors. Therefore, the dynamic properties of the measurement system are expected to have a significant influence on the obtained Rth values [20,41].

The aim of this paper is to investigate the influence of the electrical time constants of the transistor biasing circuit and the dynamic properties of the A/D converter module in the measurement system on the accuracy of thermal resistance measurements of power MOSFETs fabricated from different semiconductor materials. The systematic studies demonstrating that the thermal resistance measurement error depends significantly on all considered factors were conducted. Furthermore, it was theoretically and experimentally investigated, compared, and evaluated the Rth measurement errors for transistors made not only of silicon but also of modern wide-bandgap materials.

Section 2 describes the measurement method and system. Section 3 presents the relationships between the measurement system parameters and the thermal properties of the tested transistors, and their influence on the Rth measurement error. Section 4 provides the results of experimental studies on selected transistors.

2. Measurement Method and System

The thermal resistance of power MOSFETs is typically measured using the indirect electrical method [39,42]. The role of the thermal-sensitive electrical parameter (TSEP) can be played, for example, by the gate-to-source voltage vGS at a fixed drain current in the saturation region, or by the forward voltage vF of a forward-biased freewheeling diode at a fixed current value [17,42]. For both TSEPs, the nonlinear thermometric characteristics TSEP (Tj) are observed. The slope of these characteristics, and thus the measurement sensitivity, is higher when vGS is used as the TSEP [17].

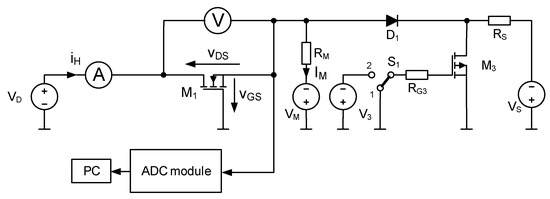

The measurement system used in this study is shown in Figure 1. It enables Rth measurements with vGS as the TSEP. In the figure, transistor M1 is the device under test (DUT).

Figure 1.

Diagram of the system for measuring Rth of power MOSFETs.

The system consists of three main functional blocks: a DUT biasing circuit, an ADC module, and a PC. The biasing circuit sets the operating point of the tested MOSFET during the measurement procedure.

In this system, the USB-2404-60 ADC module manufactured by Measurement Computing (Norton, MA, USA) is used to acquire vGS [43]. This module has four independent measurement channels, each equipped with a 24-bit delta-sigma ADC, and supports sampling rates from 1.613 kS/s to 50 kS/s. The input voltage range is ±60 V. The module is controlled using a PC with the proprietary MCScan software [17,43]. An ammeter and voltmeter included in the system play a supplementary role, measuring the power losses in the DUT during the heating phase.

The Rth measurement procedure consists of several steps:

- Measuring the thermometric characteristic VGS(Tj) of the DUT placed in a thermostatic chamber, biased at the operating point QM = (VDSM, IM), with switch S1 in position 2.

- Performing nonlinear regression to calculate the coefficients a, b, and c of a quadratic function approximating the dependence Tj(VGS).

- Heating the DUT until thermal steady state is reached (transistor biased at QH = (VDSH, IH), with power losses P = VDSH·IH, switch S1 in position 1).

- Switchover of the biasing circuit from heating to TSEP recording by changing the position of switch S1 from 1 to 2. This changes the operating point of the transistor from QH to QM = (VDSM, IDM). At this step, the value VGSH corresponding to the junction temperature is recorded immediately after the switchover.

- Calculating Rth from the measurement results using the following formula [17]:where VGSH is the gate-to-source voltage measured as soon as possible after the switchover of the measurement system.

During the transition from transistor heating to TSEP recording, both electrical and thermal transients occur due to the change in the operating point of the DUT and the presence of parasitic inductances and capacitances in the system. In practice, decaying oscillations of vGS are observed after the switchover. The vGS value used for the Rth calculation (VGSH) can be reliably determined only once these oscillations have subsided.

3. Estimation of the Measurement Error

Considerations on the error in measuring the thermal resistance of power semiconductor devices using the indirect electrical method are presented, among others, in [17,44]. Using the total differential method, it was shown that the relative error in measuring the thermal resistance Rth is the sum of the relative errors in measuring the temperature rise (Tj − Ta) and the dissipated power.

The error in determining the temperature rise depends on the accuracy of approximating the Tj(vGS) characteristic of the tested transistor and on the accuracy of the VGSH measurement. The latter is related not only to the resolution of the ADC module but also to the value of the voltage VGSH used for the Rth calculation. Since this value can be obtained only after the decaying oscillations have ceased, the measurement is delayed by a time td. While the error component resulting from the resolution of the ADC is small and easy to quantify, the error component caused by the delay depends on how much Tj decreases before a reliable TSEP measurement can be performed. This decrease is determined by the steady-state value of Tj after heating the transistor up and by the thermal time constants of the transistor and its cooling system. These thermal time constants characterize the dynamics of the heating and cooling process of the tested transistor. In particular, after a sudden shutdown of the power dissipated in the transistor, its junction temperature begins to decrease. The rate of temperature decline depends on the values of the thermal time constants. The smaller these values, the greater the temperature drop after the same time td, and consequently, the greater the measurement error.

As shown in [45,46], thermal time constants span a very wide range (from microseconds to thousands of seconds) and are associated with individual elements of the heat flow path (semiconductor die, package, PCB, heat sink, etc.). Only the shortest thermal time constants—those related to the semiconductor structure—have a real influence on the Rth measurement error. To estimate this error, the classical approximation of the transient thermal impedance Zth(t) [46,47] was used. The time response of Zth(t) corresponds to the time response of the junction temperature for a step power dissipation. It can be expressed as follows:

where ai is the weighting factor associated with the thermal time constant τthi, and N is the number of thermal time constants.

The absolute error in determining the temperature rise Tj-Ta caused by a delay td in measuring the VGSH can be estimated as follows:

Formula (3) results directly from the observation that during a step change in the power dissipated in the transistor, the increase in its internal temperature is the product of the dissipated power value and the waveform Zth(t). The power dissipated in the transistor during its heating is the product of the current IH and the voltage VDSH, and the waveform Zth(t) is described by formula (2).

Equation (3) shows that as the delay td increases, the error in determining the temperature rise also increases. The error becomes larger for higher values of ai and for smaller values of τthi. A large ai value is typical for transistors cooled with efficient systems, e.g., a heat sink with a fan or a liquid cooling system. The value of τthi depends on the material and dimensions of the semiconductor structure and on the packaging technology.

4. Investigation Results

To estimate the influence of the delay time td on the Rth measurement error for power MOSFETs made of different materials, datasheet waveforms of Zth(t) under ideal cooling conditions were analyzed. Three transistors in TO-247 packages were tested: silicon (Si), silicon carbide (SiC), and gallium nitride (GaN). The devices were IXFH15N100Q3 (Hi-perFET Q3-class produced by IXYS, Milpitas, California, CA, USA), C3M0280090D (C3M MOSFET Technology produced by Wolfspeed, Research Triangle Park, North Carolina, NC, USA), and TP65H050G4WS (GaN cascode produced by Transphorm, Goleta, California, CA, USA).

4.1. Properties of Tested Devices

The properties of the selected transistors are presented in [48,49,50]. Their maximum drain–source voltage ratings range from 650 V to 1000 V, the maximum drain current from 11.5 A to 34 A, and the on-state resistance RON from 0.06 Ω to 1.05 Ω. The junction-to-ambient thermal resistance Rthj-a specified by all manufacturers, is 40 K/W. The junction-to-case Rthj-c thermal resistance of the selected transistors differs significantly. It is 0.18 K/W for the silicon transistor, 1.05 K/W for the GaN transistor, and 2.3 K/W for the SiC transistor.

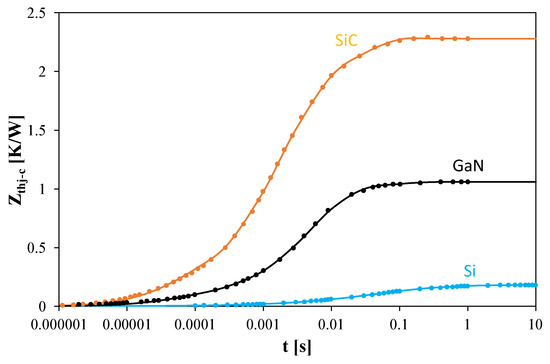

Figure 2 shows the Zthj-c(t) waveforms from datasheets (points) together with the approximations obtained using formula (2) (lines). The silicon transistor is shown in blue, the GaN transistor in black, and the SiC transistor in orange. The parameters describing the Zth(t) waveforms were determined using the method in [47], and are summarized in Table 1.

Figure 2.

Datasheet Zth(t) waveforms of the tested power MOSFETs under ideal cooling, and their approximations.

Table 1.

Parameters describing the Zth(t) waveforms of the tested transistors.

The results in Figure 2 indicate that Zth(t) of the silicon transistor remains negligible for t < 2 ms, while for the GaN transistor, it is negligible for t < 20 μs, and for the SiC transistor for t < 3 μs. Table 1 shows that the shortest thermal time constants range from 40 μs to 200 μs. The number of thermal time constants describing the semiconductor structures and packages of the tested transistors ranges from 4 to 5, with the longest exceeding 600 ms.

4.2. Influence of Recording Delay on Junction Temperature Measurement Error

To evaluate the effect of td on the error in determining the junction temperature rise, error values ΔTj1 were calculated for selected power dissipation levels in each transistor using formula (3). Ideal package cooling and selected values of td were considered. The results are presented in Table 2.

Table 2.

Absolute error ΔTj1 of the tested transistors for selected values of power P and delay time td.

The absolute error in determining the junction temperature rise increases with both td and P, but the magnitude of this increase differs among the tested transistors. Under the considered conditions, the highest errors occur for the SiC device. For P = 50 W and td = 3 ms, the error exceeds 75 K, corresponding to a relative error greater than 66%. For the same td, the error is about 20% for the silicon transistor and nearly 50% for the GaN transistor. At td = 0.1 ms, the error ranges from 4% for Si to 14% for SiC.

Table 3 and Table 4 contain the values of the ΔTj1 error calculated for selected values of the delay td and dissipated power for the tested transistors operating in actual conditions. Table 3 corresponds to transistors operating at natural convection, whereas Table 4—to transistors situated on the heat sink characterized by Rthc-a = 7 K/W.

Table 3.

Absolute error ΔTj1 of the tested transistors for selected values of power P and delay time td for transistors operating at natural convection.

Table 4.

Absolute error ΔTj1 of the tested transistors for selected values of power P and delay time td for transistors situated on the heat sink characterized by Rthc-a = 7 K/W.

These results highlight the importance of minimizing td in Rth measurements. They also show that modern wide-bandgap MOSFETs (SiC, GaN), characterized by very short thermal time constants, are more susceptible to significant errors. By analyzing the data contained in Table 2, Table 3 and Table 4, it can be easily observed that the influence of time td on the error of the junction temperature measurement ΔTj1 is stronger the higher the value of the power dissipated in the tested transistor and the more effective the cooling system is used.

The above discussion concerns the worst-case scenario of ideal case cooling, in which the devices cool down rapidly after switchover. In practical applications, cooling is less efficient, resulting in higher Rth values, smaller weighting factors for the shortest time constants, and additional longer time constants associated with other elements of the heat flow path [17,46]. These longer time constants (seconds to thousands of seconds) have a negligible influence on ΔTj1.

Table 5 shows the relative error ΔTj1/(Tj − Ta) for each transistor operating under two cooling conditions: without a cooling system (Rth = 40 K/W) and with a medium-sized heat sink (Rth = 7 K/W + Rthj-c).

Table 5.

Relative error ΔTj1/(Tj − Ta) for the tested transistors under different cooling conditions and delay times td.

The results show that the relative error increases with both td and the efficiency of the cooling system (lower Rth). Among the tested devices, the SiC transistor exhibits the largest error. With a heat sink and td > 1 ms, the error exceeds several percent, and for ideal cooling of the transistor case, this error could exceed even 40%. For the silicon transistor, the error remains below 0.5% under all actual cooling conditions, which is acceptable. To achieve below 1% error for SiC and GaN devices operating at actual cooling conditions, td must be shorter than 0.1 ms.

4.3. Influence of ADC Properties on TSEP Recording Delay

This section presents measurement results of the thermally sensitive parameter for the considered transistors under different cooling conditions and ADC configurations (sampling period TS and recording time tR). In all graphs, t = 0 corresponds to the switchover from heating to TSEP recording.

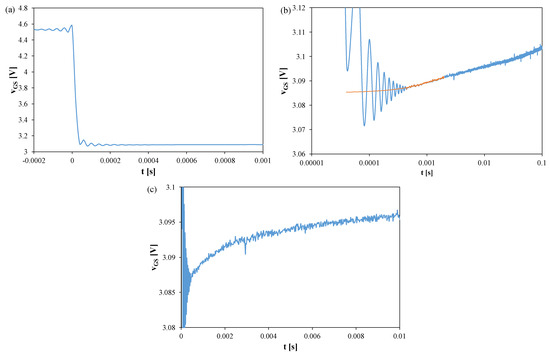

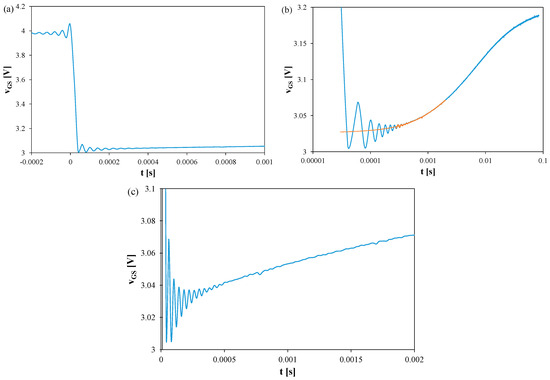

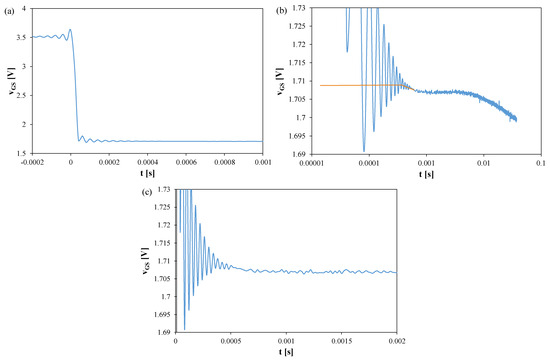

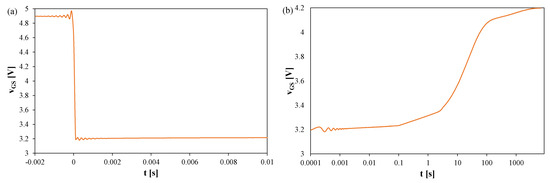

Figure 3, Figure 4 and Figure 5 show vGS waveforms for Si (Figure 3), GaN (Figure 4), and SiC (Figure 5) transistors recorded without a heat sink at P = 4 W, with TS = 20 μs and tR = 100 ms. Additionally, the approximations of these waveforms, vGS(t), are shown in Figure 3b, Figure 4b, and Figure 5b, respectively, and marked with orange color.

Figure 3.

Measured (blue) and approximated (orange) waveforms of the vGS voltage of the silicon MOSFETs without a heat sink; TS = 20 μs, tR = 100 ms: (a) vGS changes during the switchover from heating to TSEP recording, (b) settling of the vGS, logarithmic time scale, (c) settling of the vGS, linear time scale.

Figure 4.

Measured and approximated waveforms of the vGS voltage of the GaN MOSFETs operating without any heat sink; TS = 20 μs, tR = 100 ms: (a) vGS changes during the switchover from heating to TSEP recording, (b) settling of the vGS, logarithmic time scale, (c) settling of the vGS, linear time scale.

Figure 5.

Measured and approximated waveforms of the vGS voltage of the SiC MOSFETs without a heat sink; TS = 20 μs, tR = 100 ms: (a) vGS changes during the switchover from heating to TSEP recording, (b) settling of the vGS, logarithmic time scale, (c) settling of the vGS, linear time scale.

In each case, fading oscillations of vGS are observed. Their amplitudes correspond to junction temperature fluctuations of 15–25 K, disappearing after 0.3–0.5 ms. For the SiC transistor, a negative slope of vGS is also visible due to the electron trapping effect [51,52]. The orange line indicates a function approximating the measured vGS(t) waveform using a quadratic function. This line can be used to extrapolate the vGS(t) dependence and determine the vGS value corresponding to time t = 0.

Analyzing the waveforms shown in Figure 5, it can be seen that the measured vGS voltage values for this transistor are almost half that of the other transistors. It is also visible that after switching the measurement system to TSEP recording mode, the measured vGS voltage decreases instead of increasing. This is caused by the trapping effect described, among others, in [51,52]. It is worth adding that in the case of this transistor, it is worth taking into account that the VGSH value used to calculate Rth should be read only when the vGS(t) relationship becomes an increasing function.

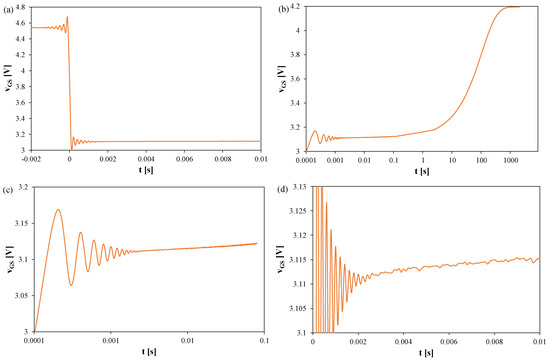

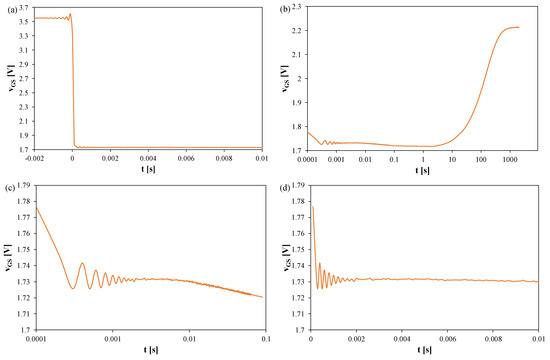

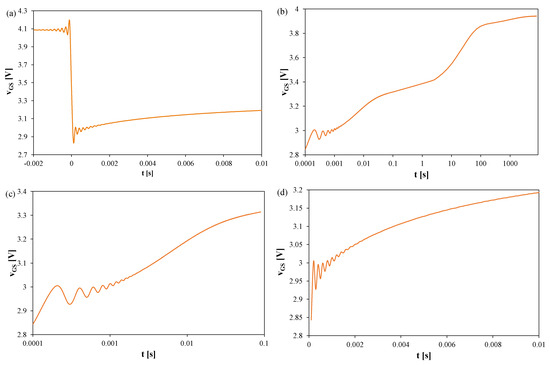

Figure 6, Figure 7 and Figure 8 present the vGS waveforms for the same devices without a heat sink, but with TS = 100 μs and tR = 2000 s. The thermal steady state occurs after about 800 s in all cases. Oscillation amplitudes range from 50 mV (SiC) to 170 mV (Si), corresponding to 25–60 K, and decay only after about 2–2.5 ms. For the SiC transistor, the increase in vGS becomes visible only for t > 1 s, implying td ≈ 1 s.

Figure 6.

Measured waveforms of the vGS voltage of the silicon MOSFETs without any heat sink; TS = 100 μs, tR = 2000 s: (a) vGS changes during the switchover from heating to TSEP recording, (b) the entire recording range, (c) settling of the vGS, logarithmic time scale, (d) settling of the vGS, linear time scale.

Figure 7.

Measured waveforms of the vGS voltage of the GaN MOSFETs operating without a heat sink; TS = 100 μs, tR = 2000 s: (a) vGS changes during the switchover from heating to TSEP recording, (b) the entire recording range, (c) settling of the vGS, logarithmic time scale, (d) settling of the vGS, linear time scale.

Figure 8.

Measured waveforms of the voltage vGS of the SiC MOSFETs operating without any heat sink; TS = 100 μs, tR = 2000 s: (a) a fragment of the waveform immediately after switching the transistor current, (b) the entire recording range, (c) magnification on a logarithmic time scale, (d) magnification on a linear time scale.

In Figure 6, it can be observed that the thermal steady state occurs after about 800 s from the moment the measuring system is switched to the TSEP recording mode. The peak-to-peak value of the oscillations reaches 170 mV, which corresponds to about 60 K. These oscillations disappear only after 2.5 ms.

In Figure 7, it can be observed that the thermal steady state occurs after about 800 s from the moment the measuring system is switched to the TSEP recording mode. The peak-to-peak value of the oscillations reaches 120 mV, which corresponds to about 35 K. These oscillations disappear only after 2 ms.

In Figure 8, it can be observed that the thermal steady state occurs after about 800 s from the moment of switching the measuring system to the TSEP recording mode. The peak-to-peak value of the oscillations reaches 50 mV, which corresponds to about 25 K. These oscillations disappear only after 2 ms. It is worth noting that in the case of this transistor, the increase in the vGS voltage value is visible only in the time interval t > 1s. According to the considerations presented above, for this transistor, the time td = 1 s.

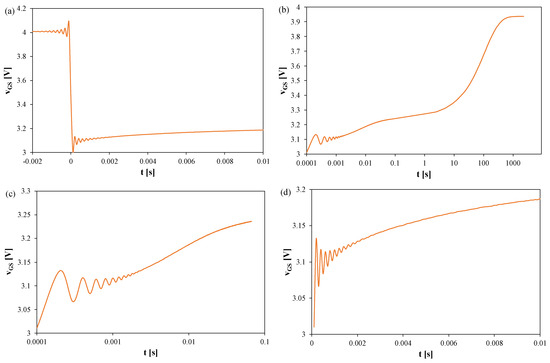

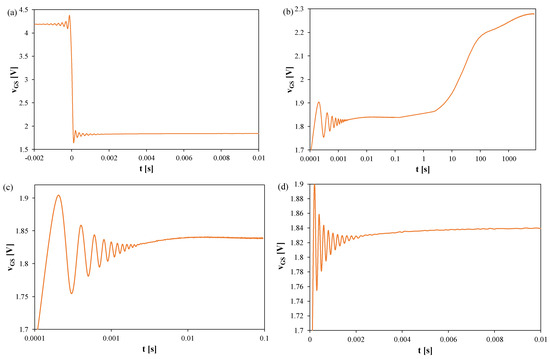

Figure 9, Figure 10 and Figure 11 show the waveforms of the vGS voltage of Si (Figure 9), GaN (Figure 10), and SiC (Figure 11) transistors recorded using the measurement setup. The presented results refer to transistors operating on a heat sink, in which the power dissipation was 9 W. The sampling period TS = 100 μs, and the recording time was 2000 s.

Figure 9.

Measured waveforms of the voltage vGS of the silicon MOSFETs on a heat sink; TS = 100 μs, tR = 2000 s: (a) a fragment of the waveform immediately after switching the transistor current, (b) the entire recording range, (c) magnification on a logarithmic time scale, (d) magnification on a linear time scale.

Figure 10.

Measured waveforms of the voltage vGS of the GaN cascode on a heat sink; TS = 100 μs, tR = 2000 s: (a) fragment of the waveform immediately after switching the IH current, (b) the entire recording range, (c) magnification on a logarithmic time scale, (d) magnification on a linear time scale.

Figure 11.

Measured waveforms of the voltage vGS of the SiC MOSFETs on a heat sink; TS = 100 μs, tR = 2000 s: (a) a fragment of the waveform immediately after switching the transistor current, (b) the entire recording range, (c) magnification on a logarithmic time scale, (d) magnification on a linear time scale.

In Figure 9, it can be observed that the thermal steady state is reached after approximately 7000 s from the moment the measuring setup is switched to the TSEP recording mode. The peak-to-peak value of the oscillations reaches 40 mV, which corresponds to approximately 12 K. These oscillations disappear only after 2 ms.

In Figure 10, it can be observed that the thermal steady state occurs after about 7000 s from the moment the measuring system is switched to the TSEP recording mode. The peak-to-peak value of the oscillations reaches 160 mV, which corresponds to about 45 K. These oscillations disappear only after 1.8 ms.

In Figure 11, it can be observed that the thermal steady state is reached approximately 8000 s after switching the measuring setup to the TSEP recording mode. The peak-to-peak value of the oscillations reaches 200 mV, which corresponds to about 100 K. These oscillations disappear only after 2 ms. The section of the vGS(t) waveform with a negative slope, which occurs when this transistor is operated without a heat sink, is not visible.

The ADC module uses both analog and digital filtering. The effective bandwidth depends on the selected sampling period. Oscillations are visible in both cases (TS = 20 μs and TS = 100 μs), but they persist longer with the larger TS. Specifically, oscillations decay after ~500 μs for TS = 20 μs and after ~2 ms for TS = 100 μs, indicating that the dynamic properties of the ADC affect the apparent settling time.

4.4. Influence of Properties of ADC Module on a Measurement Error

Combining the previous results, it can be concluded that the sampling period of the ADC strongly influences the time required for oscillations of vGS to disappear. According to formula (3), increasing td increases the measurement error of the junction temperature rise, and thus the relative error in Rth.

In the Figures shown in the previous sections, it is visible that the oscillations on the waveforms VGS(t) can be observed for a time longer than 400 μs. These oscillations are the result of both the dynamic properties of the used circuit polarizing the tested transistor and the properties of the used ADC module. If the value of VGSH voltage is measured at one of the time moments in which the high oscillations are observed, a big measurement error can be obtained. Additionally, if any extrapolation of VGSH voltage corresponding to time t = 0 will be performed using measured values of VGS voltage in the time interval in which the oscillations are observed, a big measurement error can also be obtained. Therefore, the values of VGSH should be measured when the mentioned oscillations are not observed.

Assuming that other error components (ambient temperature accuracy, TSEP calibration, and power loss determination) are negligible compared to this effect, the relative Rth error δRth was calculated for the three devices under different cooling conditions and ADC sampling periods. The results are summarized in Table 6.

Table 6.

Relative error δRth of the tested transistors under two cooling conditions and different sampling periods.

The results show that extending the sampling period increases the measurement error. Improved cooling conditions also increase the error because they accelerate the temperature decrease during the oscillation decay. The largest errors occur for SiC transistors situated on the heat sink. This error exceeds even 19% for TS = 100 μs. In contrast, the error obtained for a transistor made of Si does not exceed 3.2%.

It should be noted that these error values were calculated assuming a sufficiently large Tj − Ta difference to neglect errors due to ambient temperature measurement, thermometric characteristic approximation, and power loss determination. As shown in [23,25], these error components together do not exceed 4% when Tj − Ta > 80 K.

5. Conclusions

This paper presented research results illustrating the influence of the dynamic properties of the ADC module and the transistor biasing circuit on the measurement error of the thermal resistance of power MOSFETs fabricated from different semiconductor materials. Particular attention was given to the oscillations occurring in the measurement system immediately after the switchover from heating to TSEP recording. The TSEP value can be measured reliably only after these oscillations decay, during which time the junction temperature of the device decreases.

The problems specific to thermal resistance measurements of the mentioned devices, compared to classic silicon components, were presented. It is also important to demonstrate that in transistors made of silicon carbide or gallium nitride, thermal phenomena in these components occur more rapidly than in silicon transistors. Therefore, to obtain sufficiently accurate results, main attention should be paid to the measurement equipment used, especially the ADC module, and the selection of the sampling period.

The measurements demonstrated that the time required for oscillations to vanish increases with the sampling period of the ADC module. Another important factor affecting measurement accuracy is the cooling efficiency of the tested device. High-efficiency cooling accelerates the decrease in junction temperature during oscillation decay, which increases the measurement error. The cooling rate depends on the cooling method, the semiconductor material, and the packaging technology. The highest measurement errors were observed for SiC transistors mounted on a heat sink. Theoretical considerations also showed that the error would be even greater for devices cooled using liquid systems.

This issue is especially relevant for wide-bandgap transistors (SiC, GaN), which are characterized by short thermal time constants. For these devices, operating with highly efficient cooling systems, the error in thermal resistance measurement caused by TSEP oscillations can reach up to 75%. In contrast, for conventional silicon transistors, the error does not exceed 0.5% and is therefore negligible.

The presented results may be particularly useful for designers of measurement systems dedicated to thermal characterization of modern power semiconductor devices. They can also help developers of power electronic systems and cooling solutions properly design and test procedures, as well as verify the effectiveness of cooling systems.

The presented results demonstrate that the choice of sampling period can significantly affect measurement error, and at the same time indicate that the value of this error strongly depends on the material from which the tested transistor is made. To systematize the conducted investigations, our further research will involve obtaining measurement results for a larger number of sampling periods. Such results would perhaps allow for the formulation of an appropriate analytical relationship describing the effect of the sampling period on measurement errors.

Author Contributions

Conceptualization, K.G. and K.P.; methodology, K.G. and K.P.; validation, K.G. and K.P.; investigation, K.G. and K.P.; writing—original draft preparation, K.G. and K.P.; writing—review and editing, K.G. and K.P.; visualization, K.G. and K.P.; supervision, K.G.; All authors have read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

All data are included in the article.

Conflicts of Interest

The authors declare no conflicts of interest.

References

- She, X.; Huang, A.Q.; Lucia, O.; Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Rafin, S.M.S.H.; Ahmed, R.; Haque, M.A.; Hossain, M.K.; Haque, M.A.; Mohammed, O.A. Power Electronics Revolutionized: A Comprehensive Analysis of Emerging Wide and Ultrawide Bandgap Devices. Micromachines 2023, 14, 2045. [Google Scholar] [CrossRef]

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Chen, Z.; Li, J.; Jin, R.; Cui, M.; Guo, C. Measurement of Thermal Resistance of SiC MOSFET Module Based on Conduction Voltage Drop. IEEE Trans. Instrum. Meas. 2024, 73, 1008609. [Google Scholar] [CrossRef]

- Wang, H.; Liserre, M.; Blaabjerg, F. Toward Reliable Power Electronics: Challenges, Design Tools, and Opportunities. IEEE Ind. Electron. Mag. 2013, 7, 17–26. [Google Scholar] [CrossRef]

- Dupont, L.; Avenas, Y. Preliminary evaluation of thermo-sensitive electrical parameters based on the forward voltage for online chip temperature measurements of IGBT devices. IEEE Trans. Ind. Appl. 2015, 51, 4688–4698. [Google Scholar] [CrossRef]

- Avenas, Y.; Dupont, L.; Khatir, Z. Temperature measurement of power semiconductor devices by thermo-sensitive electrical parameters—A review. IEEE Trans. Power Electron. 2012, 27, 3081–3092. [Google Scholar] [CrossRef]

- Lienhard, J.H., IV; Lienhard, J.H., V. A Heat Transfer Textbook, 3rd ed.; Phlogistion Press: Cambridge, MA, USA, 2008. [Google Scholar]

- Otomański, P.; Pawłowski, E.; Szlachta, A. In Situ Evaluation of the Self-Heating Effect in Resistance Temperature Sensors. Sensors 2025, 25, 3374. [Google Scholar] [CrossRef]

- Posobkiewicz, K.; Górecki, K. Influence of selected factors on parameters of a cooling system with a Peltier module and forced air flow. Microelectron. Int. 2022, 39, 141–146. [Google Scholar] [CrossRef]

- Górecki, K.; Posobkiewicz, K. Cooling systems of power semiconductor devices—A review. Energies 2022, 15, 4566. [Google Scholar] [CrossRef]

- Lasance, C.J.M.; Poppe, A. Thermal Management for LED Applications; Springer Science+Business Media: New York, NY, USA, 2014. [Google Scholar]

- Zhu, X.; Huang, Y.; Zhang, D.; Zhang, Y.; Wu, J.; Jiang, B.; Xia, L.; Gao, B.; Lv, C. Online Junction Temperature Measurement for Power MOSFETs Using the Body Diode Under Varying Forward Currents. Energies 2025, 18, 5045. [Google Scholar] [CrossRef]

- Blackburn, D.L. Temperature measurements of semiconductor devices—A review. In Proceedings of the Twentieth Annual IEEE Semiconductor Thermal Measurement and Management Symposium, San Jose, CA, USA, 9–11 March 2004; pp. 70–80. [Google Scholar] [CrossRef]

- Du, M.; Xin, J.; Wang, H.; Ouyang, Z.; Wei, K. Estimating Junction Temperature of SiC MOSFET Using Its Drain Current During Turn-On Transient. IEEE Trans. Electron Devices 2020, 67, 1911–1918. [Google Scholar] [CrossRef]

- Stella, F.; Pellegrino, G.; Armando, E.; Daprà, D. Online Junction Temperature Estimation of SiC Power MOSFETs Through On-State Voltage Mapping. IEEE Trans. Ind. Appl. 2018, 54, 3453–3462. [Google Scholar] [CrossRef]

- Górecki, K.; Posobkiewicz, K. Selected problems of power MOSFETs thermal parameters measurements. Energies 2021, 14, 8353. [Google Scholar] [CrossRef]

- Colino, S.L.; Beach, R.A. Fundamentals of Gallium Nitride Power Transistors. Application Note: An002, EPC—Power Conversion Technology Lead, 2020. Available online: https://epc-co.com/epc/Portals/0/epc/documents/product-training/appnote_ganfundamentals.pdf (accessed on 25 October 2025).

- Morel, C.; Morel, J.-Y. Power Semiconductor Junction Temperature and Lifetime Estimations: A Review. Energies 2024, 17, 4589. [Google Scholar] [CrossRef]

- Zięba, D.; Rąbkowski, J. Problems related to the correct determination of switching power losses in high-speed SiC MOSFET power modules. Bull. Pol. Acad. Sci. Tech. Sci. 2022, 70, e140695. [Google Scholar] [CrossRef]

- Wang, H.; Yuan, C.; Xin, Y.; Shi, Y.; Zhong, Y.; Huang, Y.; Lu, G. Investigation on the Thermal Characteristics of Enhancement-Mode p-GaN HEMT Device on Si Substrate Using Thermoreflectance Microscopy. Micromachines 2022, 13, 466. [Google Scholar] [CrossRef]

- Kim, J.; Lim, S.; Choi, G.E.; Park, J.-k.; Cha, H.-Y.; Kwak, C.-H.; Lim, J.; Moon, Y.; Song, J.-H. Simultaneous Submicron Temperature Mapping of Substrate and Channel in p-GaN/AlGaN/GaN HEMTs Using Raman Thermometry. Appl. Sci. 2025, 15, 7860. [Google Scholar] [CrossRef]

- Martin-Horcajó, S.; Pomeroy, J.W.; Lambert, B.; Jung, H.; Blanck, H.; Kuball, M. Transient Thermoreflectance for Gate Temperature Assessment in Pulse-Operated GaN-based HEMTs. IEEE Electron Device Lett. 2016, 37, 1197–1200. [Google Scholar] [CrossRef]

- Huang, X.; Weng, Q.; Zhang, Y.; Guo, C.; Feng, S. Temperature rise detection in GaN high-electron-mobility transistors: Electrical method for junction temperature and thermal resistance. Microelectron. J. 2024, 148, 106200. [Google Scholar] [CrossRef]

- Pirosca, A.V.; Vecchio, M.; Rizzo, S.A.; Iannuzzo, F. Evaluation of the Thermal Resistance in GaN HEMTs Using Thermo-Sensitive Electrical Parameters. Energies 2023, 16, 2779. [Google Scholar] [CrossRef]

- Cutivet, A.; Bouchilaoun, M.; Hassan, B.; Rodriguez, C.J.; Ali, S.; Boone, F.; Maher, H. Thermal Transient Extraction for GaN HEMTs by Frequency-Resolved Gate Resistance Thermometry with Sub-100 ns Time Resolution. Phys. Status Solidi (A) Appl. Mater. Sci. 2018, 216, 1800503. [Google Scholar] [CrossRef]

- Pavlidis, G.; Graham, S. Monitoring the Transient Thermal Response of AlGaN/GaN HEMTs using Transient Thermoreflectance Imaging. In Proceedings of the CS MANTECH Conference, New Orlean, LA, USA, 19–22 May 2025; Available online: https://csmantech.org/wp-content/acfrcwduploads/field_5e8cddf5ddd10/post_4258/11.1.pdf (accessed on 19 October 2025).

- Zheng, X.; Pomeroy, J.W.; Jindal, G.; Kuball, M. Temperature-Dependent Thermal Impedance Measurement of GaN-Based HEMTs Using Transient Thermoreflectance. IEEE Trans. Electron Devices 2024, 71, 2367–2372. [Google Scholar] [CrossRef]

- Chen, S.-H.; Chou, P.-C.; Cheng, S. Evaluation of thermal performance of packaged GaN HEMT cascode power switch by transient thermal testing. Appl. Therm. Eng. 2016, 98, 1003–1012. [Google Scholar] [CrossRef]

- Hara, T.; Yanai, K. Transient Thermal Characterization for GaN HEMTs with p-Type Gate. Trans. Jpn. Inst. Electron. Packag. 2020, 13, E19-002-1–E19-002-13. [Google Scholar] [CrossRef]

- Bagnall, K.R.; Saadat, O.I.; Joglekar, S.; Palacios, T.; Wang, E.N. Experimental Characterization of the Thermal Time Constants of GaN HEMTs Via Micro-Raman Thermometry. IEEE Trans. Electron Devices 2017, 64, 2121–2128. [Google Scholar] [CrossRef]

- González, B.; Nunes, L.C.; Gomes, J.L.; Mendes, J.C.; Jimenez, J.L. A Simple Method to Extract the Thermal Resistance of GaN HEMTs from De-trapping Characteristics. IEEE Electron Device Lett. 2023, 44, 891–894. [Google Scholar] [CrossRef]

- Li, X.; Feng, S.; Liu, C.; Zhang, Y.; Bai, K.; Xiao, Y.; Zheng, X.; He, X.; Pan, S.; Lin, G.; et al. A Drain–Source Connection Technique: Thermal Resistance Measurement Method for GaN HEMTs Using TSEP at High Voltage. IEEE Trans. Electron Devices 2020, 67, 5454–5459. [Google Scholar] [CrossRef]

- Wang, K.; Zhu, Y.; Zhao, H.; Zhao, R.; Zhu, B. Steady-State Temperature-Sensitive Electrical Parameters’ Characteristics of GaN HEMT Power Devices. Electronics 2024, 13, 363. [Google Scholar] [CrossRef]

- VSmirnov, I.; Sergeev, V.A.; Gavrikov, A.A.; Kulikov, A.A. Measuring Thermal Resistance of GaN HEMTs Using Modulation Method. IEEE Trans. Electron Devices 2020, 67, 4112–4117. [Google Scholar] [CrossRef]

- Leung, W.T.; Niroomand, M.; Jahdi, S.; Stark, B.H. Accelerated Power Cycling of GaN HEMTs using Switching Loss and Fast Temperature Measurement. In Proceedings of the PCIM Europe 2024, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nürnberg, Germany, 11–13 June 2024; pp. 74–83. [Google Scholar]

- González, B.; Lázaro, A.; Rodríguez, R. RF Extraction of Thermal Resistance for GaN HEMTs on Silicon. IEEE Trans. Electron Devices 2022, 69, 2307–2312. [Google Scholar] [CrossRef]

- Luo, N.; Wen, H.; Liu, W.; Jiang, L. High-Accuracy Thermal Resistance Measurement Method for GaN HEMTs Based on Harmonic Pulsewidth Subthreshold. IEEE Trans. Electron Devices 2025, 72, 186–192. [Google Scholar] [CrossRef]

- Oettinger, F.F.; Blackburn, D.L. Semiconductor Measurement Technology: Thermal Resistance Measurements; NIST/SP-400/86; U. S. Department of Commerce: Washington, DC, USA, 1990. [Google Scholar]

- Szekely, V.; Rencz, M.; Courtois, B. Thermal investigations of IC’s and microstructures. Microelectron. J. 1997, 28, 205–207. [Google Scholar] [CrossRef]

- Janicki, M.; Sarkany, Z.; Napieralski, A. Impact of nonlinearities on electronic device transient thermal responses. Microelectron. J. 2014, 45, 1721–1725. [Google Scholar] [CrossRef]

- Górecki, K.; Posobkiewicz, K. Influence of a Cooling System on Power MOSFETs’ Thermal Parameters. Energies 2022, 15, 2923. [Google Scholar] [CrossRef]

- Posobkiewicz, K.; Data, A.; Górecki, K. Realizacja praktyczna układu do pomiaru parametrów cieplnych tranzystorów MOS mocy. Przegląd Elektrotech. 2022, 98, 143–146. [Google Scholar] [CrossRef]

- Górecki, K.; Górecki, P. The analysis of accuracy of the selected methods of measuring thermal resistance of IGBTs. Metrol. Meas. Syst. 2015, 22, 455–464. [Google Scholar] [CrossRef][Green Version]

- Poppe, A. Thermal measurements and modelling. The transient and multichip issues. In Proceedings of the Tutorial, 11th THERMINIC Workshop, Belgirate, Italy, 28–30 September 2005; Available online: https://therminic.org/therminic2005/APoppe_Tutorial.pdf (accessed on 25 October 2025).[Green Version]

- Górecki, K.; Ptak, P.; Janicki, M. Investigations of mutual thermal couplings in selected lighting sources with power LEDs. IEEE Trans. Compon. Packag. Manuf. Technol. 2023, 13, 1130–1138. [Google Scholar] [CrossRef]

- Górecki, K.; Zarębski, J.; Górecki, P.; Ptak, P. Compact thermal models of semiconductor devices—A review. Int. J. Electron. Telecommun. 2019, 65, 151–158. [Google Scholar] [CrossRef]

- Q3-Class HiperFETTM Power MOSFET IXFT15N100Q3. Datasheet, IXYS. Available online: https://www.littelfuse.com/assetdocs/littelfuse-discrete-mosfets-ixf-15n100q3-datasheet?assetguid=2eb816c3-afba-4569-a822-bf202a29101a (accessed on 25 October 2025).

- C3M0280090D Silicon Carbide Power MOSFET C3MTM MOSFET Technology N-Channel Enhancement Mode, Datasheet, Wolfspeed. Available online: https://assets.wolfspeed.com/uploads/2024/01/Wolfspeed_C3M0280090D_data_sheet.pdf (accessed on 25 October 2025).

- TP65H050G4WS 650V SuperGaN® FET in TO-247, Datasheet, Renesas. Available online: https://www.renesas.com/en/document/dst/tp65h050g4ws-datasheet?srsltid=AfmBOoqozaz7wACgGCUbMFgBFVVkHzt85B4aDjzMvy2Mj5oLcDjC-6F7 (accessed on 25 October 2025).

- Buffolo, M.; Favero, D.; Marcuzzi, A.; De Santi, C.; Meneghesso, G.; Zanoni, E.; Meneghini, M. Review and Outlook on GaN and SiC Power Devices: Industrial State-of-the-Art, Applications, and Perspectives. IEEE Trans. Electron Devices 2024, 71, 1344–1355. [Google Scholar] [CrossRef]

- Jiang, H.; Qi, X.; Qiu, G.; Zhong, X.; Tang, L.; Mao, H.; Wu, Z.; Chen, H.; Ran, L. A Physical Explanation of Threshold Voltage Drift of SiC MOSFET Induced by Gate Switching. IEEE Trans. Power Electron. 2022, 37, 8830–8834. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).