A 2.4 GHz Wide-Range CMOS Current-Mode Class-D PA with HD2 Suppression for Internet of Things Applications

Abstract

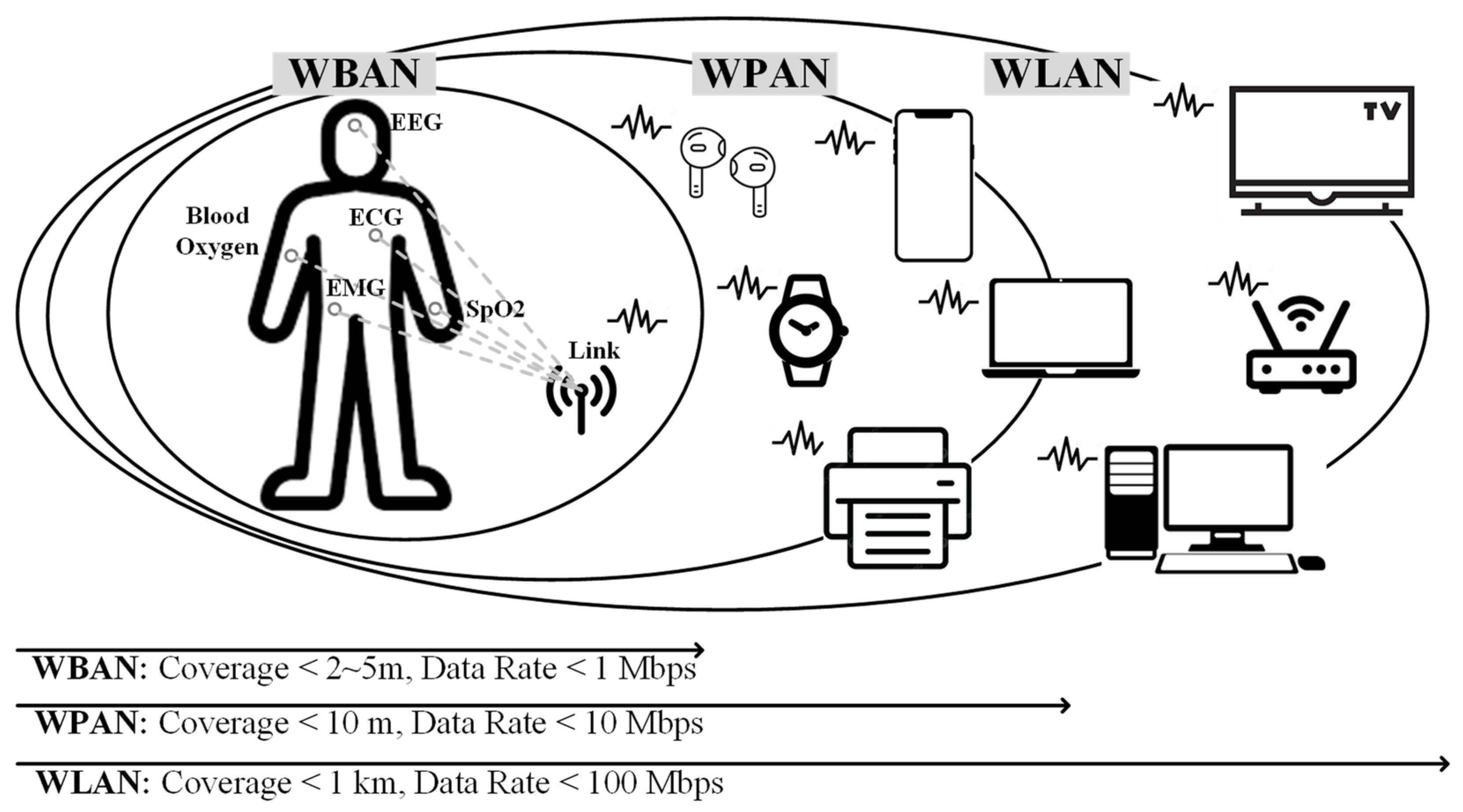

1. Introduction

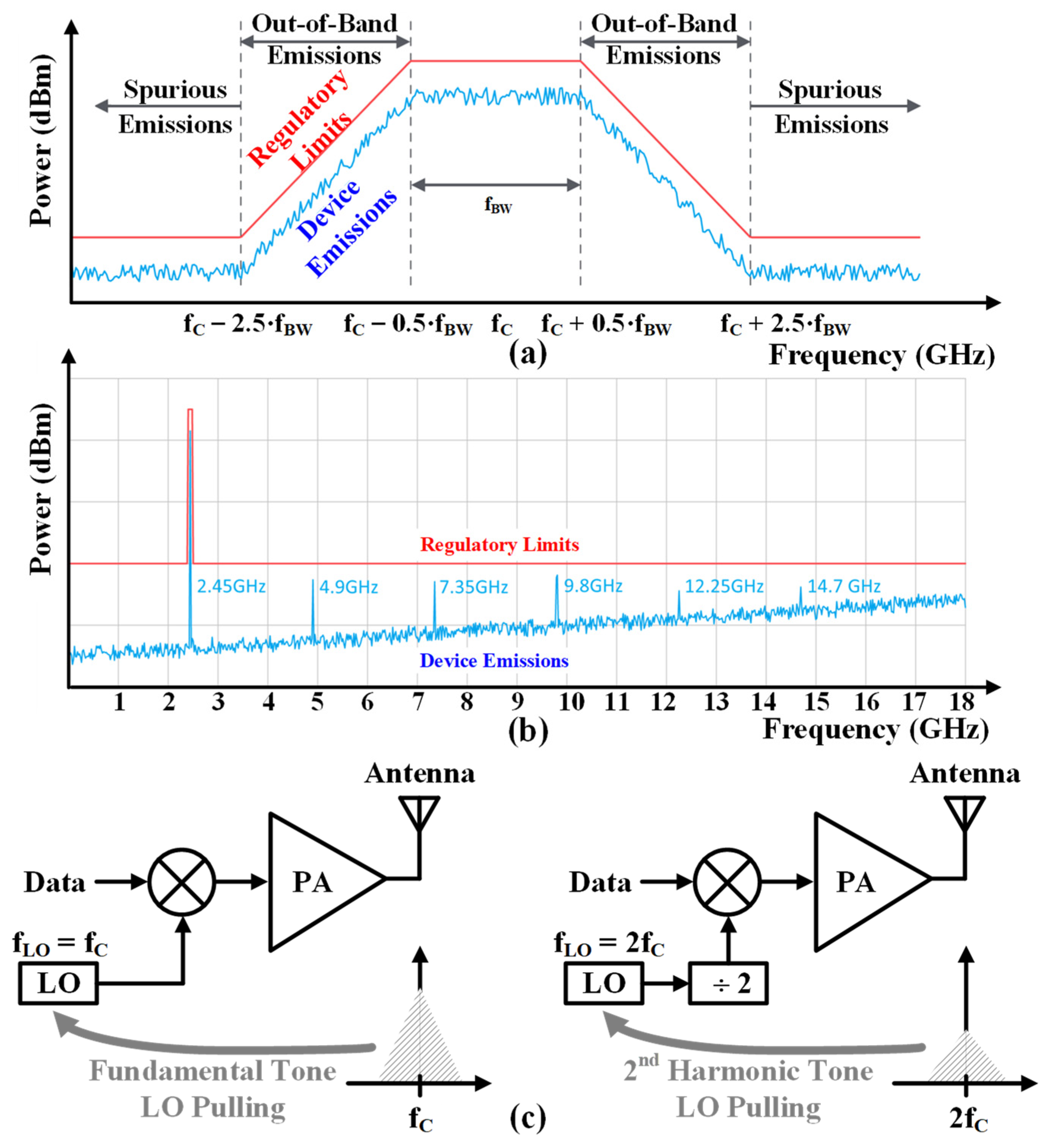

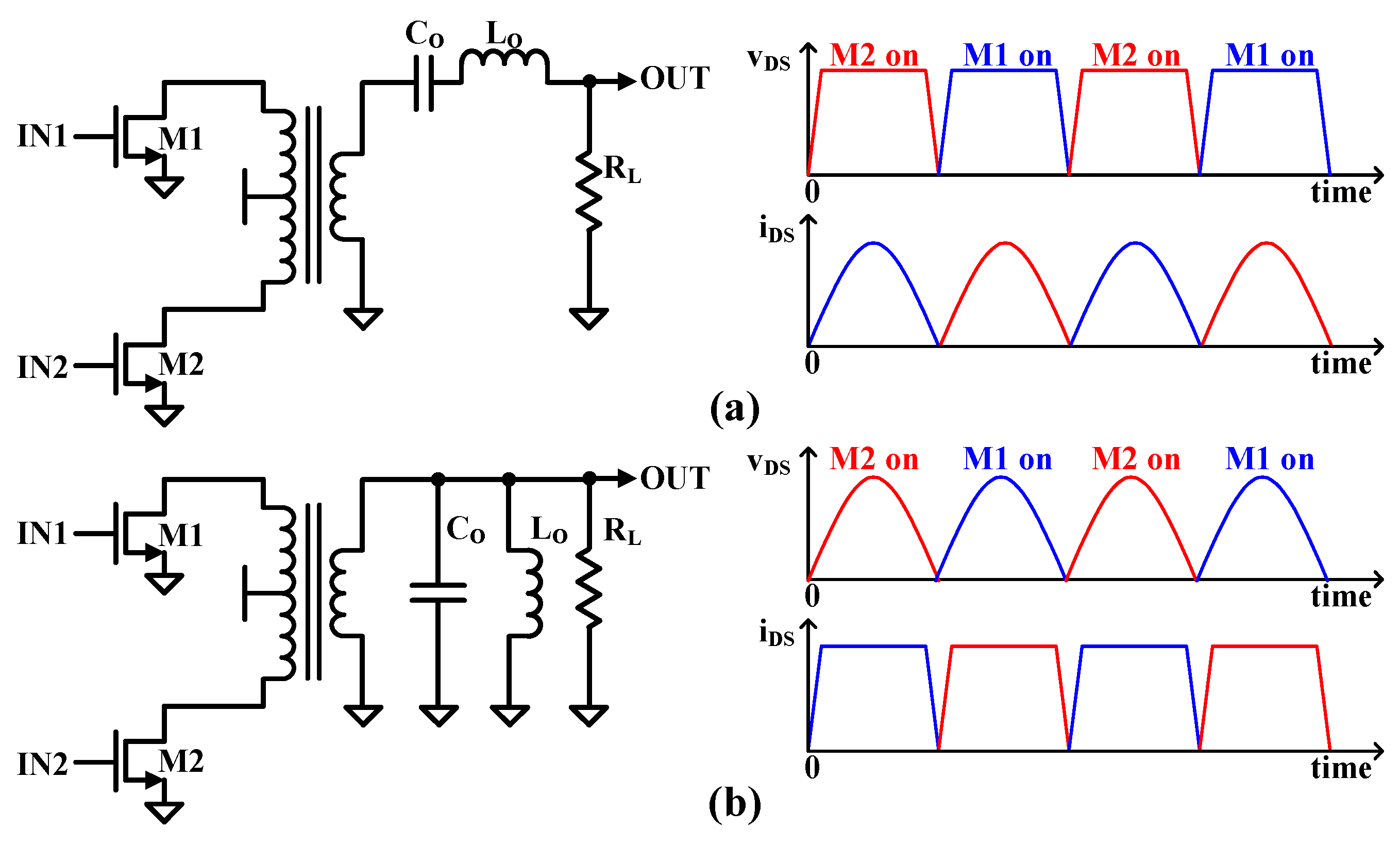

2. Class-D Power Amplifier Overview

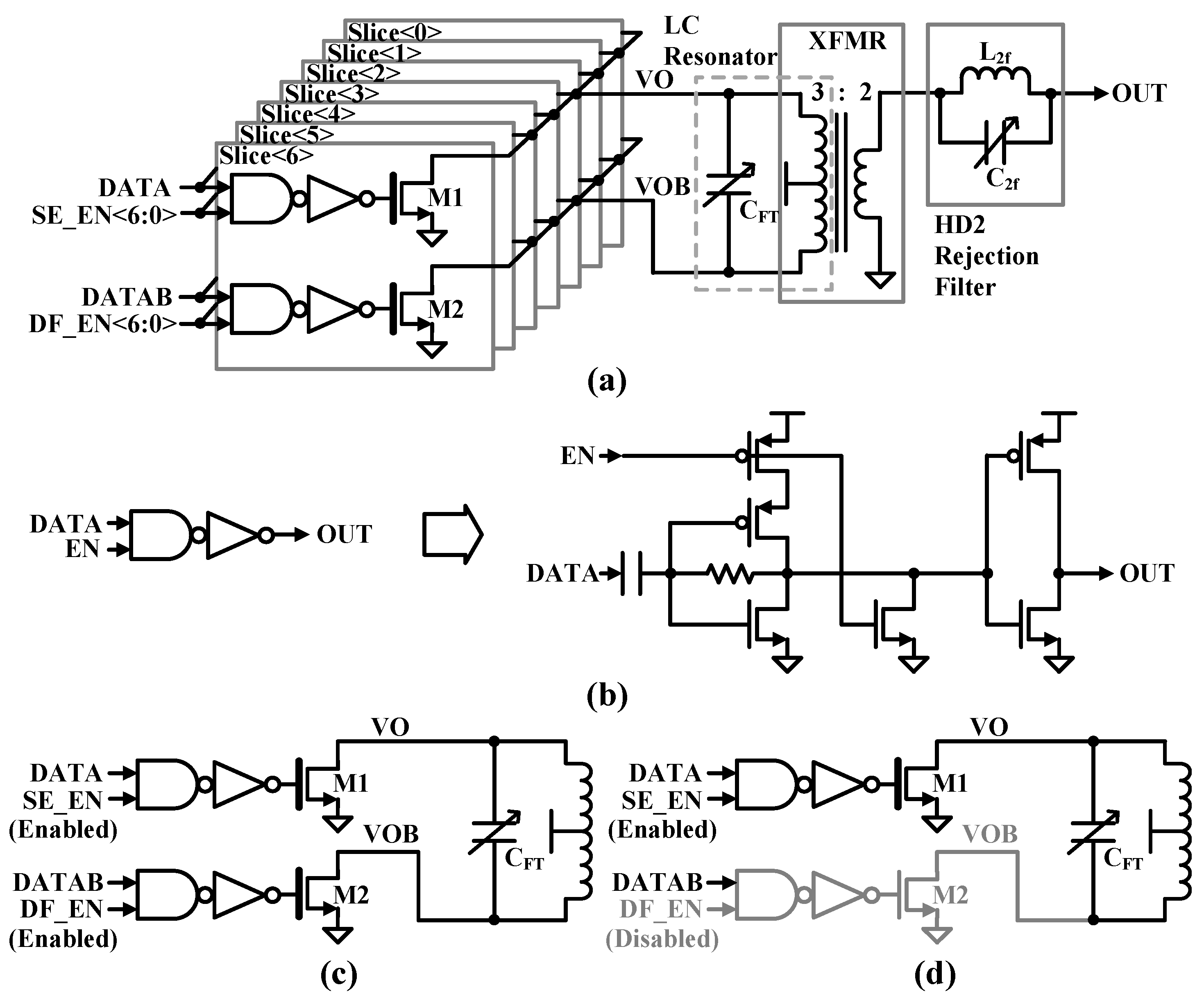

3. Wide-Range CMCD PA with Harmonic Suppression

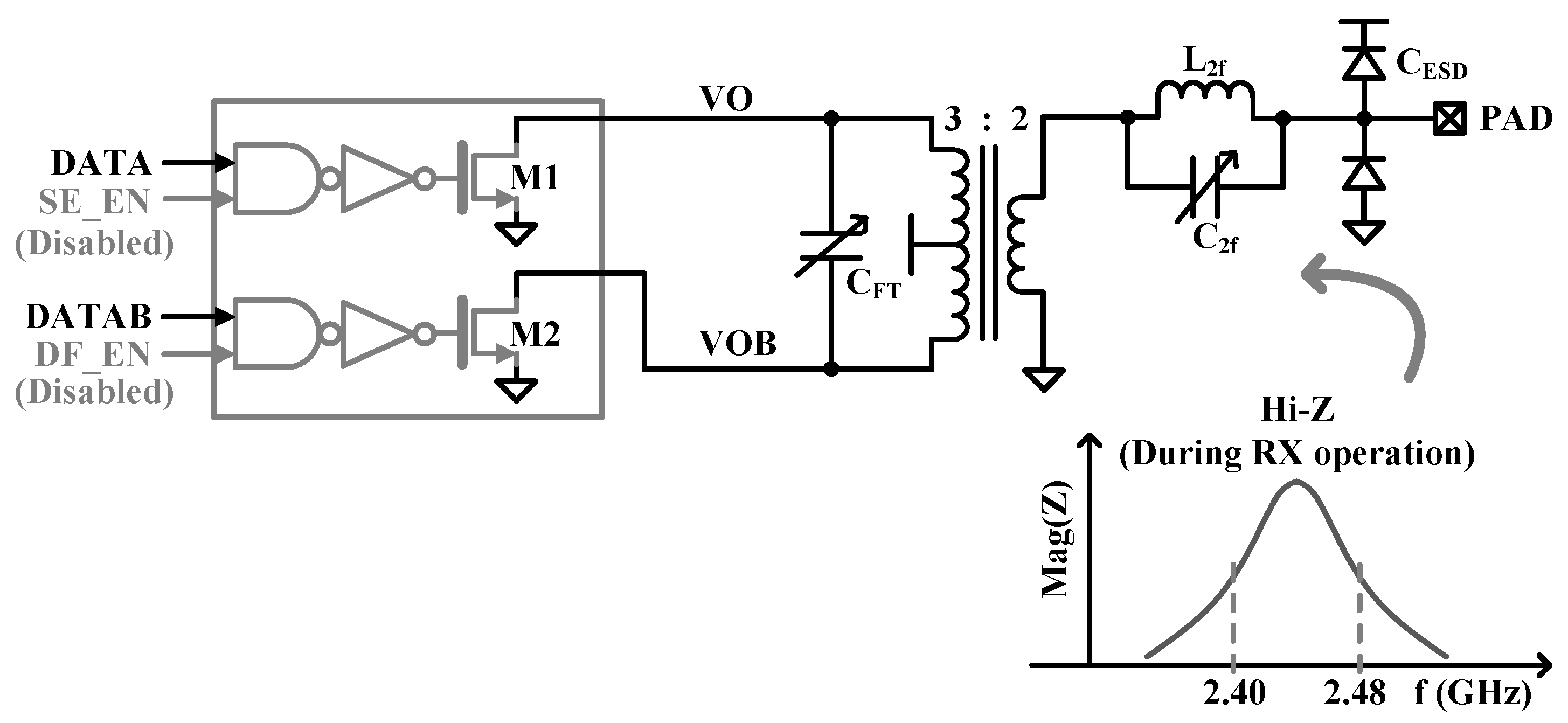

3.1. Transmitter Architecture

3.2. Wide-Range CMCD Power Amplifier

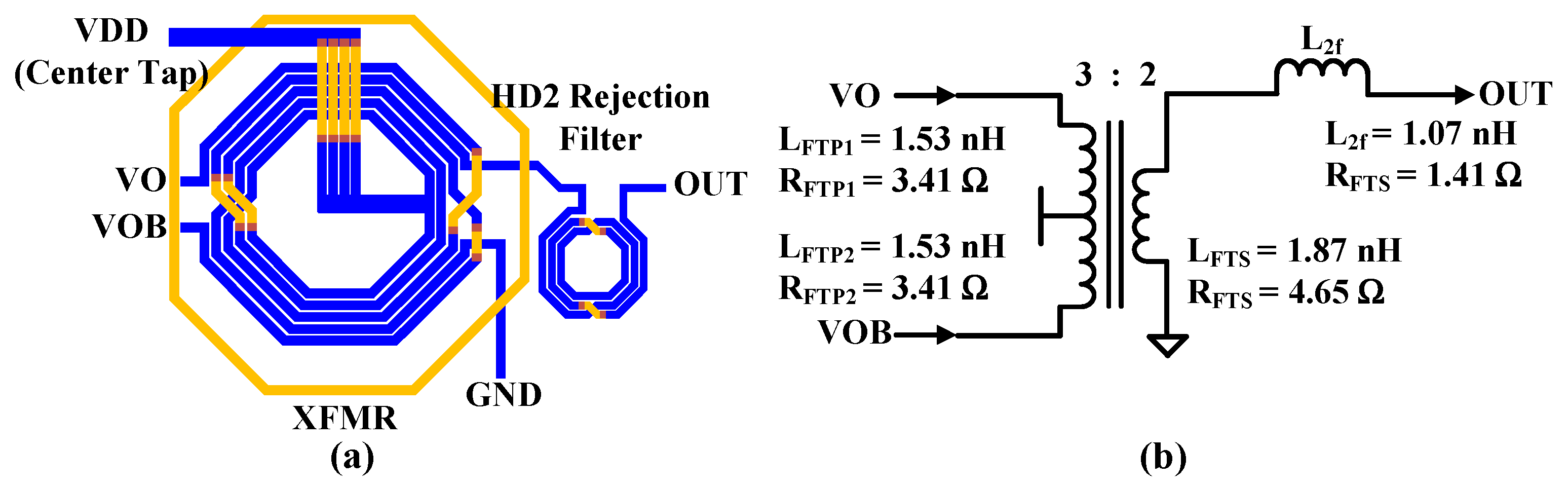

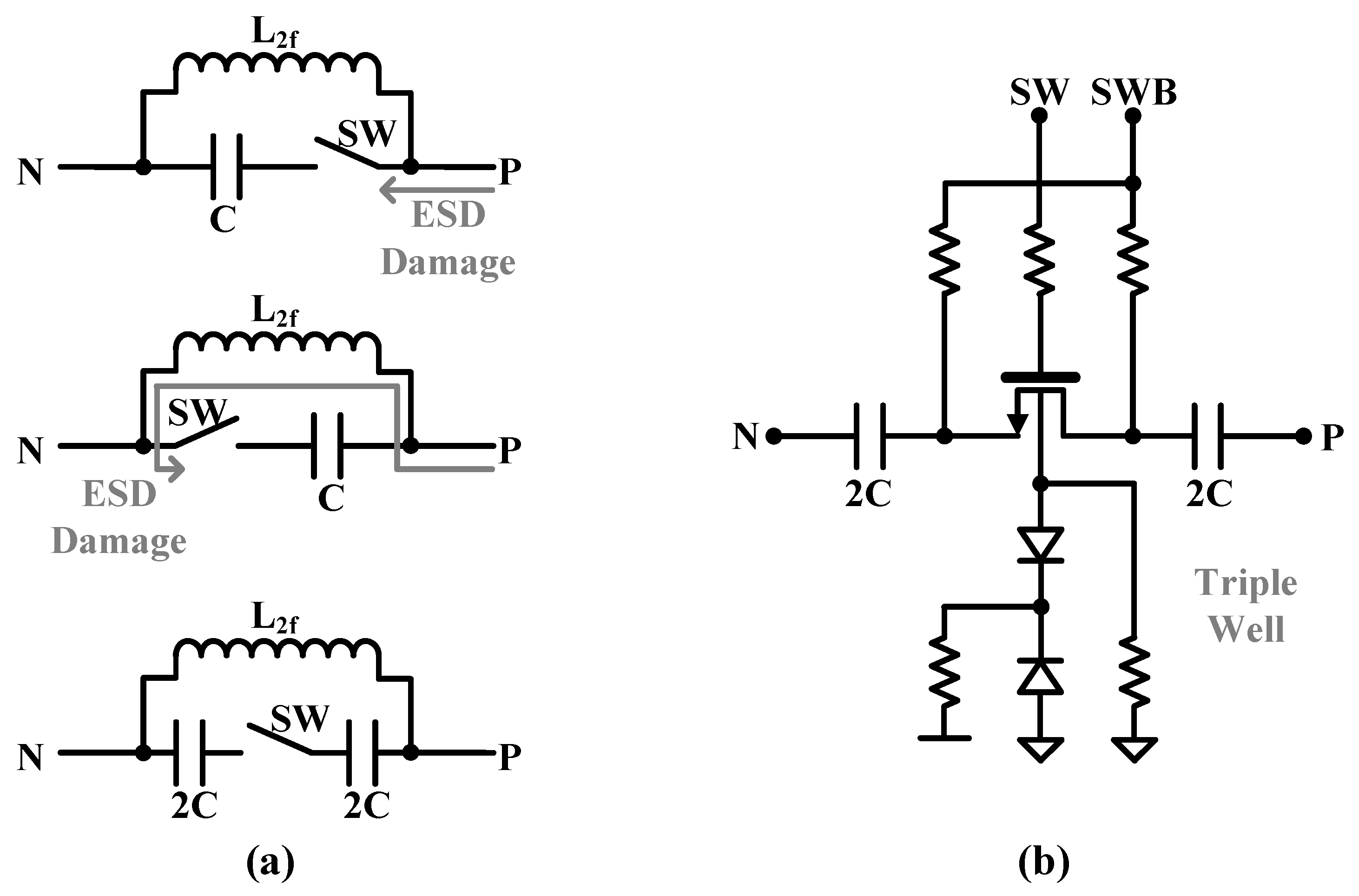

3.3. Transformer and HD2 Rejection Filter

3.4. HD2 Suppression with Duty-Cycle Correction

3.5. External CLC Low-Pass-Filter for Harmonic Suppression

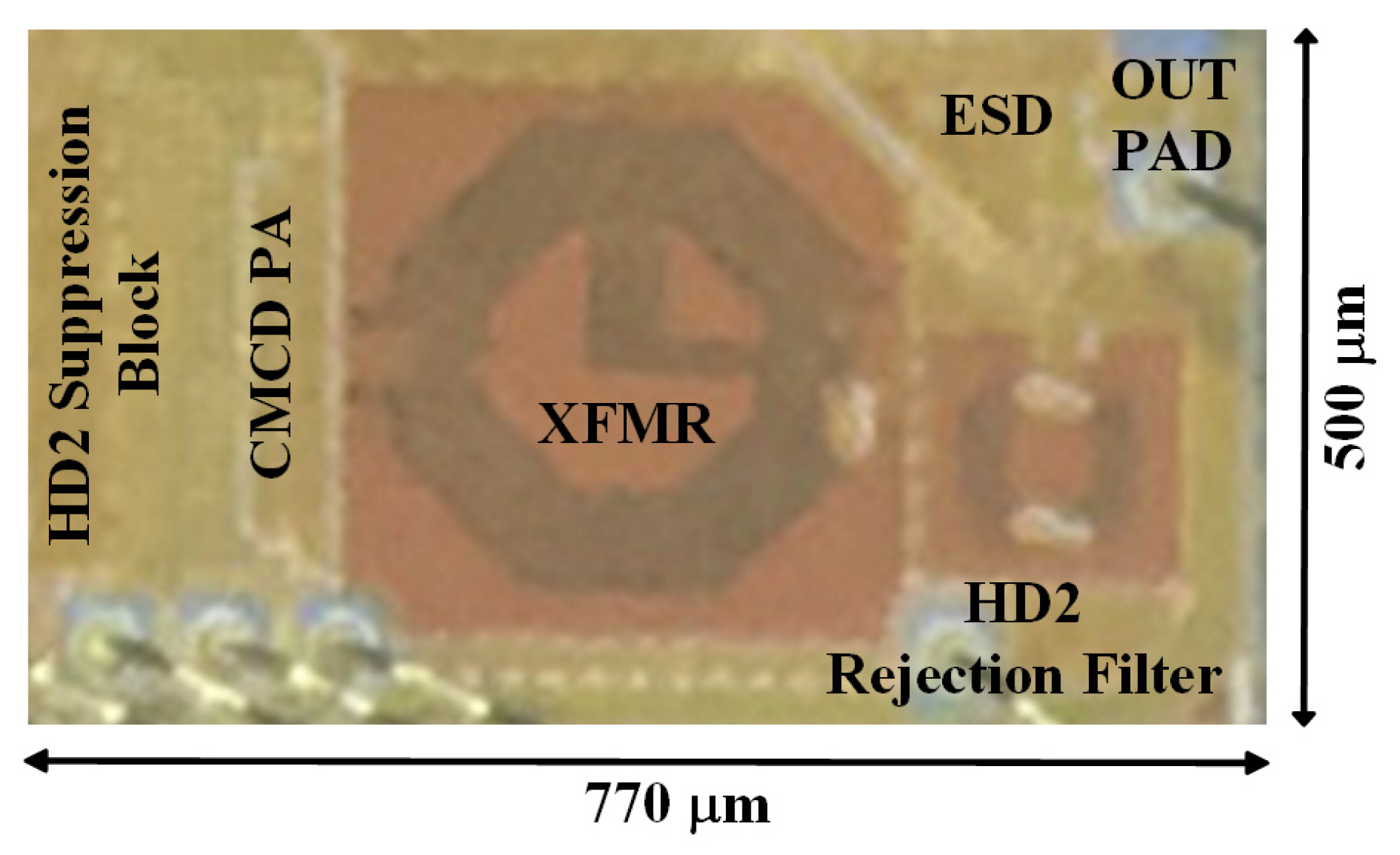

4. Experimental Results

5. Conclusions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Akyildiz, I.F.; Su, W.; Sankarasubramaniam, Y.; Cayirci, E. Wireless Sensor Networks: A Survey. Comput. Netw. 2002, 38, 399–422. [Google Scholar] [CrossRef]

- Brito, T.; Pereira, A.I.; Lima, J.; Valente, A. Wireless Sensor Network for Ignitions Detection: An IoT approach. Electronics 2020, 9, 893. [Google Scholar] [CrossRef]

- Basu, D.; Moretti, G.; Gupta, G.S.; Marsland, S. Wireless sensor network based smart home: Sensor selection, deployment and monitoring. In Proceedings of the IEEE Sensors Applications Symposium Proceedings, Galveston, TX, USA, 19–21 February 2013; pp. 49–54. [Google Scholar]

- Latha, R.; Vetrivelan, P. Wireless Body Area Network (WBAN)-Based Telemedicine for Emergency Care. Sensors 2020, 20, 2153. [Google Scholar]

- Kuo, F.; Binsfeld Ferreira, S.; Chen, H.R.; Cho, L.; Jou, C.; Hsueh, F.; Madadi, I.; Tohidian, M.; Shahmohammadi, M.; Babaie, M.; et al. A Bluetooth Low-Energy Transceiver with 3.7-mW All-Digital Transmitter, 2.75-mW High-IF Discrete-Time Receiver, and TX/RX Switchable On-Chip Matching Network. IEEE J. Solid-State Circuits 2017, 52, 1144–1162. [Google Scholar] [CrossRef]

- Ding, M.; Zhang, P.; He, Y.; Traferro, S.; Song, M.; Korpela, H.; Shibata, K.; Ueda, K.; Liu, Y.-H.; Bachmann, C. A Bluetooth 5 Transceiver with a Phase-Tracking RX and Its Corresponding Digital Baseband in 40-nm CMOS. IEEE J. Solid State Circuits 2020, 56, 254–266. [Google Scholar] [CrossRef]

- Huang, H.; Liu, X.; Tang, Z.; Song, W.; Zhang, Y.; Ma, X.; Zhang, M.; Wang, J.; Wang, Z.; Li, G. A 2 nJ/bit, 2.3% FSK Error Fully Integrated Sub-2.4 GHz Transmitter with Duty-Cycle Controlled PA for Medical Band. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 5018–5029. [Google Scholar] [CrossRef]

- Yang, W.; Hu, D.Y.; Lam, C.K.; Cui, J.Q.; Soh, L.K.; Song, D.C.; Zhong, X.W.; Hor, H.C.; Heng, C.L. A +8 dBm BLE/BT Transceiver with Automatically Calibrated Integrated RF Bandpass Filter and −58 dBc TX HD2. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 11–15 February 2017; pp. 136–137. [Google Scholar]

- Aksin, D.; Gregori, S.; Maloberti, F. High-efficiency power amplifier for wireless sensor networks. In Proceedings of the IEEE International Symposium on Circuits and Systems, ISCAS 2005, Kobe, Japan, 23–26 May 2005; pp. 5898–5901. [Google Scholar]

- Sharifzadeh, M.; Masnadi-Shirazi, A.H.; Rajavi, Y.; Lavasani, H.M.; Taghivand, M. A fully integrated multi-mode high-efficiency transmitter for IoT applications in 40 nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–10 April 2018; pp. 1–4. [Google Scholar]

- Oh, S.; Kim, S.; Ali, I.; Nga, T.T.K.; Lee, D.; Pu, Y.; Yoo, S.-S.; Lee, M.; Hwang, K.C.; Yang, Y.; et al. A 3.9 mW Bluetooth Low-Energy Transmitter Using All-Digital PLL-Based Direct FSK Modulation in 55 nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3037–3048. [Google Scholar] [CrossRef]

- Xu, H.; Palaskas, Y.; Ravi, A.; Sajadieh, M.; El-Tanani, M.A.; Soumyanath, K. A flip-chip-packaged 25.3 dBm class-D outphasing power amplifier in 32 nm CMOS for WLAN application. IEEE J. Solid-State Circuits 2011, 46, 1596–1605. [Google Scholar] [CrossRef]

- Prummel, J.; Papamichail, M.; Willms, J.; Todi, R.; Aartsen, W.; Kruiskamp, W.; Haanstra, J.; Opbroek, E.; Rievers, S.; Seesink, P.; et al. A 10mW Bluetooth Low-Energy transceiver with on-chip matching. IEEE J. Solid State Circuits 2015, 50, 3077–3088. [Google Scholar] [CrossRef]

- Sun, Z.; Liu, H.; Huang, H.; Tang, D.; Xu, D.; Kaneko, T.; Li, Z.; Pang, J.; Wu, R.; Okada, K.; et al. A 0.85 mm2 BLE Transceiver Using an On-Chip Harmonic-Suppressed RFIO Circuitry with T/R Switch. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 196–209. [Google Scholar] [CrossRef]

- Babaie, M.; Kuo, F.W.; Chen, H.N.R.; Cho, L.C.; Jou, C.P.; Hsueh, F.L.; Shahmohammadi, M.; Staszewski, R.B. A Fully Integrated Bluetooth Low-Energy Transmitter in 28 nm CMOS with 36% System Efficiency at 3 dBm. IEEE J. Solid-State Circuits 2016, 51, 1547–1565. [Google Scholar] [CrossRef]

- Kearney, N.; Billon, C.; Deeney, M.; Evans, E.; Khan, K.; Li, H.; Liang, S.; Mulvaney, K.; O’Donoghue, K.A.; O’Mahony, S.; et al. 26.4 a 160-to-960 MHz ETSI class-1-compliant IoE transceiver with 100 dB blocker rejection, 70dB ACR and 800 pA standby current. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 442–443. [Google Scholar]

- Miyashita, D.; Ishikuro, H.; Shimada, T.; Tanzawa, T.; Kousai, S.; Kobayashi, H.; Majima, H.; Agawa, K.; Hamada, M.; Hatori, F. A low-IF CMOS single-chip Bluetooth EDR transmitter with digital I/Q mismatch trimming circuit. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Kyoto, Japan, 16–18 June 2005; IEEE: Piscataway, NJ, USA, 2016; pp. 298–301. [Google Scholar]

- Srimuang, P.; Puangngernmak, N.; Chalermwisutkul, S. 13.56 MHz class E power amplifier with 94.6% efficiency and 31 watts output power for RF heating applications. In Proceedings of the 2014 11th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, Nakhon Ratchasima, Thailand, 14–17 May 2014; pp. 1–5. [Google Scholar]

- Kobayashi, H.; Hinrichs, J.M.; Asbeck, P.M. Current-mode class-D power amplifiers for high-efficiency RF applications. IEEE Trans. Microw. Theory Tech. 2001, 49, 2480–2485. [Google Scholar] [CrossRef]

- Kim, S.J.; Kim, D.G.; Oh, S.J.; Lee, D.S.; Pu, Y.G.; Hwang, K.C.; Yang, Y.; Lee, K.Y. A Fully Integrated Bluetooth Low-Energy Transceiver with Integrated Single Pole Double Throw and Power Management Unit for IoT Sensors. Sensors 2019, 19, 2420. [Google Scholar] [CrossRef] [PubMed]

- Bahamir, S.-M.; Razavi, B. A Digital RF Transmitter with Background Nonlinearity Correction. IEEE J. Solid-State Circuits 2020, 55, 1502–1515. [Google Scholar] [CrossRef]

- Sano, T.; Mizokami, M.; Matsui, H.; Ueda, K.; Shibata, K.; Toyota, K.; Saitou, T.; Sato, H.; Yahagi, K.; Hayashi, Y. 13.4 A 6.3 mW BLE transceiver embedded RX image-rejection filter and TX harmonic-suppression filter reusing on-chip matching network. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

| This Work | [7] TCAS-I22 | [8] ISSCC17 | [10] CICC18 | [11] TCAS-I18 | [13] JSSC15 | [14] TCAS-I21 | [20] Sensors19 | [21] JSSC22 * | |

|---|---|---|---|---|---|---|---|---|---|

| Technology (nm) | 28 | 40 | 55 | 40 | 55 | 55 | 65 | 55 | 28 |

| Supply Voltage (V) | 1.0 | 1.1 | 1.2 | 1.1 | 3 | 3.3 | 0.6 | 3.0 | 1 |

| PA Topology | Class-D | Class-E | Class-AB | Class-D | Class-D | Class-D | Class-E/F2 | Class-D | Class-E |

| Area (mm2) | 0.39 | 0.48 | 2.2 ** | 0.7 | 0.53 | N/A | 0.85 ** | 2.9 ** | 0.112 *** |

| TX max POUT (dBm) | 12.1 | 0 | 8 | 4 | 10.05 | 0 | 0 | 0 | 24.1 |

| TX min POUT (dBm) | −31 | −10 | N/A | −10 | −23 | −20 | −6 | N/A | 5 |

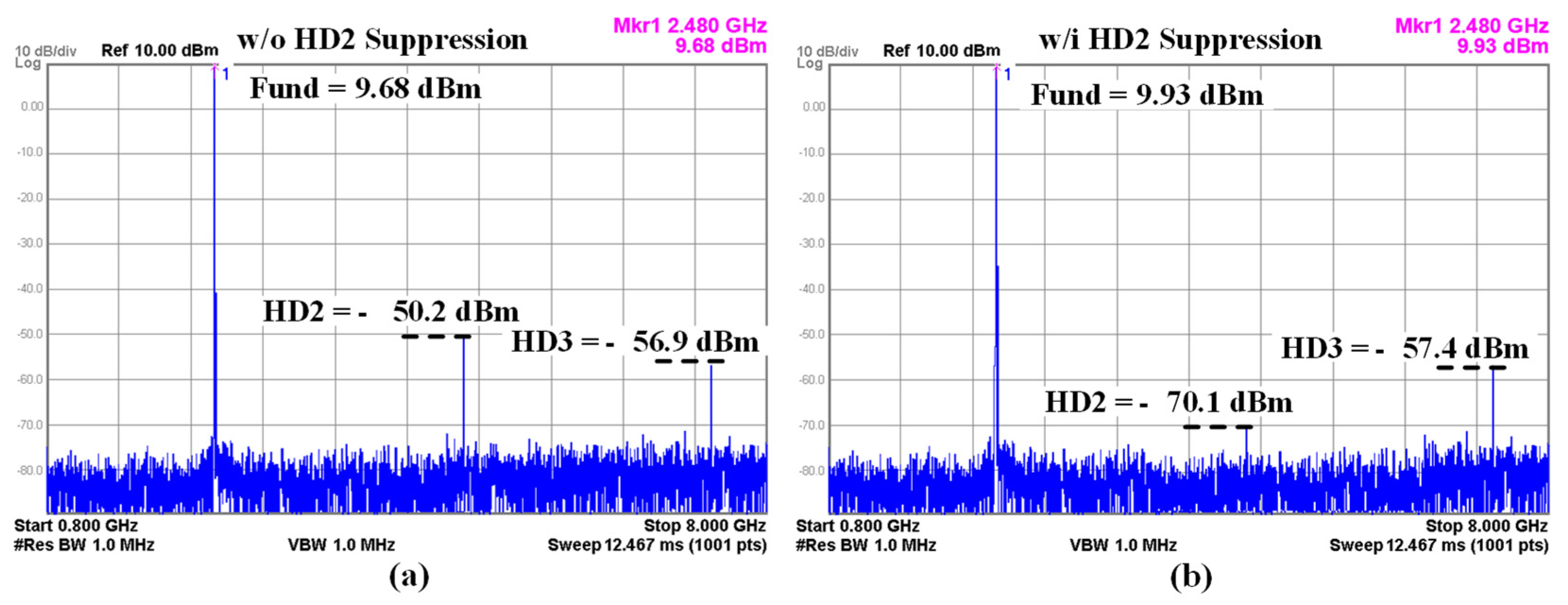

| HD2 @ POUT (dBc) | −82.2 @ +9.93 | −41.3 @ −3 | −58 @ +8 | −52 @ 0 | −45.6 @ +1.6 | −54 @ 0 | −58 @ 0 | −50.07 @ 0 | N/A |

| HD3 @ POUT (dBc) | −67.3 @ +9.93 | −54.2 @ −3 | −64 @ +8 | −30 @ 0 | −50.6 @ +1.6 | −52 @ 0 | −64 @ 0 | −47.08 @ 0 | N/A |

| Max. PDC @ POUT (mW) | 41.1 @ +12.1 | 4.85 @ 0 | 79.8 @ +8 | N/A | 18 @ +10 | 10.1 @ 0 | 5.4 @ 0 | 6 @ 0 | N/A |

| Max. Efficiency @ POUT (%) | 40.6 @ +12.1 | 20.6 @ 0 | 7.9 @ +8 | N/A | 55.6 @ +10 | 9.9 @ 0 | 18.5 @ 0 | 16.7 @ 0 | N/A |

| Max. PAE @ POUT (%) | 37.9 @ +11.9 | N/A | N/A | N/A | N/A | N/A | N/A | N/A | 50 @ 24.1 |

| PDC @ POUT (mW) | 29.4 @ +9.93 | 3.22 @ −3 | 79.8 @ +8 | 4.5 @ 0 | 3.9 @ +1.6 | 10.1 @ 0 | 5.4 @ 0 | 6 @ 0 | N/A |

| Efficiency @ POUT (%) | 33 @ +9.93 | 15.6 @ −3 | 7.9 @ +8 | 22.2 @ 0 | 37.1 @ +1.6 | 9.9 @ 0 | 18.5 @ 0 | 16.7 @ 0 | N/A |

| PAE @ POUT (%) | 32.1 @ +9.93 | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A |

| TX_FoM @ POUT (dB) | −97.52 @ +9.93 | −66.52 @ −3 | −68.99 @ −3 | −75.47 @ 0 | −69.69 @ +1.6 | −73.96 @ 0 | −80.68 @ 0 | −72.68 @ 0 | N/A |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, N.-S. A 2.4 GHz Wide-Range CMOS Current-Mode Class-D PA with HD2 Suppression for Internet of Things Applications. Sensors 2024, 24, 1616. https://doi.org/10.3390/s24051616

Kim N-S. A 2.4 GHz Wide-Range CMOS Current-Mode Class-D PA with HD2 Suppression for Internet of Things Applications. Sensors. 2024; 24(5):1616. https://doi.org/10.3390/s24051616

Chicago/Turabian StyleKim, Nam-Seog. 2024. "A 2.4 GHz Wide-Range CMOS Current-Mode Class-D PA with HD2 Suppression for Internet of Things Applications" Sensors 24, no. 5: 1616. https://doi.org/10.3390/s24051616

APA StyleKim, N.-S. (2024). A 2.4 GHz Wide-Range CMOS Current-Mode Class-D PA with HD2 Suppression for Internet of Things Applications. Sensors, 24(5), 1616. https://doi.org/10.3390/s24051616