1. Introduction

The market for CMOS image sensors (CISs) has been growing steadily, owing to the increasing demand for various applications, such as mobile devices, computer vision, and medical devices [

1,

2]. Consequently, there has been an increasing interest in basic CIS functionality and Wide Dynamic Range (WDR) CISs, which can capture a broader range of light intensities, and low-noise CISs, which aim to reduce noise under low-light conditions. Various approaches have been proposed to develop WDR and low-noise CISs [

3,

4,

5]. However, in-pixel WDR methods, such as those described in [

1,

2], suffer from issues related to process incompatibility, leading to problems such as image lag, distortion caused by frame delays and significant vertical fixed-pattern noise (FPN).

Furthermore, applying gamma correction as proposed in [

3,

4,

5] requires additional memory circuitry in image sensors equipped with logarithmic counters. Gamma correction leads to adjustments in low-light regions primarily, which can result in information loss in high-intensity regions following the correction. The gamma correction technique performs correlated double sampling (CDS) at a frequency twice as fast as when a low-light input signal is input than when a high-light input signal is received, resulting in a Signal-to-Noise Ratio (SNR) improvement effect similar to the results of correlated multiple sampling (CMS). CMS is a technique that effectively reduces the standard deviation of low-light random noise by averaging repeated sampling results. When the number of repeated samplings is

N, there is a noise reduction effect of the square root N [

6,

7].

Similarly, in the method described in [

3], gamma correction was applied in segments to improve the dynamic range; however, this approach significantly increased the exposure time of the pixels. To address these issues, a bidirectional gamma (B-gamma) correction WDR CIS, which adjusts both low-light and high-intensity regions simultaneously, has been proposed [

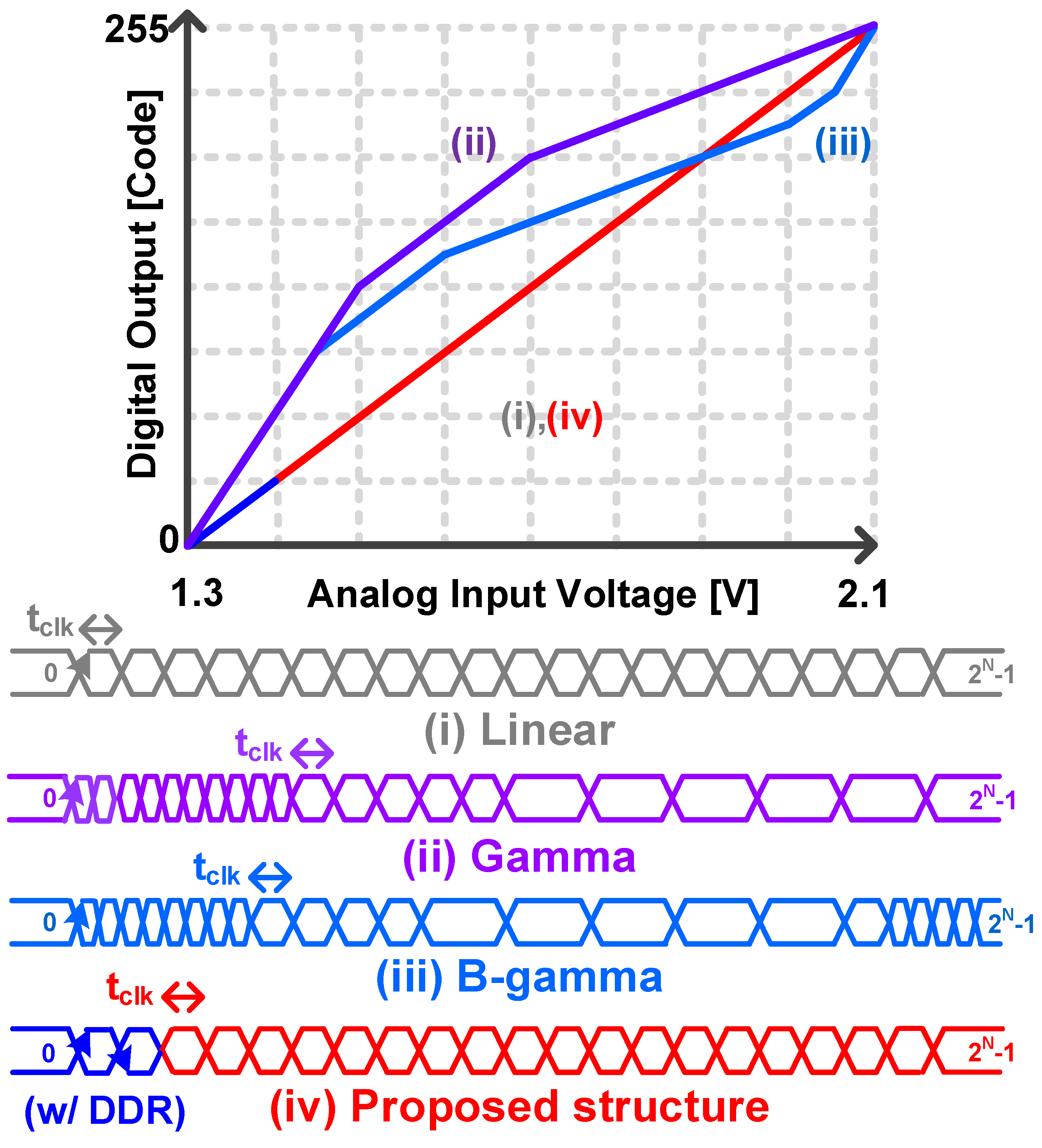

3]. As shown in

Figure 1, gamma and B-gamma show nonlinear input–output characteristics. Therefore, additional computation is required to generate a linear response at the image signal processor (ISP) stage connected to the sensor [

8].

In this study, we aimed to implement a low-noise CIS by designing a 10/11-bit hybrid Single-Slope Analog-to-Digital Converter (SS-ADC) that enables a partially-higher-resolution output in low-light conditions, while maintaining an overall linear response.

Figure 1 addresses the shortcomings of the aforementioned gamma correction and bidirectional gamma correction methods, which exhibit nonlinear in–out characteristics. The linear response allows for better noise reduction by applying digitally correlated double sampling (D-CDS), which minimizes the error voltages during noise reduction. Additionally, by enhancing the resolution only in low-light regions, rather than across the entire image, the toggling frequency of the counter does not increase for the full counting range, thereby improving the output of meaningful data in the image. To implement the proposed architecture, a double data rate (DDR) structure was applied to the Least Significant Bit (LSB) stage of the column counter, allowing digital codes with an increased 1-bit resolution to be output only in the desired regions. It should be noted that all modes had the same data conversion time when the clock frequencies were adjusted.

The output characteristics of the proposed approach are shown in

Figure 2. In the range of output codes that predominantly appear in dark images, such as those below 1/8 of the full code, the image is output with an 11-bit resolution, where one additional bit is used. For the subsequent code range, the edge-triggered data flip-flop (ETDFF) used for the LSB in DDR is turned off, maintaining the HIGH of the LSB stage.

Furthermore, this implementation results in a lower power consumption, compared to a conventional 11-bit resolution Single-Slope ADC, while maintaining the linearity of the entire output code by producing 10-bit resolution images for regions other than low-light areas. Furthermore, the LSB control block was designed to allow for an adjustable output code region with an 11-bit resolution. The remainder of this paper is organized as follows. In

Section 2, we present the design of a low-noise CIS by using the proposed D-CDS method. In

Section 3, the layout, simulation, and measurement results are discussed. Finally, the conclusions are presented in

Section 4.

2. Proposed CIS Structure

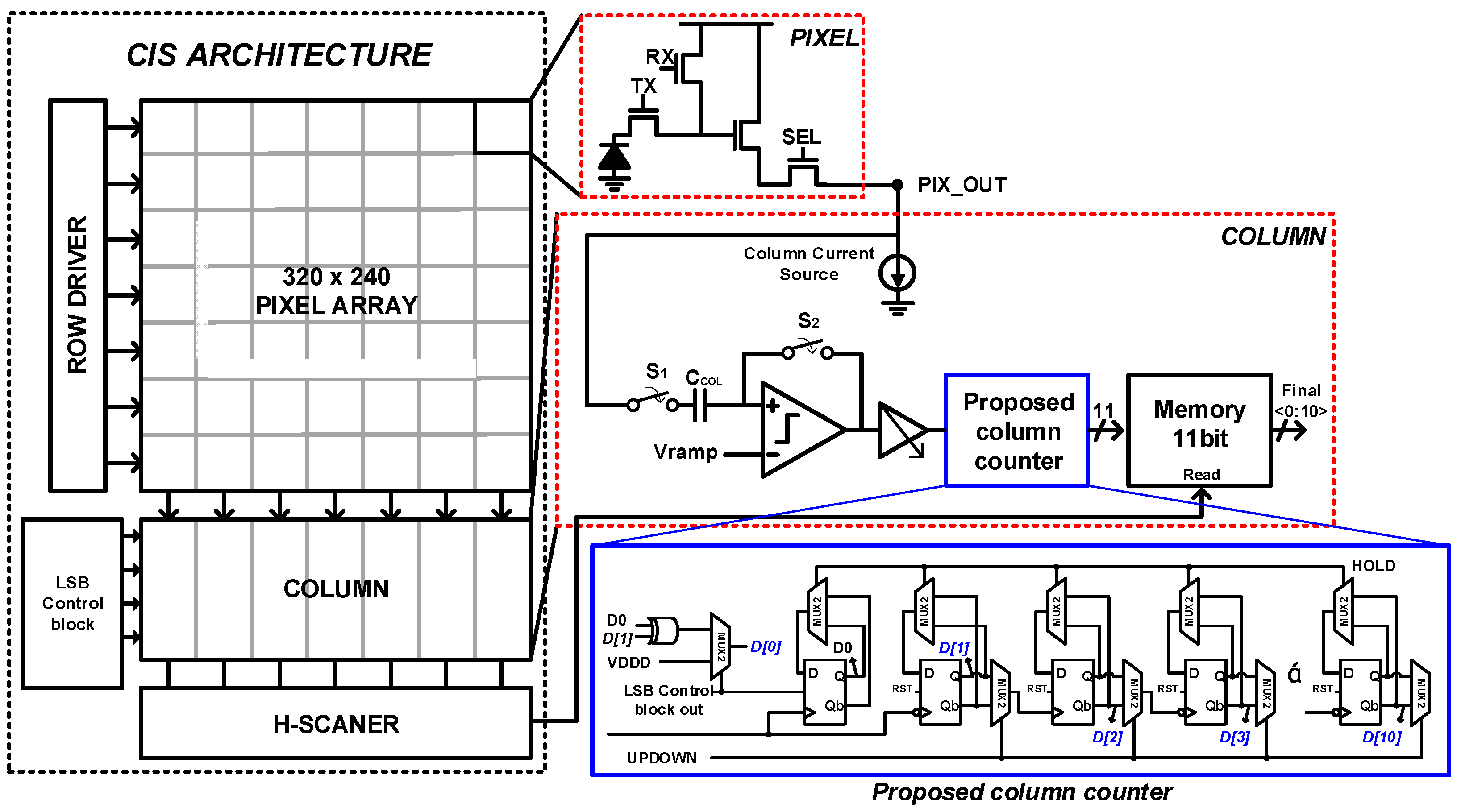

Figure 3 shows the overall block diagram of the proposed CIS. The pixel uses a 4-transistor Active Pixel Sensor (4-Tr APS) structure, and the memory was implemented using the ETDFF. The proposed column counter structure consists of an LSB counter unit implemented using a DDR and an Up/Down (U/D) counter unit for the subsequent bits. The U/D counter unit comprises two multiplexers (MUXs) that determine the HOLD and Up/Down operations, and one ETDFF. Although the proposed structure operates based on Digital Correlated Double Sampling (D-CDS), Analog Correlated Double Sampling (A-CDS) is also performed during the conversion process to allow the ADC to operate, regardless of the pixel voltage range input.

The operation sequence of the proposed CIS is as follows. The pixel array was controlled by a row driver. The reset voltage of the pixels was down-counted using a column counter. When the reset voltage matches the ramp voltage, the comparator flips its output, causing the counter to stop toggling and to latch the data. Subsequently, the signal voltage, which decreased in proportion to the incident light, was compared to the ramp voltage of the comparator. The column counter up-counts to offset the voltage generated by the same pixel and toggles until the ramp voltage matches the signal voltage.

During the up-counting process, the LSB, D[0], toggles via the DDR LSB unit, outputting an 11-bit code, whereas the LSB_CONT signal from the LSB control block is HIGH. When LSB_CONT becomes LOW, the DDR LSB unit stops toggling, resulting in an output of the 10-bit code. When the ramp signal matches the signal voltage, the column counter output is latched and stops toggling, thereby outputting the effective signal value as a digital code. The counter output is then stored in memory and, subsequently, output through the control by the H-scanner.

2.1. A 10/11-Bit Hybrid ADC

A 10/11-bit hybrid ADC was proposed for a low-noise CIS with linear output-response characteristics. In the case of multiple sampling, the noise reduction ratio theoretically corresponds to the square root of

N for the number of multiples

N [

9]. Because the image output of the Log-exponential Complex Counter (LCC) was corrected by adjusting the digital gain, the images were compared using the Modified Absolute Mean Brightness Error (M-AMBE) [

10]. Because the colors of the color blocks inside the Macbeth ColorChecker, a color chart, are constant, each color of the blocks is converted to a standard RGB (sRGB), expressed as R, G, and B values, and then converted to grayscale for actual measurements using the values as a standard. The M-AMBEs of each image were compared. As a result of the comparison, the M-AMBE improvement in images taken at 20 lx, a low-light area (=1/16 or less of the total output code), was found to be up to approximately 20% [

10]. In the case of the proposed SS-ADC, multiple sampling areas were designated using a counter, and the ADC had ADC characteristics of 11 bits under low illumination and 10 bits under high illumination. Therefore, we analyzed the noise reduction effect of the final output by adjusting the transition point from 10-bit to 11-bit to 1/8, 1/16, and 1/32 of the total output code, as shown in

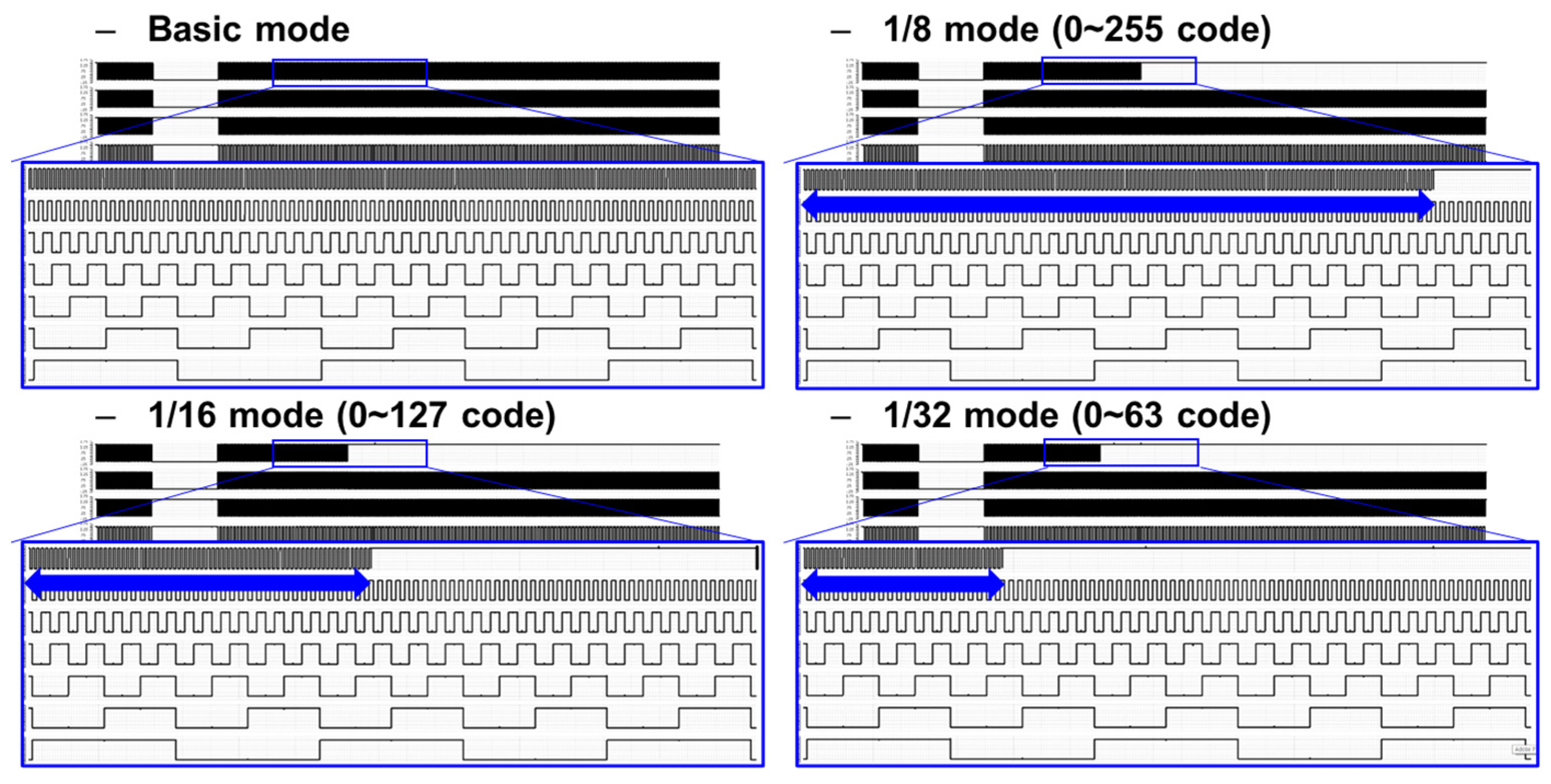

Figure 4.

2.2. Conventional U/D Counter

The proposed structure operates based on the D-CDS. However, for the ADC to operate, regardless of the range of the pixel voltage input to the ADC, A-CDS is also performed during the conversion process using a DC blocking capacitor, as shown in

Figure 5a.

Figure 5b illustrates the timing diagram of the A-CDS, which performs voltage distribution according to the law of charge conservation.

Figure 6 shows the block diagram of a conventional U/D counter. In the case of a method that applies bidirectional gamma correction by adjusting the digital gain using LCC, when compared to a conventional SS-ADC structure, the output code at a low-illuminance (approximately 0–255 out of 2047) range and Signal-to-Noise Ratio (SNR) were improved [

3]. However, in the case of high illuminance, the noise improvement effect is negligible because photon shot noise is dominant.

In addition, when applying gamma correction and bidirectional gamma correction, additional calculations are inevitable in the image signal processor (ISP) connected to the back of the image sensor, owing to the nonlinear input–output response characteristics. Accordingly, the image and noise were improved only by increasing the digital gain in the low-light area. However, a structure that maintains an overall linearity by applying a normal gain (

1) in the high-light area is still required. However, as mentioned earlier, additional bits of resolution output only in low-light conditions cannot be implemented with the existing U/D counter structure. When the LSB stage ceases to operate after switching off in low-light areas, the operation of the entire counter stops because of the structure of the counter, in which the output of the previous stage is used as the input for the next stage. The simulation results are shown in

Figure 6, which shows the stopping of the toggling of the first ETDFF. To solve this issue, the proposed 10/11-bit hybrid SS-ADC uses a DDR structure to separate the rest of the LSB stage from the other counter stages.

2.3. The Proposed Counter Using a Double Data Rate for the 10/11-Bit Hybrid ADC

Figure 7 shows the proposed one-column CIS structure and the operation of the proposed U/D counter with DDR to obtain a 10/11-bit hybrid ADC operation. Compared to the single data rate (SDR), the counter structure with a DDR enables twice the data transmission with the same clock signal. The DDR structure was implemented inside the U/D counter using a negative ETDFF, positive ETDFF, and XOR.

Figure 8 shows the output for each mode of the LSB control block. The CIS proposed to control the change point from 11-bit to 10-bit, which can operate in four modes using the CNTL [0:1] of the LSB control block. It is possible to check the change in noise by adjusting the mode-change point. The simulation results confirm the mode-change point that outputs an additional 1-bit resolution for each mode change, as shown in

Figure 8. Design simulations and analyses were performed for normal operating conditions with 3.3 and 1.5 V of analog and digital supply voltages, 10 MHz of main clock frequency (=data clock frequency in this work for 15 FPS with 0.27 ms of 1 horizontal time, 1H-time), and an operating temperature of 25 °C.