A 78.8–84 GHz Phase Locked Loop Synthesizer for a W-Band Frequency-Hopping FMCW Radar Transceiver in 65 nm CMOS

Abstract

:1. Introduction

2. W-Band Cross-Coupled VCO Design

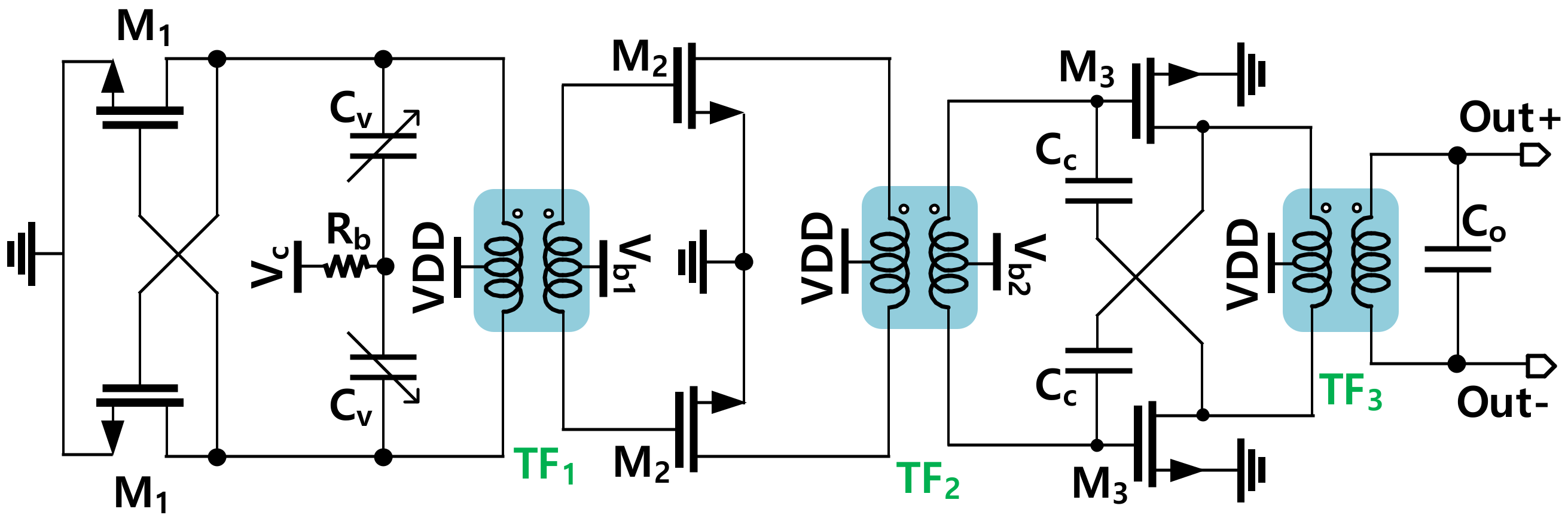

2.1. VCO Configuration

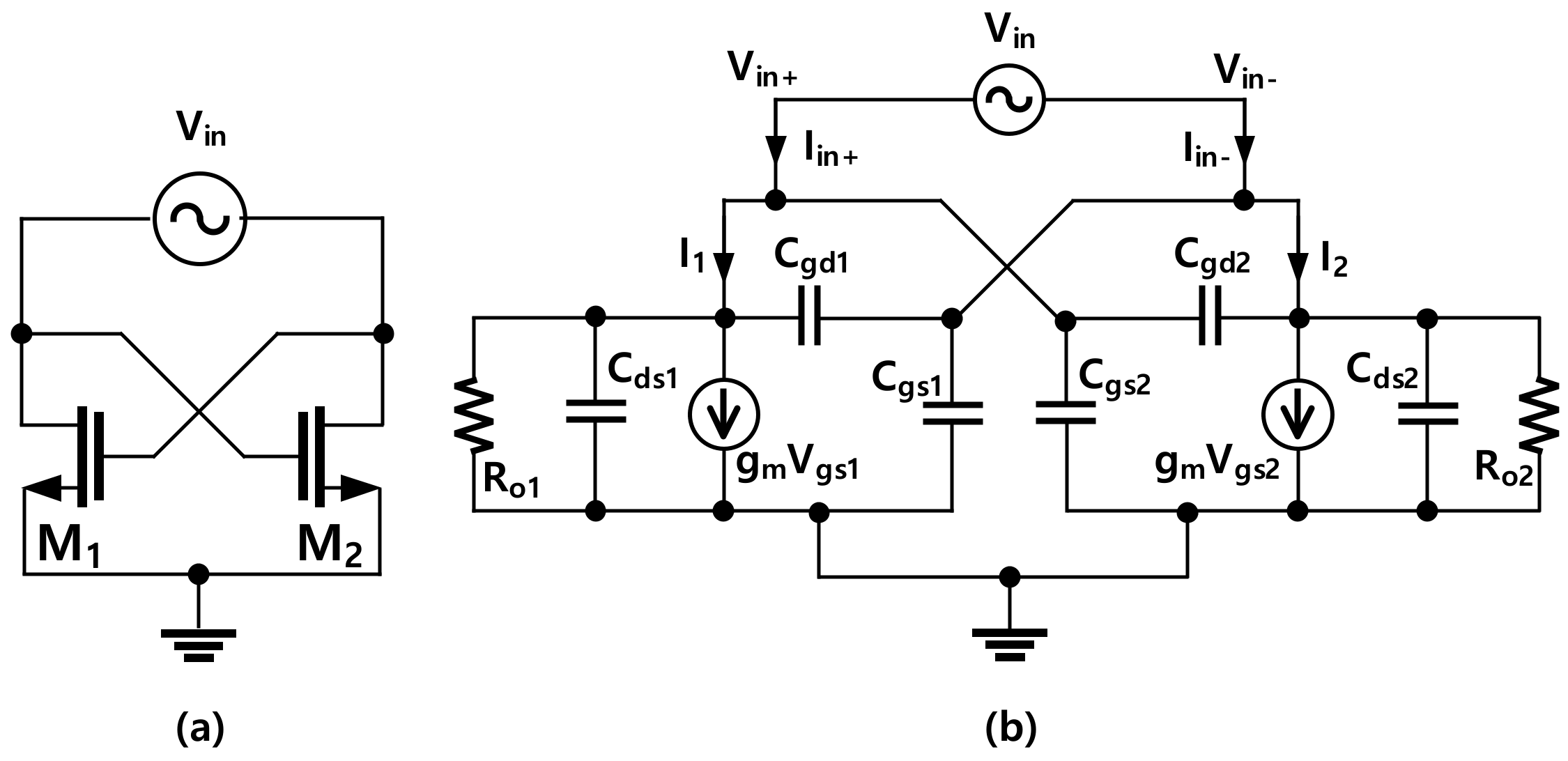

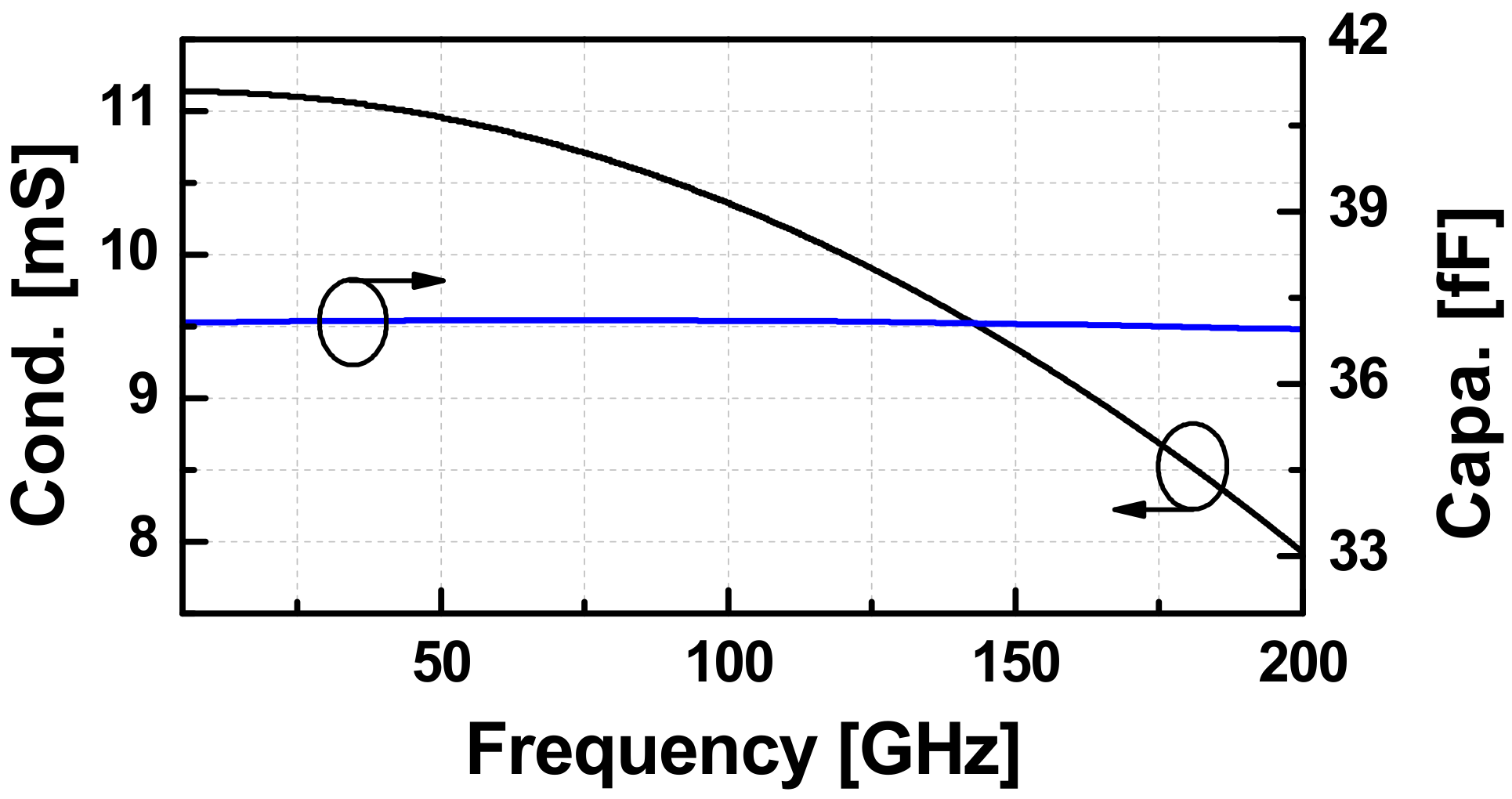

2.2. Cross-Coupled Pair Design Considerations

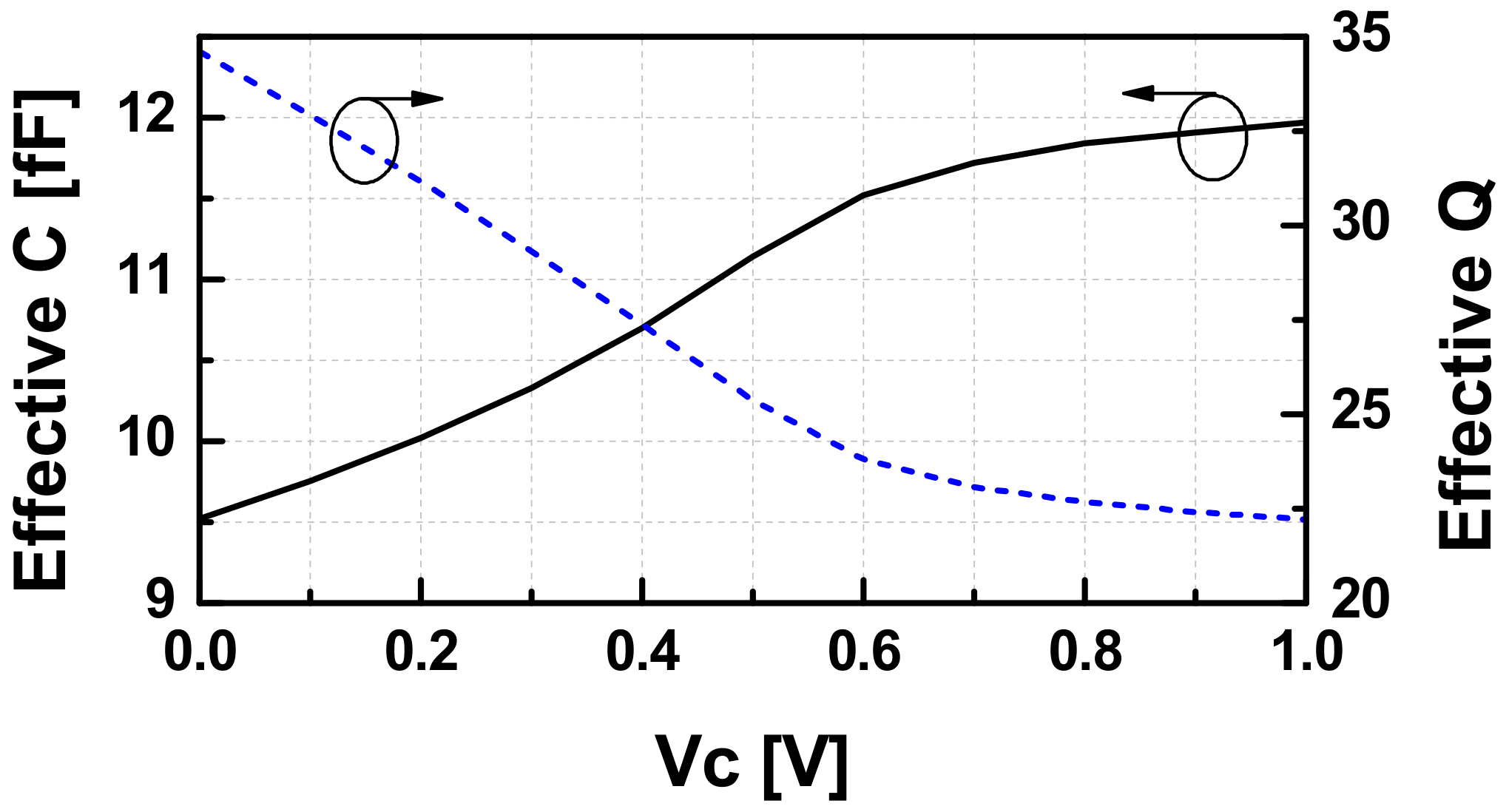

2.3. Variable Capacitor Design

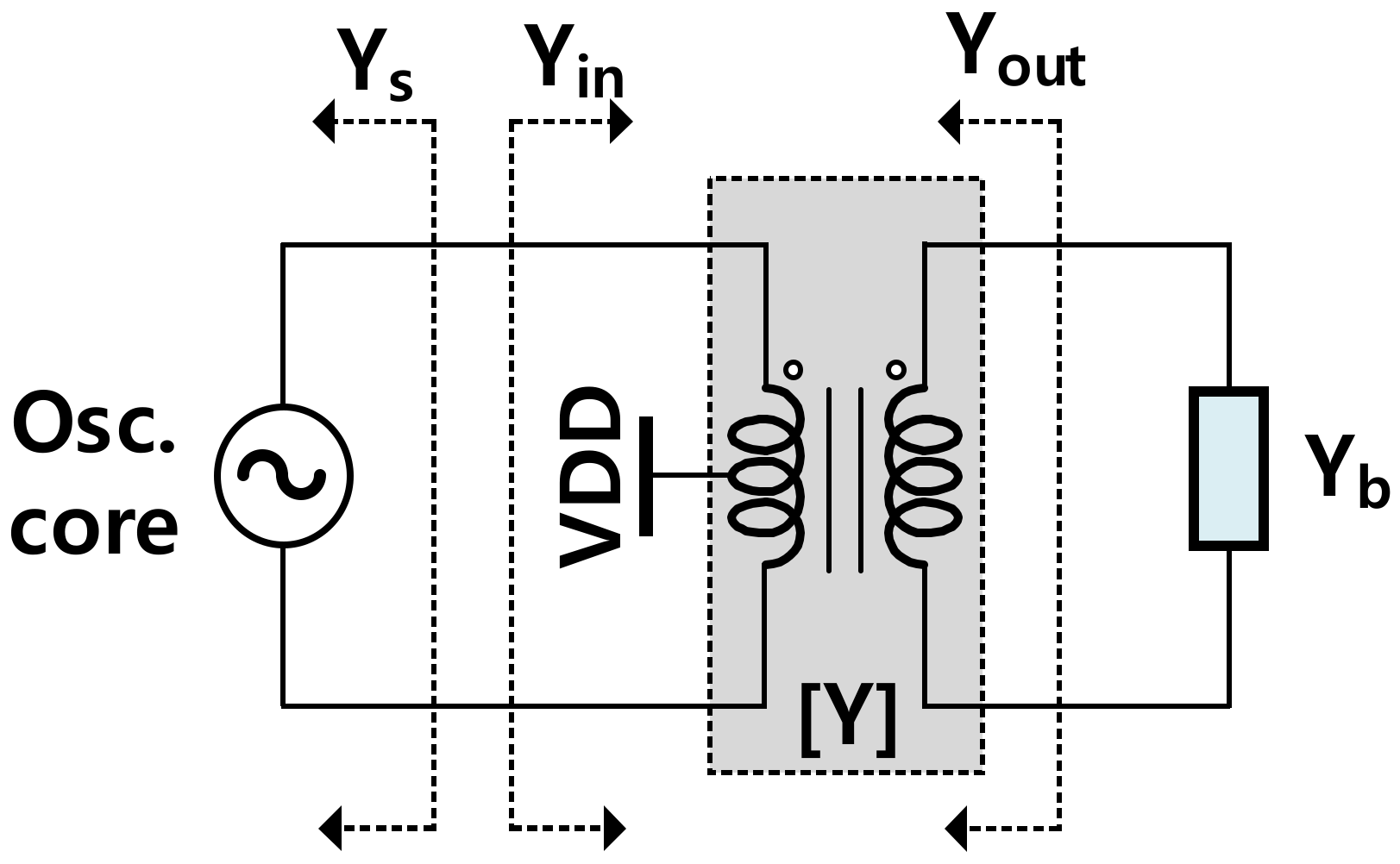

2.4. VCO Buffer Design with a Coarse Control Knob

2.5. VCO Design

3. Integer-N Phase-Locked Loop Design

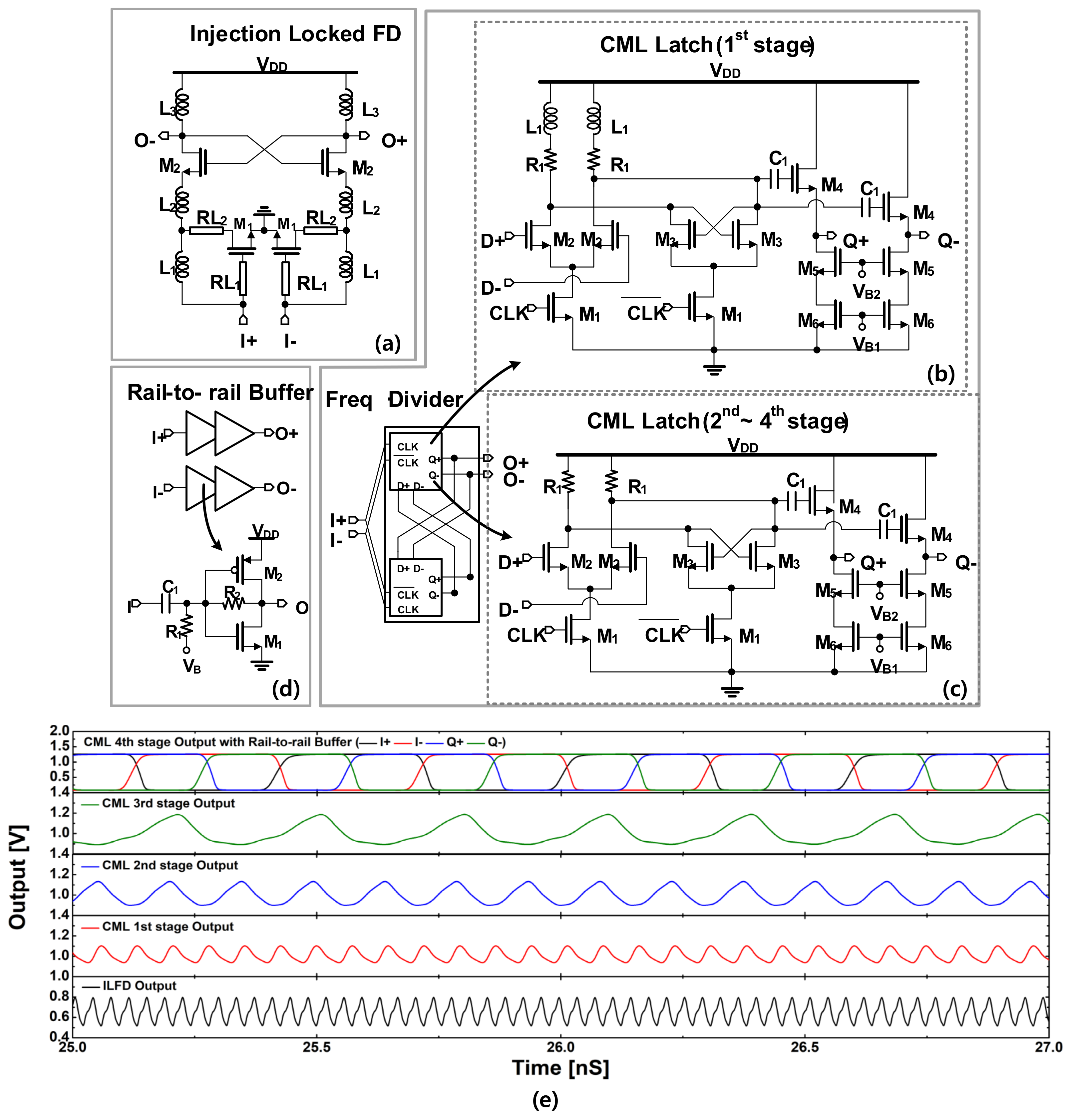

3.1. Divider Chain

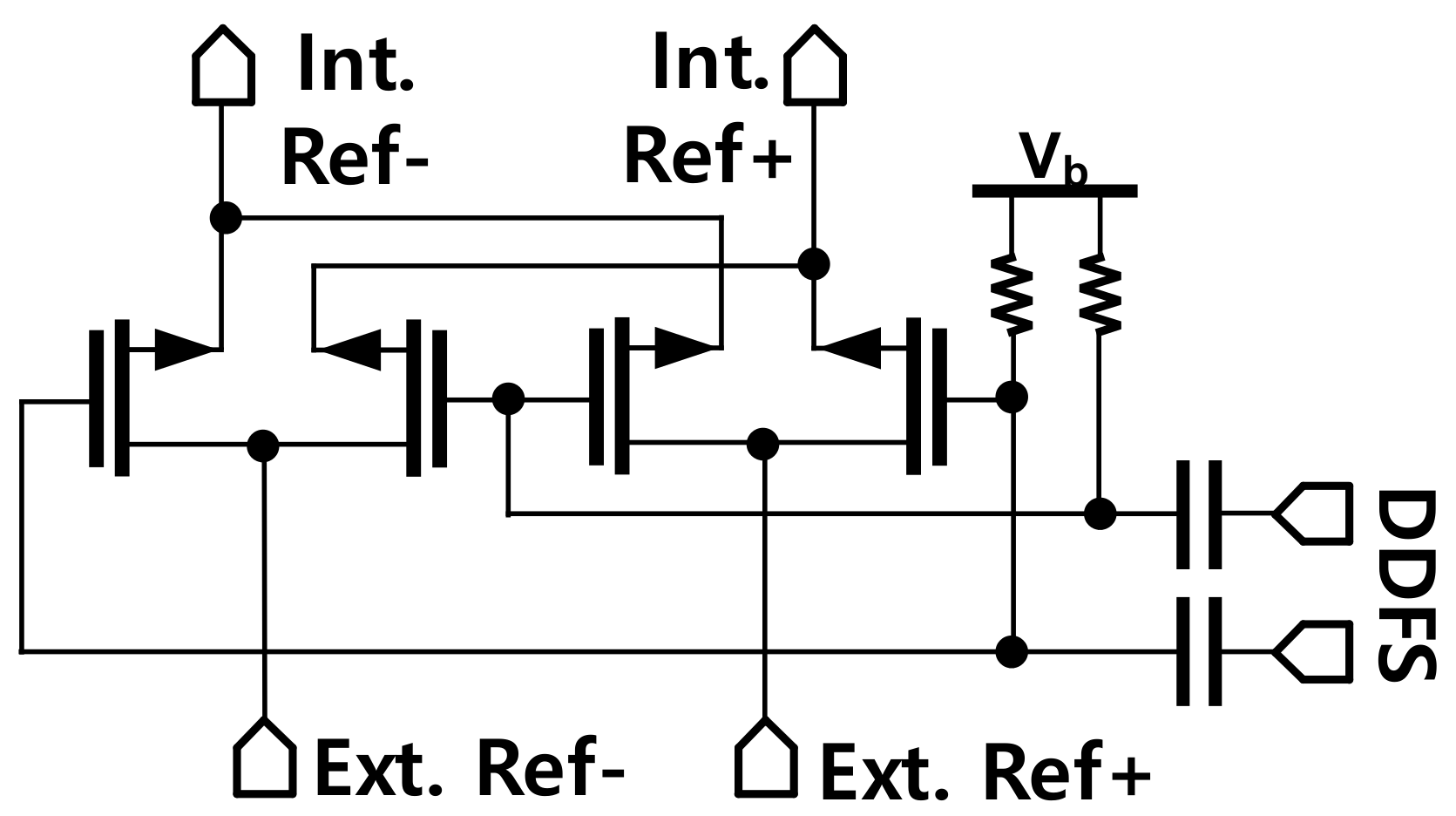

3.2. PD, FD, Loop Filter, and the Reference Clock

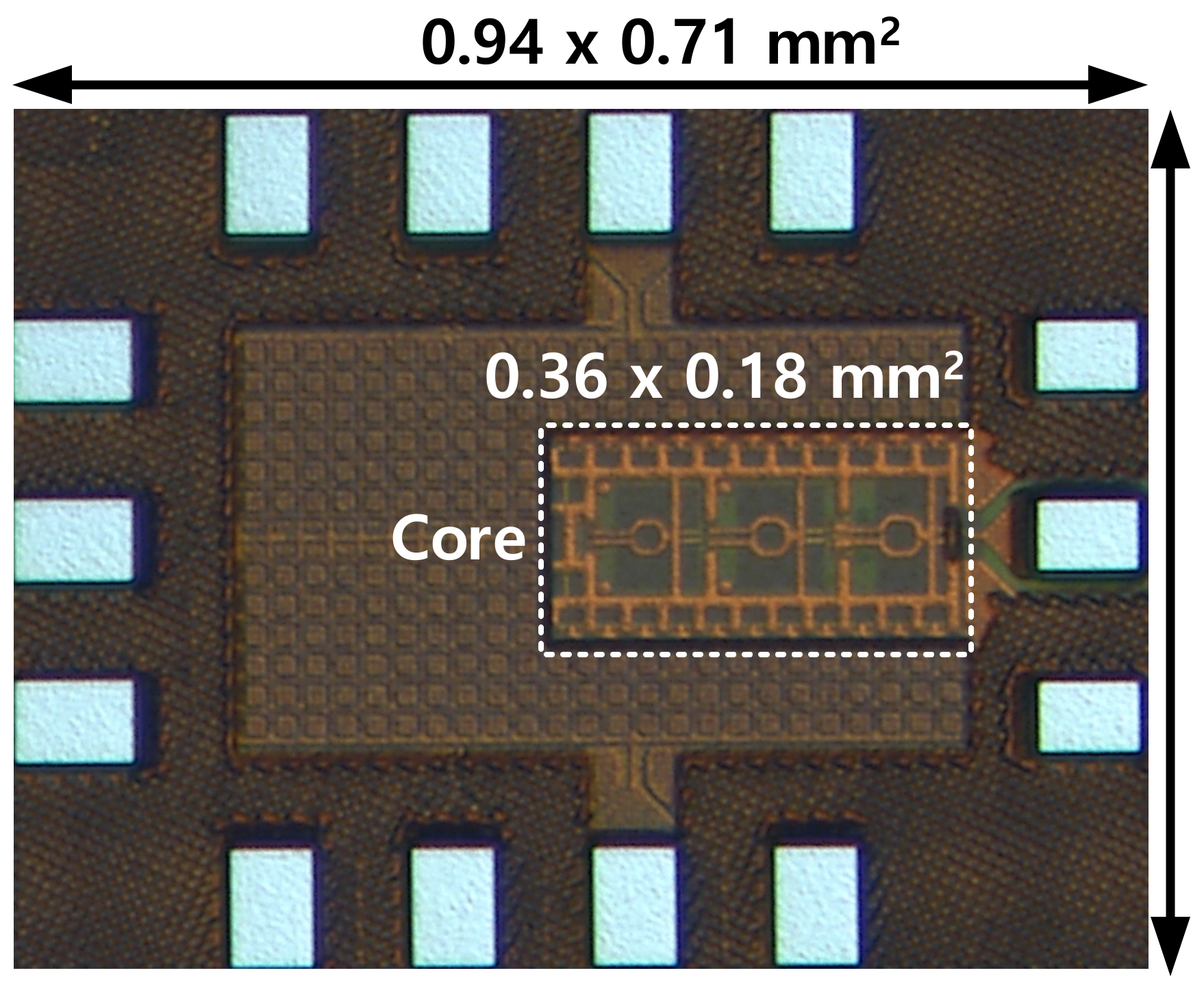

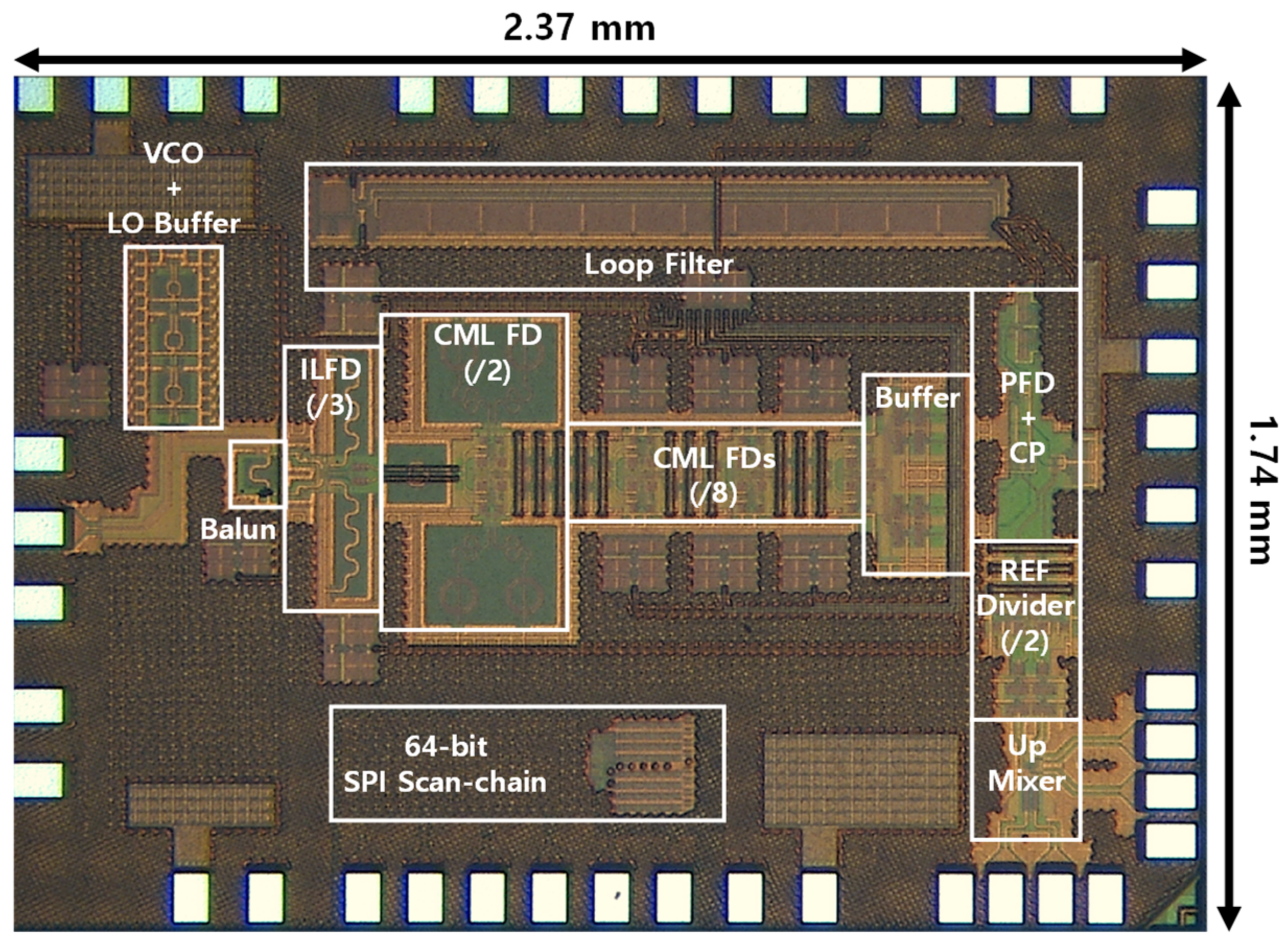

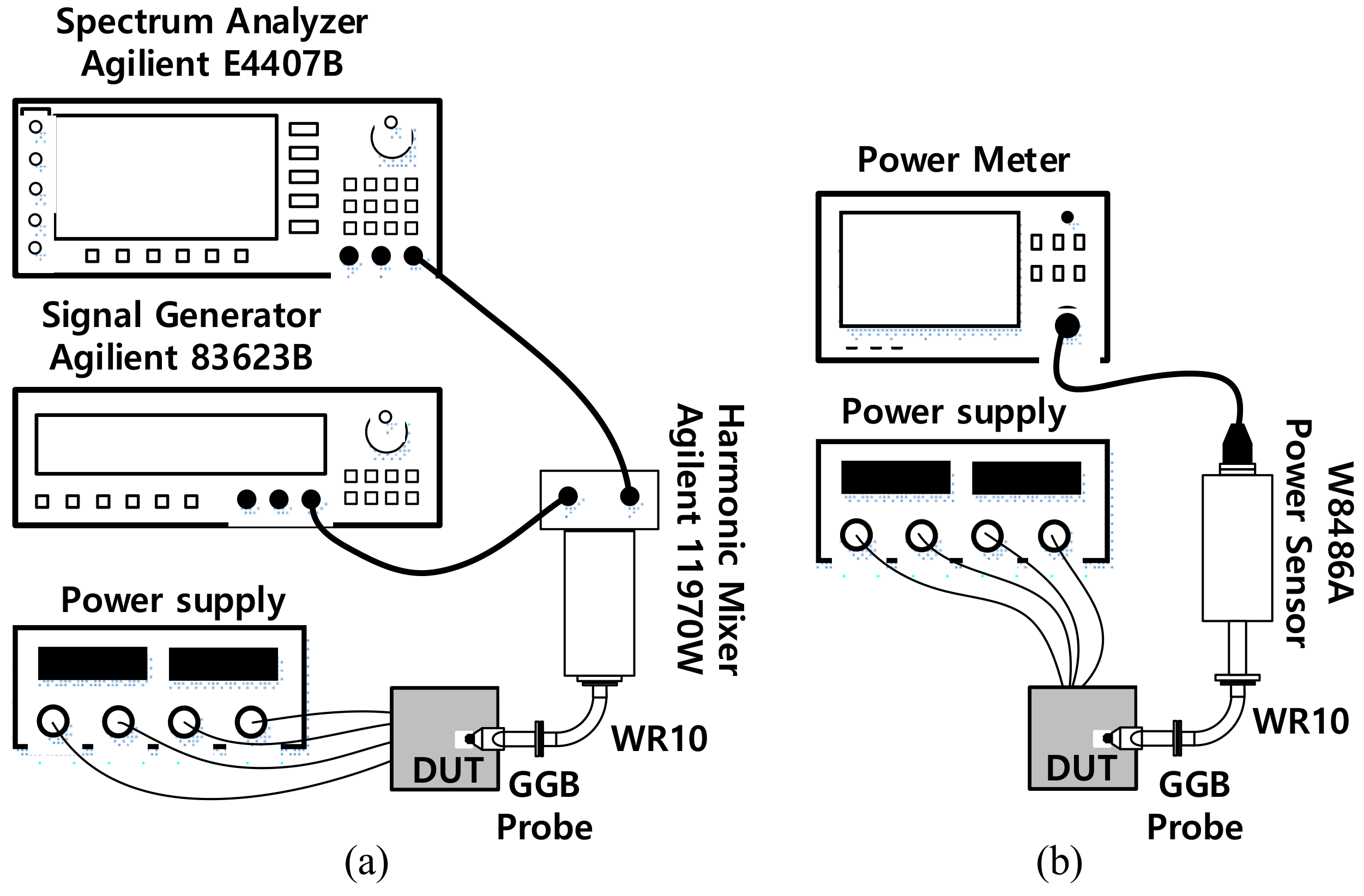

4. Measurement Results

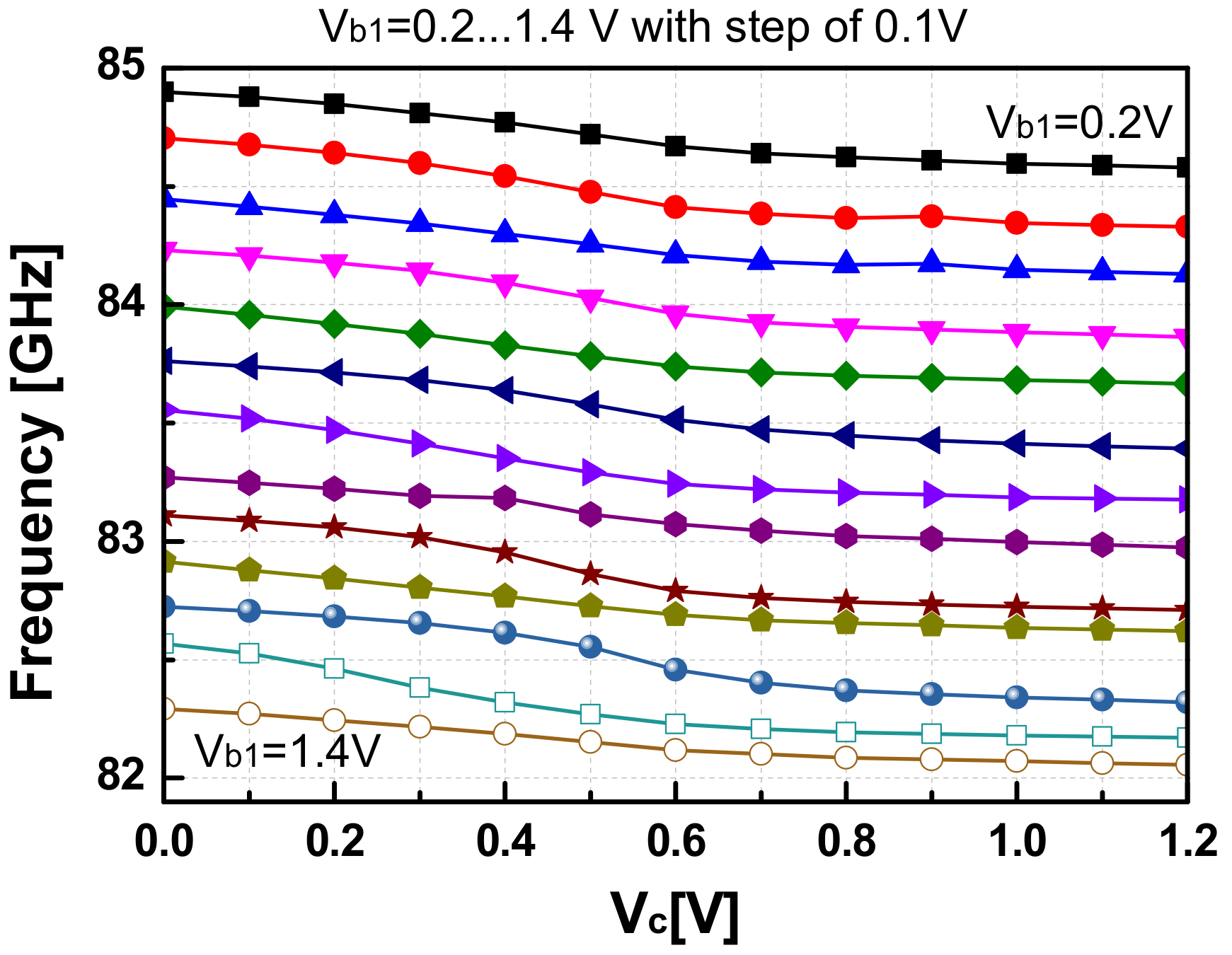

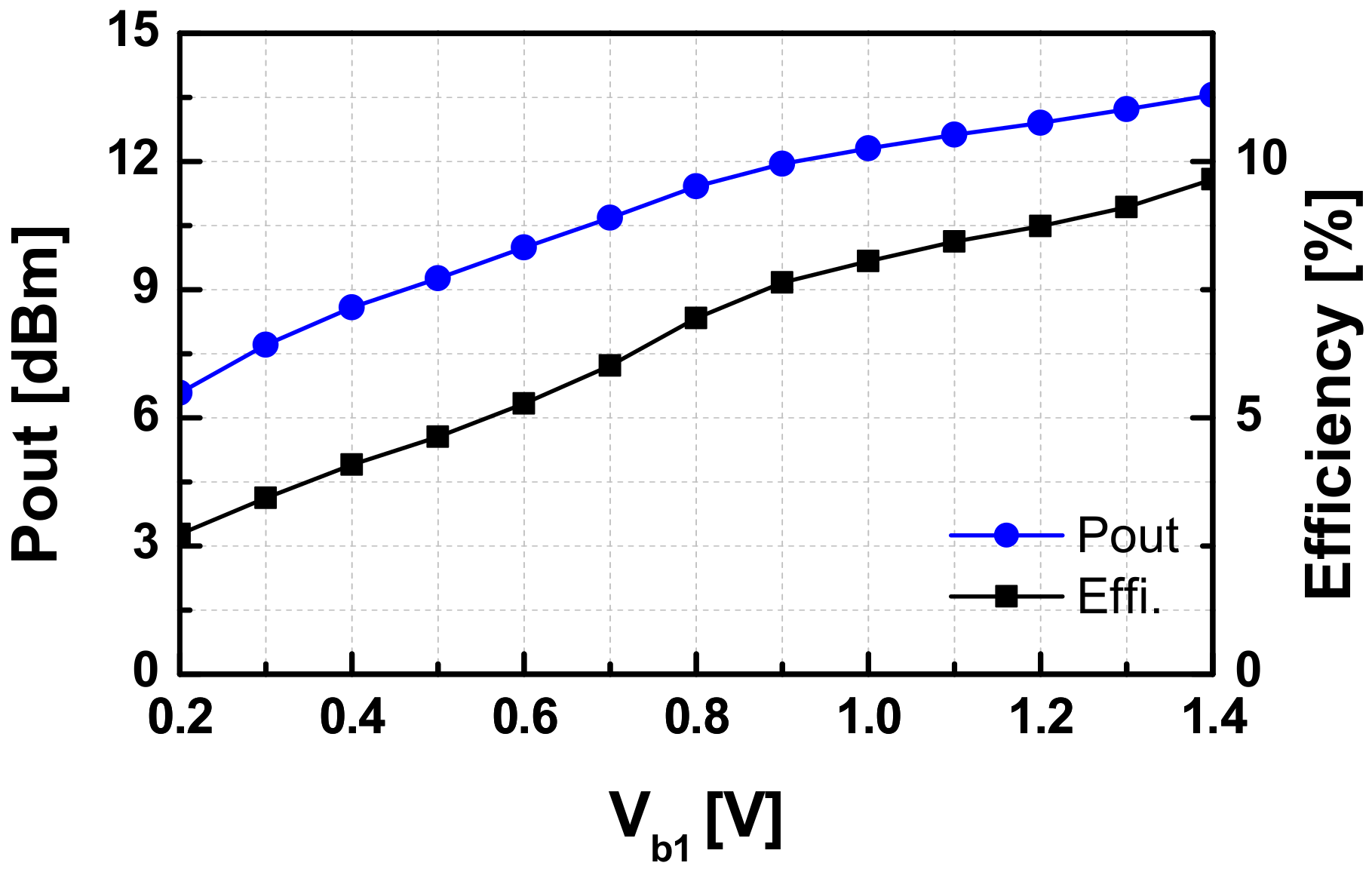

4.1. Stand-Alone VCO Measurements

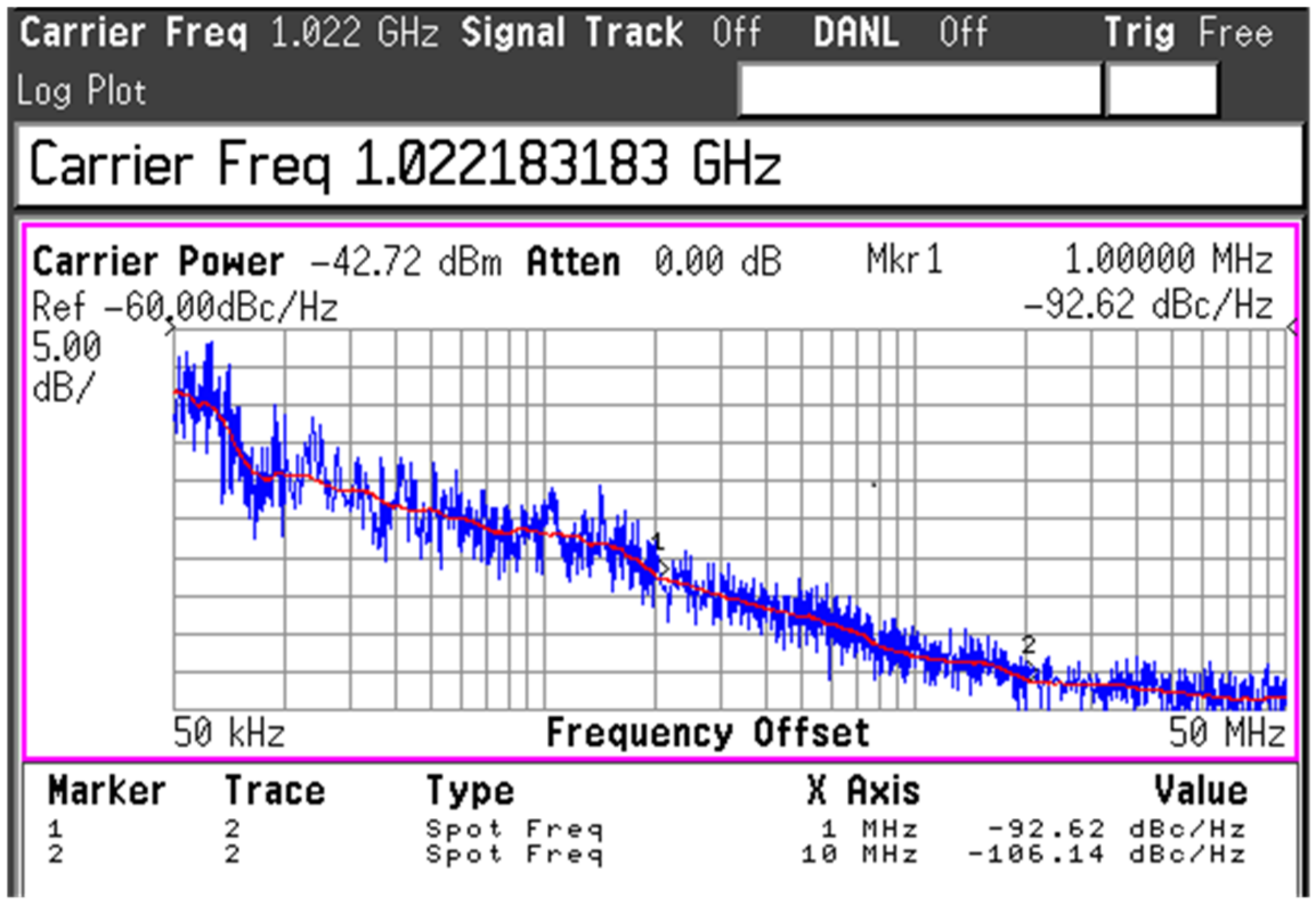

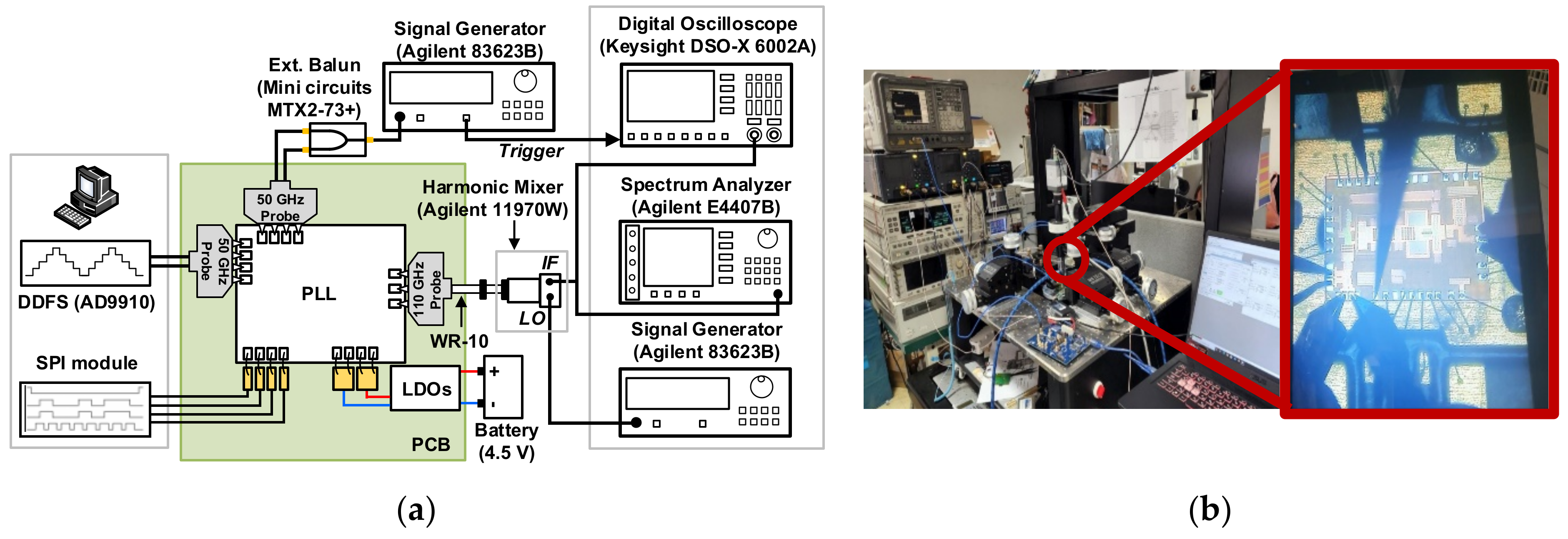

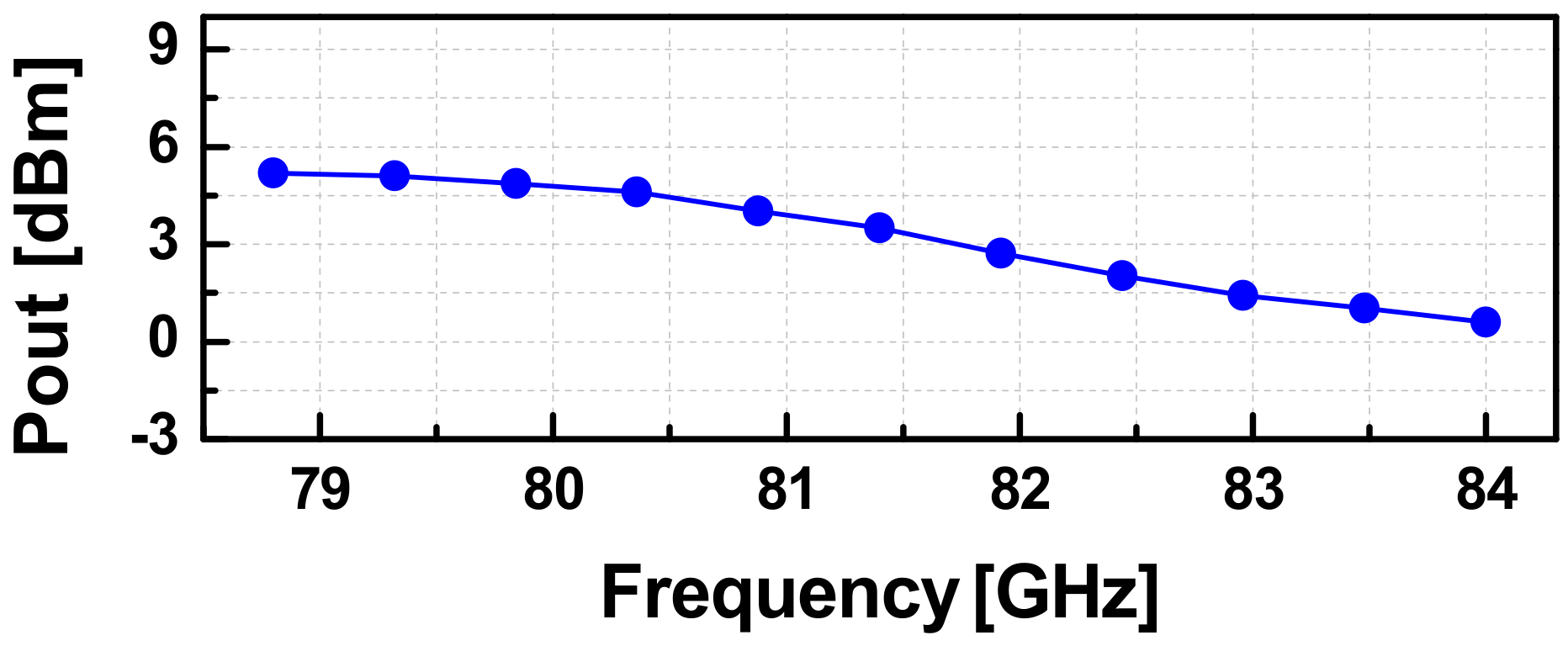

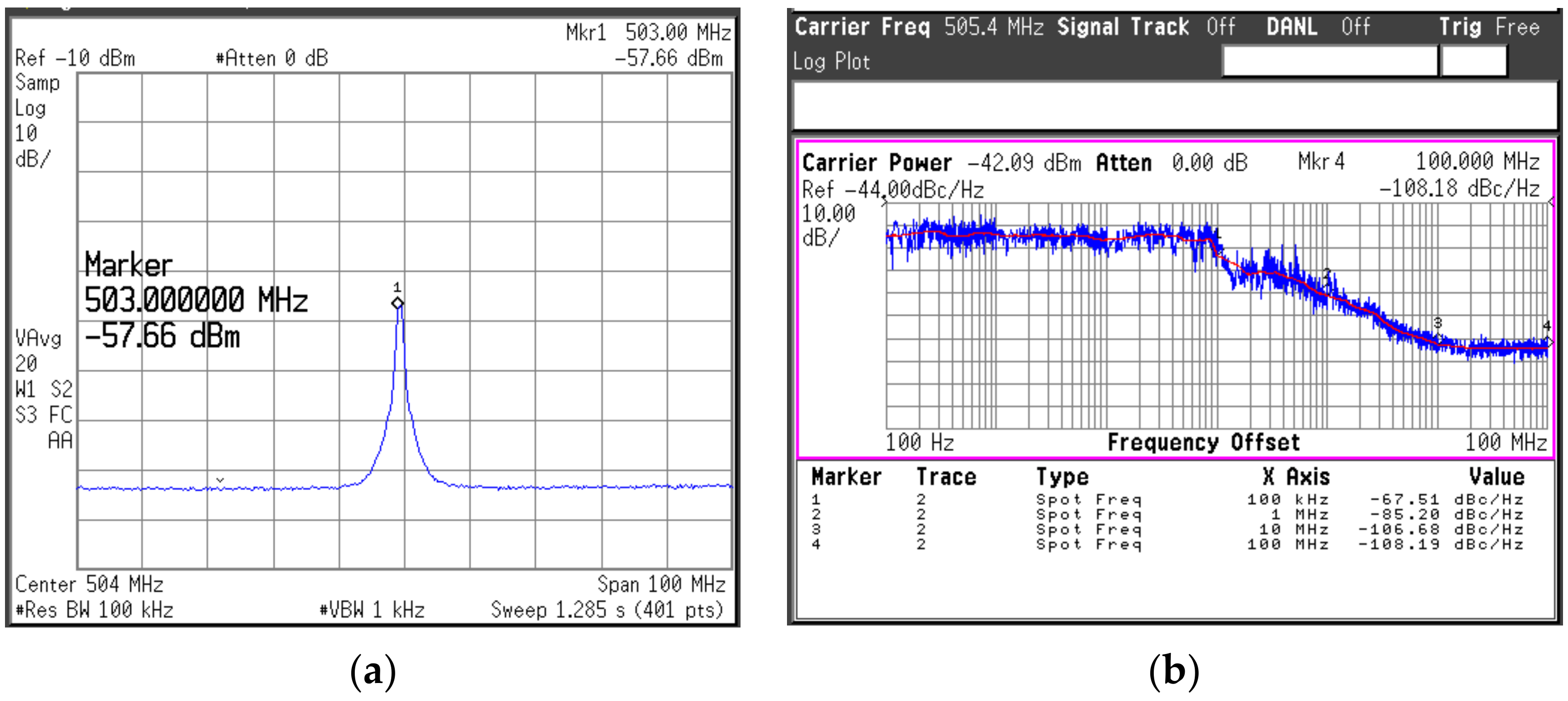

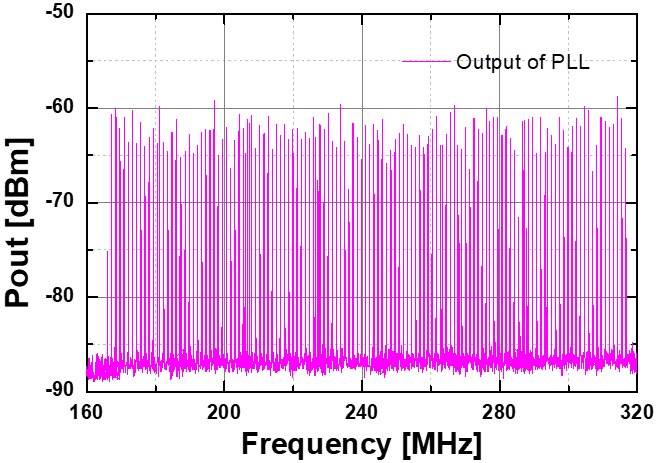

4.2. PLL Measurements

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Uwaechia, A.N.; Mahyuddin, N.M. A Comprehensive Survey on Millimeter Wave Communications for Fifth-Generation Wireless Networks: Feasibility and Challenges. IEEE Access 2020, 8, 62367–62414. [Google Scholar] [CrossRef]

- Pan, D.; Duan, Z.; Wu, B.; Wang, Y.; Huang, D.; Wang, Y.; Sun, L.; Gui, P.; Cheng, L. A 76-81-GHz Four-Channel Digitally Controlled CMOS Receiver for Automotive Radars. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 1091–1101. [Google Scholar] [CrossRef]

- Papotto, G.; Nocera, C.; Finocchiaro, A.; Parisi, A.; Cavarra, A.; Castorina, A.; Ragonese, E.; Palmisano, G. A 27-mW W-Band Radar Receiver with Effective TX Leakage Suppression in 28-Nm FD-SOI CMOS. IEEE Trans. Microw. Theory Tech. 2021, 69, 4132–4141. [Google Scholar] [CrossRef]

- Wu, J.; Deng, W.; Chen, Z.; Zheng, W.; Liu, Y.; Wang, S.; Qi, N.; Chi, B. A 77-GHz mixed-mode FMCW generator based on a vernier TDC with dual rising-edge fractional-phase detector. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 60–73. [Google Scholar] [CrossRef]

- Ahmad, W.A.; Kucharski, M.; Ergintav, A.; Abouzaid, S.; Wessel, J.; Ng, H.J.; Kissinger, D. Multimode W-band and D-band MIMO scalable radar platform. IEEE Trans. Microw. Theory Tech. 2021, 69, 1036–1047. [Google Scholar] [CrossRef]

- Ma, T.; Deng, W.; Chen, Z.; Wu, J.; Zheng, W.; Wang, S.; Qi, N.; Liu, Y.; Chi, B. A CMOS 76-81-GHz 2-TX 3-RX FMCW radar transceiver based on mixed-mode PLL chirp generator. IEEE J. Solid-State Circuits 2020, 55, 233–248. [Google Scholar] [CrossRef]

- Kissinger, D.; Kahmen, G.; Weigel, R. Millimeter-wave and terahertz transceivers in SiGe BiCMOS technologies. IEEE Trans. Microw. Theory Tech. 2021, 69, 4541–4560. [Google Scholar] [CrossRef]

- Arbabian, A.; Callender, S.; Kang, S.; Rangwala, M.; Niknejad, A.M. A 94 GHz mm-Wave-to-Baseband pulsed-radar transceiver with applications in imaging and gesture recognition. IEEE J. Solid-State Circuits 2013, 48, 1055–1071. [Google Scholar] [CrossRef]

- Moon, T.; Park, J.; Kim, S. Blue FMCW: Random Frequency Hopping Radar for Mitigation of Interference and Spoofing. EURASIP J. Adv. Signal Process 2022, 1–17. [Google Scholar] [CrossRef]

- Lazaro, A.; Porcel, A.; Lazaro, M.; Villarino, R.; Girbau, D. Spoofing Attacks on FMCW Radars with Low-Cost Backscatter Tags. Sensors 2022, 22, 2145. [Google Scholar] [CrossRef]

- Lee, J.; Liu, M.; Wang, H. A 75-GHz Phase-Locked Loop in 90-Nm CMOS Technology. IEEE J. Solid-State Circuits 2008, 43, 1414–1426. [Google Scholar] [CrossRef]

- Tsai, K.-H.; Liu, S.-I. A 43.7 mW 96GHz PLL in 65 nm CMOS. digest of technical papers. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 8–12 February 2009; pp. 276–277. [Google Scholar]

- Xu, Z.; Gu, Q.J.; Wu, Y.-C.; Jian, H.-Y.; Wang, F.; Chang, M.F. An Integrated Frequency Synthesizer for 81-86GHz Satellite Communications in 65nm CMOS. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA, 23–25 May 2010; pp. 57–60. [Google Scholar]

- Chao, Y.; Luong, H.C.; Hong, Z. A 0.6/1.2-V 14.1-mW 96.8GHz-to-108.5GHz Transformer-Based PLL with Embedded Phase Shifter in 65-Nm CMOS. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Tampa, FL, USA, 1–3 June 2014; pp. 93–96. [Google Scholar]

- Tsai, K.; Liu, S. A 104-GHz phase-locked loop using a VCO at second pole frequency. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2012, 20, 80–88. [Google Scholar] [CrossRef]

- Tan, K.-W.; Chu, T.-S.; Hsu, S.S.H. A 76.2-89.1 GHz phase-locked loop with 15.6% tuning range in 90 Nm CMOS for W-Band applications. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 538–540. [Google Scholar] [CrossRef]

- Shahramian, S.; Hart, A.; Tomkins, A.; Carusone, A.C.; Garcia, P.; Chevalier, P.; Voinigescu, S.P. Design of a Dual W- and D-Band PLL. IEEE J. Solid-State Circuits 2011, 46, 1011–1022. [Google Scholar] [CrossRef]

- Wang, C.-C.; Chen, Z.; Heydari, P. W-Band Silicon-Based frequency synthesizers using injection-locked and harmonic triplers. IEEE Trans. Microw. Theory Tech. 2012, 60, 1307–1320. [Google Scholar] [CrossRef]

- Kang, S.; Chien, J.-C.; Niknejad, A.M. A W-Band Low-Noise PLL with a Fundamental VCO in SiGe for Millimeter-Wave Applications. IEEE Trans. Microw. Theory Tech. 2014, 62, 2390–2404. [Google Scholar] [CrossRef]

- Yi, X.; Liang, Z.; Feng, G.; Meng, F.; Wang, C.; Li, C.; Yang, K.; Liu, B.; Boon, C.C. A 93.4-104.8-GHz 57-mW Fractional- Cascaded PLL with True in-Phase Injection-Coupled QVCO in 65-Nm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2019, 67, 2370–2381. [Google Scholar] [CrossRef]

- Huang, Z.; Luong, H.C. An 82–107.6-GHz Integer-N ADPLL Employing a DCO with Split Transformer and Dual-Path Switched-Capacitor Ladder and a Clock-Skew-Sampling Delt-Sigma TDC. IEEE J. Solid-State Circuits 2019, 54, 358–367. [Google Scholar] [CrossRef]

- Ku, B.; Chung, H.; Rebeiz, G.M. A Milliwatt-Level 70-110 GHz Frequency Quadrupler with >30 dBc Harmonic Rejection. IEEE Trans. Microw. Theory Tech. 2020, 68, 1697–1705. [Google Scholar] [CrossRef]

- Vehring, S.; Ding, Y.; Scholz, P.; Gerfers, F. A 3.1-dBm E-Band Truly Balanced Frequency Quadrupler in 22-Nm FDSOI CMOS. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 1165–1168. [Google Scholar] [CrossRef]

- Chou, M.; Chiu, H.; Kao, H.; Huang, F. A 60-GHz CMOS Frequency Tripler with Broadband Performance. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 281–283. [Google Scholar] [CrossRef]

- Ali, A.; Yun, J.; Kucharski, M.; Ng, H.J.; Kissinger, D.; Colantonio, P. 220-360-GHz Broadband Frequency Multiplier Chains (X8) in 130-nm BiCMOS Technology. IEEE Trans. Microw. Theory Tech. 2020, 68, 2701–2715. [Google Scholar] [CrossRef]

- Thyagarajan, S.V.; Kang, S.; Niknejad, A.M. A 240 GHz Fully Integrated Wideband QPSK Receiver in 65 Nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2268–2280. [Google Scholar] [CrossRef]

- Nam, H.; Park, J. A W-Band Divide-by-Three Injection-Locked Frequency Divider with Injection Current Boosting Utilizing Inductive Feedback in 65-Nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 516–519. [Google Scholar] [CrossRef]

- Chen, J.; Jonsson, F.; Carlsson, M.; Hedenäs, C.; Zheng, L.-R. A low power, startup ensured and constant amplitude class-c VCO in 0.18 μm CMOS. IEEE Microw. Wirel. Compon. Lett. 2011, 21, 427–429. [Google Scholar] [CrossRef]

- Trinh, V.-S.; Park, J.-D. A 25.1 dBm 25.9-dB Gain 25.4% PAE X-band power amplifier utilizing voltage combining transformer in 65-nm CMOS. IEEE Access 2021, 9, 6513–6521. [Google Scholar] [CrossRef]

- Trinh, V.; Park, J. A 16.3 dBm 14.1% PAE 28-dB gain W-Band power amplifier with inductive feedback in 65-nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 193–196. [Google Scholar] [CrossRef]

- Razavi, B. A 300-GHz fundamental oscillator in 65-nm CMOS technology. IEEE J. Solid-State Circuits 2011, 46, 894–903. [Google Scholar] [CrossRef]

- Trinh, V.; Park, J. Theory and design of impedance matching network utilizing a lossy on-chip transformer. IEEE Access 2019, 7, 140980–140989. [Google Scholar] [CrossRef]

- Razavi, B. A study of injection locking and pulling in oscillators. IEEE J. Solid-State Circuits 2004, 39, 1415–1424. [Google Scholar] [CrossRef]

- Ng, A.W.L.; Leung, G.C.T.; Kwok, K.; Leung, L.L.K.; Luong, H.C. A 1-V 24-GHz 17.5-mW phase-locked loop in a 0.18-/spl mu/m CMOS process. IEEE J. Solid-State Circuits 2006, 41, 1236–1244. [Google Scholar] [CrossRef]

- Lee, J. High-speed circuit designs for transmitters in broadband data links. IEEE J. Solid-State Circuits 2006, 41, 1004–1015. [Google Scholar] [CrossRef]

- Socher, E.; Jameson, S. Wide tuning range W-band Colpitts VCO in 90 nm CMOS. Electron. Lett. 2011, 47, 1227–1229. [Google Scholar] [CrossRef]

- Adnan, M.; Afshari, E. A 105-GHz VCO with 9.5% tuning range and 2.8-mW peak output power in a 65-nm Bulk CMOS process. IEEE Trans. Microw. Theory Tech. 2014, 62, 753–762. [Google Scholar] [CrossRef]

- Momeni, O.; Afshari, E. High power terahertz and millimeter-wave oscillator design: A systematic approach. IEEE J. Solid-State Circuits 2011, 46, 583–597. [Google Scholar] [CrossRef] [Green Version]

- Koo, H.; Kim, C.; Hong, S. A G-Band standing-wave push-push VCO using a transmission-line resonator. IEEE Trans. Microw. Theory Tech. 2015, 63, 1036–1045. [Google Scholar] [CrossRef]

- Trivedi, V.P.; To, K.-H.; Huang, W.M. A 77GHz CMOS VCO with 11.3 GHz Tuning Range, 6dBm Output Power, and Competitive Phase Noise in 65nm Bulk CMOS. In Proceedings of the 2011 IEEE Radio Frequency Integrated Circuits Symposium, Baltimore, MD, USA, 5–7 June 2011; pp. 1–4. [Google Scholar]

- Tarkeshdouz, A.; Mostajeran, A.; Mirabbasi, S.; Afshari, E. A 91-GHz Fundamental VCO with 6.1% DC-to-RF Efficiency and 4.5 dBm Output Power in 0.13-μm CMOS. IEEE Solid-State Circuits Lett. 2018, 1, 102–105. [Google Scholar] [CrossRef]

- Jameson, S.; Socher, E. A 93.9–102.5 GHz Colpitts VCO utilizing magnetic coupling band switching in 65nm CMOS. In Proceedings of the 2015 IEEE International Conference on Microwaves, Communications, Antennas and Electronic Systems (COMCAS), Tel Aviv, Israel, 2–4 November 2015; pp. 1–5. [Google Scholar]

- Sapone, G.; Ragonese, E.; Italia, A.; Palmisano, G. A 0.13-nm SiGe BiCMOS Colpitts-Based VCO for -Band Radar Transmitters. IEEE Trans. Microw. Theory Tech. 2013, 61, 185–194. [Google Scholar] [CrossRef]

- Aghasi, H.; Afshari, E. An 88-GHz compact fundamental oscillator with 19.4% DC-to-RF efficiency and 7.5-dBm output power in 130-nm SiGe BiCMOS. IEEE Solid-State Circuits Lett. 2018, 1, 106–109. [Google Scholar] [CrossRef]

- Wu, K.; Hella, M. A 103-GHz voltage controlled oscillator with 28% tuning range and 4.2 dBm Peak output power using SiGe BiCMOS technology. In Proceedings of the IEEE/MTT-S International Microwave Symposium, Philadelphia, PA, USA, 10–15 June 2018; pp. 606–609. [Google Scholar]

- Su, Y.; Cheng, Z.; He, Z.; Deng, M. Communication-awareness adaptive resource scheduling strategy for multiple target tracking in a multiple radar system. IET Signal Process 2022, 1–12. [Google Scholar] [CrossRef]

- Hu, W.; Zhang, M.; Li, Z.; Popov, S.; Leeson, M.; Xu, T. High-Dimensional Feature Based Non-Coherent Detection for Multi-Intensity Modulated Ultraviolet Communications. J. Lightwave Technol. 2022, 40, 1879–1887. [Google Scholar] [CrossRef]

| Device | Size (in PLL) | Size (SA VCO) |

|---|---|---|

| M1 | W = 32 μm; L = 65 nm | W = 32 μm; L = 65 nm |

| Cv (MOS CAP) | W = 7.2 μm; L = 0.5 μm | W = 5.4 μm; L = 0.5 μm |

| TF1 | Din = 18 um | Din = 20 um |

| M2 | W = 40 μm; L = 65 nm | W = 46μm; L = 65 nm |

| TF2 | Din = 26 μm | Din = 22 μm with an additional inductor at the secondary side |

| M3 | W = 80 μm; L = 65 nm | W = 140 μm; L = 65 nm |

| Cc (MOM CAP) | 16 fF | 34 fF |

| TF3 | Din = 24 μm | Din = 22 μm |

| Co (MOM CAP) | 26 fF | 28 fF |

| Ref. | Structure | Process | VDD/ VCC | Freq. (GHz) | Tuning Range | Pout (dBm) | PDC (mW) | Phase Noise (dBc/Hz) | DC-RF Eff. (%) | Area (mm2) | FOM |

|---|---|---|---|---|---|---|---|---|---|---|---|

| This | Cross-coupled | 65-nm CMOS | 1.2 V | 83.5 | 3.5 | 13.5 | 167–235 | −92.6@1 MHz −106.1@ 10 MHz | 9.6 | 0.065 | −205.4 |

| [36] | Diff. Colpitts | 90-nm CMOS | 1.8 V | 97.7 | 7.2 | 4.7 | 6–63 | −80@ 1 MHz | 5.5 | 0.063 | −189.0 |

| [37] | Coupled Oscillator | 65-nm CMOS | 1.2 V | 105 | 9.5 | 4.5 | 54 (1) | −92.8@ 1 MHz | 5.2 | 0.228 (2) | −204.4 |

| [38] | Ring Oscillator | 130-nm CMOS | 1.5 V | 104 | NA | −2.7 | 28 | −93.3@ 1 MHz | 1.9 | 0.16 (2) | NA |

| [39] | Push-Push | 65-nm CMOS | 1 V | 81.5 | 14 | −0.5 | 33 | 97.3 (5)@ 1 MHz | 2.7 | 0.046 | 202.3 (5) |

| [40] | Pseudo-diff. (4) | 65-nm CMOS | 1 V | 77 | 14.5 | 6.2 | 190 | −88@ 1 MHz | 2.2 | NA | −198.6 |

| [41] | Cross-coupled | 130-nm CMOS | 1.8 V | 91 | 0.5 | 4.5 | 46 | −87@ 1 MHz | 6.1 | 0.51 (2) | −172.5 |

| [42] | Diff. Colpitts | 65-nm CMOS | 1.8 V | 98 | 8.7 | −1 | 4–21.6 | −90@ 1 MHz | 3.7 | 0.18 (2) | −193.3 |

| [43] | Colpitts-based | 130-nm SiGe | 2.5 V | 74 | 4.86 | 2 (3) | 65 | −99.3@ 1 MHz | 2.4 | 0.017 (6) | −196.2 |

| [44] | Self-feeding | 130-nm SiGe | 0.82–0.96 V | 88 | 1 (7) | 7.5 (7) | - | −106.9 (7)@ 1 MHz | 19.4 (7) | 0.028 (2) | −186.2 |

| [45] | Colpitts-based | 130-nm SiGe | 1.2–1.65 V | 103.5 | 28 | 4.2 | 50 | −108.7@ 1 MHz | 5.3 | 0.16 | −229.4 |

| Ref. | Tech. | Frequency (GHz) | TR (%) | PN @1 MHz (dBc/Hz) | Reference Frequency | Reference Spur (dBc) | Pout (dBm) | Pdiss (mW) | Division Ratio | Area (mm2) |

|---|---|---|---|---|---|---|---|---|---|---|

| This | 65-nm CMOS | 78.84~84 | 6.4 | −85.2 | 1.64–1.75 GHz | 12.4 | 5.8 | 326.4 | 48 | 4.12 |

| [11] | 90-nm CMOS | 73.4~73.72 | 0.43 | −92 | 2.34 GHz | 2.5 | −18.5 | 88 | 32 | 0.8 |

| [12] | 65-nm CMOS | 95.1~96.5 | 1.5 | −75.9 | 373 MHz | 2 | −26.7 | 43.7 | 256 | 0.7 |

| [13] | 65-nm CMOS | 70~78 | 10.8 | −83 | 70 MHz | 0.3 | −18.9 | 76 | 1024~1984 | 0.31 |

| [14] | 65-nm CMOS | 96.8~108.5 | 11.5 | −88 | 195 MHz | 1 | NA | 14.1 | 512 | 0.39 |

| [15] | 65-nm CMOS | 103~104.5 | 1.5 | −80.4 | 406 MHz | 2 | −23.1 | 63 | 256 | 0.84 |

| [16] | 90-nm CMOS | 76.2~89.1 | 15.6 | −87.9 | 50 MHz | 0.1 | −2.9 | 62.4 | 512 | 1.3 |

| [20] | 65-nm CMOS | 93.4~104.8 | 11.5 | −85.75 | 100 MHz | NA | NA | 57 | NA | 0.8755 |

| [21] | 65-nm CMOS | 82.0~107.6 | 27 | NA | 125 MHz | NA | NA | 35.5 | NA | 0.36 |

| [17] | 130-nm SiGe | 86~92 | 6.7 | −100 | 0.6~6 GHz | 1.7~8.5 | −3 | 1150 | 16 | 1.87 |

| [18] | 180-nm SiGe | 90.9~101.4 | 10.9 | −92 | 125 MHz | 1 | −11 | 140 | 256 | 1.9 |

| [19] | 130-nm SiGe | 92.7~100.2 | 7.8 | −102 | 3 GHz | 20 | 3 | 469.3 | 64 | 0.93 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Trinh, V.-S.; Nam, H.; Song, J.-M.; Park, J.-D. A 78.8–84 GHz Phase Locked Loop Synthesizer for a W-Band Frequency-Hopping FMCW Radar Transceiver in 65 nm CMOS. Sensors 2022, 22, 3626. https://doi.org/10.3390/s22103626

Trinh V-S, Nam H, Song J-M, Park J-D. A 78.8–84 GHz Phase Locked Loop Synthesizer for a W-Band Frequency-Hopping FMCW Radar Transceiver in 65 nm CMOS. Sensors. 2022; 22(10):3626. https://doi.org/10.3390/s22103626

Chicago/Turabian StyleTrinh, Van-Son, Hyohyun Nam, Jeong-Moon Song, and Jung-Dong Park. 2022. "A 78.8–84 GHz Phase Locked Loop Synthesizer for a W-Band Frequency-Hopping FMCW Radar Transceiver in 65 nm CMOS" Sensors 22, no. 10: 3626. https://doi.org/10.3390/s22103626

APA StyleTrinh, V.-S., Nam, H., Song, J.-M., & Park, J.-D. (2022). A 78.8–84 GHz Phase Locked Loop Synthesizer for a W-Band Frequency-Hopping FMCW Radar Transceiver in 65 nm CMOS. Sensors, 22(10), 3626. https://doi.org/10.3390/s22103626