A Terahertz CMOS V-Shaped Patch Antenna with Defected Ground Structure

Abstract

1. Introduction

2. CMOS On-Chip Patch Antenna Design

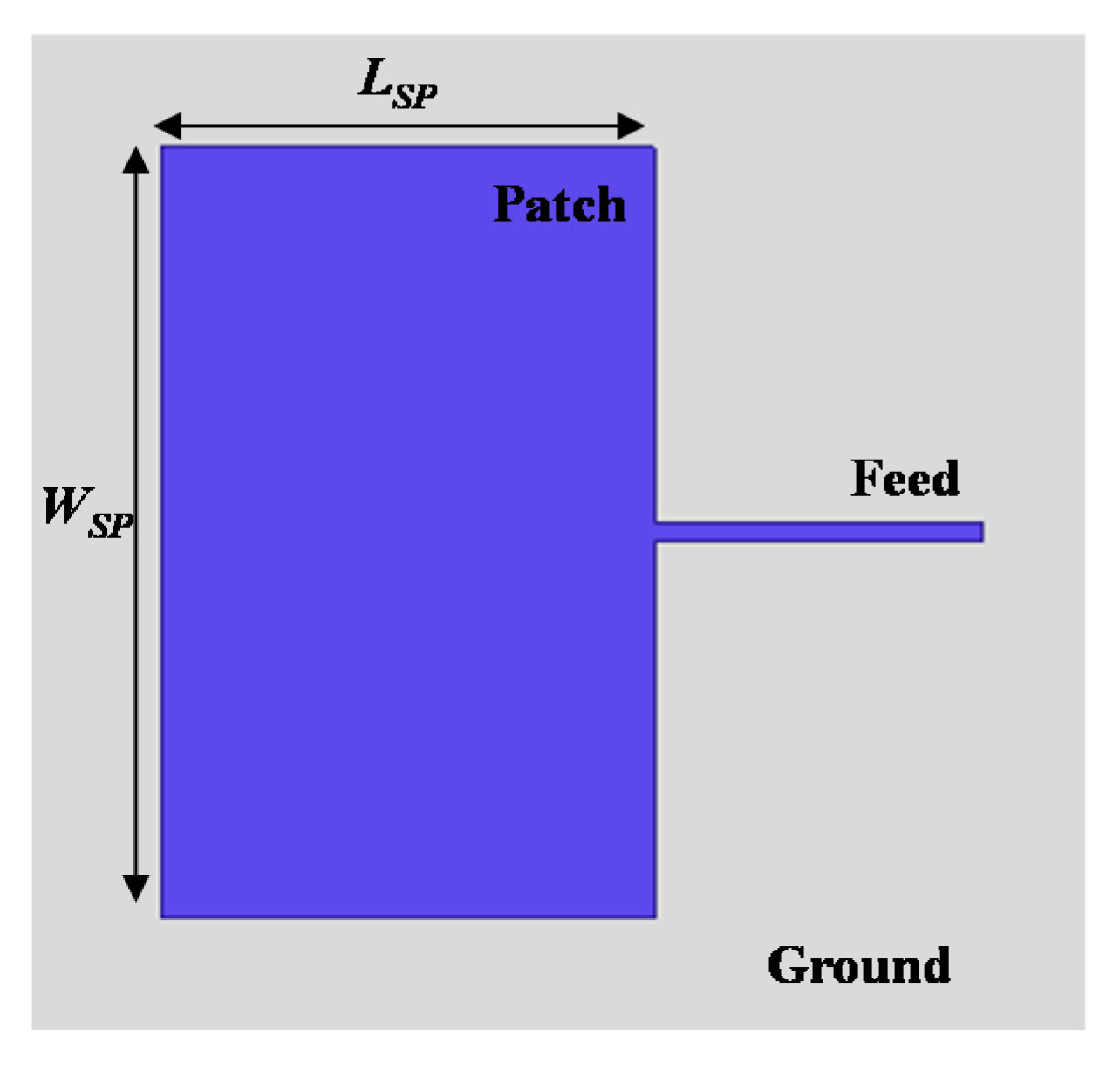

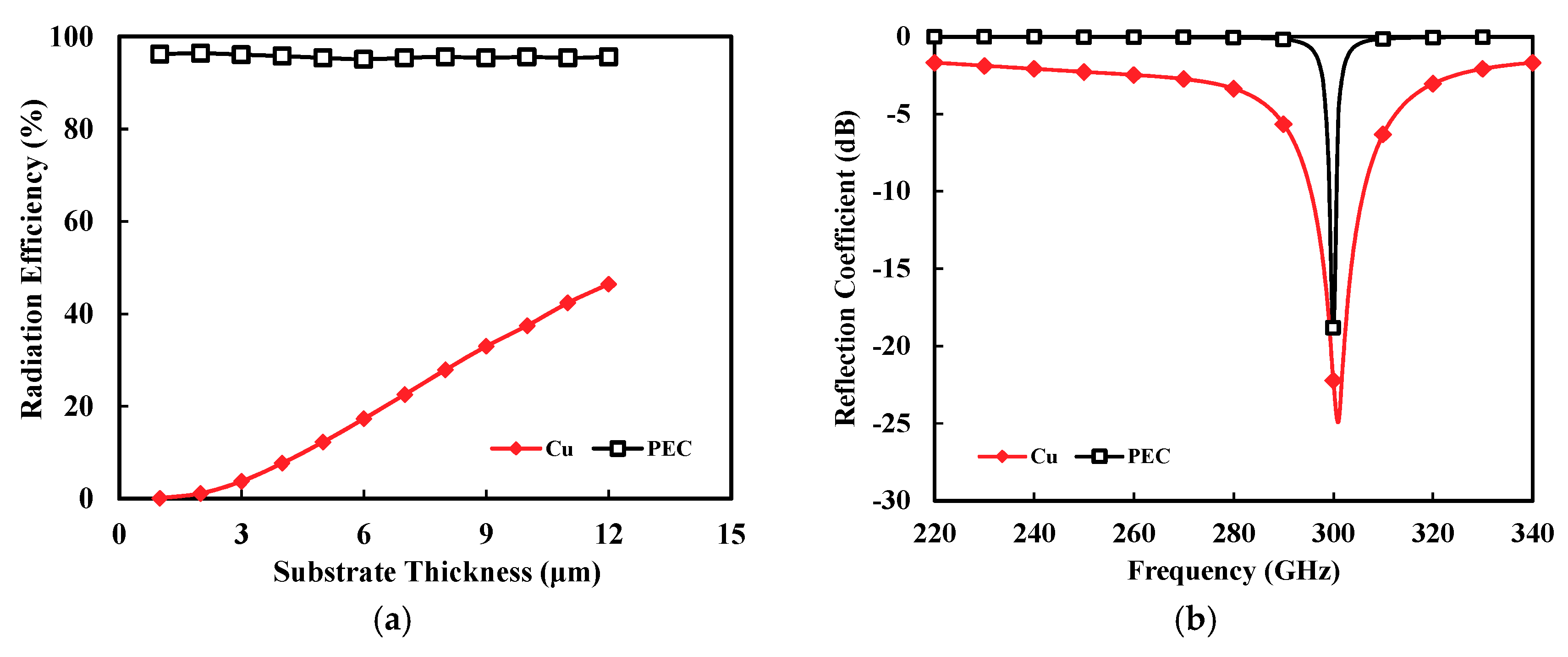

2.1. Standard CMOS On-Chip Patch Antenna

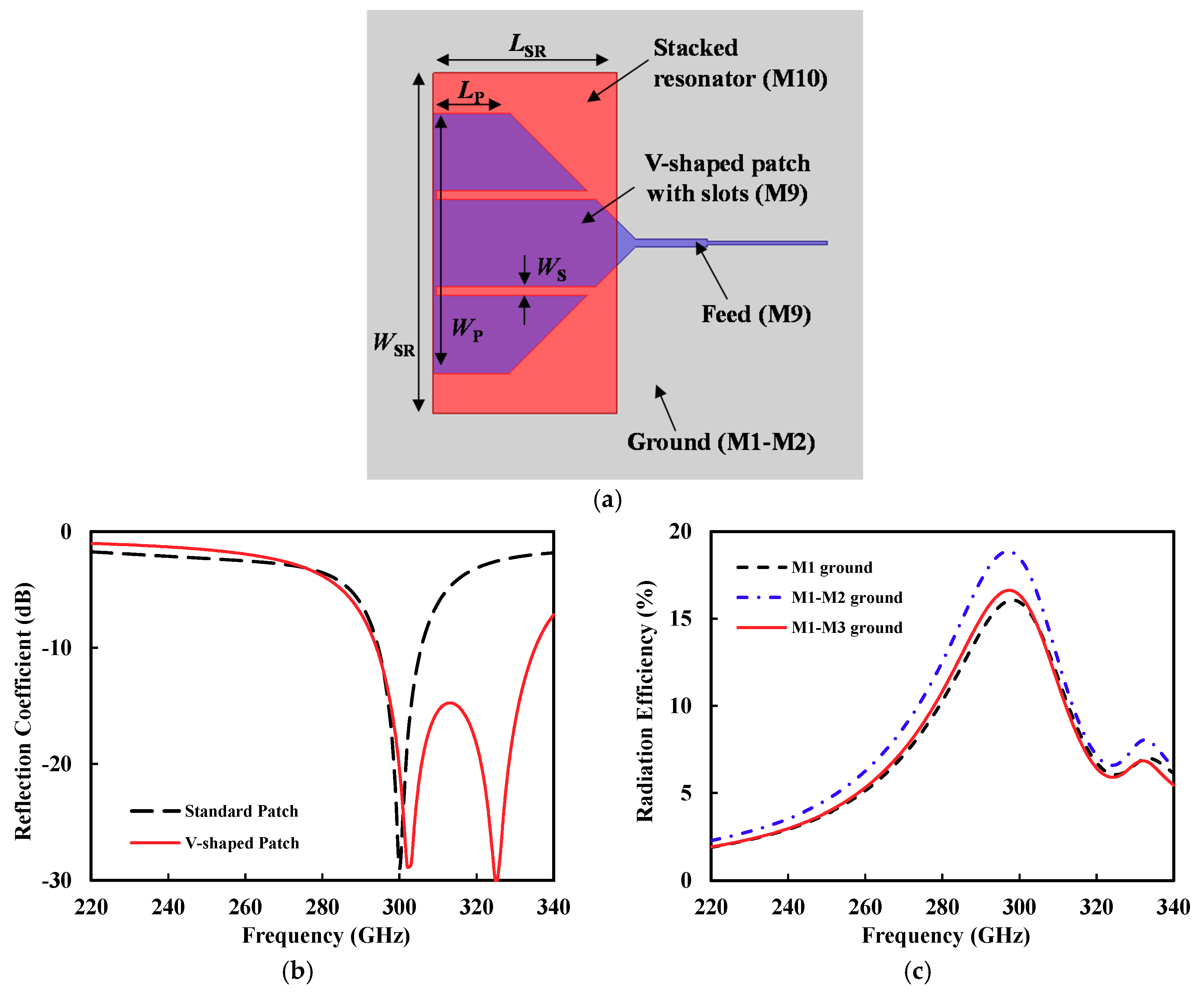

2.2. V-Shaped Patch Antenna

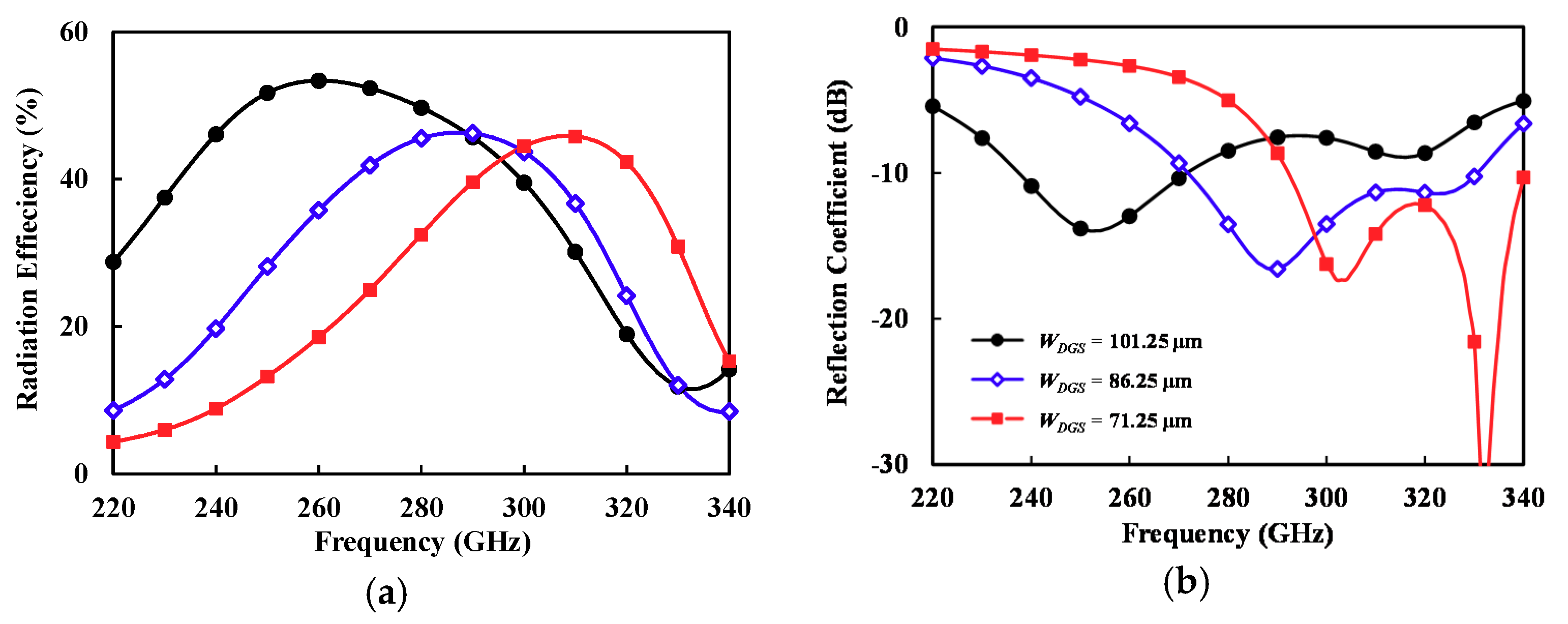

2.3. V-Shaped Patch Antenna with a Defected Ground Structure

2.4. Probe Effect on the Antenna Performance

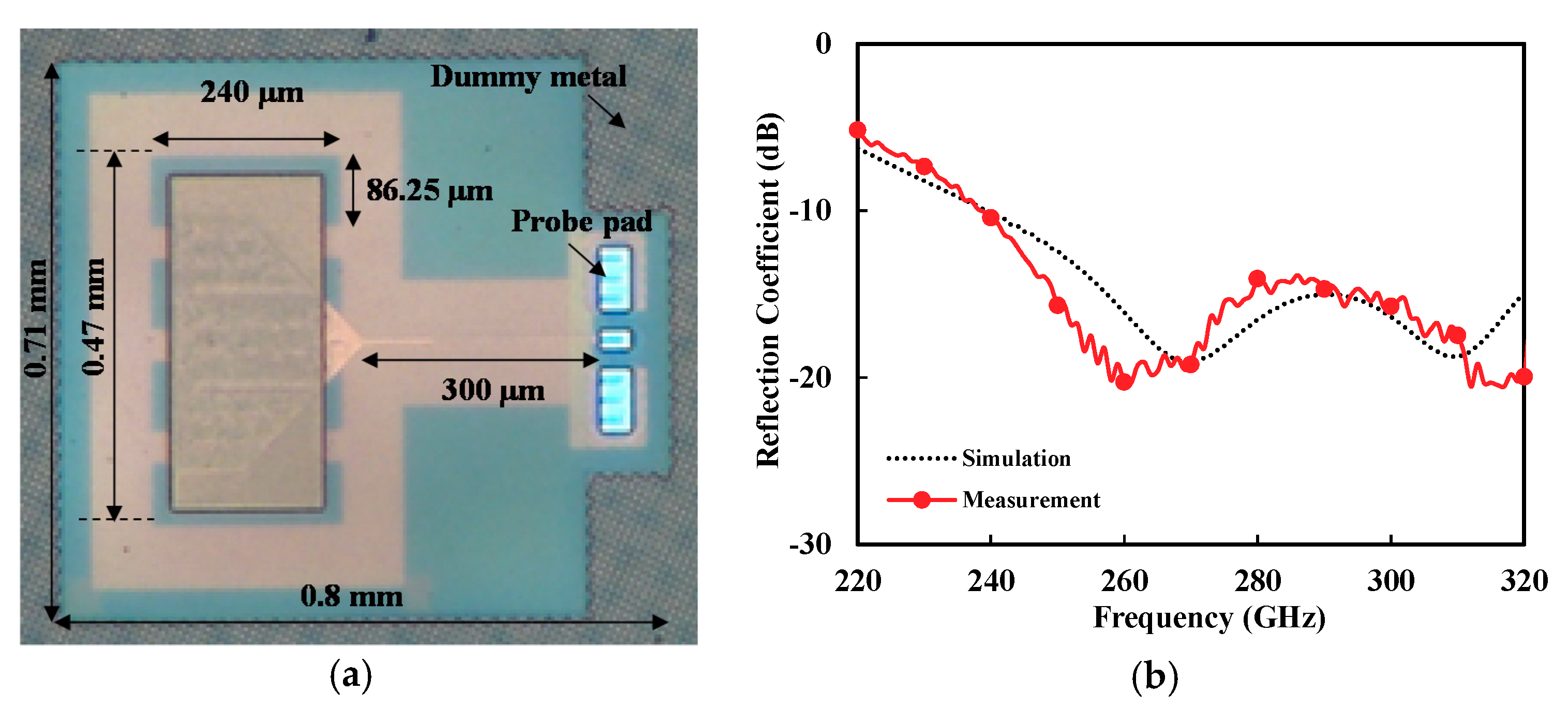

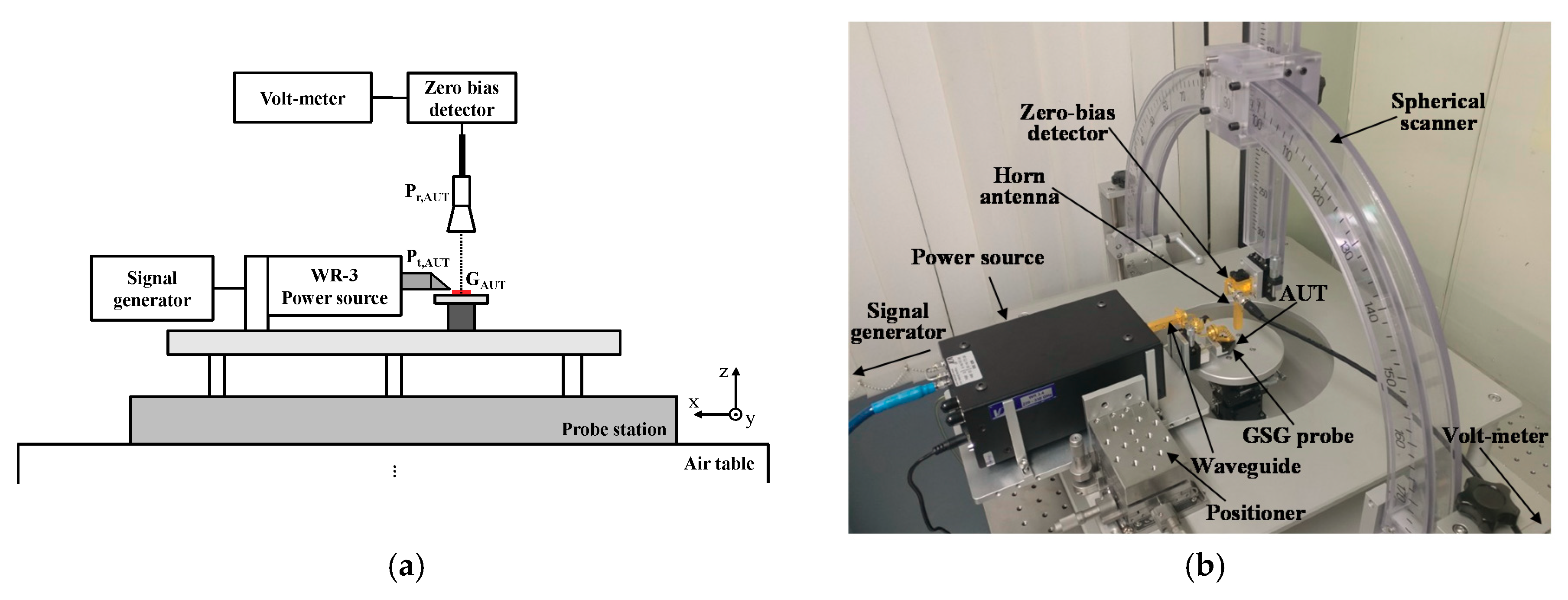

3. Measurement

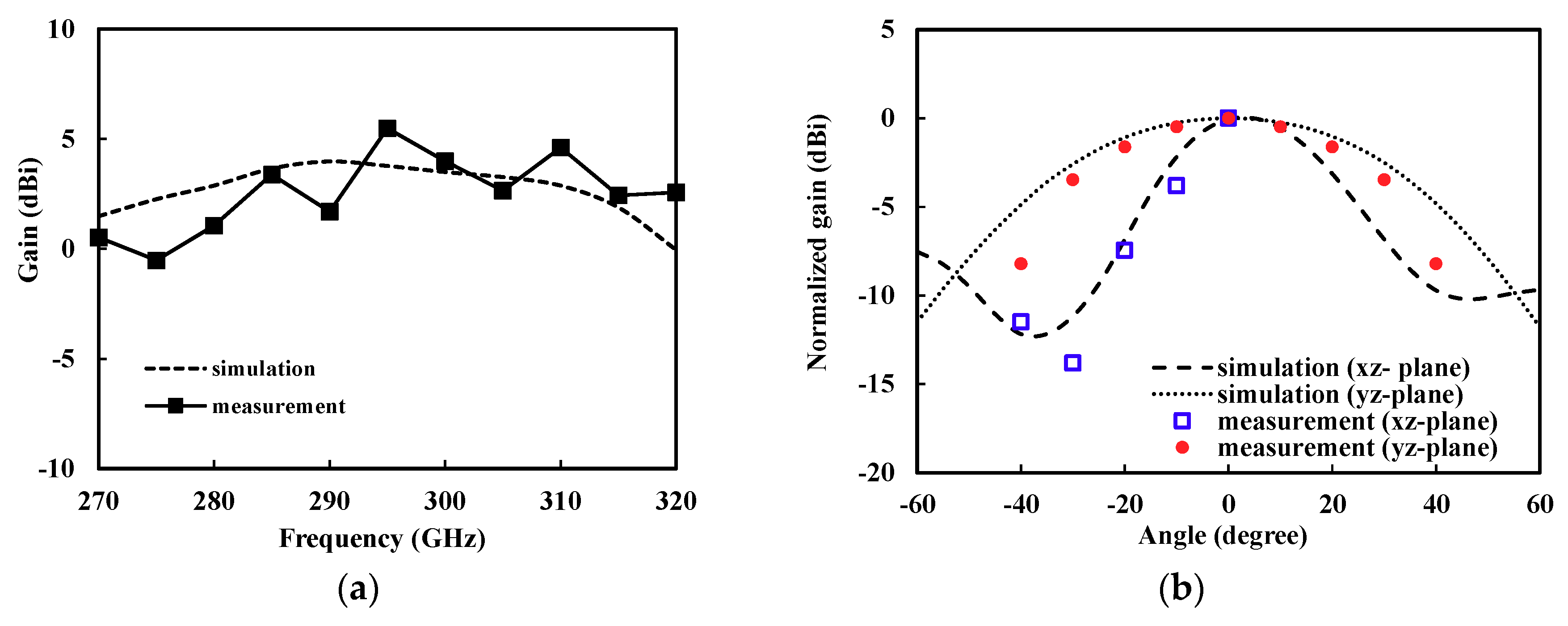

Measurement of the On-Chip Antenna

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kang, S.; Thyagarajan, S.V.; Niknejad, A.M. A 240 GHz fully integrated wideband QPSK transmitter in 65 nm CMOS. IEEE J. Solid-State Circuits 2015, 50, 2256–2267. [Google Scholar] [CrossRef]

- Kallfass, I.; Antes, J.; Schneider, T.; Kurz, F.; Lopez-Diaz, D.; Diebold, S.; Massler, H.; Leuther, A.; Tessmann, A. All active MMIC-based wireless communication at 220 GHz. IEEE Trans. Terahertz Sci. Technol. 2011, 1, 477–487. [Google Scholar] [CrossRef]

- Tesssmann, A.; Leuther, A.; Hurm, V.; Massler, H.; Wagner, S.; Kuri, M.; Zink, M.; Riessle, M.; Stulz, H.-P.; Schlechtweg, M.; et al. A broadband 220–320 GHz medium power amplifier module. In Proceedings of the IEEE Compound Semicond. Integrated Circuit Symposium, Monterey, CA, USA, 3–6 October 2010; pp. 1–4. [Google Scholar]

- Lee, I.; Kim, J.; Jeon, S. A G-Band Frequency Doubler Using a Commercial 150 nm GaAs pHEMT Technology. J. Electromagn. Eng. Sci. 2017, 17, 147–152. [Google Scholar] [CrossRef]

- Choe, W.; Kim, J.; Jeong, J. Full H-band waveguide-to-coupled microstrip transition using dipole antenna with directors. IEICE Electron. Express 2017, 14, 20170487. [Google Scholar] [CrossRef]

- Kim, J.; Choe, W.; Jeong, J. Submillimeter-wave waveguide-to-microstrip transitions for wide circuits/wafers. IEEE Trans. Terahertz Sci. Technol. 2017, 7, 440–445. [Google Scholar] [CrossRef]

- Sengupta, K.; Seo, D.; Yang, L.; Hajimiri, A. Silicon integrated 280 GHz imaging chipset with 4 × 4 SiGe receiver array and CMOS source. IEEE Trans. Terahertz Sci. Technol. 2015, 5, 427–437. [Google Scholar]

- Yan, Y.; Karandikar, Y.B.; Gunnarsson, S.E.; Urteaga, M.; Pierson, R.; Zirath, H. 340 GHz integrated receiver in 250 nm InP DHBT technology. IEEE Trans. Terahertz Sci. Technol. 2012, 2, 306–314. [Google Scholar] [CrossRef]

- Kim, J.; Jeon, S.; Kim, M.; Urteaga, M.; Jeong, J. H-band power amplifier integrated circuits using 250-nm InP HBT technology. IEEE Trans. Terahertz Sci. Technol. 2015, 5, 215–222. [Google Scholar] [CrossRef]

- Kim, J.; Seo, M.; Rieh, J. A CMOS 180-GHz Signal Source with an Integrated Frequency Doubler. J. Electromagn. Eng. Sci. 2016, 16, 229–231. [Google Scholar] [CrossRef]

- Bhutani, A.; Gulan, H.; Goettel, B.; Heine, C.; Thelemann, T.; Pauli, M.; Zwick, T. 122 GHz aperture-coupled stacked patch microstrip antenna in LTCC technology. In Proceedings of the 10th European Conference on Antennas and Propagation (EuCAP), Davos, Switzerland, 10–15 April 2016; pp. 1–5. [Google Scholar]

- Syed, W.H.; Florentino, G.; Cavallo, D.; Spirito, M.; Sarro, P.M.; Neto, A. Design, fabrication, and measurements of a 0.3 THz on-chip double slot antenna enhanced by artificial dielectrics. IEEE Trans. Terahertz Sci. Technol. 2015, 5, 288–298. [Google Scholar] [CrossRef]

- Hu, S.; Xiong, Y.-Z.; Zhang, B.; Wang, L.; Lim, T.-G.; Je, M.; Madihian, M. A SiGe BiCMOS transmitter/receiver chipset with on-chip SIW antenna for terahertz applications. IEEE J. Solid-State Circuits 2015, 50, 2256–2267. [Google Scholar] [CrossRef]

- Huang, K.K.; Wentzloff, D.D. 60 GHz on-chip patch antenna integration in a 0. In 13-μm CMOS technology. In Proceedings of the IEEE International Conference on Ultra-Wideband (ICUWB), Nanjing, China, 20–23 September 2010. [Google Scholar]

- Nafe, M.; Syed, A.; Shamim, A. Gain enhancement of low profile on-chip dipole antenna via artificial magnetic conductor at 94 GHz. In Proceedings of the 9th European Conference on Antennas and Propagation (EuCAP), Lisbon, Portugal, 13–17 April 2015; pp. 1–3. [Google Scholar]

- Mosallaei, H.; Sarabandi, K. Antenna Miniaturization and Bandwidth Enhancement using a Reactive Impedance Substrate. IEEE Trans. Antennas Propag. 2004, 52, 2403–2414. [Google Scholar] [CrossRef]

- Li, L.; Li, Y.; Yeo, T.; Mosig, J.; Martin, O. A Broadband and High-Gain Metamaterial Microstrip Antenna. Appl. Phys. Lett. 2010, 96, 164101. [Google Scholar] [CrossRef]

- Yao, J.; Tchafa, F.; Jain, A.; Tjuatja, S.; Huang, H. Far-Field Interrogation of Microstrip Patch Antenna for Temperature Sensing without Electronics. IEEE Sens. J. 2016, 16, 7053–7060. [Google Scholar] [CrossRef]

- Tajima, T.; Song, H.; Yaita, M. Compact THz LTCC receiver module for 300 GHz wireless communications. IEEE Microw. Compon. Lett. 2016, 26, 291–293. [Google Scholar] [CrossRef]

- Deng, X.; Li, Y.; Liu, C.; Wu, W.; Xiong, Y. 340 GHz on-chip 3-D antenna with 10 dBi gain and 80% radiation efficiency. IEEE Trans. Terahertz Sci. Technol. 2015, 5, 619–627. [Google Scholar] [CrossRef]

- Song, H.; Kim, J.; Ajito, K.; Yaita, M.; Kukutsu, N. Fully integrated ASK receiver MMIC for terahertz communications at 300 GHz. IEEE Trans. Terahertz Sci. Technol. 2013, 3, 445–452. [Google Scholar] [CrossRef]

- Babakhani, A.; Rutledge, D.B.; Hajimiri, A. Mm-wave phased arrays in silicon with integrated antennas. In Proceedings of the IEEE Antennas and Propagation Society International Symposium, Honolulu, HI, USA, 9–15 June 2007; pp. 4369–4372. [Google Scholar]

- Grzyb, J.; Zhao, Y.; Pfeiffer, U.R. A 288 GHz lens-integrated balanced triple-push source in a 65-nm CMOS technology. IEEE J. Solid-State Circuits 2013, 48, 1751–1761. [Google Scholar] [CrossRef]

- Schuster, F.; Videlier, H.; Dupret, A.; Coquillat, D.; Sakowicz, M.; Rostaing, J.P.; Tchagaspanian, M.; Giffard, B.; Knap, W. A Broadband THz Imager in a Low-Cost CMOS Technology. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 42–43. [Google Scholar]

- Schuster, F.; Coquillat, D.; Videlier, H.; Sakowicz, M.; Teppe, F.; Dussopt, L.; Giffard, B.; Skotnicki, T.; Knap, W. Broadband Terahertz imaging with highly sensitive silicon CMOS detectors. Opt. Express 2011, 19, 7827–7832. [Google Scholar] [CrossRef] [PubMed]

- Khan, M.S.; Tahir, F.A.; Cheema, H.M. Design of Bowtie-Slot On-chip Antenna Backed with E-Shaped FSS at 94 GHz. In Proceedings of the 10th European Conference on Antenna and Propagation, Davos, Switzerland, 10–15 April 2016; pp. 1–3. [Google Scholar]

- Arz, U. Microwave Substrate Loss Tangent Extraction from Coplanar Waveguide Measurements up to 125 GHz. In Proceedings of the 83rd ARFTG Microwave Measurement Conference, Tampa, FL, USA, 6 June 2014; pp. 1–3. [Google Scholar]

- Majid, H.A.; Rahim, M.K.A.; Hamid, M.R.; Murad, N.A.; Ismail, M.F. Frequency-reconfigurable microstrip patch-slot antenna. IEEE Antenna Wirel. Propag. Lett. 2013, 12, 218–220. [Google Scholar] [CrossRef]

- Misra, I.S.; Murmu, S.K. Design of V-shaped microstrip patch antenna at 2.4 GHz. Microw. Opt. Technol. Lett. 2011, 53, 806–811. [Google Scholar]

- Johannsen, U.; Smolders, A.B.; Mahmoudi, R. Substrate loss reduction in antenna-on-chip design. In Proceedings of the IEEE Antennas and Propagation Society International Symposium, Charleston, SC, USA, 1–5 June 2009; pp. 1–4. [Google Scholar]

- Simons, R.N. Novel On-Wafer Radiation Pattern Measurement Technique for MEMS Actuator Based Reconfigurable Patch Antennas; NASA STI/Recon Technical Report N; NASA Glenn Research Center: Cleveland, OH, USA, 2002.

- Pan, S.; Gilreath, L.; Heydari, P.; Capolino, F. Investigation of a Wideband BiCMOS Fully On-Chip W-band Bowtie Slot Antenna. IEEE Antennas Wirel. Propag. Lett. 2013, 12, 706–709. [Google Scholar] [CrossRef]

- Balanis, C.A. Antenna Theory: Analysis and Design, 4th ed.; Wiley: New York, NY, USA, 2016; pp. 49–51. [Google Scholar]

- Stutzman, W.L. Antenna Theory and Design, 3rd ed.; Wiley: New York, NY, USA, 2012; pp. 571–575. [Google Scholar]

- Kang, J.; Kim, J.; Park, J. Comparison of antenna parameters of R-/S- band standard gain horn antennas. J. Electromagn. Eng. Sci. 2015, 15, 224–231. [Google Scholar] [CrossRef]

- Han, R.; Zhang, Y.; Coquillat, D.; Videlier, H.; Knap, W.; Brown, E.; Kenneth, K.O. A 280-GHz schottky diode detector in 130-nm digital CMOS. IEEE J. Solid-State Circuits 2011, 46, 2602–2612. [Google Scholar] [CrossRef]

- Li, C.H.; Ko, C.L.; Kuo, M.C.; Chang, D.C. A 340-GHz heterodyne receiver front end in 40-nm CMOS for THz biomedical imaging applications. IEEE Trans. Terahertz Sci. Technol. 2016, 6, 625–636. [Google Scholar] [CrossRef]

- Shang, Y.; Yu, H.; Fu, H.; Lim, W.M. A 239–281 GHz CMOS receiver with on-chip circular-polarized substrate integrated waveguide antenna for sub-terahertz imaging. IEEE Trans. Terahertz Sci. Technol. 2014, 4, 686–695. [Google Scholar] [CrossRef]

- Wang, Z.; Chiang, P.-Y.; Nazari, P.; Wang, C.-C.; Chen, Z.; Heydari, P. A CMOS 210-GHz fundamental transceiver with OOK modulation. IEEE J. Solid-State Circuits 2014, 49, 564–580. [Google Scholar] [CrossRef]

| Parameter | LSR | LP | WSR | WP | WS | LDGS | WDGS | SDGS |

|---|---|---|---|---|---|---|---|---|

| Value (μm) | 200 | 95 | 425 | 300 | 5 | 240 | 86 | 40 |

| This Work | [1] | [36] | [37] | [38] | [39] | [20] | [23] | |

|---|---|---|---|---|---|---|---|---|

| Technology | 65 nm | 65 nm | 130 nm | 40 nm | 65 nm | 32 nm | 130 nm | 65 nm |

| Center frequency (GHz) | 290 | 240 | 280 | 340 | 270 | 210 | 340 | 288 |

| Bandwidth (%) 1 | >28 | 8.3 * | 2.1 * | 4.1 * | 12 * | 20 * | 11 | n.a. |

| Peak efficiency (%) | 26.3 * | 11.4 * | 21 * | 6.5 * | 21.4 * | 24 * | 80 | 65 |

| Peak gain (dBi) | 5.48 | 1.55 * | −1.6 * | −5.5 * | −0.5 * | −2.5 * | 10 | n.a. |

| Type | Patch | Slotted loop | Patch | Patch | SIW 2 | Dipole | DRA 3 | HHLA 4 |

| Planar | Yes | Yes | Yes | Yes | Yes | Yes | No | No |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, H.; Choe, W.; Jeong, J. A Terahertz CMOS V-Shaped Patch Antenna with Defected Ground Structure. Sensors 2018, 18, 2432. https://doi.org/10.3390/s18082432

Kim H, Choe W, Jeong J. A Terahertz CMOS V-Shaped Patch Antenna with Defected Ground Structure. Sensors. 2018; 18(8):2432. https://doi.org/10.3390/s18082432

Chicago/Turabian StyleKim, Hyeongjin, Wonseok Choe, and Jinho Jeong. 2018. "A Terahertz CMOS V-Shaped Patch Antenna with Defected Ground Structure" Sensors 18, no. 8: 2432. https://doi.org/10.3390/s18082432

APA StyleKim, H., Choe, W., & Jeong, J. (2018). A Terahertz CMOS V-Shaped Patch Antenna with Defected Ground Structure. Sensors, 18(8), 2432. https://doi.org/10.3390/s18082432