Sensing and Reliability Improvement of Electrostatic-Discharge Transient by Discrete Engineering for High-Voltage 60-V n-Channel Lateral-Diffused MOSFETs with Embedded Silicon-Controlled Rectifiers

Abstract

:1. Introduction

2. Testing Devices Layout

2.1. 60-V High-Voltage n-Channel Lateral-Diffused MOSFET Reference Device

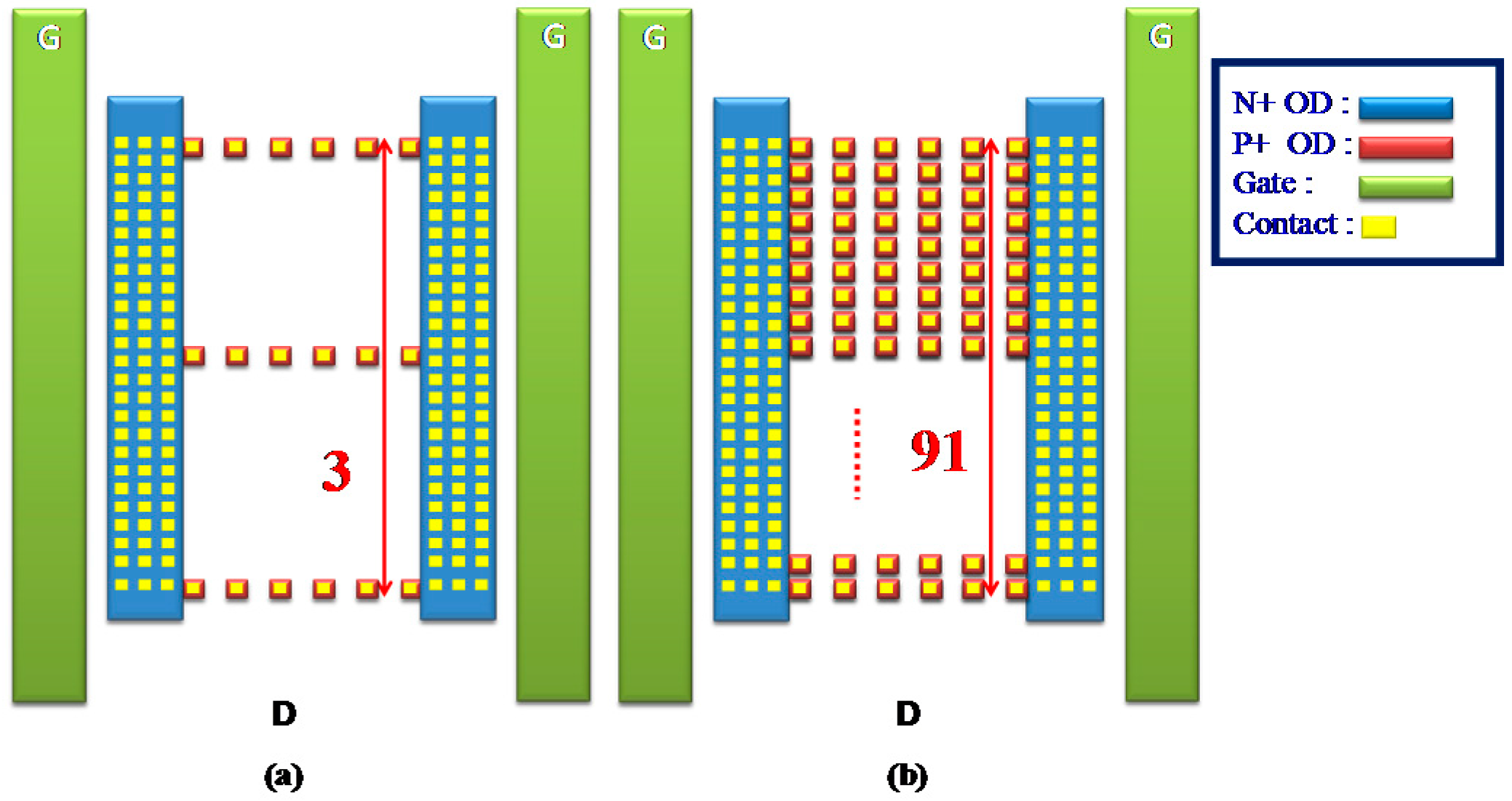

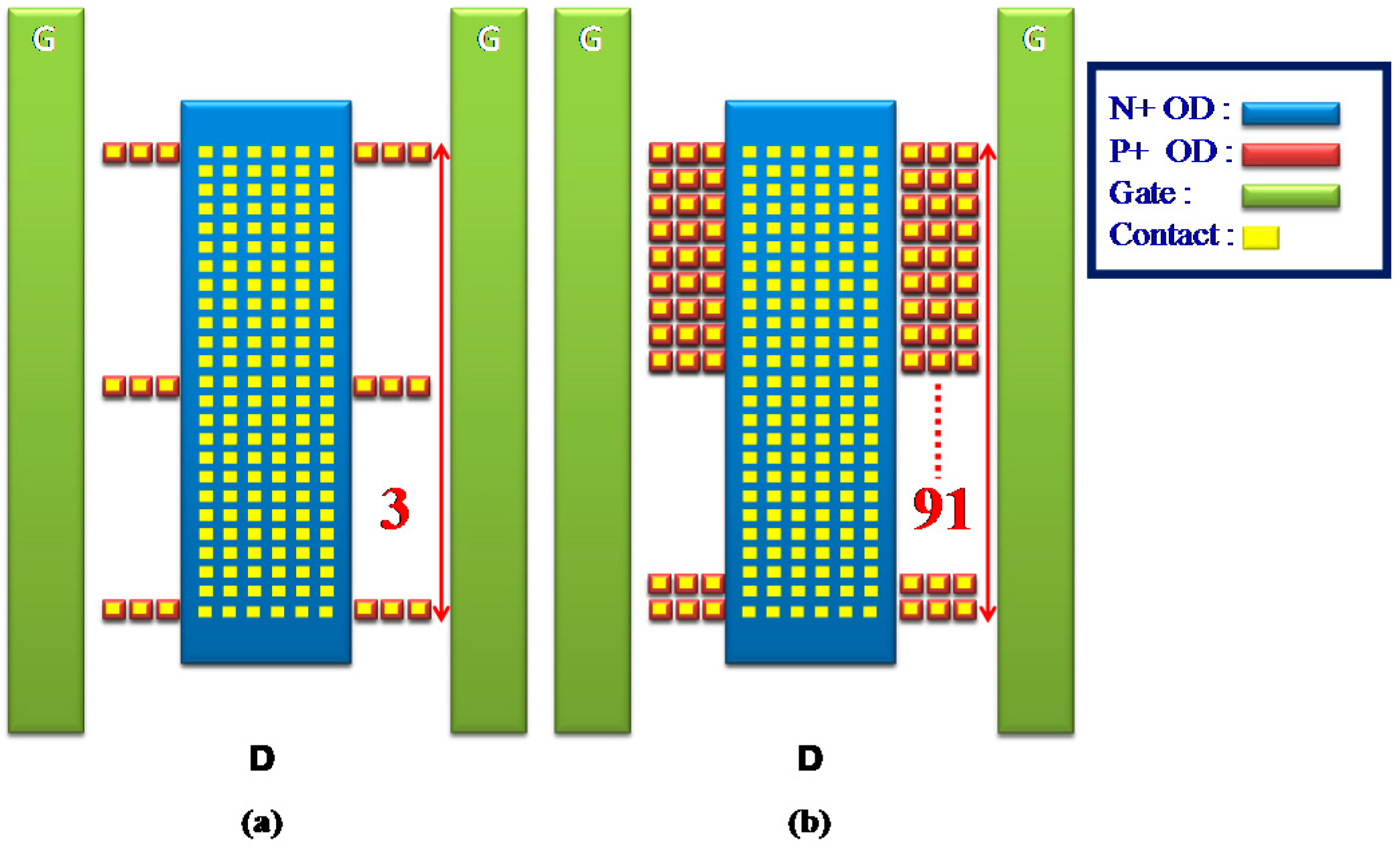

2.2. 60-V High-Voltage n-Channel Lateral-Diffused MOSFET-Silicon-Controlled Rectifier: Anode-Discrete Modulations

3. Transmission–Line–Pulse Testing Equipment

4. Measurement Results and Discussion

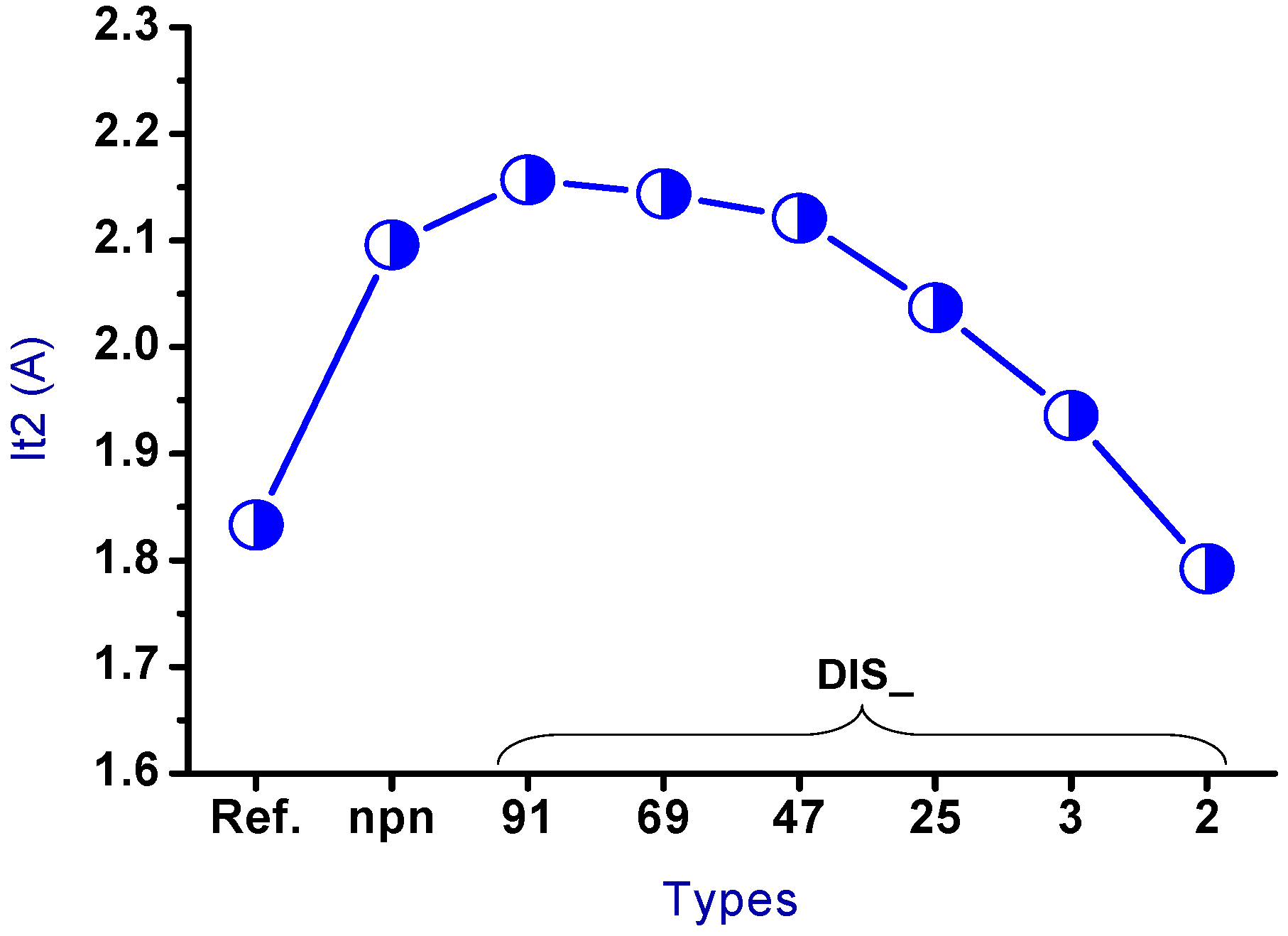

4.1. 60-V High-Voltage nLDMOS-Silicon-Controlled Rectifier: The Discrete n-p-n-Arranged Type

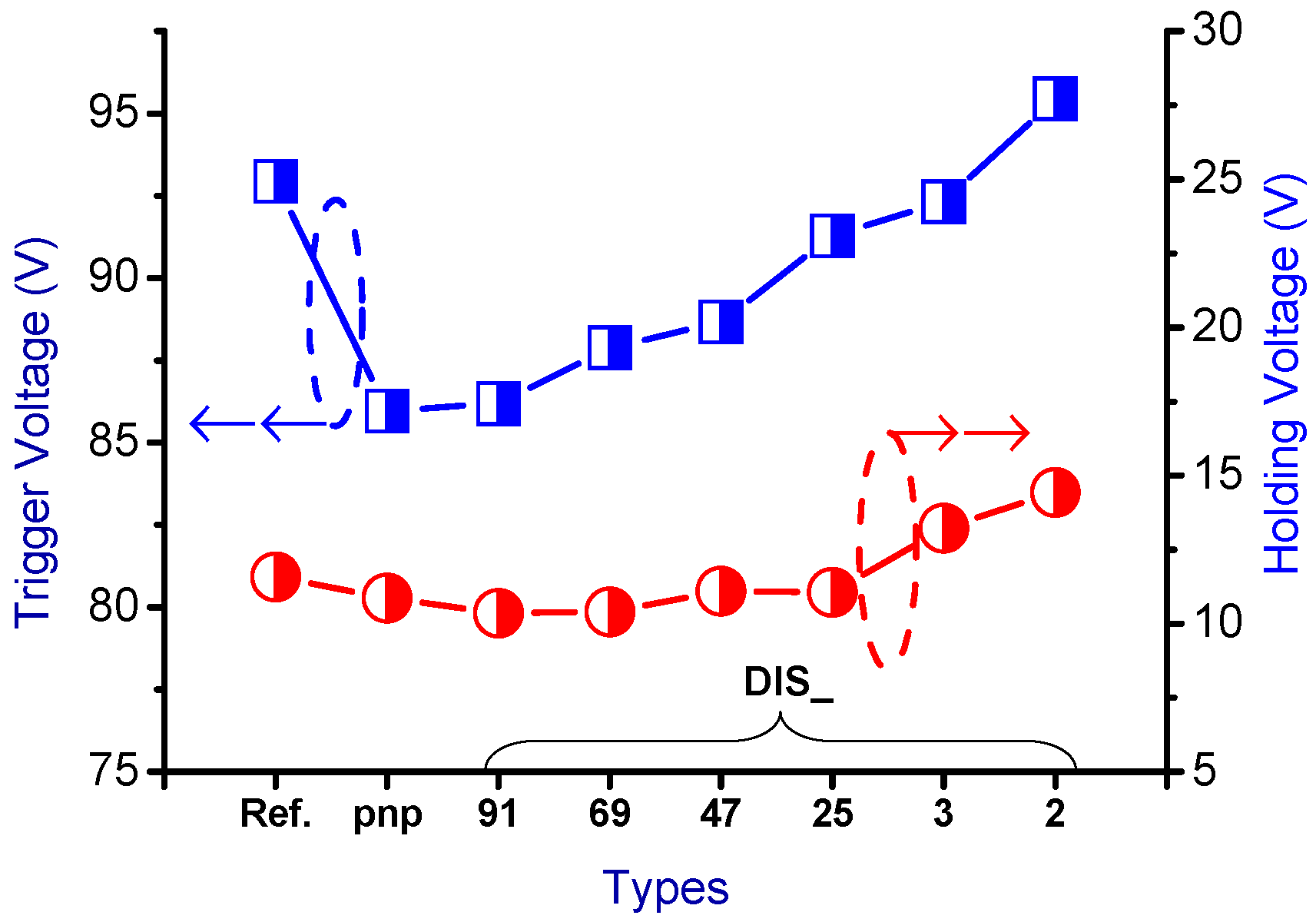

4.2. 60-V High-Voltage nLDMOS-Silicon-Controlled Rectifier: The Discrete p-n-p-Arranged Type

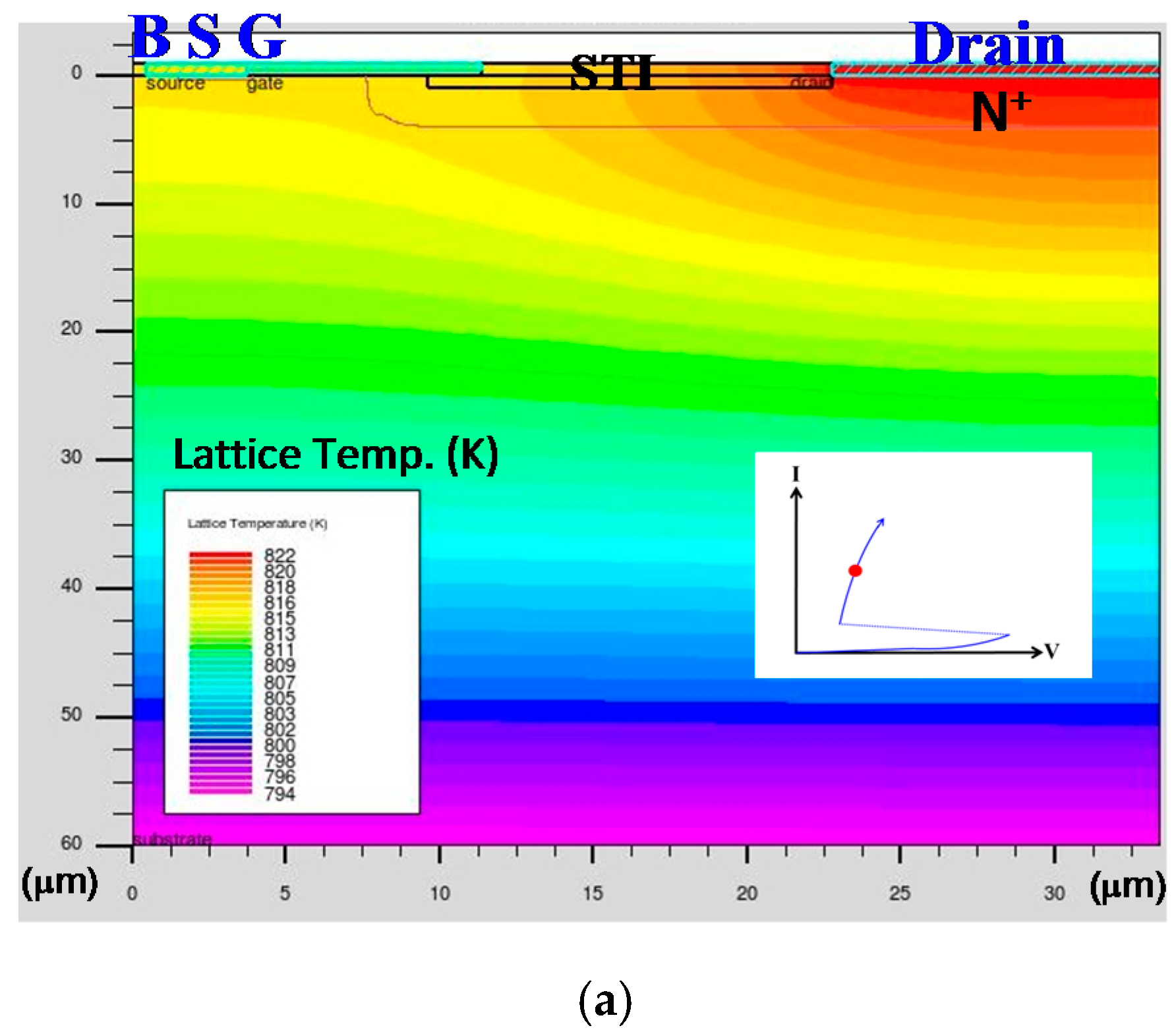

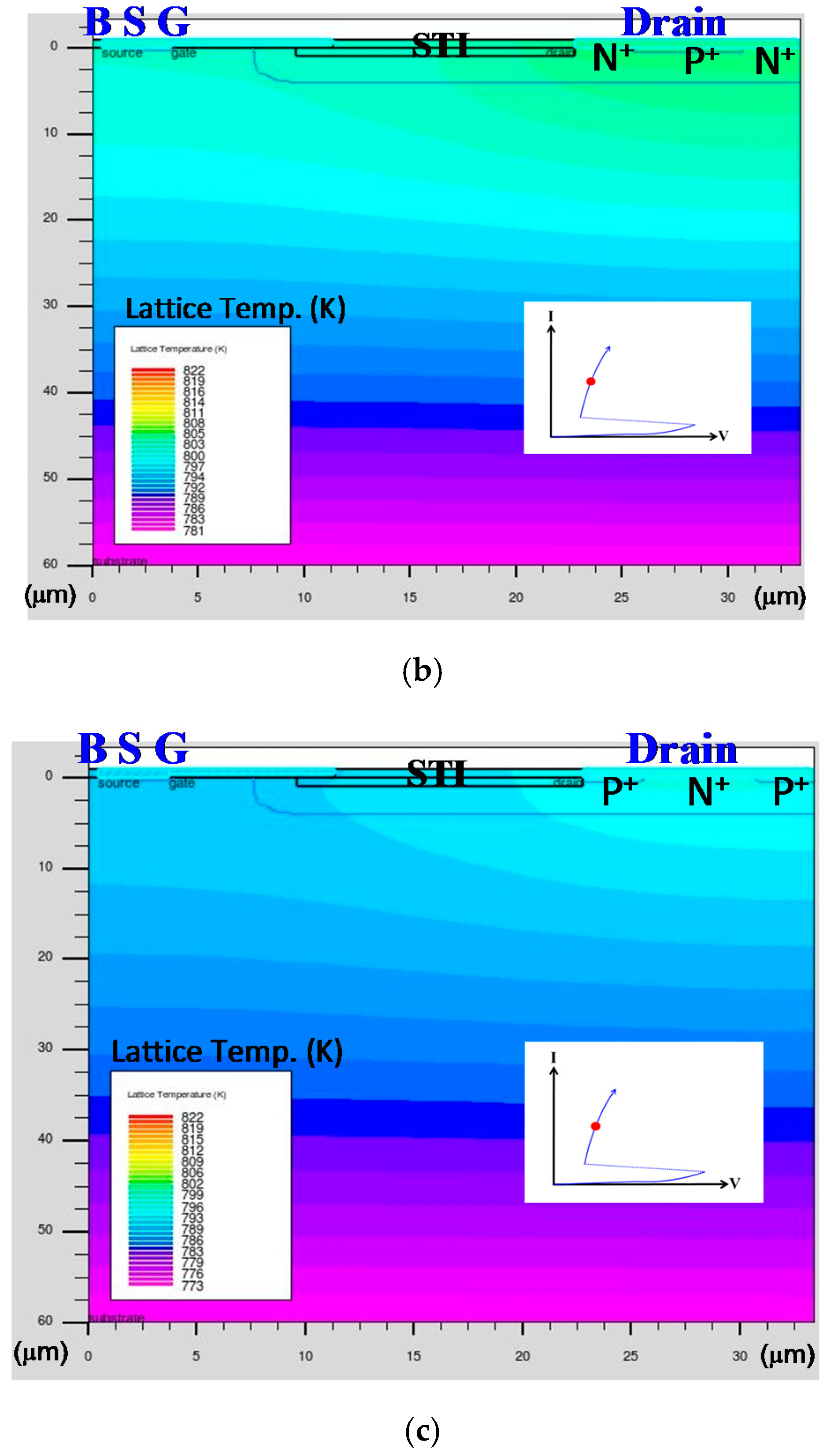

4.3. High-Voltage nLDMOS and nLDMOS-Silicon-Controlled Rectifier TCAD Simulation and Verification

5. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Vinson, J.E.; Liou, J.J. Electrostatic discharge in semiconductor devices: Overview of circuit protection techniques. In Proceedings of the IEEE Hong Kong Electron Devices Meeting, Hong Kong, China, 24 June 2000; pp. 5–8. [Google Scholar]

- Sasaki, H.; Sugimoto, H.; Tanino, N. Reliability of Metal-Insulator-Metal (MIM) after Electrostatic Discharge (ESD) Stress. In Proceedings of the IEEE Compound Semiconductor Integrated Circuits Symposium, Monterey, CA, USA, 12–15 October 2008; pp. 1–4. [Google Scholar]

- Olney, A.H. Eliminating the top causes of customer-attributable integrated circuit failures. In Proceedings of the 20th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Suzhou, China, 15–19 July 2013; pp. 8–14. [Google Scholar]

- Gossner, H. Design for ESD protection at its limits. In Proceedings of the 2013 Symposium on VLSI Technology, Kyoto, Japan, 11–13 June 2013; pp. T120–T121. [Google Scholar]

- Li, Y.; Mishra, R.; Song, L.; Gauthier, R. Design and optimization of ESD lateral NPN device in 14 nm FinFET SOI CMOS technology. In Proceedings of the Electrical Overstress/Electrostatic Discharge Symposium, Reno, NV, USA, 27 September–2 October 2015; pp. 1–7. [Google Scholar]

- Abu, H.; Abdennadher, S.; Provost, B.; Muljono, H. Augmenting ESD and EOS physical analysis with per pin ESD and leakage DFT. In Proceedings of the 19th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 13–14 March 2018; pp. 20–24. [Google Scholar]

- Ko, K.; Park, J.; Eum, J.; Lee, K.; Lee, S.; Lee, J. Proposal of 0.13 μm new structure LDMOS for automotive PMIC. In Proceedings of the 73rd Annual Device Research Conference (DRC), Columbus, OR, USA, 21–24 June 2015; pp. 119–120. [Google Scholar]

- Disney, D.; Park, I.L.Y.; Lin, W.C.; Kim, J. High-voltage IC technologies for AC/DC power conversion. In Proceedings of the IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), Singapore, 1–4 June 2015; pp. 142–145. [Google Scholar]

- Kojima, J.; Matsuda, J.; Kamiyama, M.; Tsukiji, N.; Kobayashi, H. Optimization and analysis of high reliability 30–50 V dual RESURF LDMOS. In Proceedings of the 13th IEEE International Conference on Solid-State and Integrated Circuit Technology, Hangzhou, China, 25–28 October 2016; pp. 392–394. [Google Scholar]

- Ritter, M.; Pham, G.; Pfost, M. On-Chip Sensors to Detect Impending Metallization Failure of LDMOS Transistors under Repetitive Thermo-Mechanical Stress. IEEE Trans. Semicond. Manuf. 2016, 29, 193–200. [Google Scholar] [CrossRef]

- Shrivastava, M. Drain Extended Tunnel FET-A Novel Power Transistor for RF and Switching Applications. IEEE Trans. Electron. Devices 2017, 64, 481–487. [Google Scholar] [CrossRef]

- Bosi, G.; Raffo, A.; Trevisan, F.; Vadalà, V.; Crupi, G.; Vannini, G. Nonlinear-Embedding Design Methodology Oriented to LDMOS Power Amplifiers. IEEE Trans. Power Electron. 2018, 33, 8764–8774. [Google Scholar] [CrossRef]

- Wang, S.J.; Yao, F.; Qin, B.; Chen, H.Y.; Wang, X.; Zhao, H.; Fang, Q.; Lin, L.; Wang, A. Analysis and optimization of HV ESD protection. In Proceedings of the IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 15–17 December 2010; pp. 1–4. [Google Scholar]

- Wang, Y.; Lu, G.; Cao, J.; Liu, Q.; Zhang, G.; Zhang, X. A novel ESD self-protecting symmetric nLDMOS for 60 V SOI BCD process. In Proceedings of the IEEE International Conference of Electron Devices and Solid-State Circuits, Hong Kong, China, 3–5 June 2013; pp. 1–2. [Google Scholar]

- Tazzoli, A.; Vashchenko, V.; Shibkov, A. Effect of process technology variation on ESD clamp parameters. In Proceedings of the Electrical Overstress/Electrostatic Discharge Symposium, Tucson, AZ, USA, 7–12 September 2014; pp. 1–7. [Google Scholar]

- Wang, Y.; Jin, X.; Yang, L. Robust lateral double-diffused MOS with interleaved bulk and source for high-voltage electrostatic discharge protection. IET Power Electron. 2015, 8, 2251–2256. [Google Scholar] [CrossRef]

- Liang, H.L.; Gu, X.F.; Dong, S.; Liou, J.J. RC-Embedded LDMOS-SCR With High Holding Current for High-Voltage I/O ESD Protection. IEEE Trans. Device Mater. Reliab. 2015, 15, 495–499. [Google Scholar] [CrossRef]

- Wu, C.-H.; Lee, J.-H.; Lien, C.-H. A New Low-Voltage Triggering SCR for the Protection of a Double RESURF HV-LDMOS. IEEE Electron. Device Lett. 2016, 37, 1201–1203. [Google Scholar] [CrossRef]

- Pjenčák, J.; Agam, M.; Šeliga, A.; Yao, T.; Suwhanov, A. Novel approach for NLDMOS performance enhancement by critical electric field engineering. In Proceedings of the IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 307–310. [Google Scholar]

- Tseng, J.-C.; Chen, Y.-L.; Hsu, C.-T.; Tsai, F.-Y.; Chen, P.-A.; Ker, M.-D. Mechanism of snapback failure induced by the latch-up test in high-voltage CMOS integrated circuits. In Proceedings of the IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008; pp. 625–626. [Google Scholar]

- Zhang, P.; Wang, Y.; Jia, S.; Zhang, X. A novel multi-finger layout strategy for GGnMOS ESD protection device. In Proceedings of the IEEE 9th International Conference on ASIC (ASICON), Xiamen, China, 25–28 October 2011; pp. 275–278. [Google Scholar]

- Meng, K.-H.; Rosenbaum, E. Layout-aware, distributed, compact model for multi-finger MOSFETs operating under ESD conditions. In Proceedings of the Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Las Vegas, NV, USA, 10–12 September 2013; pp. 1–8. [Google Scholar]

- Aliaj, B.; Vashchenko, V.A.; Liou, J.-J.; Mitchell, T. Overcoming multi finger turn-on in HV DIACs using local poly-ballasting. In Proceedings of the 36th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Tucson, AZ, USA, 7–12 September 2014; pp. 1–7. [Google Scholar]

- Wu, C.-H.; Lien, C.-H.; Lee, J.-H. Failure mechanism of high-voltage isolated lateral diffused NMOS under high-current events. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016; pp. EL-2-1–EL-2-5. [Google Scholar]

- Chen, S.-L.; Yen, C.-Y.; Yang, C.-H.; Wu, Y.-C.; Chen, K.-J.; Lin, Y.-L.; Chiu, Y.-H.; Chao, Y.-H.; Chen, H.-W.; Chen, D.; et al. ESD-Immunity Evaluations of a 40 V nLDMOS with Embedded SCRs in the Drain Side. In Proceedings of the IEEE International Symposium on Next-Generation Electronics, Keelung, Taiwan, 23–25 May 2017; pp. 1–2. [Google Scholar]

| nLDMOS + Drain SCR | Vt1 (V) | Vh (V) | It2 (A) (mean ± σ) | |

|---|---|---|---|---|

| Ref. DUT (nLDMOS) | 92.941 | 11.587 | 1.833 ± 0.083 | |

| nLD-SCR npn Stripe type | 93.114 | 12.006 | 2.096 ± 0.214 | |

| n-p-n-type | DIS_91 | 93.313 | 12.138 | 2.157 ± 0.034 |

| DIS_69 | 93.494 | 12.148 | 2.144 ± 0.078 | |

| DIS_47 | 93.518 | 12.175 | 2.121 ± 0.163 | |

| DIS_25 | 93.559 | 12.378 | 2.034 ± 0.019 | |

| DIS_3 | 93.683 | 12.616 | 1.936 ± 0.066 | |

| DIS_2 | 93.41 | 12.472 | 1.792 ± 0.024 | |

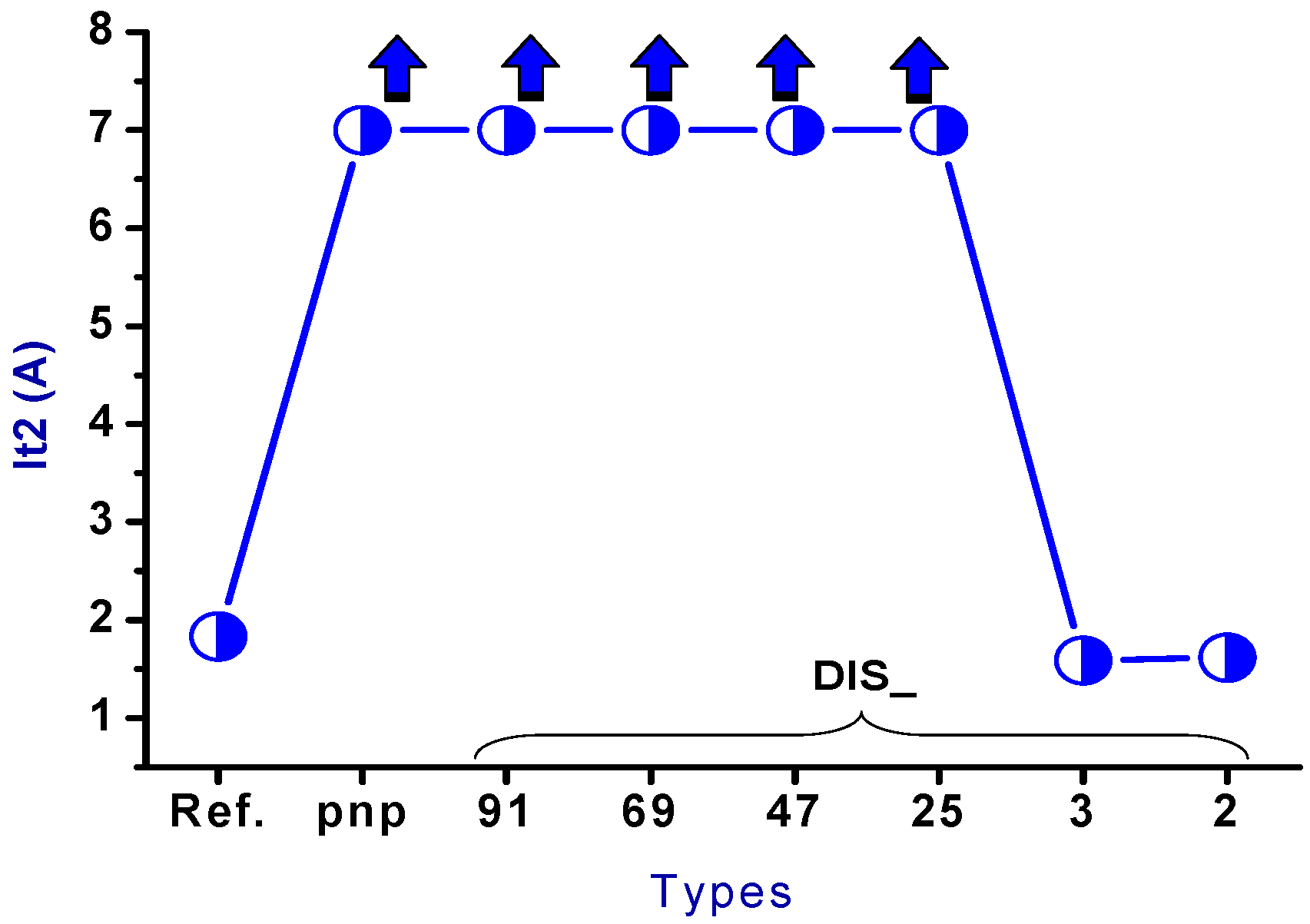

| nLDMOS + Drain SCR | Vt1 (V) | Vh (V) | It2 (A) (mean ± σ) | |

|---|---|---|---|---|

| Ref. DUT (nLDMOS) | 92.941 | 11.587 | 1.833±0.083 | |

| nLD-SCR pnp Stripe type | 85.971 | 10.863 | >7 | |

| p-n-p-type | DIS_91 | 86.189 | 10.358 | >7 |

| DIS_69 | 87.889 | 10.401 | > | |

| DIS_47 | 88.661 | 11.106 | >7 | |

| DIS_25 | 91.287 | 11.051 | >7 | |

| DIS_3 | 92.326 | 13.220 | 1.59 ± 0.2 | |

| DIS_2 | 95.445 | 14.434 | 1.618 ± 0.084 | |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, S.-L.; Wu, Y.-C. Sensing and Reliability Improvement of Electrostatic-Discharge Transient by Discrete Engineering for High-Voltage 60-V n-Channel Lateral-Diffused MOSFETs with Embedded Silicon-Controlled Rectifiers. Sensors 2018, 18, 3340. https://doi.org/10.3390/s18103340

Chen S-L, Wu Y-C. Sensing and Reliability Improvement of Electrostatic-Discharge Transient by Discrete Engineering for High-Voltage 60-V n-Channel Lateral-Diffused MOSFETs with Embedded Silicon-Controlled Rectifiers. Sensors. 2018; 18(10):3340. https://doi.org/10.3390/s18103340

Chicago/Turabian StyleChen, Shen-Li, and Yi-Cih Wu. 2018. "Sensing and Reliability Improvement of Electrostatic-Discharge Transient by Discrete Engineering for High-Voltage 60-V n-Channel Lateral-Diffused MOSFETs with Embedded Silicon-Controlled Rectifiers" Sensors 18, no. 10: 3340. https://doi.org/10.3390/s18103340

APA StyleChen, S.-L., & Wu, Y.-C. (2018). Sensing and Reliability Improvement of Electrostatic-Discharge Transient by Discrete Engineering for High-Voltage 60-V n-Channel Lateral-Diffused MOSFETs with Embedded Silicon-Controlled Rectifiers. Sensors, 18(10), 3340. https://doi.org/10.3390/s18103340