Multiphase Interpolating Digital Power Amplifiers for TX Beamforming

Abstract

:1. Introduction

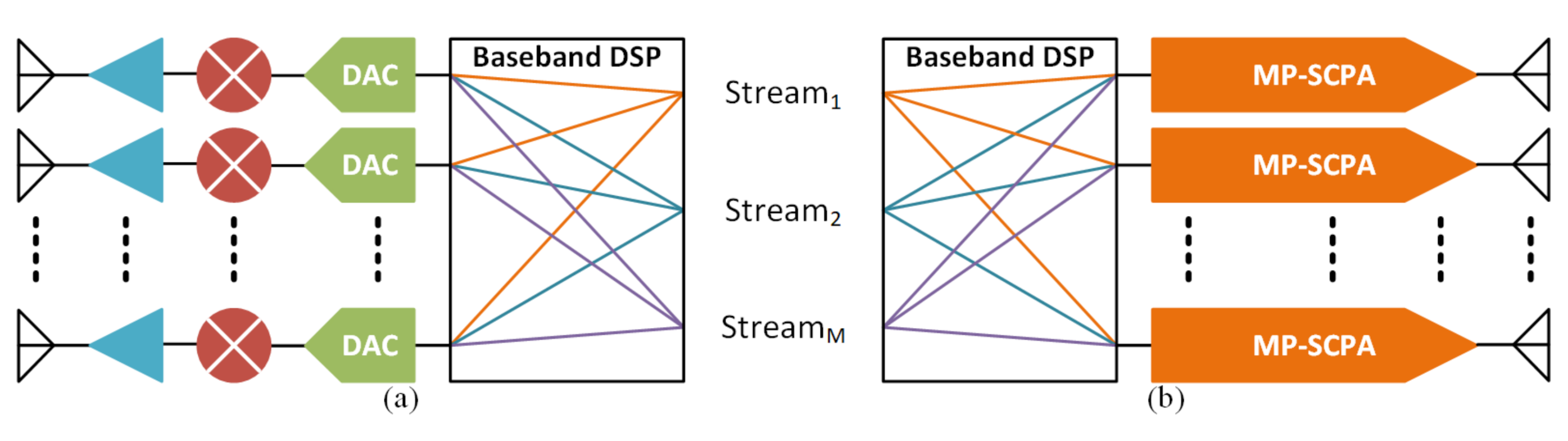

2. Review of Highly Digital Beamforming Transmitters/PAs

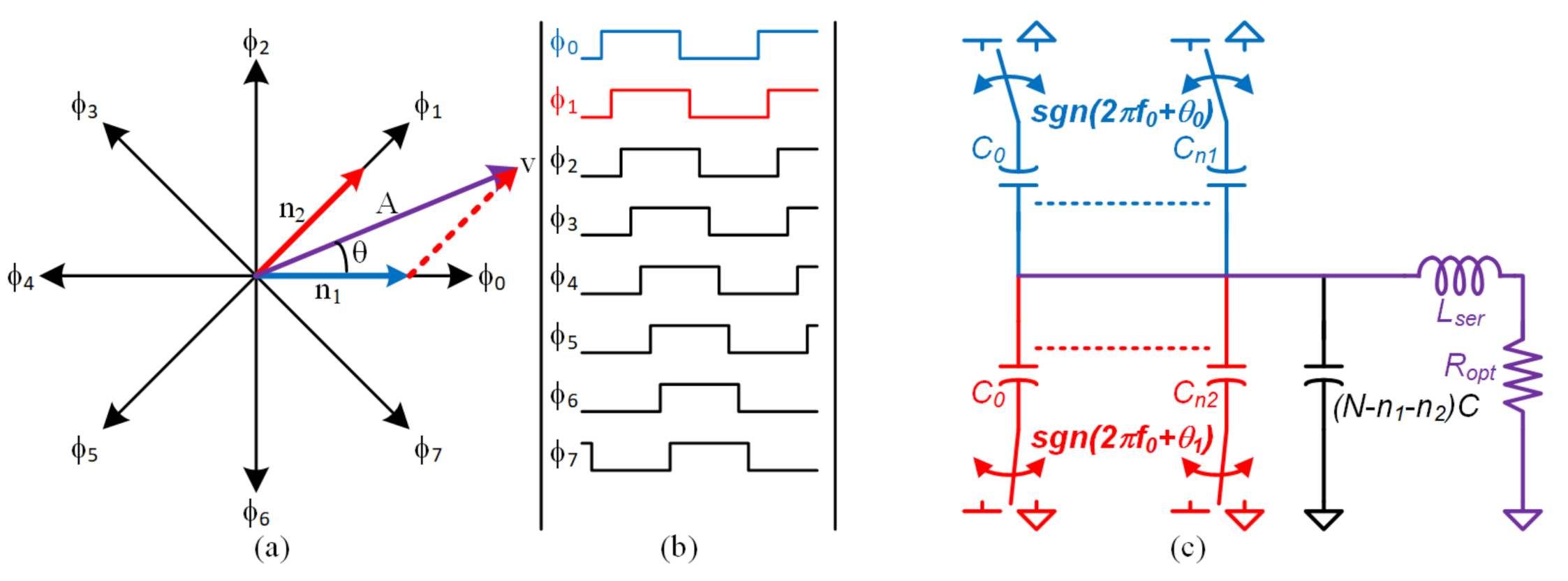

3. Multiphase Interpolation Beamforming

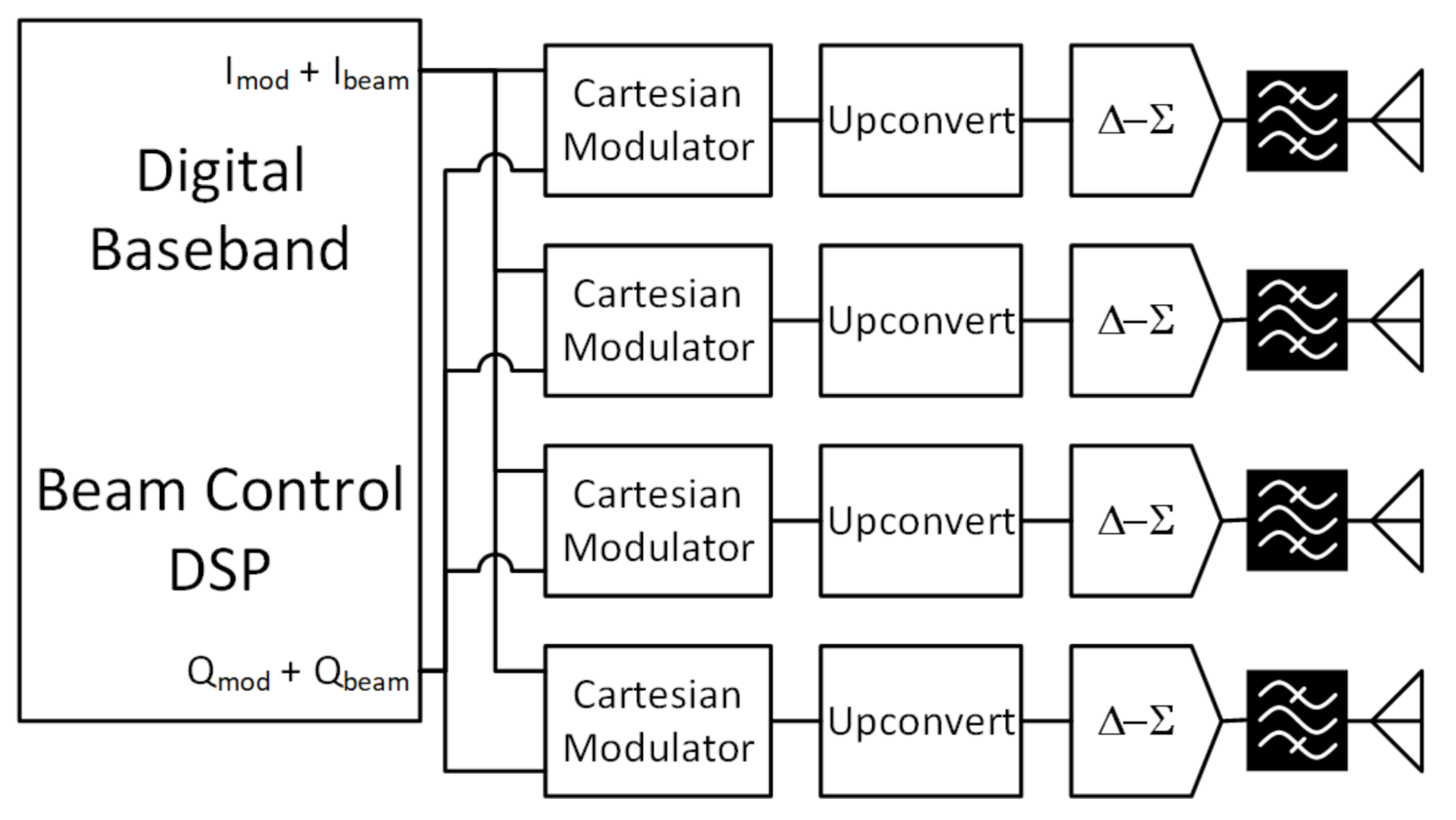

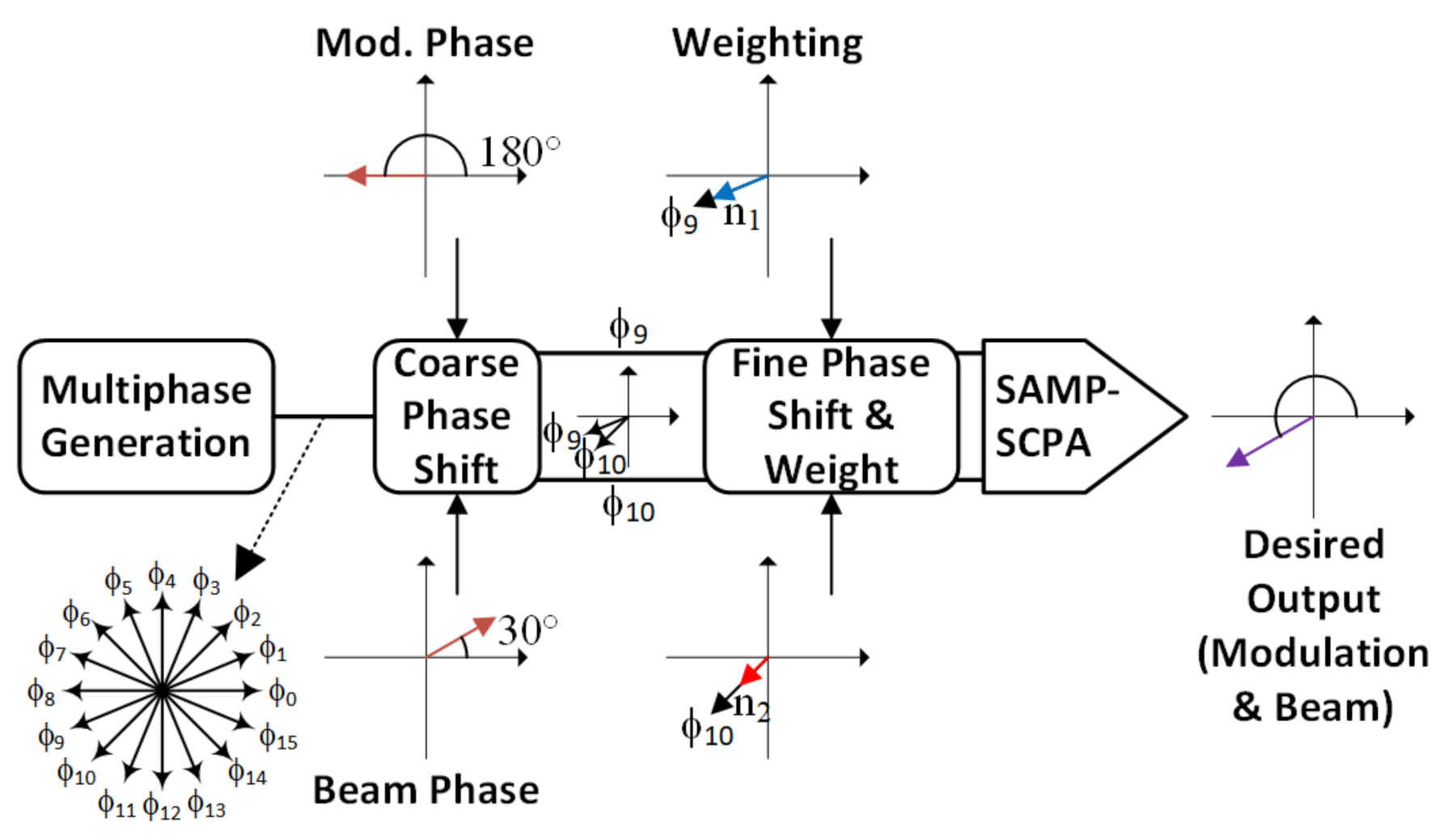

3.1. Single Multiphase Transmitter Operation

3.2. Amplitude and Phase Resolution in MP-SCPA

3.3. Multiphase Beamforming Operation Example

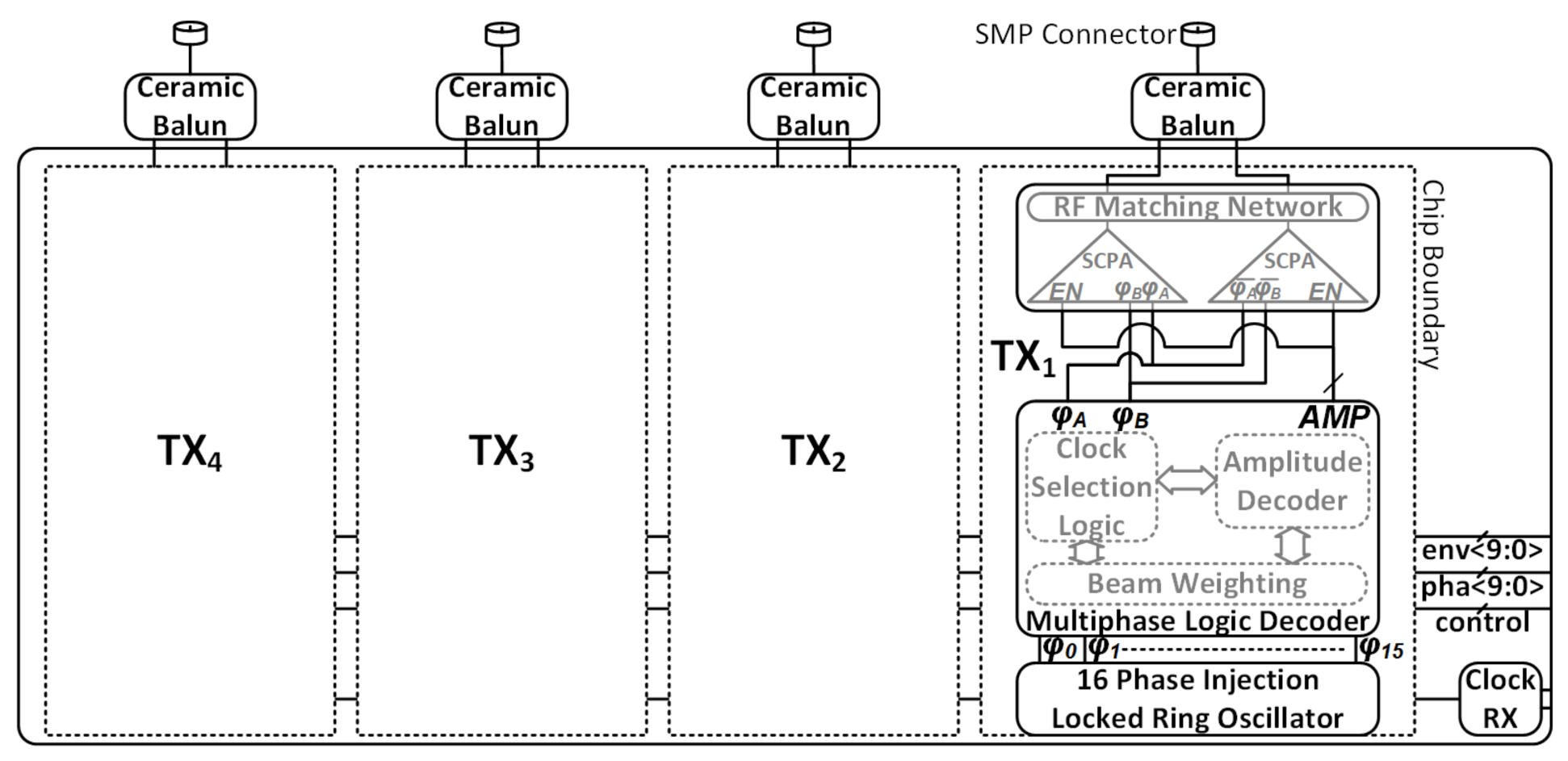

4. Circuit Design Details

4.1. MP Clock Generation

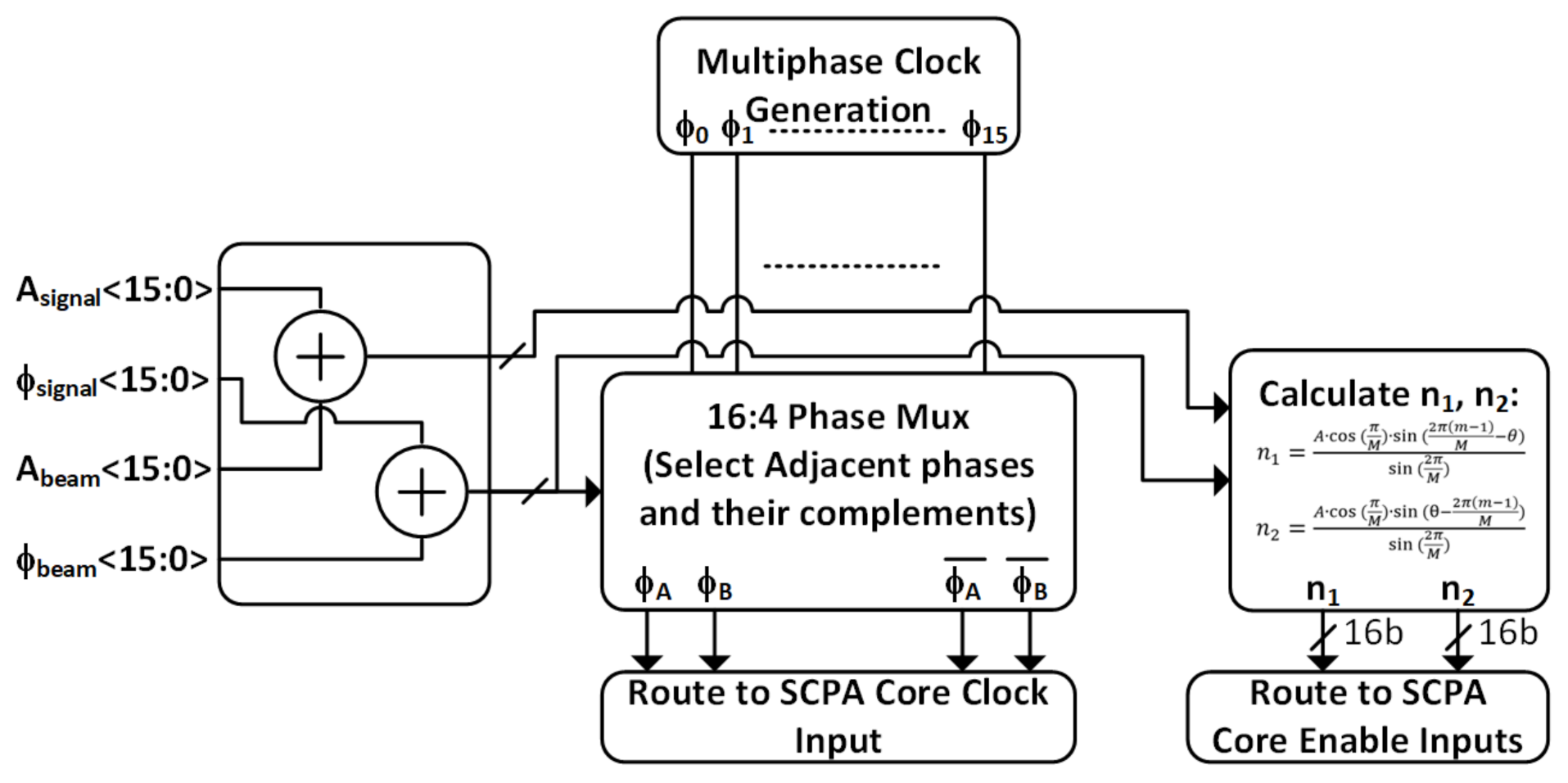

4.2. MP Logic Decoder

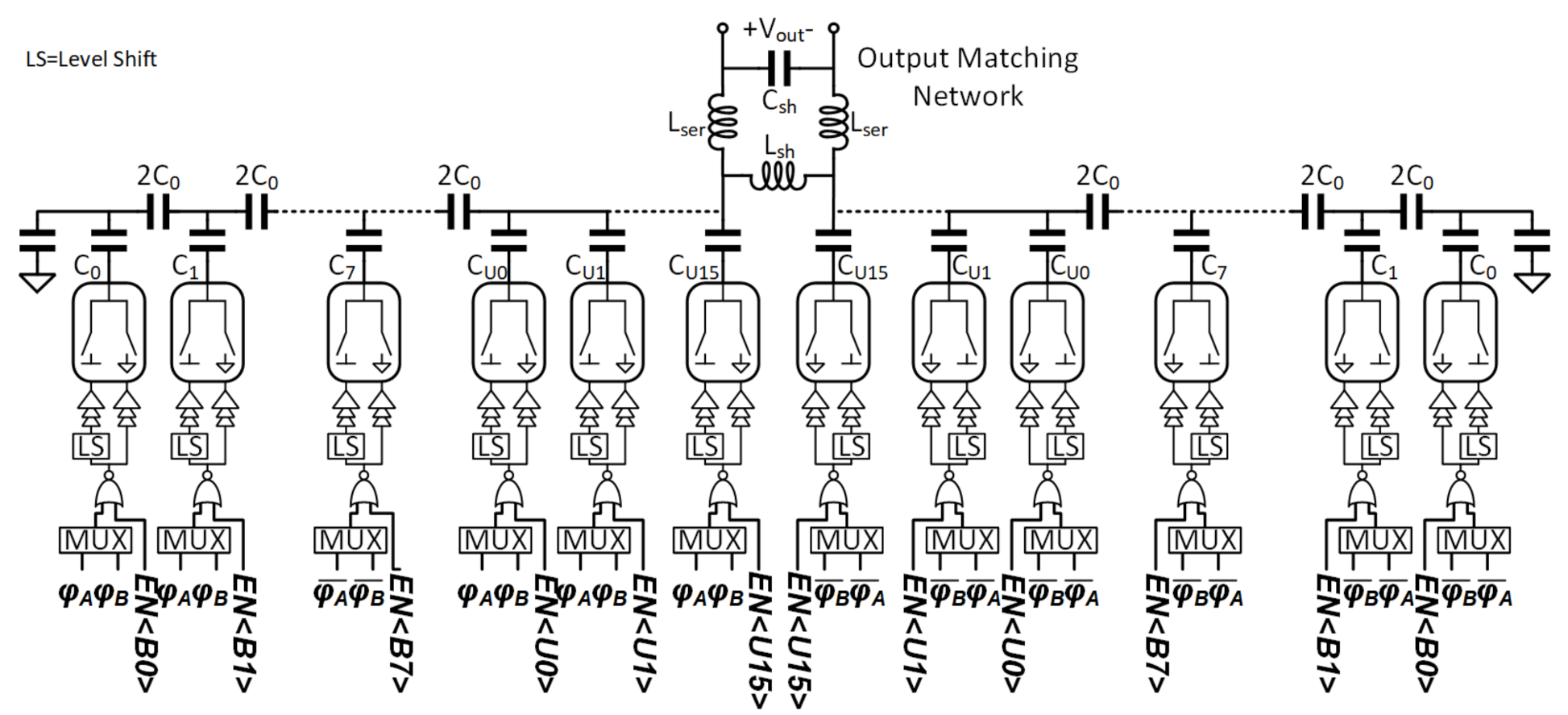

4.3. 16-b SAMP-SCPA

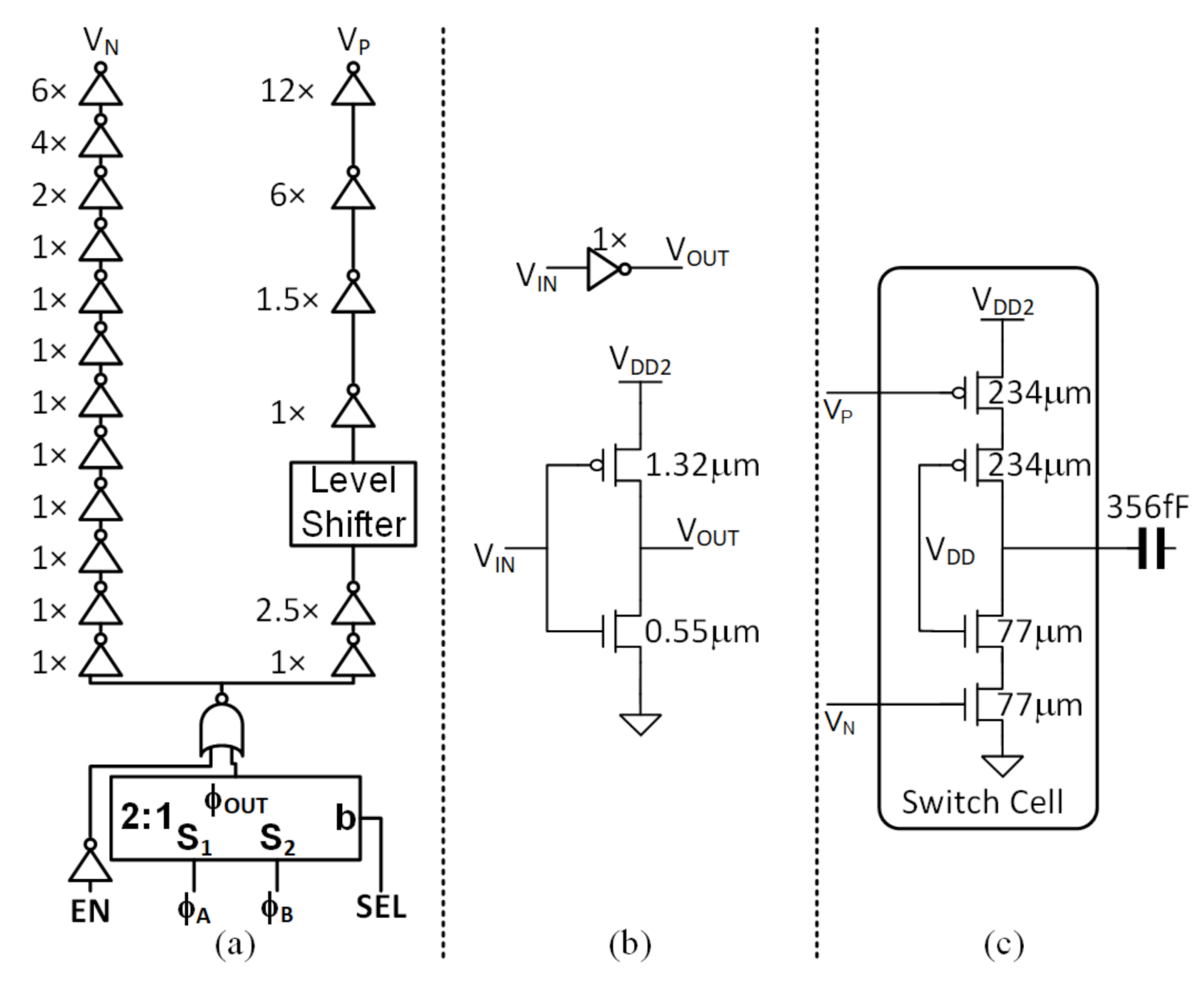

4.3.1. SAMP-SCPA Input Logic Design

4.3.2. Switch Driver Slice Design

4.3.3. Output Switch and Capacitor

4.3.4. Matching Network

5. Experimental Results

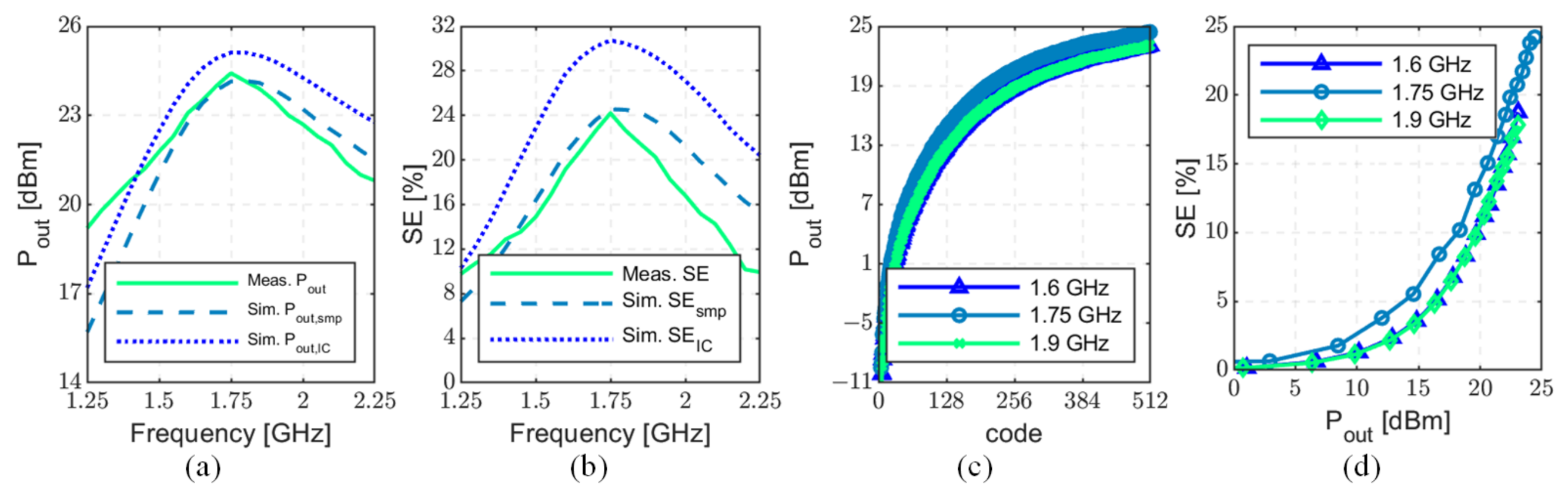

5.1. Static Measurements

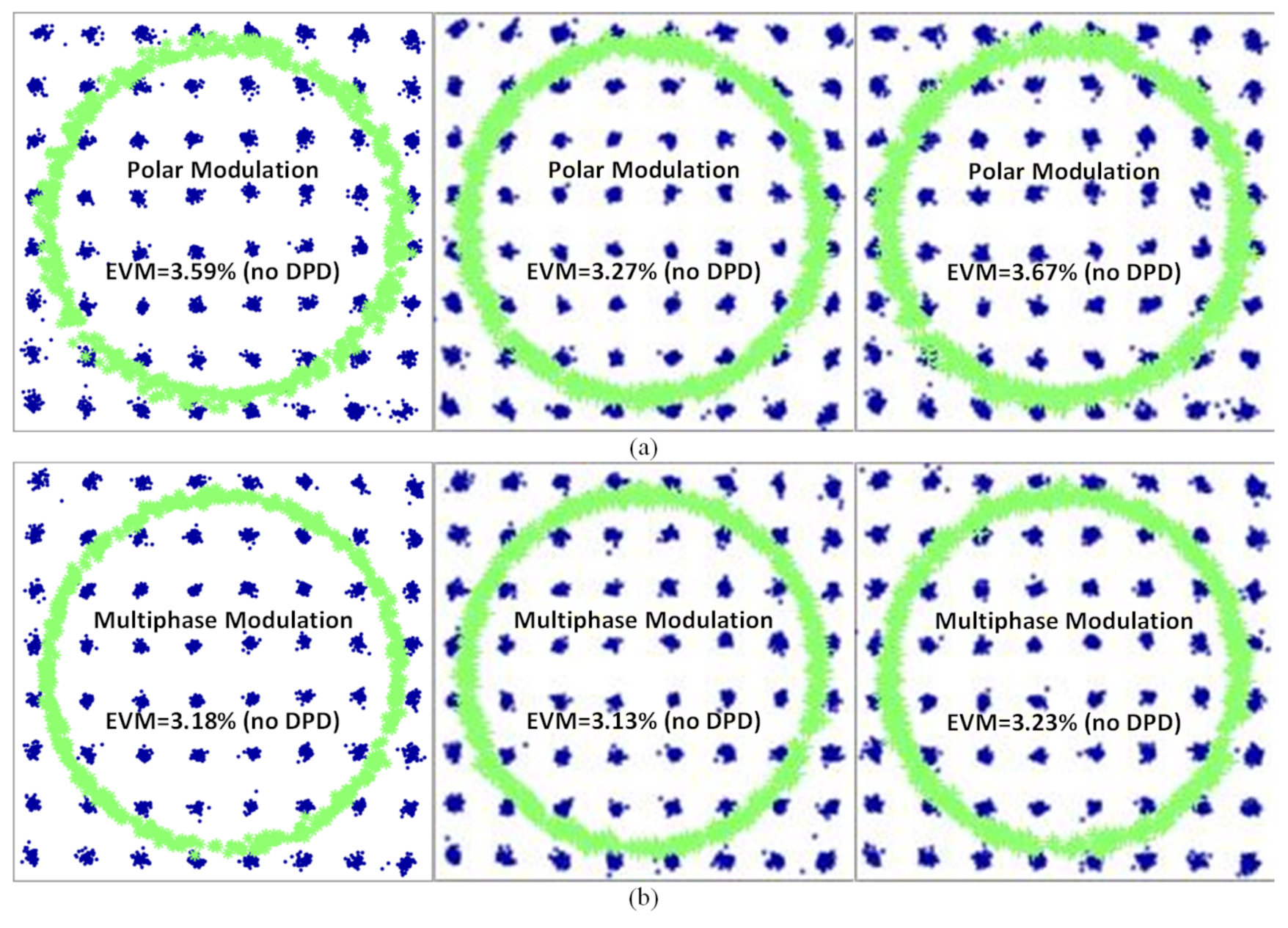

5.2. Dynamic Measurements

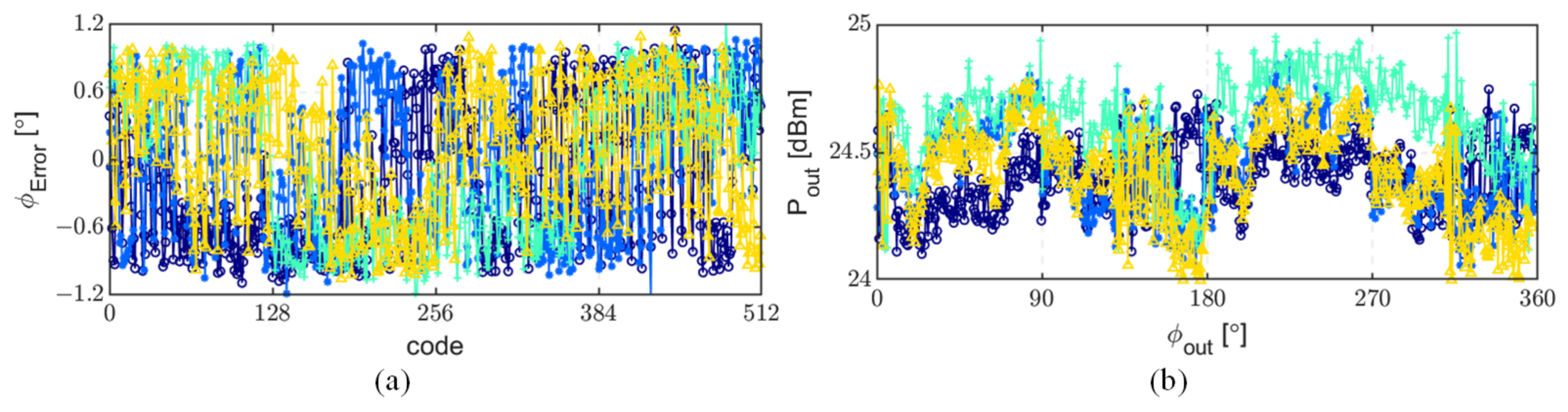

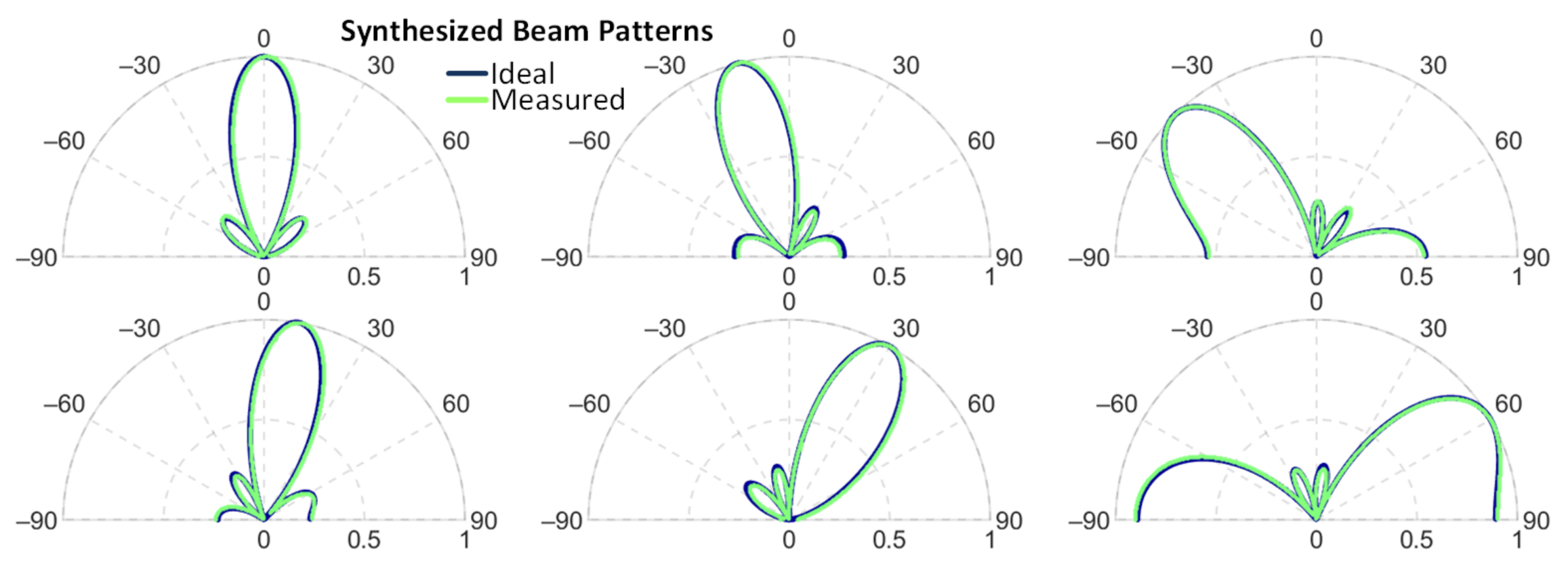

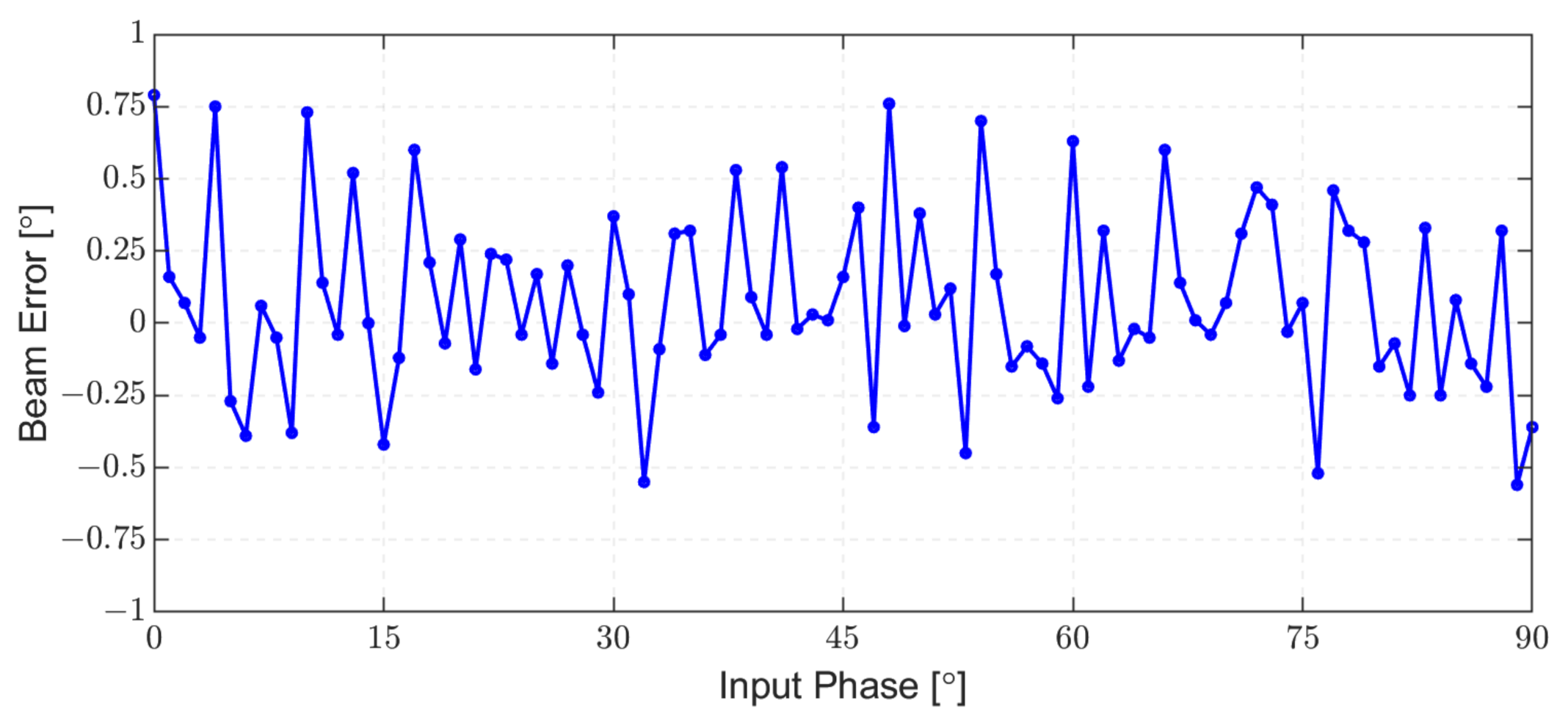

5.3. Beamforming Measurements

6. Discussion

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Hashemi, H.; Guan, X.; Komijani, A.; Hajimiri, A. A 24-GHz SiGe phased-array receiver-LO phase-shifting approach. IEEE Trans. Microw. Theory Tech. 2005, 53, 614–626. [Google Scholar] [CrossRef] [Green Version]

- Krishnaswamy, H.; Hashemi, H. A Variable-Phase Ring Oscillator and PLL Architecture for Integrated Phased Array Transceivers. IEEE J. Solid-State Circuits 2008, 43, 2446–2463. [Google Scholar] [CrossRef]

- Ta, T.T.; Tanifuji, S.; Kameda, S.; Suematsu, N.; Takagi, T.; Tsubouchi, K. A Si-CMOS 5-bit baseband phase shifter using fixed gain amplifier matrix. In Proceedings of the 2012 7th European Microwave Integrated Circuit Conference, Amsterdam, The Netherlands, 29–30 October 2012; pp. 576–579. [Google Scholar]

- Paramesh, J.; Bishop, R.; Soumyanath, K.; Allstot, D. A four-antenna receiver in 90-nm CMOS for beamforming and spatial diversity. IEEE J. Solid-State Circuits 2005, 40, 2515–2524. [Google Scholar] [CrossRef]

- Koh, K.J.; Rebeiz, G.M. An X- and Ku-Band 8-Element Phased-Array Receiver in 0.18-μm SiGe BiCMOS Technology. IEEE J. Solid-State Circuits 2008, 43, 1360–1371. [Google Scholar] [CrossRef]

- Paro Filho, P.E.; Ingels, M.; Wambacq, P.; Craninckx, J. An Incremental-Charge-Based Digital Transmitter with Built-in Filtering. IEEE J. Solid-State Circuits 2015, 50, 3065–3076. [Google Scholar] [CrossRef]

- Yoo, S.M.; Walling, J.S.; Woo, E.C.; Jann, B.; Allstot, D.J. A Switched-Capacitor RF Power Amplifier. IEEE J. Solid-State Circuits 2014, 46, 2977–2987. [Google Scholar] [CrossRef]

- Wang, L.; Lian, Y.; Heng, C.H. 3–5 GHz 4-Channel UWB Beamforming Transmitter with 1∘ Scanning Resolution Through Calibrated Vernier Delay Line in 0.13-μm CMOS. IEEE J. Solid-State Circuits 2012, 47, 3145–3159. [Google Scholar] [CrossRef]

- Qian, H.J.; Zhou, J.; Yang, B.; Luo, X. A 4-Element Digital Modulated Polar Phased-Array Transmitter With Phase Modulation Phase-Shifting. IEEE J. Solid-State Circuits 2021, 56, 3331–3347. [Google Scholar] [CrossRef]

- Zheng, B.; Jie, L.; Bell, J.; He, Y.; Flynn, M.P. A Two-Beam Eight-Element Direct Digital Beamforming RF Modulator in 40-nm CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 2569–2579. [Google Scholar] [CrossRef]

- McCune, E.W. Concurrent polar and quadrature modulator. In Proceedings of the WAMICON 2014, Tampa, FL, USA, 6 June 2014; pp. 1–4. [Google Scholar] [CrossRef]

- Bai, Z.; Yuan, W.; Azam, A.; Walling, J.S. A Multiphase Interpolating Digital Power Amplifier for TX Beamforming in 65nm CMOS. In Proceedings of the 2019 IEEE International Solid- State Circuits Conference—(ISSCC) 2019, San Francisco, CA, USA, 17–21 February 2019; pp. 78–80. [Google Scholar] [CrossRef]

- Yuan, W.; Walling, J.S. A Multiphase Switched Capacitor Power Amplifier. IEEE J. Solid-State Circuits 2017, 52, 1320–1330. [Google Scholar] [CrossRef]

- Bai, Z.; Azam, A.; Johnson, D.; Yuan, W.; Walling, J.S. Split-Array, C-2C Switched-Capacitor Power Amplifiers. IEEE J. Solid-State Circuits 2018, 53, 1666–1677. [Google Scholar] [CrossRef]

- Alavi, M.S.; Staszewski, R.B.; de Vreede, L.C.N.; Long, J.R. A Wideband 2×13-bit All-Digital I/Q RF-DAC. IEEE Trans. Microw. Theory Tech. 2014, 62, 732–752. [Google Scholar] [CrossRef]

- Bhat, R.; Zhou, J.; Krishnaswamy, H. Wideband Mixed-Domain Multi-Tap Finite-Impulse Response Filtering of Out-of-Band Noise Floor in Watt-Class Digital Transmitters. IEEE J. Solid-State Circuits 2017, 52, 3405–3420. [Google Scholar] [CrossRef]

- Hashemi, M.; Shen, Y.; Mehrpoo, M.; Alavi, M.S.; de Vreede, L.C.N. An Intrinsically Linear Wideband Polar Digital Power Amplifier. IEEE J. Solid-State Circuits 2017, 52, 3312–3328. [Google Scholar] [CrossRef]

- Park, J.S.; Wang, Y.; Pellerano, S.; Hull, C.; Wang, H. A CMOS Wideband Current-Mode Digital Polar Power Amplifier with Built-In AM–PM Distortion Self-Compensation. IEEE J. Solid-State Circuits 2018, 53, 340–356. [Google Scholar] [CrossRef]

- Zhang, A.; Chen, M.S.W. A Watt-Level Phase-Interleaved Multi-Subharmonic Switching Digital Power Amplifier. IEEE J. Solid-State Circuits 2019, 54, 3452–3465. [Google Scholar] [CrossRef]

- Yin, Y.; Li, T.; Xiong, L.; Li, Y.; Min, H.; Yan, N.; Xu, H. A Broadband Switched-Transformer Digital Power Amplifier for Deep Back-Off Efficiency Enhancement. IEEE J. Solid-State Circuits 2020, 55, 2997–3008. [Google Scholar] [CrossRef]

- Zarei, H.; Allstot, D. A low-loss phase shifter in 180 nm CMOS for multiple-antenna receivers. In Proceedings of the 2004 IEEE International Solid-State Circuits Conference (IEEE Cat. No.04CH37519), San Francisco, CA, USA, 15–19 February 2004; Volume 1, pp. 392–534. [Google Scholar] [CrossRef]

- Walling, J.S. The Switched-Capacitor Power Amplifier: A Key Enabler for Future Communications Systems. In Proceedings of the IEEE 45th European Solid State Circuits Conference (ESSCIRC), Cracow, Poland, 23–26 September 2019; pp. 18–24. [Google Scholar] [CrossRef]

- Fulde, M.; Belitzer, A.; Boos, Z.; Bruennert, M.; Fritzin, J.; Geltinger, H.; Groinig, M.; Gruber, D.; Gruenberger, S.; Hartig, T.; et al. A digital multimode polar transmitter supporting 40MHz LTE Carrier Aggregation in 28nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 218–219. [Google Scholar] [CrossRef]

- Yoo, S.W.; Hung, S.C.; Yoo, S.M. A Watt-Level Quadrature Class-G Switched-Capacitor Power Amplifier With Linearization Techniques. IEEE J. Solid-State Circuits 2019, 54, 1274–1287. [Google Scholar] [CrossRef]

- Kavousian, A.; Su, D.K.; Hekmat, M.; Shirvani, A.; Wooley, B.A. A Digitally Modulated Polar CMOS Power Amplifier With a 20-MHz Channel Bandwidth. IEEE J. Solid-State Circuits 2008, 43, 2251–2258. [Google Scholar] [CrossRef]

- Presti, C.D.; Carrara, F.; Scuderi, A.; Asbeck, P.M.; Palmisano, G. A 25 dBm Digitally Modulated CMOS Power Amplifier for WCDMA/EDGE/OFDM With Adaptive Digital Predistortion and Efficient Power Control. IEEE J. Solid-State Circuits 2009, 44, 1883–1896. [Google Scholar] [CrossRef]

- Yoo, S.M.; Walling, J.S.; Degani, O.; Jann, B.; Sadhwani, R.; Rudell, J.C.; Allstot, D.J. A Class-G Switched-Capacitor RF Power Amplifier. IEEE J. Solid-State Circuits 2013, 48, 1212–1224. [Google Scholar] [CrossRef]

- Walling, J.S.; Allstot, D.J. Design considerations for supply modulated EER power amplifiers. In Proceedings of the WAMICON 2013, Orlando, FL, USA, 7–9 April 2013; pp. 1–4. [Google Scholar] [CrossRef]

- Staszewski, R.; Muhammad, K.; Leipold, D.; Hung, C.M.; Ho, Y.C.; Wallberg, J.; Fernando, C.; Maggio, K.; Staszewski, R.; Jung, T.; et al. All-digital TX frequency synthesizer and discrete-time receiver for Bluetooth radio in 130-nm CMOS. IEEE J. Solid-State Circuits 2004, 39, 2278–2291. [Google Scholar] [CrossRef]

- Boos, Z.; Menkhoff, A.; Kuttner, F.; Schimper, M.; Moreira, J.; Geltinger, H.; Gossmann, T.; Pfann, P.; Belitzer, A.; Bauernfeind, T. A fully digital multimode polar transmitter employing 17b RF DAC in 3G mode. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 376–378. [Google Scholar] [CrossRef]

- Ye, L.; Chen, J.; Kong, L.; Alon, E.; Niknejad, A.M. Design Considerations for a Direct Digitally Modulated WLAN Transmitter With Integrated Phase Path and Dynamic Impedance Modulation. IEEE J. Solid-State Circuits 2013, 48, 3160–3177. [Google Scholar] [CrossRef]

- Jin, H.; Kim, D.; Kim, B. Efficient Digital Quadrature Transmitter Based on IQ Cell Sharing. IEEE J. Solid-State Circuits 2017, 52, 1345–1357. [Google Scholar] [CrossRef]

- Li, T.; Xiong, L.; Yin, Y.; Liu, Y.; Min, H.; Yan, N.; Xu, H. A Wideband Digital Polar Transmitter with Integrated Capacitor-DAC-Based Constant-Envelope Digital-to-Phase Converter. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 83–86. [Google Scholar] [CrossRef]

- Madoglio, P.; Palaskas, Y.; Angel, J.; Tomasik, J.; Hampel, S.; Schubert, P.; Preyler, P.; Mayer, T.; Bauernfeind, T.; Plechinger, P.; et al. A Cellular Multiband DTC-Based Digital Polar Transmitter With -153-dBc/Hz Noise in 14-nm FinFET. IEEE J. Solid-State Circuits 2020, 55, 1830–1841. [Google Scholar] [CrossRef]

- Xiong, W.; Guo, Y.; Zschieschang, U.; Klauk, H.; Murmann, B. A 3-V, 6-Bit C-2C Digital-to-Analog Converter Using Complementary Organic Thin-Film Transistors on Glass. IEEE J. Solid-State Circuits 2010, 45, 1380–1388. [Google Scholar] [CrossRef]

- Maneatis, J.; Horowitz, M. Precise delay generation using coupled oscillators. IEEE J. Solid-State Circuits 1993, 28, 1273–1282. [Google Scholar] [CrossRef] [Green Version]

- Serneels, B.; Piessens, T.; Steyaert, M.; Dehaene, W. A high-voltage output driver in a 2.5-V 0.25-/spl mu/m CMOS technology. IEEE J. Solid-State Circuits 2005, 40, 576–583. [Google Scholar] [CrossRef]

- Jeong, J.; Kimball, D.F.; Kwak, M.; Hsia, C.; Draxler, P.; Asbeck, P.M. Modeling and Design of RF Amplifiers for Envelope Tracking WCDMA Base-Station Applications. IEEE Trans. Microw. Theory Tech. 2009, 57, 2148–2159. [Google Scholar] [CrossRef]

- Bai, Z.D.; Yuan, W.; Azam, A.; Walling, J.S. Multiphase Switched-Capacitor Power Amplifiers and Bandpass Digital Transmitters. IEEE RFIC Virtual J. 2016, 8, 1–12. [Google Scholar] [CrossRef]

- Chowdhury, D.; Hull, C.D.; Degani, O.B.; Wang, Y.; Niknejad, A.M. A Fully Integrated Dual-Mode Highly Linear 2.4 GHz CMOS Power Amplifier for 4G WiMax Applications. IEEE J. Solid-State Circuits 2009, 44, 3393–3402. [Google Scholar] [CrossRef]

| Ref. | Architecture | Technology (nm) | Supply (V) | Chip Area (mm) | Frequency (GHz) | Phase Resolution () | Phase Error (-rms) | Error (dB) |

|---|---|---|---|---|---|---|---|---|

| This Work | Multiphase Interpolation | 65 | 1.4/2.8 | 5 | 1.45–2.15 * | 0.7 | 0.32 | 0.15 |

| [8] | Vernier Delay Line | 130 | 1.2 | 7.2 | 3–5 | 1 | N/A | N/A |

| [9] | Quadrature Phase Modulator | 40 | 1.1/1.2 | 8.6 | 3–7 * | 0.35 | 0.2 | 0.2 |

| [10] | Quadrature Phase Modulator with Modulator | 40 | 1 | 0.19 | 0.8-1.2 | 11.25 | N/A | N/A |

| Ref. | Architecture | Technology (nm) | Supply (V) | Frequency (GHz) | Modulation | Linear (dBm) | Linear SE (%) | EVM (%-rms) | ACLR (dBc) | DPD |

|---|---|---|---|---|---|---|---|---|---|---|

| This Work | SAMP-SCPA | 65 | 1.4/2.8 | 1.75 | 15 MHz, 64 QAM OFDM | 18.4 * | 14 * | 3.3 | −30.4/−30.8 | No |

| [14] | SAMP-SCPA | 65 | 1.2/2.4 | 1.8 | 1.4 MHz, 64 QAM OFDM | 18.9 | 21.2 | 2.65 | −30.5/−30.9 | Yes |

| [17] | Polar-IDPA | 40 | 0.5 | 2.2 | 20 MHz, 64 QAM OFDM | 6.2 | 10.7 | 1.6 | −46/−46 | No |

| [18] | Polar-IDPA | 28 | 1.2 | 3.2 | 20 MS/s 256 QAM SC | 17.5 | 21.3 $ | 2.39 | −31.3 | PM-Free |

| [19] | Polar SCPA | 65 | 3.6 | 1.9 | 5 MHz, 16 QAM OFDM | 22.8 | 31.4 $ | 5.8 | N/A | Yes |

| [20] | Polar SCPA | 40 | 1.1 | 1.5 | 20 MHz, 64 QAM OFDM | 15.2 | 25.3 | 2.4 | −33/−30.4 | Yes |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bai, Z.; Yuan, W.; Azam, A.; Walling, J.S. Multiphase Interpolating Digital Power Amplifiers for TX Beamforming. Chips 2022, 1, 30-50. https://doi.org/10.3390/chips1010004

Bai Z, Yuan W, Azam A, Walling JS. Multiphase Interpolating Digital Power Amplifiers for TX Beamforming. Chips. 2022; 1(1):30-50. https://doi.org/10.3390/chips1010004

Chicago/Turabian StyleBai, Zhidong, Wen Yuan, Ali Azam, and Jeffrey S. Walling. 2022. "Multiphase Interpolating Digital Power Amplifiers for TX Beamforming" Chips 1, no. 1: 30-50. https://doi.org/10.3390/chips1010004

APA StyleBai, Z., Yuan, W., Azam, A., & Walling, J. S. (2022). Multiphase Interpolating Digital Power Amplifiers for TX Beamforming. Chips, 1(1), 30-50. https://doi.org/10.3390/chips1010004