Verification of SoC Using Advanced Verification Methodology †

Abstract

:1. Introduction

Problem Statement

2. Materials and Methods

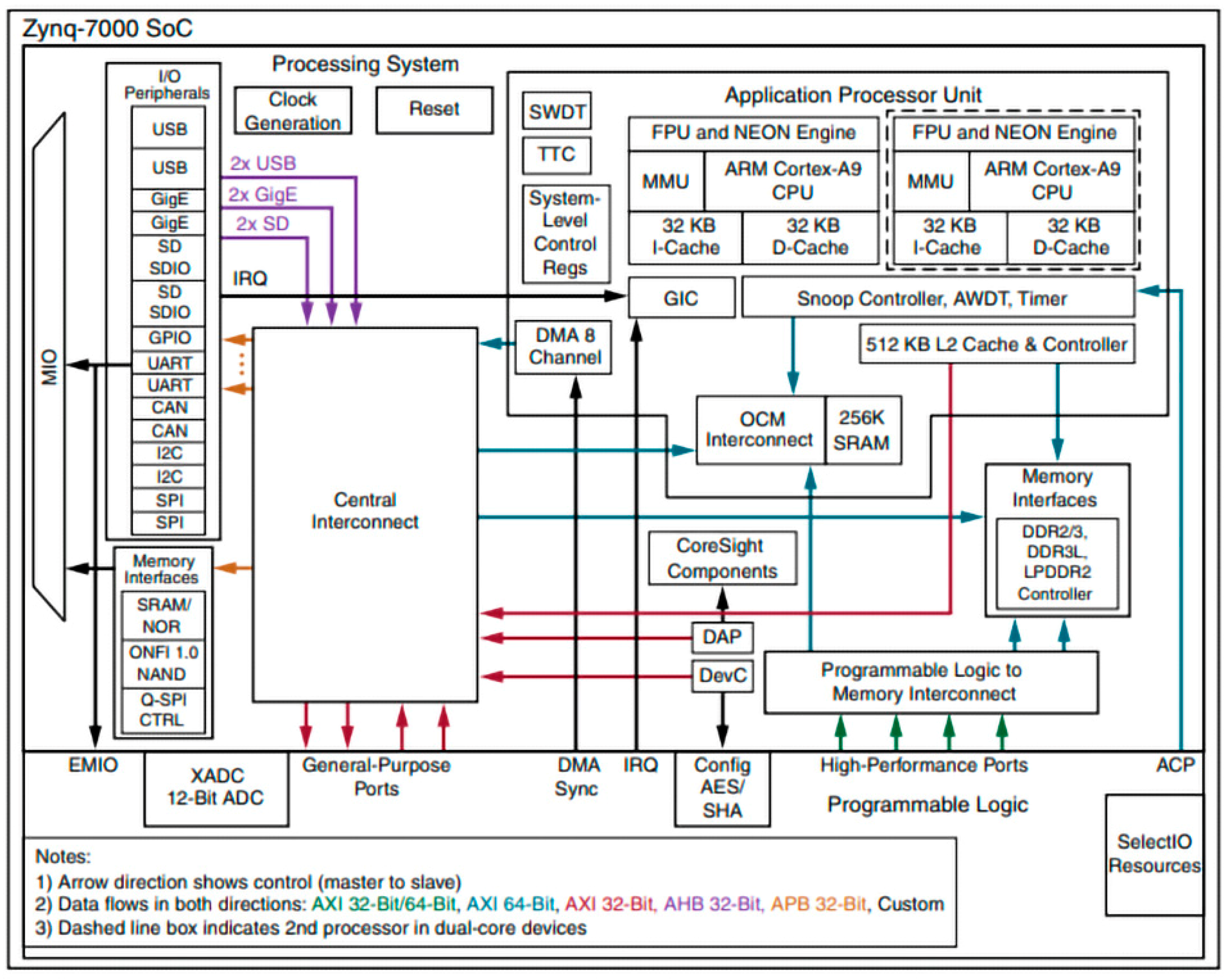

2.1. Architectural Overview

- Processing system;

- Programmable logic.

Processing System (PS)

- Application processor unit: The application processor unit offers high performance and standard-compliant capabilities. The runtime configurations allow the single processor or asymmetrical or symmetrical multiprocessing setups. It is a 32 Kb instruction set with a 32 Kb cache [12]. In addition, a sharable 512 Kb cache with parity is available. An accelerator coherency port from PL to PS, which is a 64 b AXI slave port, provides a connection between the processing system and programmable logic. APU also contains 256 Kb of on-chip SRAM which is a dual-ported memory. It is accessible to CPUs, PL, and central interconnects. There are four DMA (direct memory access) channels for PS to copy data from CPU memory to/from other system memories.

- Memory interfaces: The memory interface of PS includes multiple memory technologies. It consists of DDR controllers with 16 b and 32 b widths. This uses up to 73 dedicated pins of PS [12]. The DDR can be powered down as per the idle periods of PS. Transaction scheduling is performed for optimizing data bandwidth and latency. The efficiency of memory is increased by 90% by advanced re-ordering engines and increased by 80% with random read/write operations. Collision check monitors the memory for any write–read collisions and the write buffer is used in that case. The primary boot device can be a NAND controller or a parallel SRAM/NOR controller.

- I/O peripherals: The input–output peripherals are a collection of industry standard interfaces for communication with external systems. Programmable interrupt controllers on the GPIO are used for a status read of raw and masked interrupts. These interrupts are positive-edge, negative-edge, either--edge, high-level, or low-level sensitive. A USB 2.0 high-speed on-the-go (OTG) dual-role USB host controller and USB device controller operations are performed using a single hardware. This configuration uses MIO pins only. The USB host controller registers, and data structures are EHCI compatible [12]. It supports up to 12 endpoints.

- Interconnect: The SoC uses several interconnect technologies that are optimized for specific communication requirements of the functional blocks. The SoC interconnect is divided into two parts: one is based on the high-performance data path of AXI on the PS interconnect and the other is based on PS-PL interfaces. The PS interconnect consists of an OCM interconnect and a central interconnect. The OCM interconnect provides access to 256 Kb of memory from the central interconnect and PL. The CPU and ACP interfaces have the lowest latencies to OCM through the SCU. The central interconnect is a 64-bit interconnect. It connects the input–output peripherals and the DMA controller to the DDR memory controller, on-chip RAM, and the AXI-GP interfaces for PL logic. It also connects the local DMA units in Ethernet, USB, and SD/SDIO controllers to the central interconnect. It also connects the PS master to the IOP.

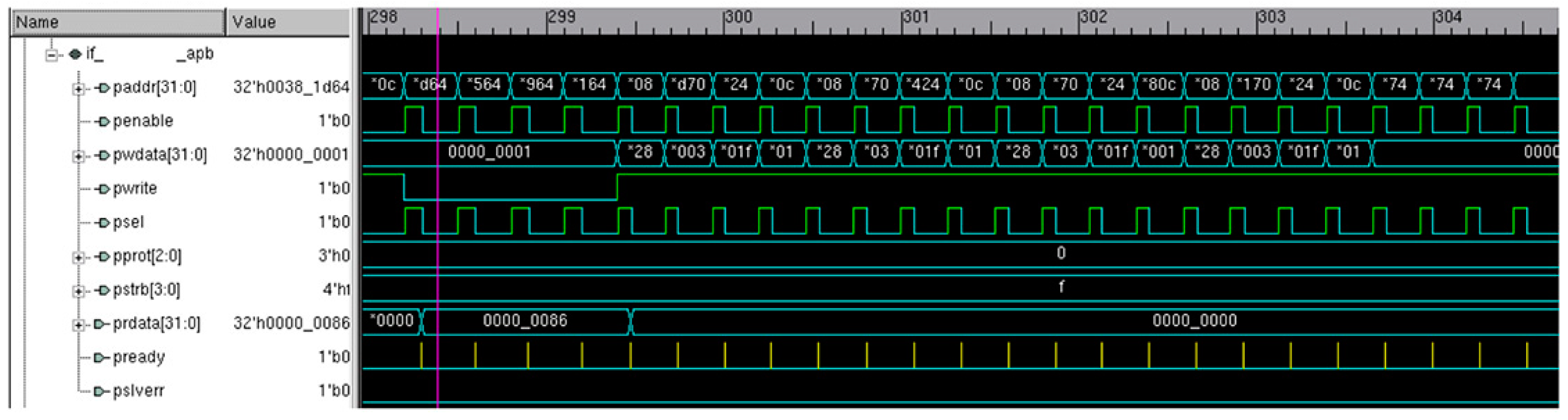

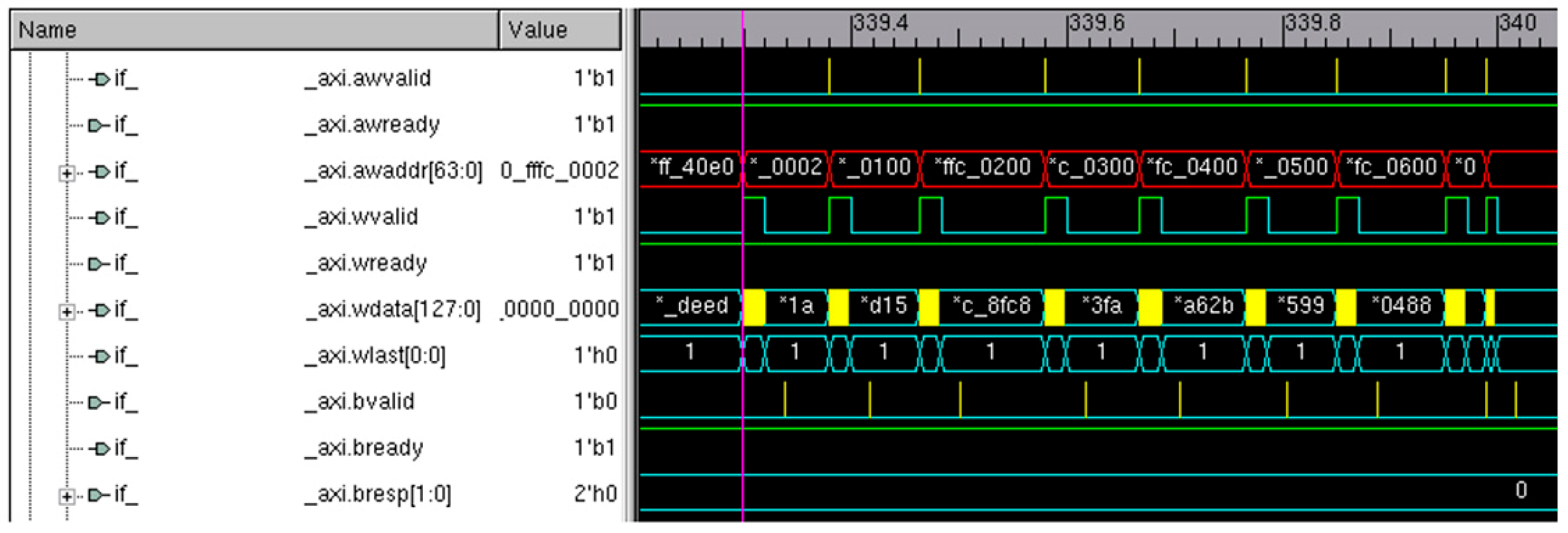

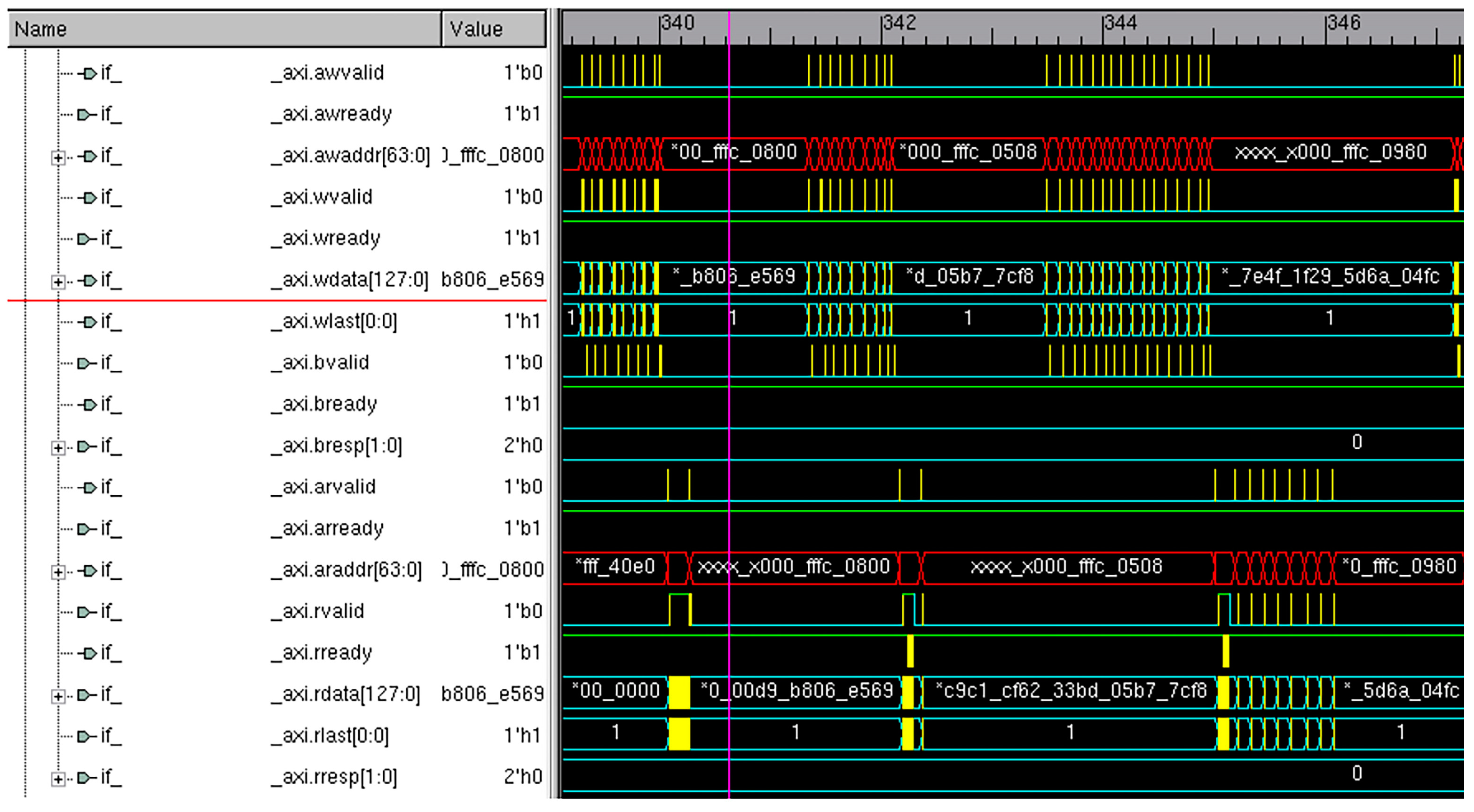

2.2. Connectivity Check in Interconnect

3. Results

- Green line: Transaction of 1.

- Blue line: Transaction of 0.

- Yellow line: Brust Transactions.

- Purple line: Marker.

- Red line: transaction of address is represented.

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Ghosh, P.; Srivastava, R. Case Study: SoC Performance Verification and Static Verification of RTL Parameters. In Proceedings of the 2019 20th International Workshop on Microprocessor/SoC Test, Security and Verification (MTV), Austin, TX, USA, 9–10 December 2019; pp. 65–72. [Google Scholar]

- Huang, X.; Liu, L.; Li, Y.; Liu, L.; Huang, X. FPGA Verification Methodology for SiSoC Based SoC Design. In Proceedings of the 2011 IEEE International Conference of Electron Devices and Solid-State Circuits, Tianjin, China, 17–18 November 2011. [Google Scholar]

- Bai, L.; Fan, X.; Zhang, M.; Sun, L. A VMM/FPGA Co-verification Method for “Longtium Stream” Processor. In Proceedings of the 2013 IEEE International Conference on Signal Processing, Communication and Computing (ICSPCC 2013), KunMing, China, 5–8 August 2013. [Google Scholar]

- Podivinsky, J.; Simkova, M.; Cekan, O.; Kotasek, Z. FPGA Prototyping and Accelerated Verification of ASIPs. In Proceedings of the 2015 IEEE 18th International Symposium on Design and Diagnostics of Electronic Circuits & Systems, Belgrade, Serbia, 22–24 April 2015; pp. 145–148. [Google Scholar]

- Noami, A.; Alahdal, A.; Kumar, B.P.; Chandrasekhar, P.; Safi, N. High Speed Data Transactions for Memory Controller Based on AXI4 Interface Protocol SoC. In Proceedings of the 2021 International Conference on Advances in Electrical, Computing, Communication and Sustainable Technologies (ICAECT), Bhilai, India, 19–20 February 2021. [Google Scholar]

- Seongyoung, S.; Moon, J.; Jun, S. FPGA-Accelerated Time Series Mining on Low-Power IoT Devices. In Proceedings of the 2020 IEEE 31st International Conference on Application-specific Systems, Architectures and Processors (ASAP), Manchester, UK, 6–8 July 2020. [Google Scholar]

- Noami, A.; Kumar, B.P.; Paidimarry, C.S. Power Optimization for Multi-Core Memory Controller Using Intelligent Clock Gating Technique. J. Electr. Electron. Eng. 2022, 15, 129–137. [Google Scholar]

- Gophane, K.C.; Bhaskar, P.C. FPGA Based Adaptive IoT Framework for Distinct Applications. In Proceedings of the 2018 Fourth International Conference on Computing Communication Control and Automation (ICCUBEA), Pune, India, 16–18 August 2018. [Google Scholar]

- Accounting For Very Deep Sub-Micron Effects in Silicon Models. Available online: https://www.eetimes.com/accounting-for-very-deep-sub-micron-effects-in-silicon-models/ (accessed on 15 February 2023).

- Tuomi, I. The lives and death of Moore’s Law. First Monday 2002, 7. [Google Scholar] [CrossRef]

- Noguera, J.; Badia, R.M. System-level power-performance trade-offs in task scheduling for dynamically reconfigurable architectures. In Proceedings of the 2003 International Conference on Compilers, Architecture and Synthesis for Embedded Systems, San Jose, CA, USA, 30 October–1 November 2003. [Google Scholar]

- Zynq-7000 SoC Data Sheet: Overview. Available online: https://docs.xilinx.com/v/u/en-US/ds190-Zynq-7000-Overview (accessed on 15 February 2023).

- Chris, S. System Verilog for Verification: A Guide to Learning the Testbench Language Features; Springer Science & Business Media: Berlin/Heidelberg, Germany, 2008. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pamula, P.; Gorthy, D.P.; Ngangbam, P.S.; Alagarsamy, A. Verification of SoC Using Advanced Verification Methodology. Eng. Proc. 2023, 34, 12. https://doi.org/10.3390/HMAM2-14160

Pamula P, Gorthy DP, Ngangbam PS, Alagarsamy A. Verification of SoC Using Advanced Verification Methodology. Engineering Proceedings. 2023; 34(1):12. https://doi.org/10.3390/HMAM2-14160

Chicago/Turabian StylePamula, Pranuti, Durga Prasad Gorthy, Phalguni Singh Ngangbam, and Aravindhan Alagarsamy. 2023. "Verification of SoC Using Advanced Verification Methodology" Engineering Proceedings 34, no. 1: 12. https://doi.org/10.3390/HMAM2-14160

APA StylePamula, P., Gorthy, D. P., Ngangbam, P. S., & Alagarsamy, A. (2023). Verification of SoC Using Advanced Verification Methodology. Engineering Proceedings, 34(1), 12. https://doi.org/10.3390/HMAM2-14160