A Review of Techniques to Enhance an Amplifier’s Performance Using Resistive Local Common Mode Feedback

Abstract

1. Introduction

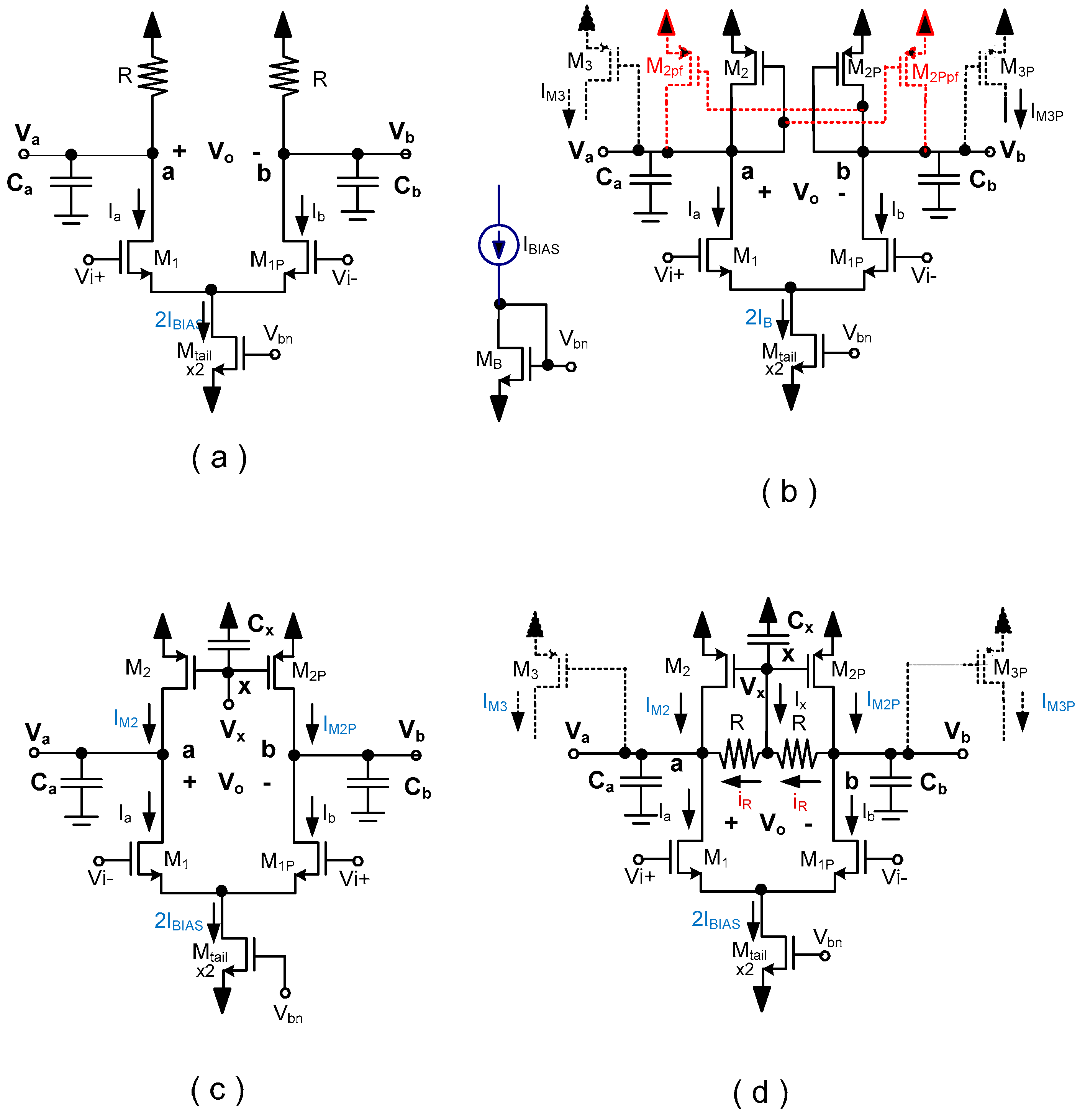

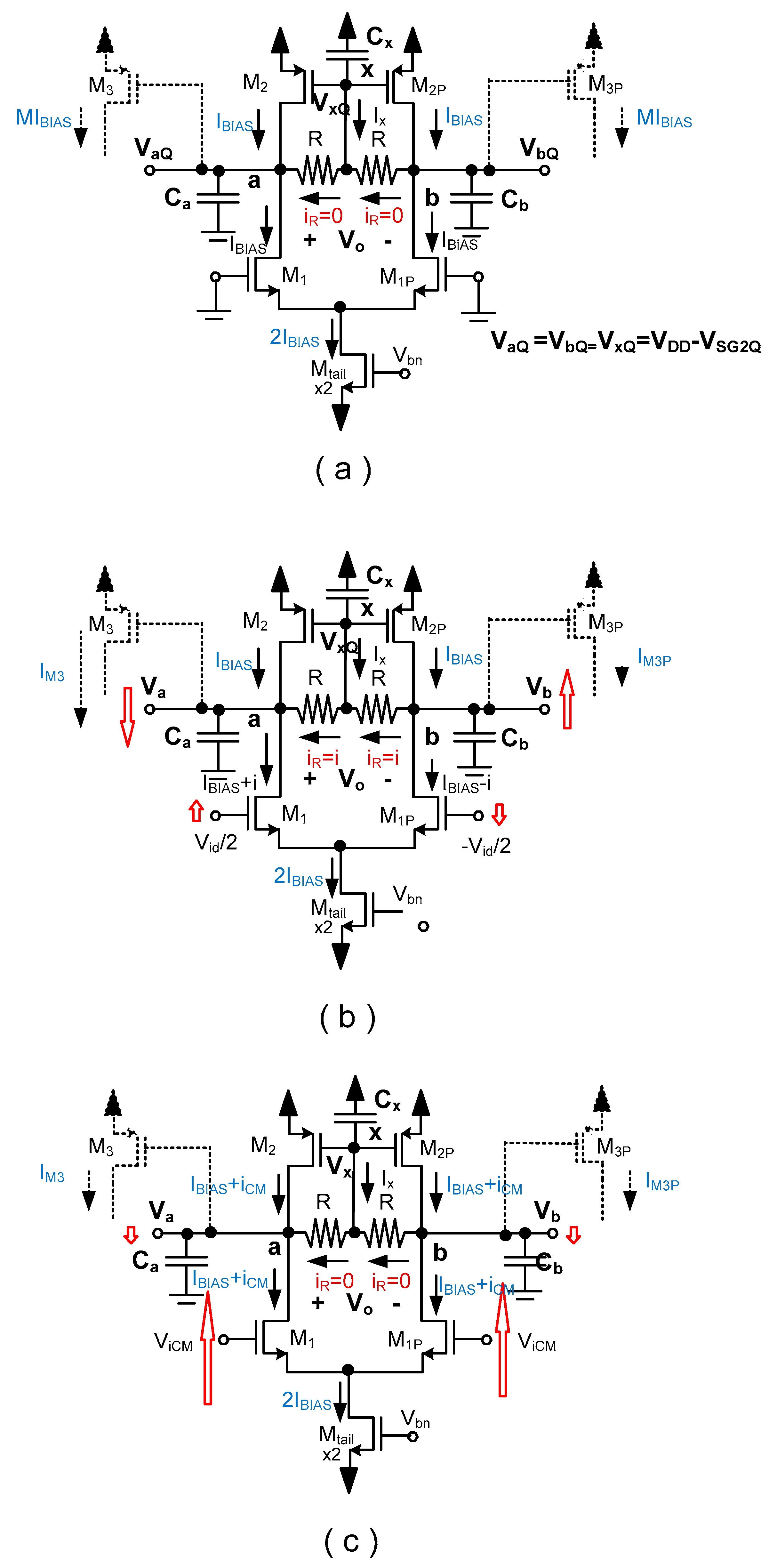

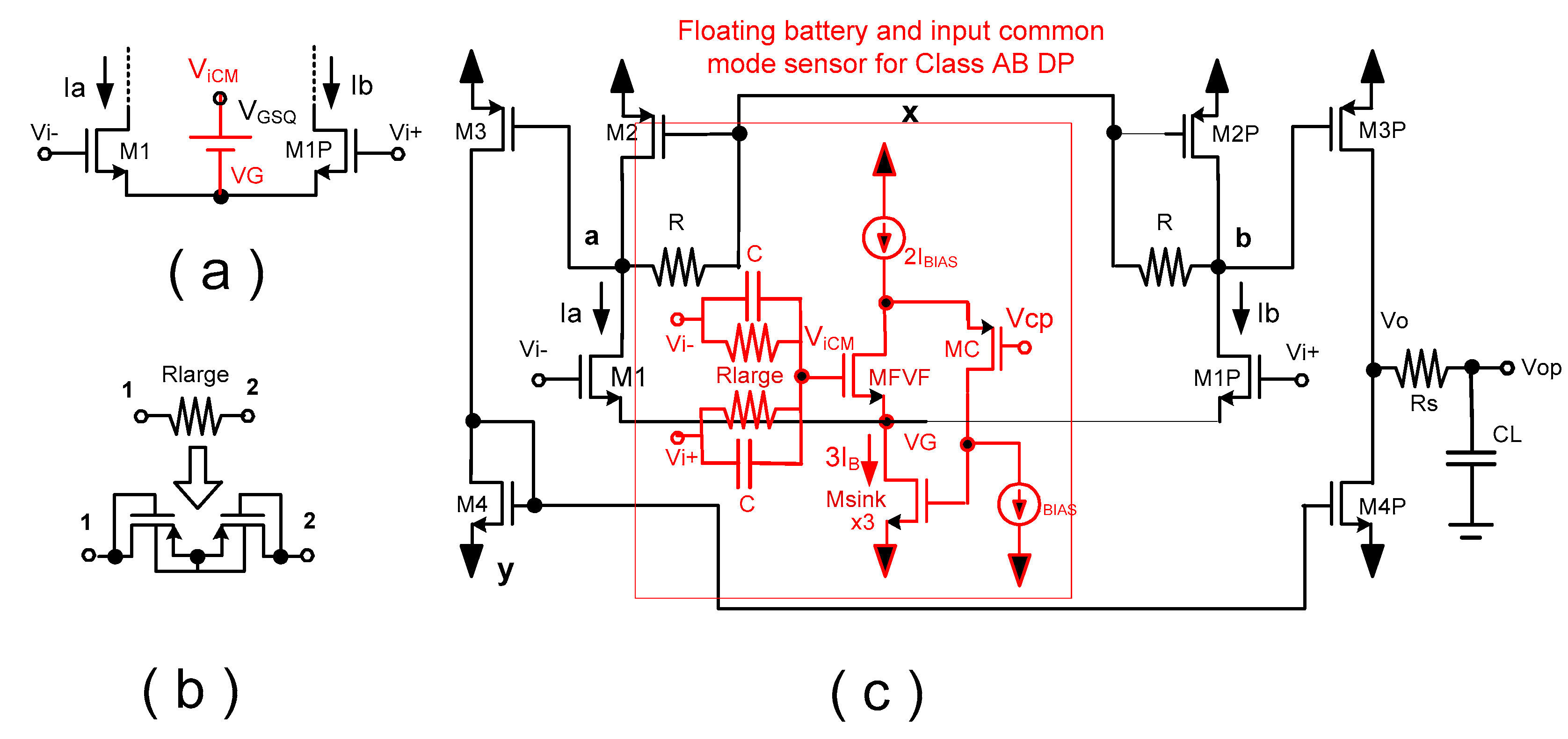

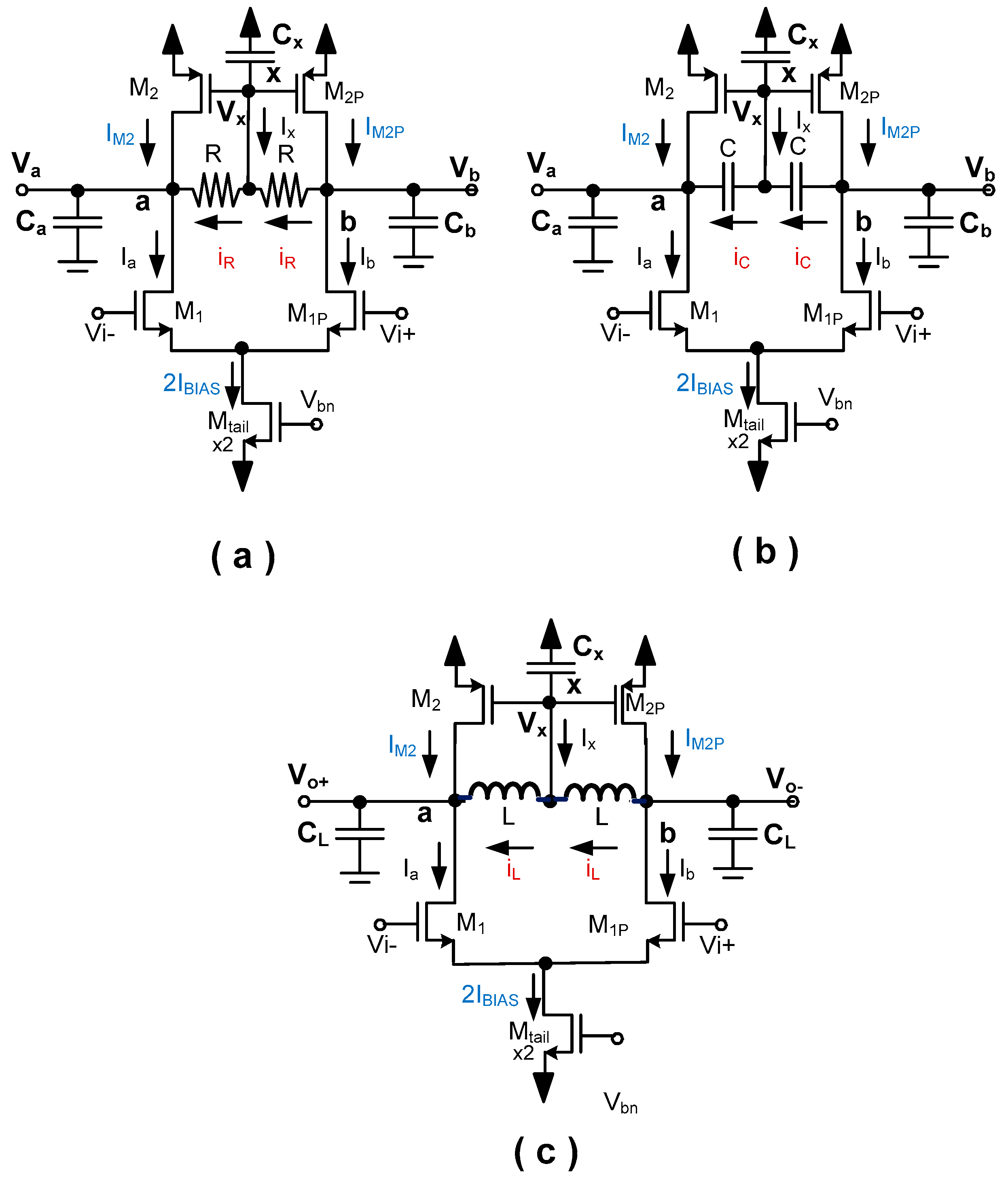

2. Differential Pair with Resistive Local Common Mode Feedback

2.1. Operation under Quiescent Conditions (Vi+ = Vi− = 0)

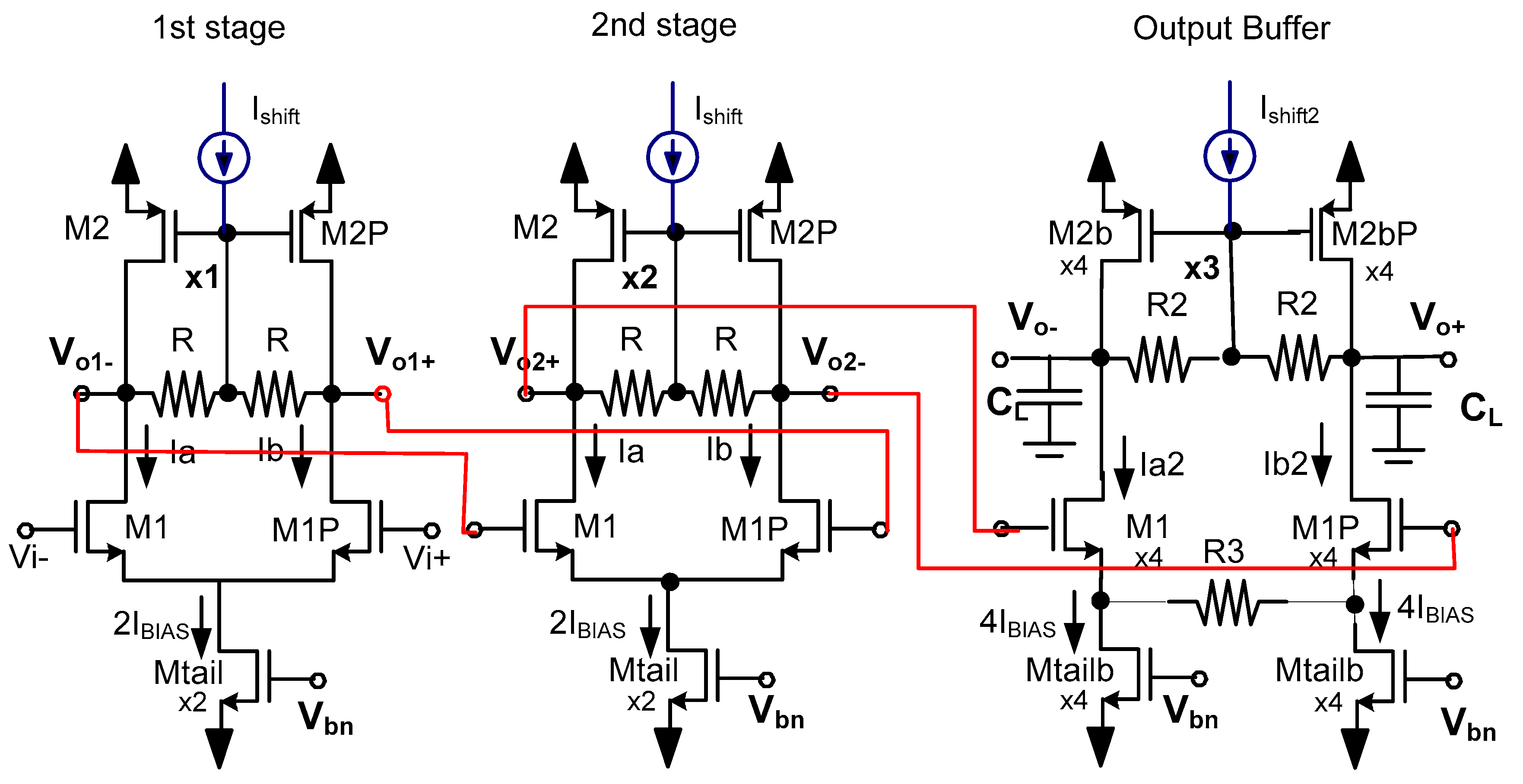

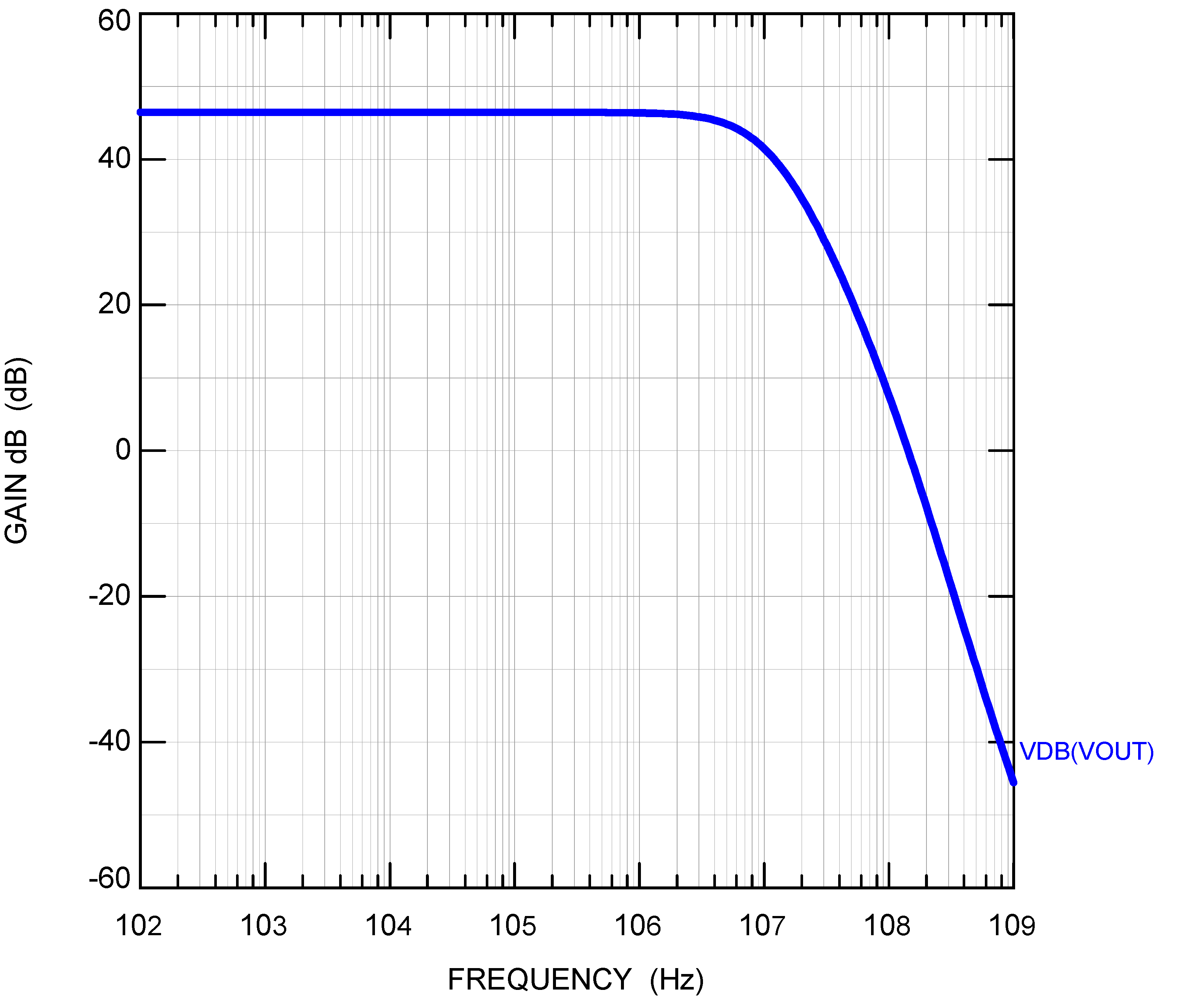

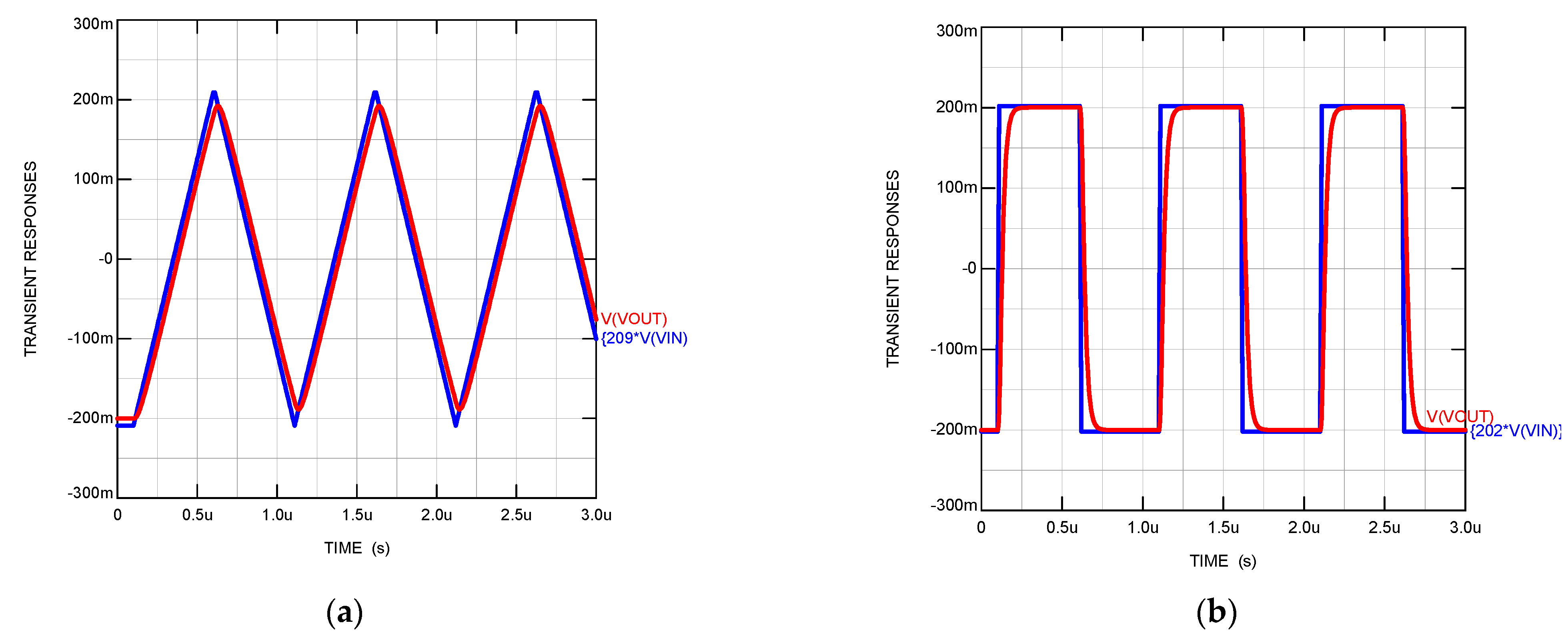

2.2. Differential Operation

2.3. Common Mode Operation

2.4. Some Remarks on the Operation of the Circuit of Figure 1d

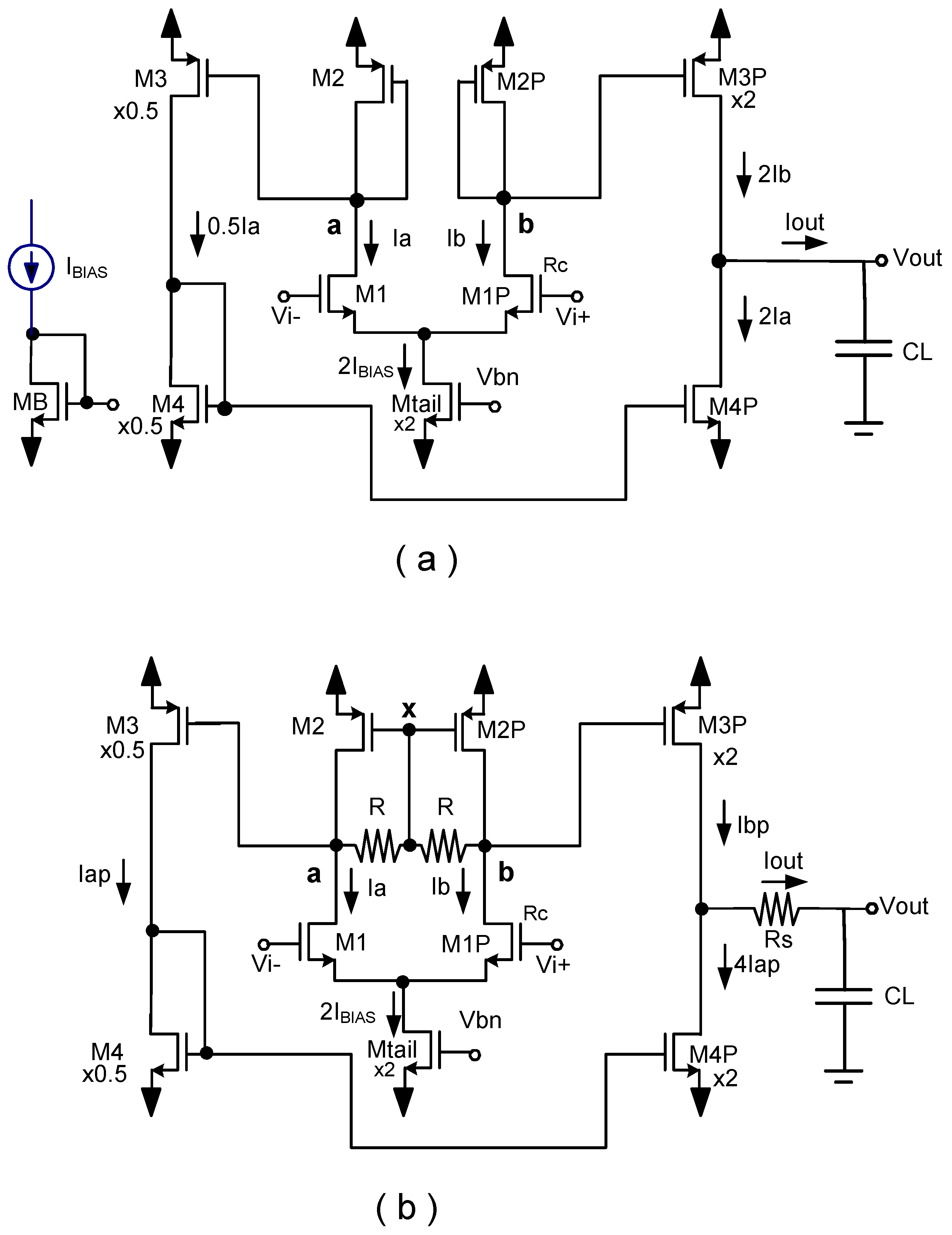

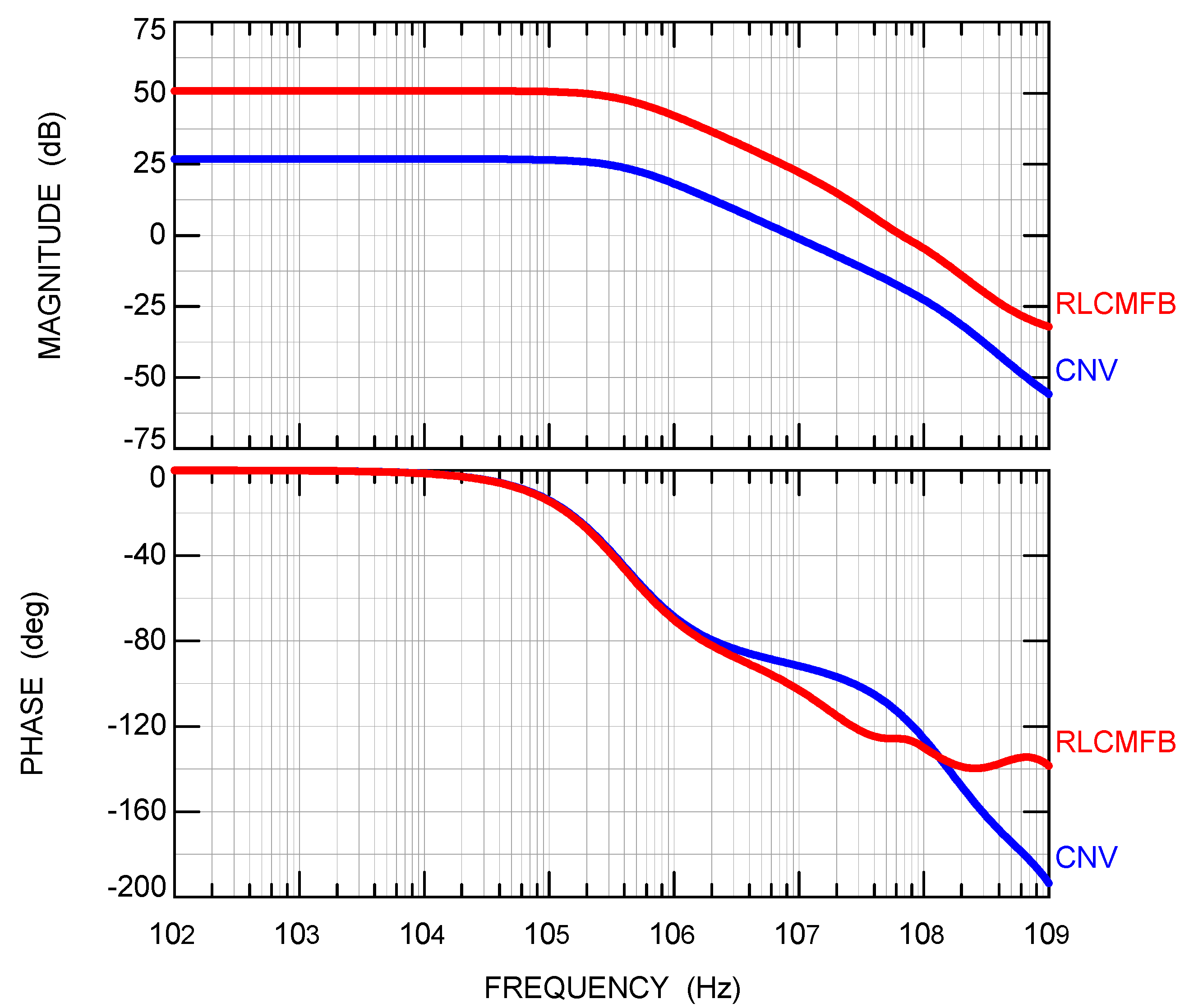

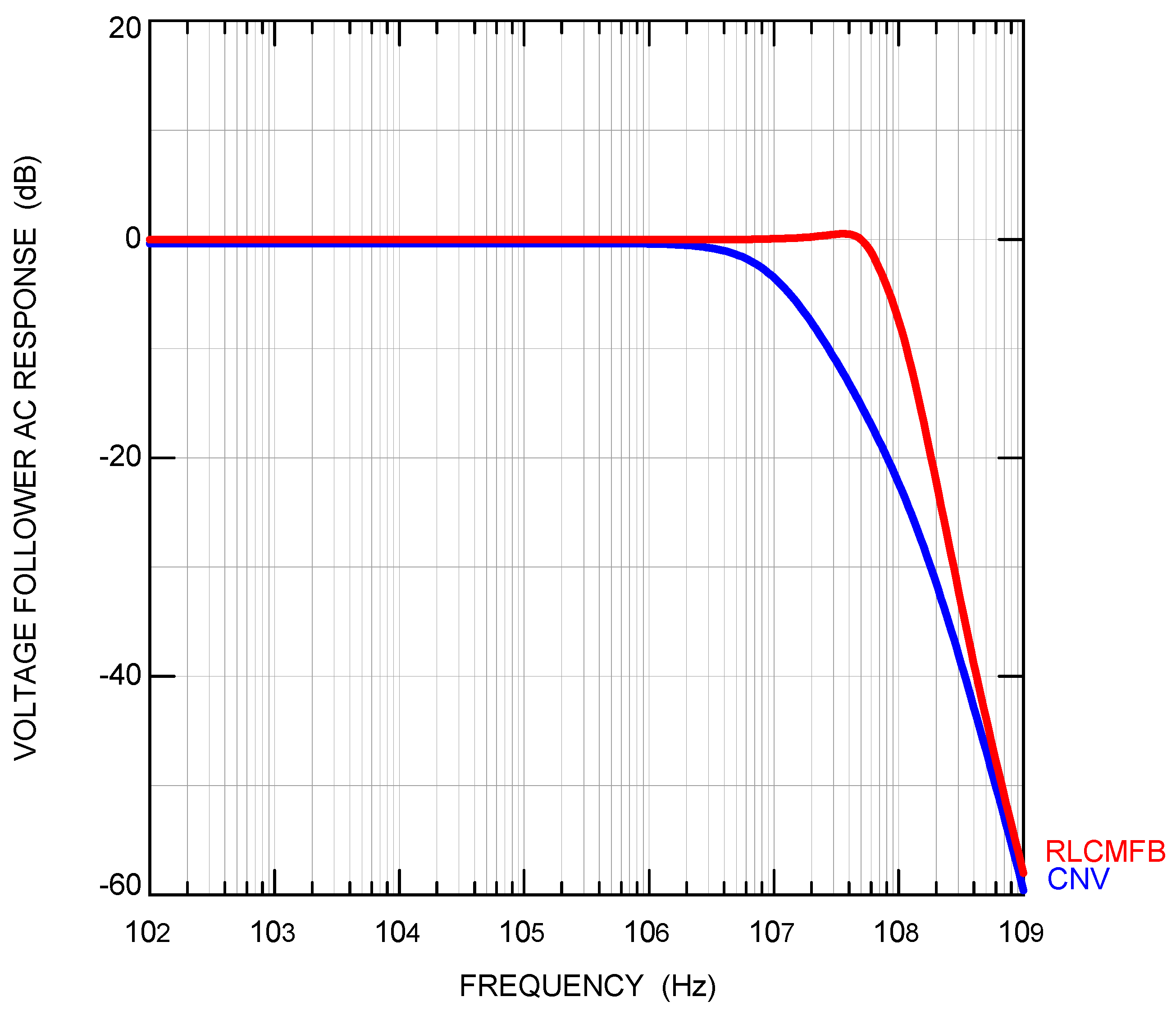

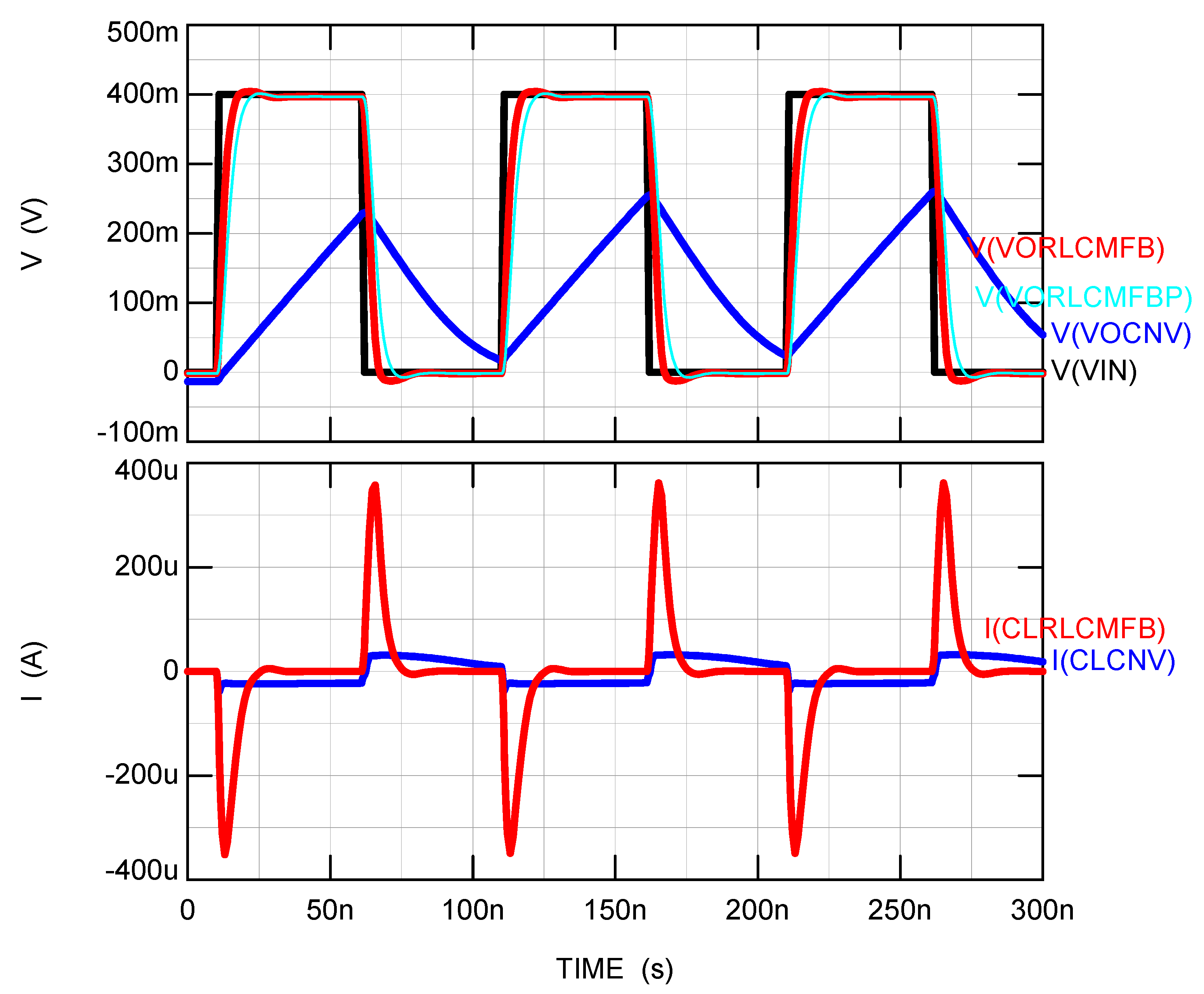

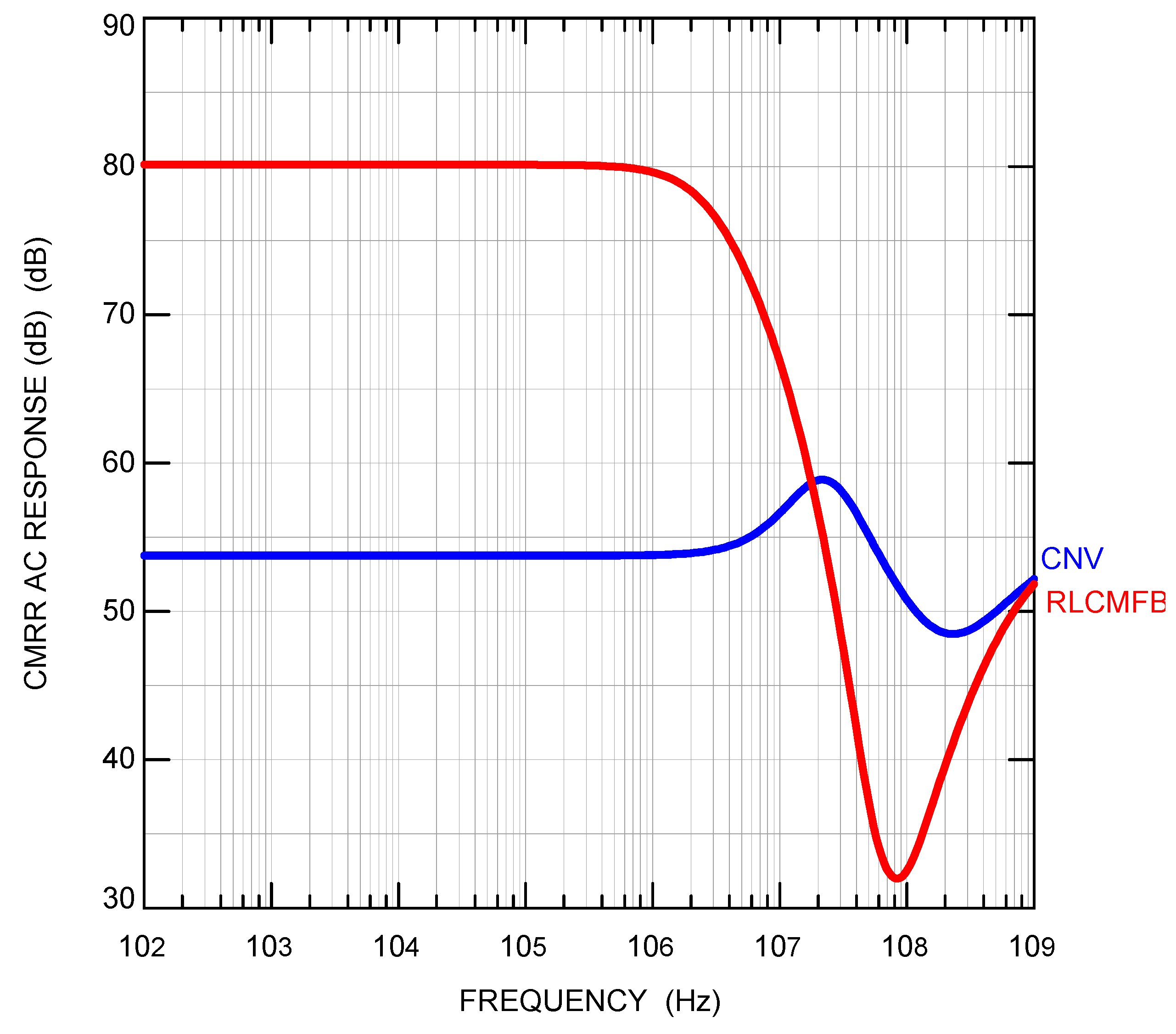

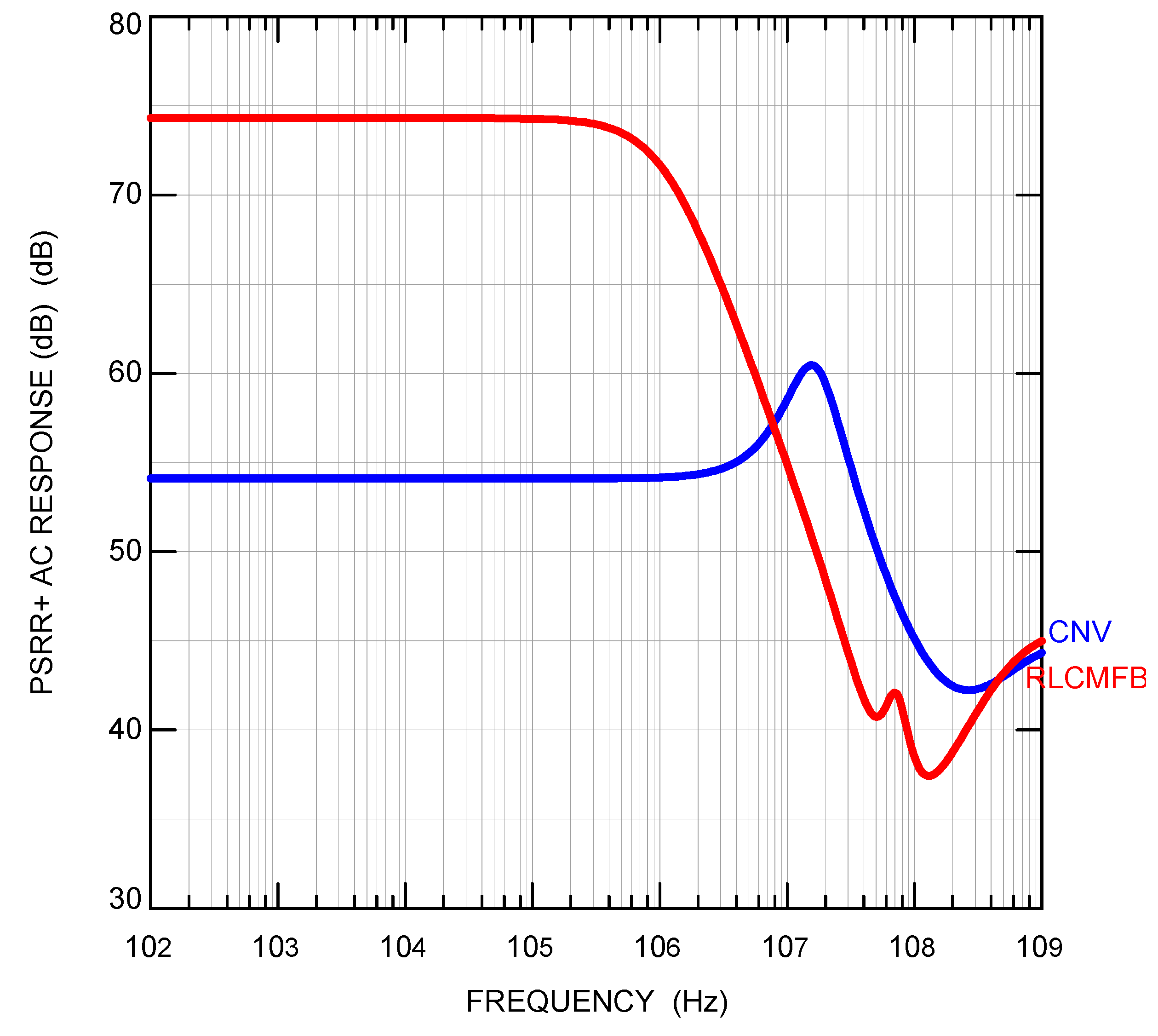

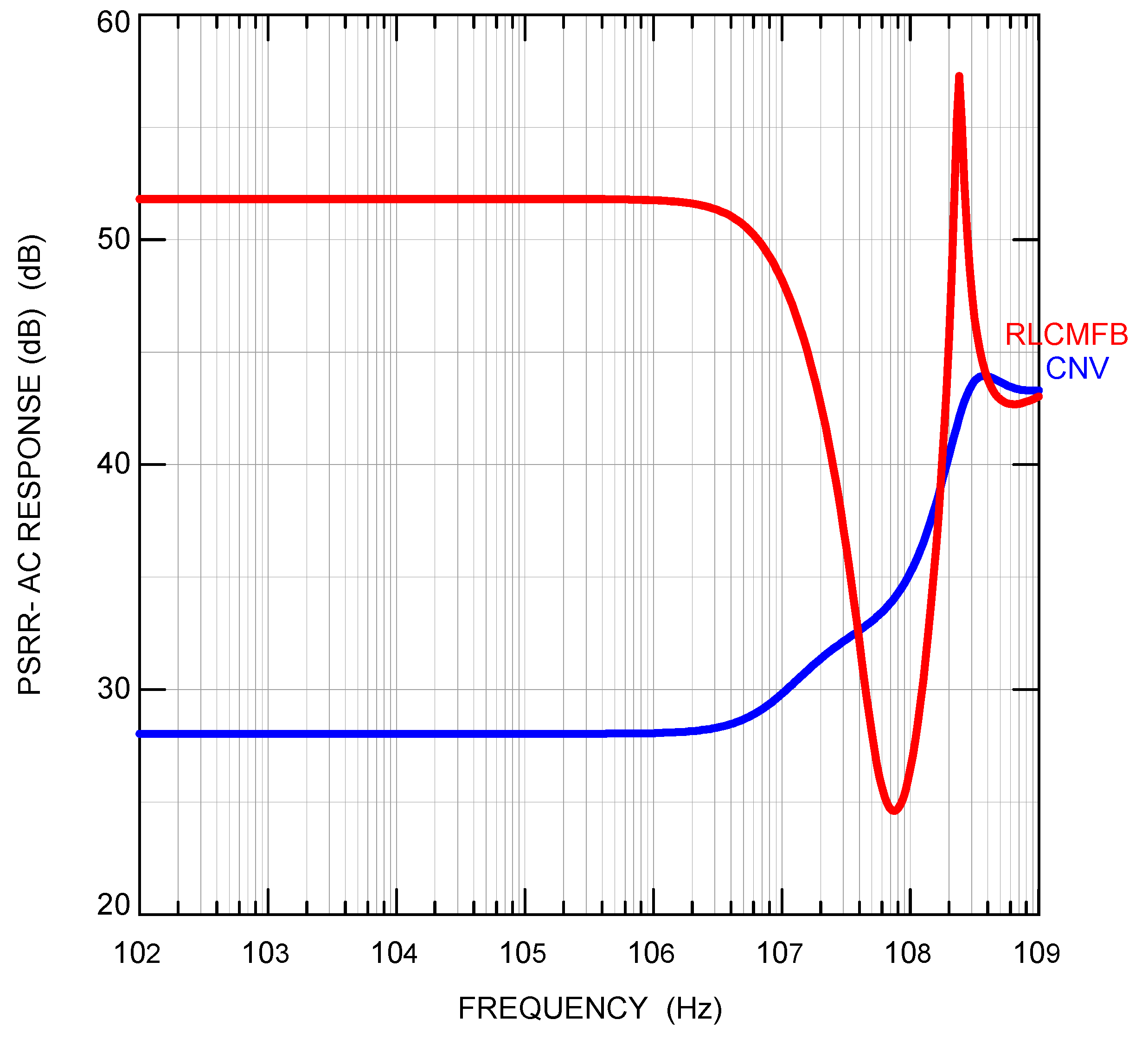

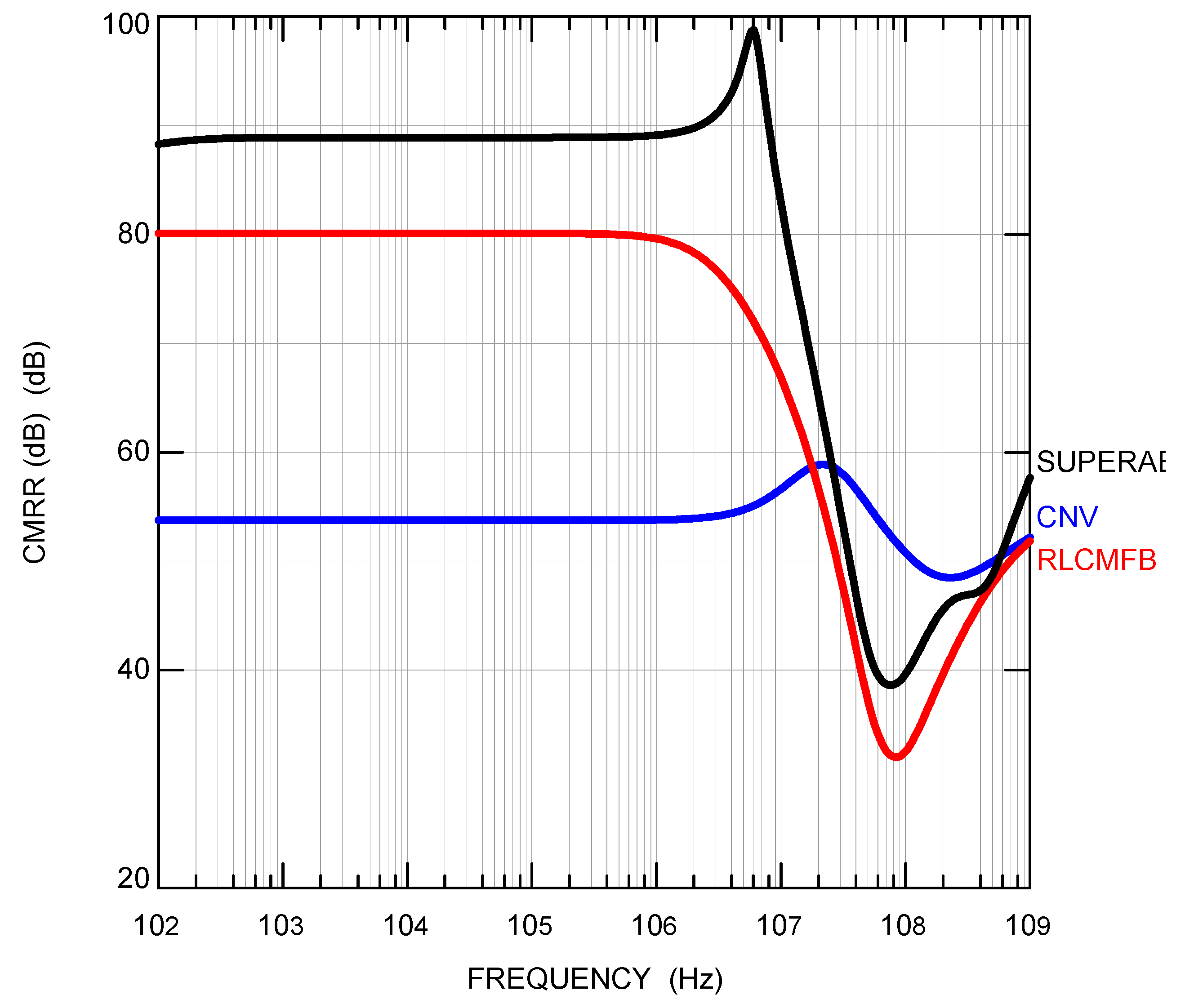

3. Comparison of Non-Cascoded Conventional and Resistive Local Common Mode Feedback OTAs

Summary

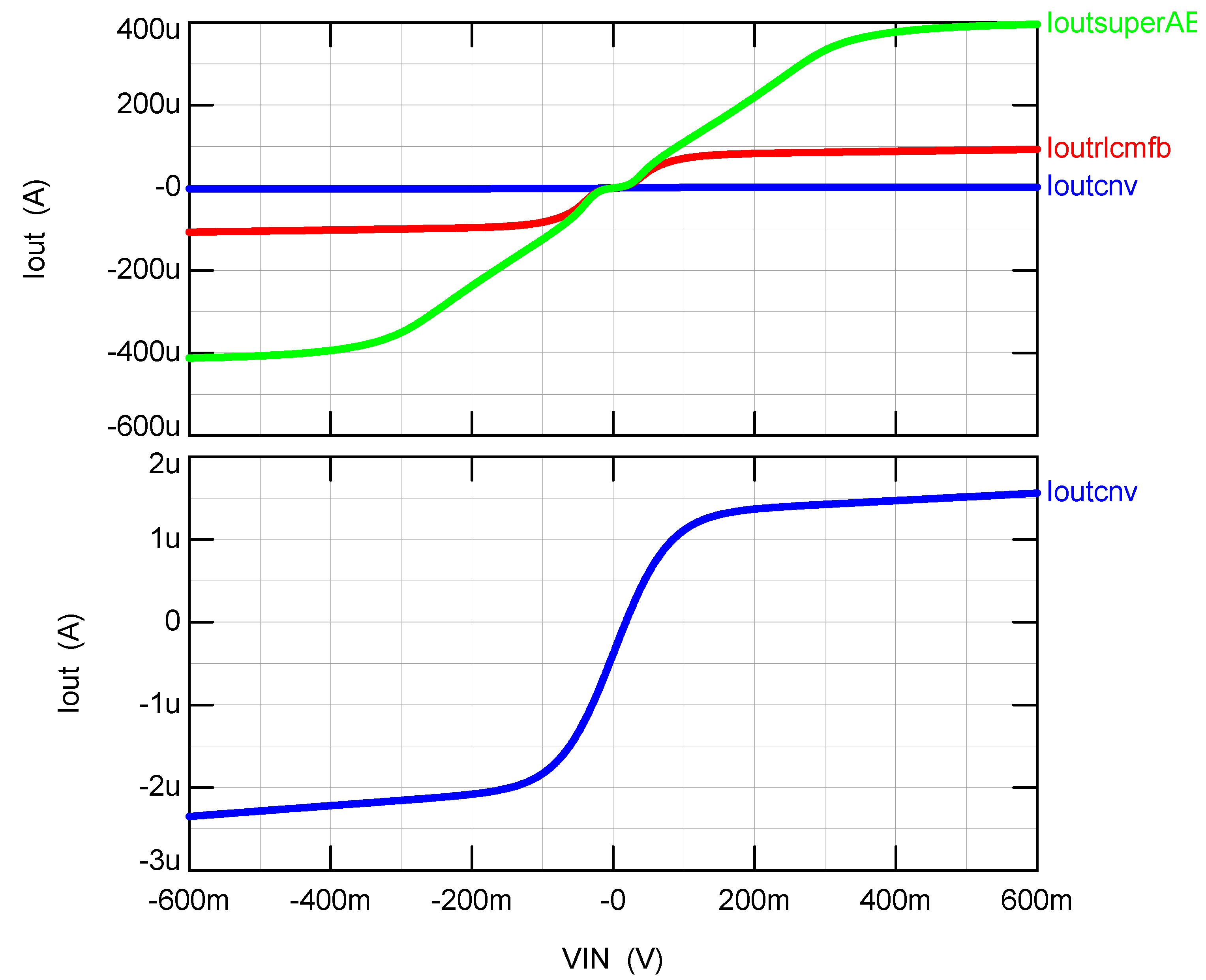

4. Super Class AB OTAs

5. Feedforward Amplifiers

6. Other Applications

7. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Ramirez-Angulo, J.; Holmes, M. Simple technique using Local CMFB to enhance Slew Rate and bandwidth of one-Stage CMOS op-amps. Electron. Lett. 2002, 38, 1409–1411. [Google Scholar] [CrossRef]

- Ragheb, A.N.; Kim, H. Ultra-low power OTA based on bias recycling and subthreshold operation with phase margin enhancement. Microelectron. J. 2017, 60, 94–101. [Google Scholar] [CrossRef]

- Feizbakhsh, S.V.; Yosefi, G. An enhanced fast slew rate recycling folded cascode Op-Amp with general improvement in 180 nm CMOS process. AEU-Int. J. Electron. Commun. 2019, 101, 200–217. [Google Scholar] [CrossRef]

- Kuo, P.-Y.; Tsai, S.-D. An Enhanced Scheme of Multi-Stage Amplifier with High-Speed High-Gain Blocks and Recycling Frequency Cascode Circuitry to Improve Gain-Bandwidth and Slew Rate. IEEE Access 2019, 7, 130820–130829. [Google Scholar] [CrossRef]

- Kuo, P.-Y.; Liao, H.-W.; Peng, J.-S. An Improved Recycling Folded-Cascode Amplifier with High Unity-Gain Frequency. In Proceedings of the 2020 IEEE International Conference on Consumer Electronics-Taiwan (ICCE-Taiwan), Taoyuan, Taiwan, 28–30 September 2020; pp. 1–2. [Google Scholar]

- Kim, J.; Song, S.; Roh, J. A High Slew-Rate Enhancement Class-AB Operational Transconductance Amplifier (OTA) for Switched-Capacitor (SC) Applications. IEEE Access 2020, 8, 226167–226175. [Google Scholar] [CrossRef]

- Nandi, G.; Yadav, S.; Kondekar, P. A Fast Settling, High Slew Rate CMOS Recycling Folded Cascode Operational Transconductance Amplifier (OTA) for High Speed Applications. In Proceedings of the 2021 12th International Conference on Computing Communication and Networking Technologies (ICCCNT), Kharagpur, India, 6–8 July 2021; pp. 1–6. [Google Scholar]

- Harrison, J.; Weste, N. 350 MHz opamp-RC filter in 0.18 µm CMOS. Electron. Lett. 2002, 38, 259–260. [Google Scholar] [CrossRef]

- Harrison, J.; Weste, N. A 500 MHz CMOS anti-alias filter using feed-forward op-amps with local common-mode feedback. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13 February 2003; pp. 132–133. [Google Scholar]

- Baswa, S.; Lopez-Martin, A.J.; Ramirez-Angulo, J.; Carvajal, R.G. Low-voltage Micropower Super Class AB CMOS OTA. Electron. Lett. 2004, 40, 216–217. [Google Scholar] [CrossRef]

- Schlogl, F.; Zimmermann, H. 1.5 GHz OPAMP in 120 nm digital CMOS. In Proceedings of the 30th European Solid-State Circuits Conference, Leuven, Belgium, 21–23 September 2004; pp. 239–242. [Google Scholar]

- Chawla, R.; Serrano, G.; Allen, D.J.; Pereira, A.W.; Hasler, P.E. Fully differential floating-gate programmable OTAs with novel common-mode feedback. In Proceedings of the IEEE International Symposium on Circuits and Systems, Vancouver, CA, USA, pp. I-817–I-820., 23–26 May 2004. [Google Scholar]

- Lopez-Martin, A.J.; Baswa, S.; Ramirez-Angulo, J.; Carvajal, R.G. Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE J. Solid-State Circuits 2005, 40, 1068–1077. [Google Scholar] [CrossRef]

- Baswa, S.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G.; Bikumandla, M. Rail-to-Rail super Class AB CMOS Operational Amplifiers. Electron. Lett. 2005, 41, 1–2. [Google Scholar] [CrossRef]

- Chawla, R.; Serrano, G.; Allen, D.; Hasler, P. Programmable floating-gate second-order sections for Gm-C filter applications. In Proceedings of the 48th Midwest Symposium on Circuits and Systems, Cincinnati, OH, USA, 21–23 August 2005; pp. 1649–1652. [Google Scholar]

- Chawla, R.; Adil, F.; Serrano, G.; Hasler, P.E. Programmable Gm–C Filters Using Floating-Gate Operational Transconductance Amplifiers. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 481–491. [Google Scholar] [CrossRef]

- Motlak, H.J.; Ahmad, S.N. A Novel Design Technique of One Stage CMOS OTA For High Frequency Applications. Frequenz 2007, 61, 182–188. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Lujan-Martinez, C.; Rubia-Marcos, C.; Carvajal, R.G.; Lopez-Martin, A.J. Rail to Rail Fully Differential Sample and Hold Based on Clocked Differential Difference Amplifier Using Resistive Local Common Mode Feedback. IET Electron. Lett. 2008, 44, 656–658. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Carvajal, R.G.; Lopez-Martin, A.J. High slew rate two stage A/AB and AB/AB op-amps with phase lead compensation at output node and local common mode feedback. In Proceedings of the IEEE International Symposium on Circuits and Systems, Seattle DC, USA, 21–23 May 2008; pp. 288–291. [Google Scholar]

- Grasso, A.D.; Monsurrò, P.; Pennisi, S.; Scotti, G.; Trifiletti, A. Analysis and Implementation of a Minimum-Supply Body-Biased CMOS Differential Amplifier Cell. IEEE Trans. Very Large Scale Integr. (Vlsi) Syst. 2009, 17, 172–180. [Google Scholar] [CrossRef]

- Mehra, A.; Gupta, A.; Patil, S.; Mehra, A.; Sahoo, S.K. A Novel Dynamic Current Boosting Technique for Enhancement of Settling Time and Elimination of Slewing of CMOS Amplifiers. In Proceedings of the 2009 International Conference on Advances in Recent Technologies in Communication and Computing, Kottayam, India, 27–28 October2009; pp. 115–117. [Google Scholar]

- Ramirez-Angulo, J.; Nargis, A.; Carvajal, R.G.; Lopez-Martin, A. CMOS Operational Amplifiers with Continuous-Time Capacitive Common Mode Feedback. In Proceedings of the IEEE ISCAS 2010, Paris, France, 29 May–2 June 2010; pp. 1280–1283. [Google Scholar]

- Nargis, A. CMOS Operational Amplifiers with continuous time Capacitive Common Mode Feedback. Master’s Thesis, New Mexico State University, Las Cruces, NM, USA, 2010. [Google Scholar]

- Heer, L.F.; Frey, U.; Bakkum, D.J.; Hierlemann, A. Compact Voltage and Current Stimulation Buffer for High-Density Microelectrode Arrays. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 372–378. [Google Scholar]

- Chen, Y.; He, X.-y.; Pun, K.-p. A 0.5V amplifier with adaptive CMFB compensation for a 2-1 cascade CT Delta Sigma modulator. In Proceedings of the 2010 IEEE International Conference of Electron Devices and Solid-State Circuits (EDSSC), Hong Kong, China, 15–17 December 2010; pp. 1–4. [Google Scholar]

- Huang, B.; Xu, L.; Chen, D. Slew rate enhancement via excessive transient feedback. IET Electron. Lett. 2013, 49, 930–932. [Google Scholar] [CrossRef]

- Fathipour, R.; Saberkari, A.; Martinez, H.; Alarcón, E. High slew rate current mode transconductance error amplifier for low quiescent current output-capacitorless CMOS LDO regulator. Integr. VLSI J. 2014, 47, 204–212. [Google Scholar] [CrossRef]

- Perez-Nicoli, P.; Veirano, F.; Lisboa, P.C.; Silveira, F. Low-power operational transconductance amplifier with slew-rate enhancement based on non-linear current mirror. J. Analog. Integr. Circuits Signal Process. 2016, 89, 521–529. [Google Scholar] [CrossRef]

- Cabrera-Bernal, E.; Pennisi, S.; Grasso, A.D.; Torralba, A.; Carvajal, R.G. 0.7-V Three-Stage Class-AB CMOS Operational Transconductance Amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1807–1815. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.J.; Ramirez-Angulo, J. Improved common-mode feedback based on LCMFB techniques. In Proceedings of the 2017 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Taormina, Italy, 12–15 June 2017; pp. 277–280. [Google Scholar]

- Algueta-Miguel, J.M.; Lopez-Martin, A.; Pilar Garde, M.; De La Cruz, C.A.; Ramirez-Angulo, J. ±0.5 V 15 μW Recycling Folded Cascode Amplifier with 34,767 MHzpF/mA. IEEE Solid State Circuits Lett. 2018, 1, 170–173. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.; Carvajal, R.G.; Ramírez-Angulo, J. Super Class-AB Recycling Folded Cascode OTA. IEEE J. Solid-State Circuits 2018, 53, 2614–2623. [Google Scholar] [CrossRef]

- Pourashraf, S.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; González-Carvajal, R. A Highly Efficient Composite Class-AB-AB Miller Op-Amp With High Gain and Stable From 15 pF Up To Very Large Capacitive Loads. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 2061–2072. [Google Scholar] [CrossRef]

- Chen, Y.; Wang, X.; Zhang, Y.; Pun, K.P. A 0.4-V 0.2 pJ/step 90-dB SNDR 20-kHz CT delta-sigma modulator using class-AB amplifier with a novel local common-mode feedback. IEICE Electron. Express 2019, 16, 20190170. [Google Scholar] [CrossRef]

- Paul, A.; Ramírez-Angulo, J.; López-Martín, A.J.; Carvajal, R.G.; Rocha-Pérez, J.M. Pseudo-Three-Stage Miller Op-Amp with Enhanced Small-Signal and Large-Signal Performance. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 2246–2259. [Google Scholar] [CrossRef]

- Rico-Aniles, H.D.; Ramírez-Angulo, J.; Rocha-Pérez, J.M.; López-Martín, A.J.; Carvajal, R.G. Low-Voltage 0.81mW, 1-32 CMOS VGA with 5% Bandwidth Variations and -38dB DC Rejection. IEEE Access 2020, 8, 106310–106321. [Google Scholar] [CrossRef]

- Yen, A.; Blalock, B.J. A High Slew Rate, Low Power, Compact Operational Amplifier Based on the Super-Class AB Recycling Folded Cascode. In Proceedings of the IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), Springfield, MA, USA, 9–12 August 2020; pp. 9–12. [Google Scholar]

- Renteria-Pinon, M.; Ramirez-Angulo, J.; Diaz-Sanchez, A. Simple Scheme for the Implementation of Low Voltage Fully Differential Amplifiers without Output Common-Mode Feedback Network. MDPI J. Low Power Electron. Appl. 2020, 10, 34. [Google Scholar] [CrossRef]

- Paul, A.; Ramírez-Angulo, J.; Díaz-Sánchez, A.; López-Martín, A.J.; Carvajal, R.G.; Li, F.X. Super-Gain-Boosted AB-AB Fully Differential Miller Op-Amp with 156 dB Open-loop Gain and 174MV/V MHZ pF/µW Figure of Merit in 130 nm CMOS Technology. IEEE Access 2021, 9, 57603–57617. [Google Scholar] [CrossRef]

- Paul, A.; Renteria-Pinon, M.; Ramirez-Angulo, J.; Bolaños-Pérez, R.; Vázquez-Leal, H.; Huerta-Chua, J.; Diaz-Sánchez, A. Implementation of Power-Efficient Class AB Miller Amplifiers Using Resistive Local Common-Mode Feedback. J. Low Power Electron. Appl. 2021, 11, 31. [Google Scholar] [CrossRef]

- Beloso-Legarra, J.; de la Cruz-Blas, C.A.; Lopez-Martin, A.J.; Ramirez-Angulo, J. Gain-Boosted Super Class AB OTAs Based on Nested Local Feedback. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 3562–3573. [Google Scholar] [CrossRef]

- Sagar, G.N.; Kumar, B.A.; Reddy, G.B.S. Low-Power High-Gain Op-Amp With Cascoded Current Mirror Loads. In Proceedings of the 2021 5th International Conference on Electronics, Communication and Aerospace Technology (ICECA), Coimbatore, Tamil Nadu, India, 2–4 December 2021; pp. 179–186. [Google Scholar]

- Sagar, G.N.; Kumar, B.A.; Reddy, G.B.S. High Gain and Stable Class AB-AB Miller Op-Amp for Large Capacitive Loads Ranging From 15pF. In Proceedings of the 2021 5th International Conference on Trends in Electronics and Informatics (ICOEI), Tirunelveli, Tamilnadu, India, 3–5 June 2021; pp. 19–25. [Google Scholar]

- Paul, A.; Ramirez-Angulo, J.; Huerta-Chua, J.; Vazquez-Leal, H.; Diaz Sanchez, A. Fully Differential Miller Op-amp with Enhanced Large and Small Signal Figures of Merit. J. Low Power Electron. Appl. 2022, 12, 9. [Google Scholar] [CrossRef]

- Gangeni, M.; Ramirez-Angulo, J.; Vazquez-Leal, H.; Huerta-Chua, J.; Lopez-Martin, A.J.; Carvajal, R.G. ±0.3V Bulk-Driven Fully Differential Buffer with High Figures of Merit. J. Low Power Electron. Appl. 2022, 12, 35. [Google Scholar] [CrossRef]

- Yu, Z.; Xiao, Z.; Liyuan, D. A Local Positive Feedback Loop-Reused Technique for Enhancing Performance of Folded Cascode Amplifier. In Proceedings of the 2022 IEEE 4th International Conference on Circuits and Systems (ICCS), Chengdu, China, 23–26 September 2022; pp. 164–167. [Google Scholar]

- Ramirez-Angulo, J.; Diaz-Armendariz, A.; Molinar-Solis, J.E.; Diaz-Sanchez, A.; Huerta-Chua, J. Simple Technique to essentially improve the performance of one stage op-amps in deep submicrometer CMOS technology. J. Low Power Electron. Appl. 2023, 13, 4. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Gonzalez-Carvajal, R.; Torralba, A.; Nieva, C. A new Class AB differential Input stage for implementation of low voltage high slew rate op-amps and linear transconductors. In Proceedings of the IEEE International Symposium on Circuits an Systems, Sidney, Australia, 6–9 May 2001; pp. I-671–I-674. [Google Scholar]

- Gupta, S.; Padilla, I.; Ramirez-Angulo, J.; Torralba, A.; Jimenez, M. Comparison of Conventional and New Flipped Voltage Follower Structures. In Proceedings of the 2005 IEEE Midwest Symposium on Circuits and Systems, Cincinnati, OH, USA, 21–23 August 2005; pp. 1151–1154. [Google Scholar]

- Ramirez-Angulo, J.; Urquidi, C.; Carvajal, R.G.; Lopez-Martin, A.J. A new Family of Very Low-Voltage Analog Circuits Based on Quasi Floating Gate Transistors. IEEE Trans. Circuits Syst. II 2003, 50, 214–220. [Google Scholar] [CrossRef]

- Pourashraf, S.; Ramírez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G. Op-Amp Approaches for Bandpass VGAs with Constant Bandwidth. IEEE TCAS-II 2018, 65, 1144–1148. [Google Scholar]

| Parameter Expression | Conventional OTA of Figure 3a | OTA with RLCMFB of Figure 3b |

|---|---|---|

| Aol (V/V) | (gm1gm3/gm2) ro3||ro4~Aint/2 | gm1R′gm3 (ro3||ro4)~(Aint/2)2 |

| GB (rad/s) | (gm1/CL) (gm3/gm2)~gm/CL | gm1R′gm3/CL)~Aintgm/CL |

| SR (V/s) | 2IBIAS/CL | MIBIAS(IBIASR/VDSSat)2/CL |

| CMRR | ~200 gm1rotail | ~200(gm1R′)(gm2rotail) |

| Conventional OTA Figure 3a | RLCMFB OTA Figure 3b | |

|---|---|---|

| CL (pF), Rs(kΩ) | 5 pf, 0 | 5 pF, 0.4 |

| W/L PMOS, and NMOS (µm/µm) | 5/0.26 | 5/0.26 |

| Vos (mV) | −12.4 | 0.9 |

| Aol (dB) | 27.2 | 50.3 |

| PM (°) | 90.8 | 62.2 |

| Pdiss (uW) | 30 | 30 |

| fpout (MHz) | 0.3802 | 0.3802 |

| fu (MHz) | 8.7 | 72.4 |

| Pdis(uW) | 30 | 30 |

| BWVF | 8.3 | 75.9 |

| GB (MHz) | 8.7 | 124 |

| SR+/SR− (V/µs) | 6.4/4.6 | 71.4/70.4 |

| CMRR (dB) | 54 | 80 |

| PSRR+ (dB) | 54.1 | 74.3 |

| PSRR− (dB) | 28 | 51.8 |

| Input noise at 1kHz nV/(Hz)1/2 | 26 | 20 |

| IoutPk+/Ioutpk− µA | 32/23 | 357/352 |

| FOMSS (MHz pF/µW) | 1.45 | 12.1 |

| FOMLS (V/µs)pF/µW | 0.77 | 11.7 |

| Parameters | [2] 2017 | [3] 2019 | [4] 2019 | [5] 2020 | [6] 2020 | [7] 2021 | OTA with RLCMFB of Figure 3b |

|---|---|---|---|---|---|---|---|

| CMOS process (nm) | 180 | 180 | 180 | 180 | 180 | 180 | 130 |

| Vsupply (V) | 0.5 | 1.2 | 1.8 | 1.8 | 1.8 | 1.8 | 1.2 |

| ItotQ (µA) | 7.9 | 700 | 530 | 260 | - | 400 | 22.5 |

| CL (pF) | 1 | 10 | 5 | 5.6 | 8 | 18 | 5 |

| Aol (dB) | 50 | 75 | 105.5 | 90.1 | 68 | 73.4 | 50.3 |

| GB (MHz) | 16.6 | 185 | 231.7 | 157 | 172.5 | 224 | 72.4 |

| PM (degree) | 72 | 71 | 53 | 62.1 | 48.7 | 69 | 62.2 |

| SR+/SR− (V/µs) | 4.25 | 99 | 13.2 | 64 | 212 | 110 | 71.4/70.4 |

| FOMSS (MHz pF/µW) | 4.2 | 2.2 | 1.21 | 1.87 | 1.21 | 5.6 | 12.1 |

| FOMLS ((V/µs)pF/µW) | 1.076 | 1.17 | 0.007 | 0.76 | 0.34 | 2.75 | 11.7 |

| FOMGLB = (FOMLSFOMSS)1/2 | 2.12 | 1.61 | 0.09 | 1.19 | 0.64 | 4 | 11.9 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ramirez-Angulo, J.; Lopez-Martin, A.J.; Carvajal, R.G.; Torralba, A.; Huerta-Chua, J. A Review of Techniques to Enhance an Amplifier’s Performance Using Resistive Local Common Mode Feedback. Eng 2023, 4, 780-798. https://doi.org/10.3390/eng4010047

Ramirez-Angulo J, Lopez-Martin AJ, Carvajal RG, Torralba A, Huerta-Chua J. A Review of Techniques to Enhance an Amplifier’s Performance Using Resistive Local Common Mode Feedback. Eng. 2023; 4(1):780-798. https://doi.org/10.3390/eng4010047

Chicago/Turabian StyleRamirez-Angulo, Jaime, Antonio J. Lopez-Martin, Ramón G. Carvajal, Antonio Torralba, and Jesus Huerta-Chua. 2023. "A Review of Techniques to Enhance an Amplifier’s Performance Using Resistive Local Common Mode Feedback" Eng 4, no. 1: 780-798. https://doi.org/10.3390/eng4010047

APA StyleRamirez-Angulo, J., Lopez-Martin, A. J., Carvajal, R. G., Torralba, A., & Huerta-Chua, J. (2023). A Review of Techniques to Enhance an Amplifier’s Performance Using Resistive Local Common Mode Feedback. Eng, 4(1), 780-798. https://doi.org/10.3390/eng4010047