Abstract

Extensive research has been conducted on the scaling fractal fractor using various structures. The development of high-resolution emulator circuits to achieve a variable-order scaling fractal fractor with high resolution is a major area of interest. We present a scaling fractal-ladder circuit for achieving high-resolution variable-order fractor based on scaling expansion theory using a high-resolution multiplying digital-to-analog converter (HMDAC). Firstly, the circuit configuration of variable-order scaling fractal-ladder fractor (VSFF) is designed. A theoretical demonstration proves that VSFF exhibits the operational characteristics of variable-order fractional calculus. Secondly, a programmable resistor–capacitor series circuit and universal electronic component emulators are developed based on the HMDAC to adjust the resistance and capacitance in the circuit configuration. Lastly, the model, component parameters, approximation performance, and variable-order characteristics are analyzed, and the circuit is physically implemented. The experimental results demonstrate that the circuit exhibits variable-order characteristics, with an operational order ranging from to and an operational frequency ranging from to . The peak value of the input signal is . This study also proposes a novel method for variable-order fractional calculus based on circuit theory. This study was the first attempt to implement feasible high-resolution continuous variable-order fractional calculus hardware based on VSFF.

1. Introduction

Fractional calculus, a branch of mathematics, has been widely implemented in the various fields of science and engineering [1,2,3]. Although it typically has a constant order, its application in describing new phenomena and problems with an operational order dependent on variables such as time and space is difficult. These problems can be better described using variable-order fractional calculus [4,5,6], which was first proposed by Samko and Ross [7] in 1993. Variable-order fractional calculus is expressed through mathematical functions that can be used to model natural phenomena and processes. The studies conducted on variable-order fractional calculus were primarily focused on the mathematical description of variable-order phenomena and processes and on the theory of variable-order fractional calculus application system design [4,5,6,8,9,10,11,12]. However, studies on the implementation of flexible and controllable physical entities of variable-order fractional calculus are scarce.

The solid-state fractor can be used as the physical entity of variable-order fractional calculus operation. However, it faces certain limitations, such as a narrow range of operational order variation, limited temperature control, and difficulty in operational order adjustment [13,14]. Analog circuit implementation is an important approach that enables the flexible and controllable physical implementation of variable-order fractional calculus operation. Sierociuk et al. conducted several pioneering studies [15,16,17]. They use analog circuits to implement many kinds of variable-order fractional calculus circuits. These studies primarily employed the switching strategy to switch between two or three-order types. Constant-order fractor has been used in variable-order circuits and systems [15,16,17,18]. Variable-order fractional impedance (variable-order fractor) is a basic unit circuit or element that can perform variable-order fractional calculus. Variable-order fractional calculus can be realized by changing the operational order while maintaining the structure of the variable-order fractor circuit. In [19], a fractor circuit was designed based on rational approximation, and the order was changed by adjusting the transconductance operational amplifier control current. The operational order was switched between 0.2, 0.5, and 0.8; however, a physical circuit was not implemented. The studies conducted on variable-order fractor with a low operational order variation, narrow range, and regulation difficulties remain limited, to the best of our knowledge. Additionally, the studies conducted on circuit implementation are scarce.

To date, the studies conducted on fractor primarily focused on constant-order fractor circuits. These studies primarily involved two types of constant-order fractor [20]. The first type is constructed either directly or by modeling the phenomena of electrochemistry or other scientific fields, such as Liu-Kaplan [21], 2h-type fractal-tree [20], fractal-ladder [22,23], and fractal-chuan fractor [22,23,24]. The second type is constructed by designing a circuit-realizable rational function to approximate the performance of fractional-order operators such as the Oustaloup algorithm [25,26], Dutta Roy’s fractor [27], and Carlson’s iterating rational approximation algorithm [28,29].

In a previous study, we developed scaling expansion theory [30,31]. This theory can be used to extend multiple fractors, thereby overcoming the limitation of only realizing half- to arbitrary-order operations [30,32,33]. Scaling expansion theory can also be used in mathematics to extend the algebraic iterative equation, which describes the rational approximation of half-order operators into an irregular scaling equation describing arbitrary fractional operators. This theory can be used to construct the scaling fractal-lattice [30,31], scaling fractal-chuan [32], scaling fractal-chain [33], and scaling fractal-ladder fractor [34]. The scaling fractal fractor presents a high operating frequency bandwidth.

Scaling expansion theory is used to extend the semi-order fractor to a fixed scaling structure based on the required constant order. The theory is employed to realize the circuit of a fractional memristor of the scaling fractal-lattice [30] and scaling fractal-ladder fractor [34]. The lumped parameter value adjustment with the port flux or charge must be solved to achieve the scaling fractal fractional memristor [34]. It is similar to that the operational order adjustment must be solved to achieve the variable-order fractor.

Several studies have been conducted on scaling fractal fractor by using various structures [30,31,32,33,34]. However, the design of high-resolution emulator circuits to achieve high-resolution variable-order scaling fractal fractor is theoretically challenging. A variable-order scaling fractal-ladder fractor (VSFF) circuit implementation method is proposed to overcome this issue. The main contributions of this study are as follows:

- The proposed circuit can realize the VSFF, thereby overcoming the limitations faced by the existing variable-order fractor, such as limited operational order variation, narrow range, and difficult adjustment [13,14,19].

- A programmable resistor–capacitor series circuit and programmable universal electronic component emulators are designed based on the high-resolution multiplying digital-to-analog converter (HMDAC). These emulators can also be applied to other variable-order fractor circuits, memristor emulators, and memcapacitor emulators [35,36,37].

- This paper also proposes a method for variable-order fractional calculus based on circuit theory.

The remainder of this paper is organized as follows. Section 2 presents the VSFF circuit configuration. A programmable resistor–capacitor series circuit emulator and a universal electronic component emulator are designed based on the requirements of the circuit configuration. Section 3 presents the model and component parameters in the VSFF and the calculation of the relative error of equivalent parameters of the programmable circuit. The approximation performance and variable-order characteristics of the VSFF are analyzed in the frequency domain. The VSFF is implemented, and the variable-order operation characteristic of the circuit is experimentally validated. Section 4 and Section 5 present the discussions and conclusions, respectively.

2. VSFF Design

This section describes the design of the proposed VSFF. Firstly, the circuit configuration is presented. Subsequently, the emulators required to realize the programmable resistor–capacitor series circuit, universal electronic capacitor, and resistor components are described.

2.1. VSFF Circuit Configuration

Scaling fractal-ladder fractor is a classic constant-order fractor circuit [34]. It is employed to achieve the scaling fractal fractional memristor and design the lumped parameter value of the fractor with the port flux or charge [34]. Similarly, the constant-order fractor circuit component parameters must be adjusted based on the required change in the operational order to design a variable-order fractor circuit for solving the problem. Therefore, the design of the VSFF circuit configuration requires only the resistor and capacitor to be replaced in the constant-order scaling fractal-ladder fractor with the variable resistor and capacitor controlled by the microcontroller.

This subsection presents the VSFF circuit configuration and explains the parameters and calculation of the admittance function. Subsequently, the equivalent operation order expression of the VSFF in the characteristic frequency range is calculated to prove that the VSFF possesses characteristics of variable-order fractional calculus operations. Furthermore, it presents a method to optimize the VSFF and improve the approximation performance. Lastly, it explains the correlation between the circuit parameters and operation order.

2.1.1. Circuit Configuration and Admittance

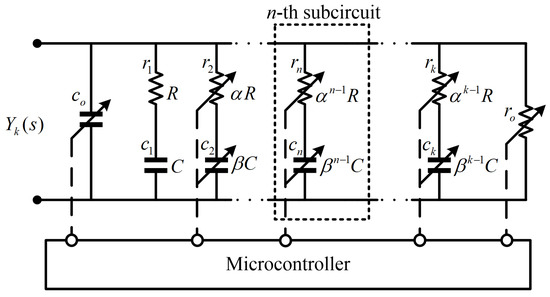

Figure 1 depicts the VSFF circuit configuration. The n-th subcircuit comprises a variable resistor, , in series with a variable capacitor, . k denotes the total number of subcircuits. The serial number, . , denotes the reference resistance (capacitance). Resistor and capacitor are used for circuit optimization. The n-th subcircuit, , and denote the programmable resistor–capacitor series circuit, programmable resistor, and programmable capacitor emulators, respectively, which are controlled by the microcontroller. denotes the resistance (capacitance) progression ratio. The parameter [15,31],

represents the scaling factor of the circuit, where , , and denote the scaling parameters. The scaling parameters are positive real numbers and , . The case in which all the scaling parameters are greater than 1 corresponds to the direct proportion extension VSFF. However, the case in which all the scaling parameters are between 0 and 1 corresponds to the inverse proportion extension VSFF.

Figure 1.

Circuit configuration of VSFF.

The VSFF can realize any real fractional operation in the approximation frequency range. When resistor and capacitor are not considered, the admittance of the VSFF function can be obtained as follows:

s denotes the Laplace or the operational variable, where , , and . The admittance function is normalized as follows:

The iterative algorithm formula of the normalized admittance function is expressed as follows:

When , the equation,

corresponding to the formula of the iterative algorithm, which is the VSFF scaling equation. Equation (5) can be used to analyze the electrical characteristics of the VSFF, including the frequency characteristics and operational order.

2.1.2. Characteristic Frequency and Operational Order

The theoretical expression of the operational order of VSFF in the characteristic frequency range can be calculated. The characteristic frequency of the n-th subcircuit can be expressed as follows:

Therefore, when is a direct proportion extension, is extended to the lower-frequency range. In an inverse proportion extension, , is extended to the higher-frequency range. When

at high frequencies (), the circuit exhibits resistive characteristics. At low frequencies (), the circuit exhibits capacitive characteristics, that is

When the frequency band meets

the resistive and capacitive components interact, and the circuit exhibits fractional calculus operational performance. The operational order can be expressed as follows [34]:

where denotes the operational order. A VSFF can be constructed by adjusting the values of and , as shown in (10).

2.1.3. VSFF Optimization

The parallel-connected resistor, , and capacitor, , in the circuit are used to optimize the VSFF to achieve a better variable-order fractional calculus performance. It is assumed that an infinite number of subcircuits exist before the 1-th subcircuit and behind the k-th subcircuit since the total number of subcircuits is limited. When . The resistance and capacitance decrease progressively with decreasing number of n at each subcircuit before the 1-th circuit. The capacitor of each subcircuit plays a significant role. The capacitor connected in parallel before the 1-th subcircuit is expressed as follows:

For each subcircuit behind the k-th circuit, both the resistance and capacitance increase with increasing number of n. The resistor of each subcircuit plays a significant role. The resistor connected in parallel behind the k-th subcircuit is expressed as follows:

Similarly, when , the capacitor connected in parallel before the 1-th subcircuit and the resistor connected in parallel behind the k-th subcircuit are and , respectively.

Without loss of generality, the VSFF circuit uses a direct proportion extension ( and ).

2.1.4. Component Parameter Calculation

The parameter values of each component and its variation rule of the circuit configuration can be calculated based on the operational order, , and its variable-order range. and denote the minimum and maximum values of the variable-order range, respectively. The resistance progressive ratio, , and capacitance progressive ratio, , are calculated based on the variable-order range, , and scaling parameter, . The n-th variable resistor,

and the n-th variable capacitor,

The resistor,

and the capacitor,

The partial derivative of the n-th variable resistor with respect to the operational order can be obtained as follows:

If , . If ,

The resistance of decreases with an increase in apart from the fixed value of . The partial derivative of corresponding to can be obtained as follows:

If , . If ,

Except for the fixed value of , the capacitance of increases with an increase in .

2.2. Programmable Resistor–Capacitor Series Circuit Emulator

Figure 1 depicts the n-th subcircuit, which is composed of a variable resistor, , in series with a variable capacitor, . If the variable resistor, , and variable capacitor, , are equivalent when using separate emulators, each emulator must be controlled separately, and the variable capacitor emulator circuit must be operated by floating. The n-th programmable resistor–capacitor series circuit emulator () was designed to avoid using more hardware circuits and separately control each emulator. and can be controlled by a single HMDAC, and a separate floating emulator circuit is not required.

This subsection presents the circuit schematic of the programmable resistor–capacitor series circuit emulator and explains the parameters involved. The theory proves that the circuit schematic can achieve the aim of the emulator. The expression of the control variable, , is then theoretically deduced to fulfill the variable-order requirement. Lastly, the expressions of the relative errors of and are derived theoretically.

2.2.1. Circuit Schematic

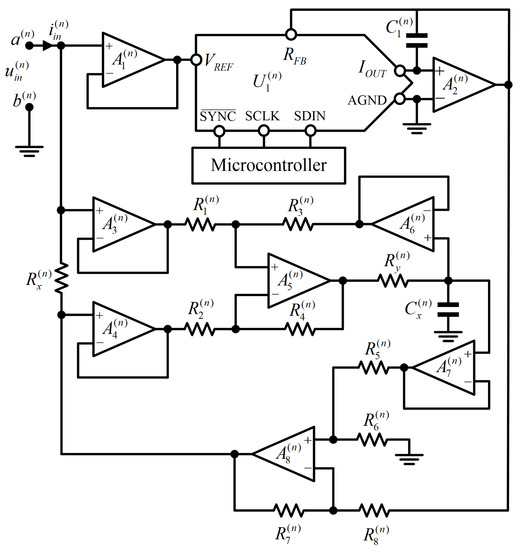

Figure 2 depicts the circuit schematic of the n-th programmable resistor–capacitor series circuit emulator (), where represents the HMDAC. The electrical characteristics between ports, and , are considered as the equivalent electrical characteristics of the n-th subcircuit, as shown in Figure 1. , , the operational amplifier, (, , , and ), and the resistor, (, , , , , and ) form the current follower. The current flowing through the capacitor current, , is equal to the current flowing through the resistor, . If the voltage across the capacitor, , is in , the voltage is obtained as .

Figure 2.

Circuit schematic of the n-th programmable resistor–capacitor series circuit emulator ().

Most digital-to-analog converters (DACs) operate at a fixed reference voltage, where the output voltage or current corresponds to the product of the reference voltage and the value of a set control variable. The reference voltage of a multiplicative DAC typically varies within the range of . for the output current, , and the integrated feedback resistor inside the constitute a precision current-voltage conversion amplifier. The output voltage of is and the control variables,

are controlled by the microcontrollers. corresponds to the digital quantity, (), provided by the microcontroller. m is expressed as the number of bits of the HMDAC. , , , , , and constitute a differential amplifier circuit. The output voltage of is

Therefore,

According to (23), the circuit illustrated in Figure 2 is equivalent to the series connection of the programmable resistance,

Furthermore, the programmable capacitance,

2.2.2. Calculating the Control Variable of

The equivalent and of Figure 2 can be achieved by adjusting the value of the control variable, , using the microcontroller based on the VSFF, which decreases the number of DACs and presents considerable advantages. According to

gradually increases and gradually decreases with an increase in . When , the minimum programmable resistance, is . According to (13) and (18), when is the minimum value within the change range, must be the maximum value, i.e.,

When , the maximum value of is . According to (14) and (20), when is the maximum value within the change range, the operational order, , must be the maximum value, that is

When ,

can be obtained from (13) and (29). When ,

can be obtained from (14) and (30). Remarkably, (31) and (32) produce the same result:

Only one control variable, , is required to satisfy the change in the resistance, , and capacitance, , of the n-th subcircuit in the VSFF, as shown in (33). When compared to the programmable resistance and capacitance circuits, which require HMDAC control, the number of HMDAC is halved, the circuit is simpler, and the I/O port resources of the microcontroller are reduced.

2.2.3. Calculating the Relative Errors of and

Figure 2 depicts the relative errors of and of the circuit, which correspond to , , n, and m. According to (24), the correlation between the relative error, , of and the resolution, , of the HMDAC is expressed as:

According to (25), the correlation between the relative error, , of and is expressed as:

When , is the maximum value within the change range, and and can be used to obtain the maximum relative error within the change range:

The maximum relative error of the programmable resistor–capacitor series circuit emulator corresponds to the ranges of , n, and m. The larger the range of , the larger the maximum relative error of the equivalent programmable parameter. The larger the serial number, n, the larger the maximum relative error of the equivalent programmable parameter. The larger the number of bits, m, the smaller the resolution, , and the maximum relative error of the equivalent programmable parameters.

2.3. Programmable Universal Electronic Component Emulator–Programmable Resistor and Capacitor for Circuit Optimization

Figure 1 illustrates the programmable resistor, , and programmable capacitor, . Fewer schematics are used to simplify the overall circuit schematic. A programmable universal electronic component emulator was also designed.

This subsection presents a circuit schematic of the programmable universal electronic component emulator and explains the parameters involved. The theory proves that the circuit schematic can achieve the aim of the emulator. Subsequently, the expressions of the control variables, and , are deduced theoretically to fulfill the variable-order requirement. Lastly, the expressions of the relative errors of and are derived theoretically.

2.3.1. Circuit Schematic

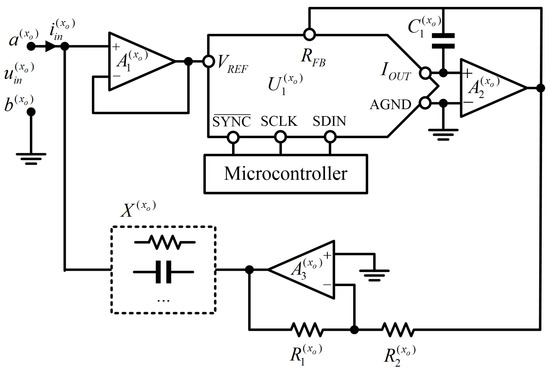

Figure 3 depicts the circuit schematic of the programmable universal electronic component emulator. represents the HMDAC. If and represent the resistance, , the electrical characteristics between ports and are considered to be equivalent to the electrical characteristics of the resistor, , as shown in Figure 1. If and represent the capacitance, , the electrical characteristics between the ports, and , are used as the equivalent electrical characteristics of capacitor, , as shown in Figure 1. The operational amplifier, , constitutes the voltage follower. The operational amplifiers, , and resistors, ( and ), constitute the inverse proportional amplifiers. When and , the output voltage is . For port, , the input current is expressed as

that is

where s denotes the complex frequency variable. According to (39), the equivalent component parameter value of the circuit shown in Figure 3 can be adjusted by adjusting the control variables, , using the microcontroller. If and , the equivalent programmable optimized resistance is expressed as

where corresponds to the control variable, , and is controlled by the microcontroller. If and , the equivalent programmable optimized capacitance is expressed as:

where corresponds to the control variable, , and is controlled by the microcontroller. If represents circuit parameters other than the resistance and capacitance, such as the inductance, fractance, and transtance [38], the circuit shown in Figure 3 can also be used to realize a programmable circuit with more component parameter values, thereby improving its applicability.

Figure 3.

Circuit schematic of the programmable universal electronic component emulator.

2.3.2. Calculating the Control Variables of and

The equivalent programmable optimized resistance, , or the programmable optimized capacitance, , shown in Figure 3 can be realized through a microcontroller by adjusting or . The partial derivative of corresponding to can be obtained as . This indicates that, with an increase in , decreases progressively. The partial derivative of , shown in (15), to can be obtained as . This indicates that increases with an increase in . When is used, the maximum obtained is when . That is,

The partial derivative of corresponding to is obtained as follows:

decreases with the increase in . The partial derivative of of (16) corresponding to can be obtained as

where decreases with an increase in . When is set, the maximum is in . That is,

can be obtained from (16), (41) and (46) as follows:

2.3.3. Calculating the Relative Errors of and

When realizing the VSFF, the relative error of the equivalent element parameter values in Figure 3 corresponds to , , n, and m. The correlation between the relative error, , of and is expressed as follows:

According to (43), can be obtained when and the minimum relative error of within the change range is expressed as follows:

when , is the maximum value within the change range, and the maximum relative error can be obtained from (43) and (48) as follows:

The correlation between the relative error of and can be given as

According to (47), when the operation, , the control variable , and is the minimum relative error within the change range,

When , is the maximum value within the change range and the maximum relative error of is obtained. That is,

3. Experimental Results

This section presents the results of the experiments and the verification of the VSFF circuit. Firstly, the model and component parameters in the VSFF are provided, and the relative error of the programmable circuit is calculated. Subsequently, the approximation performance and variable-order characteristics of the VSFF are analyzed in the frequency domain. Furthermore, two equivalent methods to calculate the variable-order electrical characteristics are presented. One of these characteristics is derived from circuit theory and is presented herein. Lastly, the VSFF is implemented and the variable-order characteristic of the circuit is experimentally validated.

3.1. Circuit Implementation

This subsection presents the parameters, models, and instruments used for circuit implementation. Firstly, the values of the component parameters are presented and the model selection of the microcontroller and the HMDAC are introduced. Subsequently, a list of circuit parameters is presented, which includes the control variables of the microcontroller, equivalent parameters of the emulators, and equivalent parameter relative errors of the emulators. The influence of the different parameters is also demonstrated. Lastly, some details that were considered in the implementation of the circuit are presented.

This circuit realizes the VSFF by replacing the n-th subcircuit shown in Figure 1 with the emulator shown in Figure 2 (), and by replacing the resistance, , (, ) and capacitance, , (, ) of the emulator shown in Figure 3. It was assumed that , , , , , and . The operational amplifiers, , , , , , and , used OP97 and all the other operational amplifiers used OP07.

The HMDAC used AD5544 [39], bits, and a resolution of . Each AD5544 comprised four current output DACs, with each DAC containing an independent multiplying reference input. A load strobe enabled 4-channel, simultaneous updates for hardware-synchronized output voltage changes. Two AD5544 units were used for the implementation of the circuit.

STC8A8K64S4A12 was selected as the microcontroller, as shown in Figure 1. This microcontroller did not require an external crystal oscillator and external reset circuit for an internal clock source frequency of up to 24 MHz. According to (33), (43), (47), and the variable order , the control variables, , , and of AD5544 were set by the STC8A8K64S4A12 to realize the change in the operational order of the VSFF.

Table 1 lists the parameters of the circuit. , , , , , , and were calculated from (27)–(29), (30), (33), (36) and (37), respectively. Following the circuit implementation, and took fixed values. was controlled by the microcontroller, and by varying this value, the microcontroller adjusted and , thereby achieving variable order. and were the minimum and maximum relative errors of and within the range of variation. , , , , and were calculated from (40), (42), (43), (49) and (50), respectively. Following the circuit implementation, took fixed values. was controlled by a microcontroller, and by varying this value, the microcontroller changed , thereby achieving variable order. and were the minimum and maximum relative errors of within the range of variation. , , , , and were calculated from (41), (46), (47), (52) and (53), respectively. Following the circuit implementation, took fixed values. was controlled by a microcontroller and by varying this value, the microcontroller changed , thereby achieving variable order. and were the minimum and maximum relative errors of within the range of variation. For the capacitance, , the resistances not marked in Table 1 were assumed to be .

Table 1.

Circuit parameter list.

As shown in Table 1, , , and were within the range of achievable changes (0∼1). The equivalent minimum relative error and maximum relative error of the emulator met the requirements of Figure 1. If and were not nominal values, they were obtained in series by using the nominal resistors. If and were not nominal values, they were obtained in parallel by using the nominal capacitance. Figure 2 and Figure 3 illustrate the resistors and capacitors of the circuit, which were packaged with 0805. The rated power of the resistance was and the rated voltage of the capacitor was . During production, it was assumed that the power rating of the resistor did not exceed the rated power value, the capacitor voltage was less than the voltage withstand value, and that the power supply voltage, input and output voltages, and input and output currents of all the chips in the circuit were within the standard range.

3.2. Frequency Characteristic Analysis

This subsection presents the frequency domain analysis of the approximation performance and variable-order characteristics of the VSFF. The amplitude-frequency characteristic, phase-frequency characteristic, order-frequency characteristic, and F-frequency characteristic function are introduced, and the theoretical and experimental frequency domain characteristic analysis curve of the VSFF is obtained. Subsequently, the frequency domain characteristic curve is analyzed, and the range of the approximation frequency is obtained when the VSFF changes to a different operation order. Lastly, the correlation between the lumped parameter value and the operation order was solved.

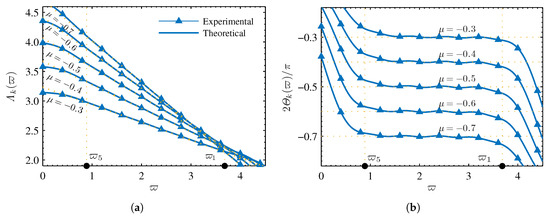

The approximation performance and variable-order characteristics of the VSFF were analyzed by using the frequency characteristics. The impedance function of the VSFF was when the operational order changed to and the impedance was then approximated. The complex frequency variable, s, was replaced by the exponential frequency variable, [31]. That is:

The amplitude-frequency characteristic functions are:

The phase-frequency characteristic function is:

The order-frequency characteristic function [20] is:

The F-frequency characteristic function [40] is:

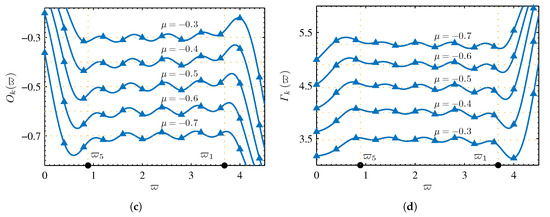

These functions were used for comparative analysis. , , , and represent the frequency characteristic functions of . , , , and represent the frequency characteristic functions of . For the circuit configuration shown in Figure 1 and in the case of the parameter values shown in Table 1, when , respectively. , , , and were calculated from (13), (14)–(16), respectively. These parameters are substituted into (2). Based on (55)–(58), the theoretical characteristic function curve in the frequency domain was determined, as shown in Figure 4. Figure 4 also shows the simulation experiment results obtained by Multisim 14.

Figure 4.

Frequency characteristic curves of VSFF: , , R = 330 , and C = 0.1 : (a) amplitude-frequency characteristic; (b) phase-frequency characteristic; (c) order-frequency characteristic; (d) F-frequency characteristic.

The amplitude-frequency and phase-frequency characteristic function curves, shown in Figure 4a,b, describe the gain and phase characteristics between the voltage and current of the VSFF in the frequency domain, respectively. It can be observed from the amplitude–frequency function curve that the amplitude–frequency characteristic values decreased with increasing frequency. The smaller the operational order, the higher the rate of reduction in the amplitude–frequency characteristic values with increasing frequency. In the low-frequency range, the amplitude—frequency characteristic values decreased with increasing operational order. The phase-frequency and order-frequency characteristic curves, shown in Figure 4b,c, respectively, constitute the mathematical basis to analyze the operational performance (such as the operational order, constant phase, and approximation performance) of the VSFF.

In the case of a fixed operational order, the phase was a fixed value in the approximation frequency range (∼). When the frequency was less than , the phase increased with decreasing frequency. When the frequency was greater than , the phase decreased with increasing frequency. In the case of a fixed frequency, the phase decreased with decreasing operational order. The order-frequency characteristic function represents the operational order of the VSFF from the frequency domain. It can be observed from the order–frequency function curve that the operational order was a fairly constant value in the approximation frequency range (∼). When the frequency was less than , the operational order increased with decreasing frequency. When the frequency was greater than , the operational order decreased with increasing frequency. In the case of a fixed frequency, the operational order decreased with decreasing operational order. The F-frequency characteristic function curve, shown in Figure 4d, represents the lumped parameter value of the VSFF in the frequency domain.

It can be observed from F-frequency function curve that the lumped parameter value was a fairly constant value in the approximation frequency range (∼). When the frequency was less than , the lumped parameter value decreased with the decrease in the frequency. When the frequency was greater than , the lumped parameter value increased with the increase in frequency. In the case of a fixed frequency, the lumped parameter value increased with the decrease in the operational order. The order-frequency and F-frequency characteristic functions visually represent the degree of operational order and the lumped parameter value of the VSFF approximation of the ideal fractor element. It can be observed from the order-frequency and F-frequency characteristic curves, that the VSFF realized the fractional and variable operation orders within a certain frequency range. The highest frequency index value [31],

and the lowest frequency index value [31],

were used to realize fractional-order operation.

Therefore, the operating frequency range of the VSFF of the parameters shown in Table 1 was obtained as (∼), i.e., (∼). The lumped parameter value, , was solved within the operating frequency range, as observed from the F-frequency characteristic curve. The correlation between the lumped parameter value, , and was solved by using the least square method to fit the data and to obtain the following equation:

The relative error of calculated by (61) within the variation range of , was less than .

3.3. Two Equivalent Methods for Calculating Variable-Order Electrical Characteristics

This subsection presents two equivalent methods to calculate the variable-order electrical characteristics to obtain the time-domain theoretical electrical characteristics of the VSFF. One of these methods is derived from circuit theory and is presented in this study. The other variable-order electrical characteristic calculation method is obtained through the Grünwald-Letnikov variable-order fractional calculus.

3.3.1. Variable-Order Electrical Characteristics Obtained through Circuit Theory

For the input voltage signal, , to the VSFF, the current flowing through the VSFF according to Kirchhoff’s current and voltage laws can be represented as follows:

where denotes the voltage across the capacitor, , and is described by

3.3.2. Variable-Order Electrical Characteristics Obtained through the Grünwald–Letnikov Definition

The input voltage signal, , to the VSFF and the main spectral range of was within the approximate frequency range of the VSFF. The input current obtained is expressed as follows [13]:

where is the initial time.

Grünwald-Letnikov variable-order fractional calculus was used to define the computation completion (64). It has at least three widely used definitions [15,16,17]. These definitions are based on replacing the constant operational order, , with variable operational order, . The coefficients are then obtained based on different sampling methods. If the coefficient is sampled from the order value at the corresponding time of the coefficient, then [15,16,17]:

where , , and are binomial coefficients. To complete the numerical calculation of (65), the step size, h, must be sufficiently small; therefore:

where represents the polynomial coefficient of the function, , which can be directly calculated by using the following recursive formula:

If is constant, the calculated result of (66) must be consistent with that defined by the Grünwald-Letnikov fractional calculus of the constant operational order.

3.4. Experimental Verification

In this subsection, the variable-order characteristics of VSFF are experimentally verified. The experimental fields include steady-state, dynamic, and continuous variable order. The steady-state variable-order experiments can be used to prove that a single VSFF can be used as a constant-order fractor of different orders. The dynamic variable-order experiments can prove that the VSFF contains a variable-order process, which can be used in the cases where the operational order requires a jump. For example, in the design of programmable variable-order fractional chaos [18]. The continuous variable-order experiments can be used to demonstrate the capability of VSFF for programmable high-resolution continuous variable-order.

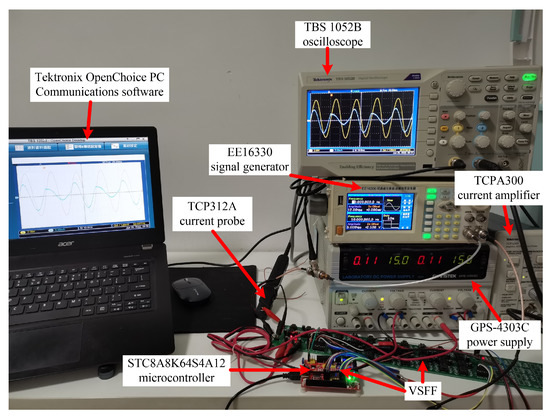

GPS-4303C, TBS1052B, EE16330, TCP312A, and TCPA300, were employed as the power supply, oscilloscope, signal generator, current probe, and current amplifier, respectively. The current probe and amplifier were used to convert the current waveform to a linear voltage signal and to amplify the voltage signal for the oscilloscope test, respectively. The TBS1052B is connected to a PC through a USB interface, which has the Tektronix OpenChoice PC Communications software installed on it to obtain the data that it measured by TBS1052B. Figure 5 depicts the experimental test images.

Figure 5.

VSFF Experiment.

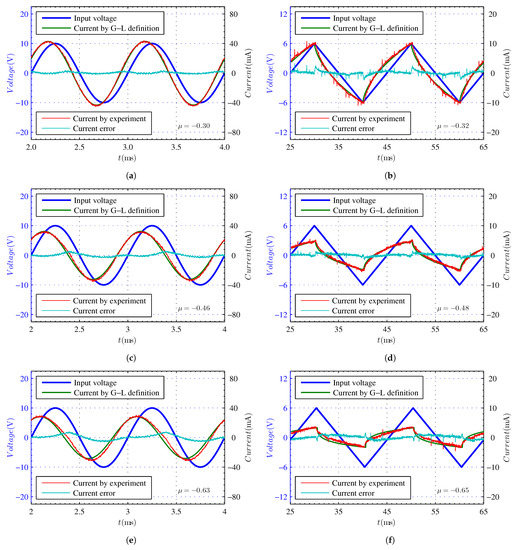

3.4.1. Steady-State Variable-Order Experiment

If the signal generator outputs a sinusoidal voltage signal,

to the VSFF, , and . Then, is , , and , respectively. The Grünwald-Letnikov definition method is used to calculate the current waveform obtained from (61), (66) and (67), and Figure 6a,c,e presents the corresponding experimental current waveform. If the triangular wave voltage signal, , is input into the VSFF, the peak voltage, , frequency, , and change to , , and , respectively. The Grünwald-Letnikov definition method is used to calculate the current waveform, and Figure 6b,d,f depicts the corresponding experimental current waveform. Furthermore, Figure 6 depicts the current error waveform between the experimental current waveform and the Grünwald-Letnikov definition method is used to calculate the current waveform.

Figure 6.

Experimental results of VSFF of steady-state variable-order: (a) sine wave, ; (b) triangular wave, ; (c) sine wave, ; (d) triangular wave, ; (e) sine wave, ; (f) triangular wave, .

According to the experimental current waveform shown in Figure 6, when the input voltage signals are sinusoidal and triangular, the VSFF can perform steady-state variable-order experiments of different orders. The average values of the current error waveforms shown in Figure 6a–f are , , , , , and , respectively. The standard deviations of the current error waveforms shown in Figure 6a–f are , , , , , and , respectively. When the input amplitude of the voltage waveform is constant, the smaller the operational order, , the smaller the amplitude of the current waveform. This is consistent with the amplitude-frequency characteristic function curve depicted in Figure 4a. Figure 6a,c,e demonstrates that when is , , and , the corresponding theoretical phase difference is , and , respectively. Figure 6a,c,e also demonstrates that when is , , and , the corresponding experimental phase difference is , and , respectively. The phase error between the experimental and the theoretical phase is shown in Figure 6a,c,e are , , and , respectively. The phase difference decreases with a decrease in the operational order, , which is consistent with the phase-frequency characteristic curve presented in Figure b. The experimental results concur well with their theoretical counterparts when the input waveform, amplitude, frequency, and operational order change. The peak value of the input signal was .

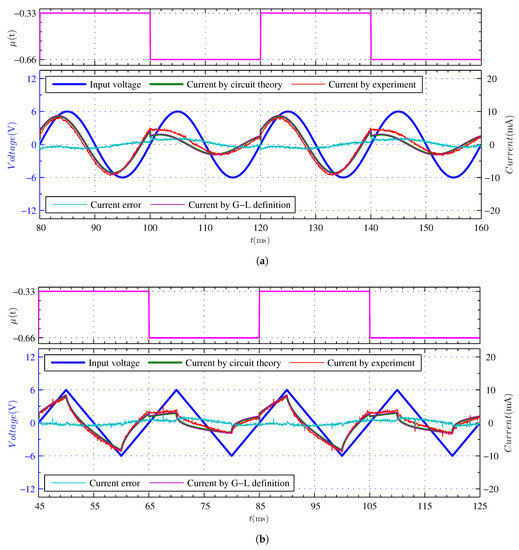

3.4.2. Dynamic Variable-Order Experiment

If the voltage signal, , shown in (68) is input to the VSFF and the peak voltage, ,

Figure 7a presents the circuit theoretical method used to calculate the current waveform obtained from (10), (62) and (63) and the Grünwald-Letnikov definition method used to calculate the current waveform obtained from (61), (66) and (67). Figure 7a presents the corresponding experimental current waveforms. When the triangle wave voltage signal, , is input into the VSFF, the peak voltage, , frequency, , and vary between and . Figure 7b illustrates the circuit theoretical method used to calculate the current waveform obtained from (10), (62) and (63) and the Grünwald-Letnikov definition method used to calculate the current waveform obtained from (61), (66) and (67). Figure 7b illustrates the corresponding experimental current waveform. Additionally, Figure 7a,b presents the current error waveform between the experimental current waveform and the circuit theoretical method calculated current waveform.

Figure 7.

Experimental results of VSFF of dynamic variable-order: (a) sine wave; (b) triangular wave.

According to the experimental current waveform shown in Figure 7, when the input voltage signals are sinusoidal and triangular, the VSFF can complete dynamic variable-order experiments of different orders. The circuit theoretical method and the Grünwald-Letnikov definition method used to calculate the current waveform overlap perfectly. The accuracy of the variable-order electrical characteristics obtained through circuit theory is verified. The average values of the current error waveforms shown in Figure 7a,b are and , respectively. The standard deviations of the current error waveforms shown in Figure 7a,b are and , respectively. At the moment when the operation order jumps, the circuit theoretical method calculated current waveform and the Grünwald-Letnikov definition method calculated current waveform also jump. However, the corresponding experimental waveform jump is not obvious. This is due to parasitic resistance and capacitance parameters in VSFF, test cables, and experimental apparatus, which filter out the high-frequency spectrum during the current waveform jump. According to the experimental current waveform shown in Figure 7, the VSFF completed the change of order within the approximation frequency and operational order ranges.

3.4.3. Continuous Variable-Order Experiment

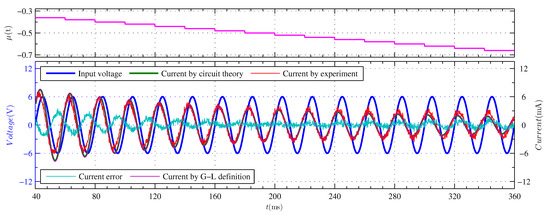

A continuous variable-order experiment was conducted to fully demonstrate the variable-order capability of the VSFF and to reflect its advantages. If the voltage signal, , shown in (68) is input to the VSFF and the peak voltage, , the frequency, , and change from to . The variable-order range included the maximum and minimum values of the designed operational order. Figure 8 depicts the circuit theoretical method used to calculate current waveform obtained from (10), (62) and (63) and the Grünwald-Letnikov definition method used to calculate the current waveform obtained from (61), (66) and (67). Figure 8 depicts the corresponding experimental current waveform. Additionally, Figure 8 depicts the current error waveform between the experimental current waveform and the circuit theoretical method used to calculate the current waveform.

Figure 8.

Experimental results of VSFF of continuous variable-order.

The VSFF can perform continuous variable-order experiments based on the experimental current waveform depicted in Figure 8. The circuit theoretical method and the Grünwald-Letnikov definition method used to calculate the current waveform overlap perfectly. The accuracy of the variable-order electrical characteristics obtained through circuit theory is confirmed once again. The larger current error waveforms are partly due to small phase errors. In essence, the current error is not large. The average value and standard deviations of the current error waveforms shown in Figure 8 are and , respectively. Errors may be caused by many factors such as circuit components, experimental instruments, and frequency domain approximation errors. Errors in circuit components include resistors, capacitors, operational amplifiers, and AD5544. The relative errors of various equivalent parameters of AD5544 caused by resolution have been given in Table 1. Integral non-linearity is also an important factor causing error of AD5544. There is a non-linear relationship between integral non-linearity and digital quantity of AD5544 [39]. The frequency characteristic curves shown in Figure 4 also indicate that there are frequency domain errors that fluctuate with frequency within the approximate frequency range. When the input amplitude of the voltage waveform is constant, changes from to , the smaller the amplitude of the current waveform. This is consistent with the amplitude-frequency characteristic function curve shown in Figure 4a. It can also be observed from Figure 8 that when the operation order reduces, the smaller the operation order, the larger the relative error between the experimental current waveform and the theoretical waveform. This is similar to the equivalent relative error variation rule shown in Table 1. It is observed that the equivalent relative error changes from minimum to maximum as the operation order changes from maximum to minimum. It can be observed from Figure 8 that the variable-order scaling fractal-ladder fractor can perform high-resolution continuous variable-order experiments within the range of the operation order. This is because the HRMDAC and other devices can support the requirement of device indicators for continuous operational order varying.

It can also be observed from Figure 8 that when the operation order is large, the amplitude of the experimental current waveform is smaller than that of the theoretical current waveform. When the operation order is small, the amplitude of the experimental current waveform is larger than that of theoretical current waveform. A similar situation is observed in the steady-state variable-order and dynamic variable-order experiments. The error between the experimental waveform and the theoretical waveform, and the operation order exhibit a stable regularity; this type of error is called a systematic error. System errors must be calibrated often in circuit and system design. Therefore, when the results of Figure 6 and Figure 7 are presented, the same systematic error calibration parameters are implemented for the circuit theoretical method, which is used to obtain the current waveform from (10), (62) and (63) and the Grünwald-Letnikov definition method used to obtain the current waveform from (61), (66) and (67). The calibration results used while constructing an application system using VSFF must be more accurate.

4. Discussion

This study implemented the VSFF superior to existing related studies in multiple indicator dimensions. In [13], when the temperature of the solid-state fractor changed within the range of 25∼, and the operational order changed within a range of only ∼. In [14], when the temperature of the solid-state fractor changed within the range 100∼, the operational order changed within a range of only ∼. The VSFF implemented in this study used a microcontroller, which is more convenient and efficient than the temperature control method [13,14]. In [19], the operational order switched between , , and . However, the studies conducted on circuit implementation are limited. The variable-order range of the circuit realized in this study was from to . This significantly exceeds the operational order range of the variable-order fractor [13,14,19] and exhibits high-resolution characteristics. The HMDAC is crucial in the implementation of the VSFF.

In this study, the scaling fractal fractor used in the VSFF exhibited a classic structure. The voltage-controlled resistance and capacitance circuits used the AD633 multiplier as the core in the memristor and memcapacitor emulators [35,36,37]. The resolution and precision requirements of the VSFF for variable circuit parameter adjustment could not be easily satisfied since the accuracy of the AD633 was approximately . The HMDACs are typically used in the DAC conversion and in multiplier circuits. The HMDAC uses the AD5544, bits, and a resolution of . For the emulator, the equivalent minimum relative error and maximum relative error . The programmable resistor–capacitor series circuit and programmable universal electronic component emulators designed using the HMDAC as the core can better meet the requirements of the VSFF parameter adjustment.

In this study, the selection of component parameters is merely an example of the circuit implementation of the VSFF. The technical specifications of VSFF can be adjusted based on the requirement of the actual system. The frequency range of the operations can be increased by increasing the total number of subcircuits. The accuracy can be improved by decreasing the value of the scaling parameter, . The VSFF accuracy can also be improved by selecting components with higher precision and resolution. Furthermore, the speed of the variable order can be increased by using faster microcontrollers.

Despite the various advantages presented by the implemented VSFF, it faces certain limitations that must be addressed. Firstly, VSFF is larger and thus requires more space, although it is more flexible and has a wider range of steps when compared to the existing solid-state fractor. Secondly, the VSFF variable-order speed is limited by the control speed of the microcontroller. Lastly, it can be observed from the F-frequency characteristic function curve presented in Figure 4d, that when the operational order of VSFF changes, the lumped parameter value also changes.

5. Conclusions

Variable-order fractor is an important unit or component for realizing variable-order fractional calculus operations. Based on previous studies on scaling fractal fractor with various structures [30,31,32,33,34], the theoretical problem of developing high-resolution emulator circuits to achieve VSFF is a major challenge. This study proposed a VSFF circuit configuration based on the scaling expansion theory [30,31]. A programmable resistor–capacitor series circuit and programmable universal electronic component emulators with HMDAC were designed based on the requirements of the circuit configuration. The experimental content includes steady-state, dynamic and continuous variable-order. The operational order ranged from to . The operation frequency of the VSFF ranged from to and the peak value of the input signal was .

The programmable resistor–capacitor series circuit and the programmable universal electronic component emulators were designed based on the HMDAC. Furthermore, these emulators can be applied to other variable-order fractor circuits, memristor emulators, and memcapacitor emulators. The proposed implementation method can also be used to design the existing scaling fractal-chain [33], fractal-chuan [32], and fractal-lattice [30,31] circuits with variable-order fractor. The VSFF can be used to model natural phenomena and processes of the variable order. The proposed variable-order fractional calculus method that is based on circuit theory can be used as a new time-domain approximation method. More circuit theoretical calculation formulas of variable-order fractional calculus operation can be obtained based on the proposed circuit theoretical calculation method of variable-order fractional calculus operation. The variable-order fractional calculus using circuit theory requires further analysis since it is a novel calculation method.

Author Contributions

Conceptualization, B.Y. and Y.P.; methodology, B.Y. and X.Y.; software, B.Y. and Q.H.; validation, B.Y.; writing—original draft preparation, B.Y.; writing—review and editing, B.Y. and Y.P.; supervision, Y.P.; funding acquisition, Y.P. and B.Y. All authors have read and agreed to the published version of the manuscript.

Funding

This work was supported by the National Natural Science Foundation of China, under Grant 62171303; China South Industries Group Corporation (Chengdu) Fire Control Technology Center Project (non-secret), under Grant HK20-03; National Key Research and Development Program Foundation of China, under Grant 2018YFC0830300; Chengdu Normal University Foundation of China, under Grant CS21ZC02; Classic Undergraduate Course Construction Project in the Sichuan Province of China, under Grant SJYLKC2118; and the Collaborative Education Quality Project of Industry-University Cooperation by the Ministry of Education of China, under Grant 201702119108.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

Abbreviations

The following abbreviations are used in this manuscript:

| VSFF | Variable-Order Scaling Fractal-Ladder Fractor |

| HMDAC | High-Resolution Multiplying Digital-to-Analog Converter |

References

- Sun, H.G.; Yong, Z.; Baleanu, D.; Wen, C.; Chen, Y.Q. A new collection of real world applications of fractional calculus in science and engineering. Commun. Nonlinear. Sci. Numer. Simul. 2018, 64, 213–231. [Google Scholar] [CrossRef]

- Baleanu, D.; Agarwal, R.P. Fractional calculus in the sky. Adv. Differ. Equ. 2021, 2021, 117. [Google Scholar] [CrossRef]

- Yu, B.; Pu, Y.F.; He, Q.Y. Fractional-Order Dual-Slope Integral Fast Analog-to-Digital Converter with High Sensitivity. J. Circuit. Syst. Comp. 2020, 29, 2050082. [Google Scholar] [CrossRef]

- Sun, H.G.; Chang, A.; Zhang, Y.; Chen, W. A review on variable-order fractional differential equations: Mathematical foundations, physical models, and its applications. Fract. Calc. Appl. Anal. 2018, 22, 27–59. [Google Scholar] [CrossRef] [Green Version]

- Wu, G.C.; Deng, Z.G.; Baleanu, D.; Zeng, D.Q. New variable-order fractional chaotic systems for fast image encryption. Chaos Interdiscip. J. Nonlinear Sci. 2019, 29, 083103. [Google Scholar] [CrossRef]

- Patnaik, S.; Hollkamp, J.P.; Semperlotti, F. Applications of variable-order fractional operators: A review. Proc. Roy. Soc. A-Math. Phy. 2020, 476, 20190498. [Google Scholar] [CrossRef] [Green Version]

- Samko, S.G.; Ross, B. Integration and differentiation to a variable fractional order. Integral Transform. Spec. Funct. 1993, 1, 277–300. [Google Scholar] [CrossRef]

- Huang, L.L.; Ju, H.P.; Wu, G.C.; Mo, Z.W. Variable–order fractional discrete–time recurrent neural networks. J. Comput. Appl. Math. 2019, 370, 112633. [Google Scholar] [CrossRef]

- Wu, F.; Gao, R.B.; Liu, J.; Li, C.B. New fractional variable-order creep model with short memory. Appl. Math. Comput. 2020, 380, 125278. [Google Scholar] [CrossRef]

- Gu, X.M.; Sun, H.W.; Zhao, Y.L.; Zheng, X. An implicit difference scheme for time-fractional diffusion equations with a time-invariant type variable order. Appl. Math. Lett. 2021, 120, 107270. [Google Scholar] [CrossRef]

- Zheng, X.C.; Wang, H.; Guo, X. Analysis of a Time-Fractional Substantial Diffusion Equation of Variable Order. Fractal Fract. 2022, 6, 114. [Google Scholar] [CrossRef]

- Zheng, X.C.; Wang, H. Discretization and Analysis of an Optimal Control of a Variable-Order Time-Fractional Diffusion Equation with Pointwise Constraints. J. Sci. Comput. 2022, 91, 56. [Google Scholar] [CrossRef]

- Sheng, H.; Sun, H.G.; Coopmans, C.; Chen, Y.Q.; Bohannan, G.W. A Physical experimental study of variable-order fractional integrator and differentiator. Eur. Phys. J. Spec. Top. 2011, 193, 93–104. [Google Scholar] [CrossRef]

- Buscarino, A.; Caponetto, R.; Di Pasquale, G.; Fortuna, L.; Graziani, S.; Pollicino, A. Carbon Black based capacitive Fractional Order Element towards a new electronic device. Int. J. Electron. Commun. 2018, 84, 307–312. [Google Scholar] [CrossRef]

- Sierociuk, D.; Malesza, W.; Macias, M. On the Recursive Fractional Variable-Order Derivative: Equivalent Switching Strategy, Duality, and Analog Modeling. Circuits Syst. Signal Process. 2015, 34, 1077–1113. [Google Scholar] [CrossRef] [Green Version]

- Sierociuk, D.; Macias, M.; Malesza, W. Analog realization of fractional variable-type and -order iterative operator. Appl. Math. Comput. 2018, 336, 138–147. [Google Scholar] [CrossRef]

- Sierociuk, D.; Macias, M.; Malesza, W. Fractional Recursive Variable-Type and Order Operator for a Particular Switching Strategy. Electronics 2020, 9, 855. [Google Scholar] [CrossRef]

- Zhou, C.Y.; Li, Z.J.; Xie, F. Coexisting attractors, crisis route to chaos in a novel 4D fractional-order system and variable-order circuit implementation. Eur. Phys. J. Plus. 2019, 134, 73. [Google Scholar] [CrossRef]

- Tsirimokou, G.; Psychalinos, C.; Freeborn, T.J.; Elwakil, A.S. Emulation of current excited fractional-order capacitors and inductors using OTA topologies. Microelectron. J. 2016, 55, 70–81. [Google Scholar] [CrossRef]

- Yuan, X. Mathematical Principles of Fractance Approximation Circuits; Science Press: Beijing, China, 2015. (In Chinese) [Google Scholar]

- Kaplan, T.; Gray, L.J. Effect of disorder on a fractal model for the ac response of a rough interface. Phys. Rev. B 1985, 32, 7360–7366. [Google Scholar] [CrossRef]

- Charef, A. Analogue realisation of fractional-order integrator, differentiator and fractional PID controller. IEE Proc.-Control. Theory Appl. 2006, 153, 714–720. [Google Scholar] [CrossRef]

- Valsa, J.; Vlach, J. RC models of a constant phase element. Int. J. Circ. Theor. App. 2013, 41, 59–67. [Google Scholar] [CrossRef]

- Adhikary, A.; Sen, P.; Sen, S.; Biswas, K. Design and Performance Study of Dynamic Fractors in Any of the Four Quadrants. Circuits Syst. Signal Process. 2016, 35, 1909–1932. [Google Scholar] [CrossRef]

- Oustaloup, A.; Levron, F.; Mathieu, B.; Nanot, F.M. Frequency-band complex noninteger differentiator: Characterization and synthesis. IEEE Trans. Circuits Syst. Fundam. Theory Appl. 2002, 47, 25–39. [Google Scholar] [CrossRef]

- Morales-Delgado, V.F.; Gómez-Aguilar, J.; Taneco-Hernandez, M.A. Analytical solutions of electrical circuits described by fractional conformable derivatives in Liouville-Caputo sense. Int. J. Electron. Commun. 2017, 134, 108–117. [Google Scholar] [CrossRef]

- Roy, D.S. Constant argument immittance realization by a distributed RC network. IEEE Trans. Circuits Syst. 1974, 21, 655–658. [Google Scholar] [CrossRef]

- Carlson, G.E.; Halijak, C. Approximation of Fractional Capacitors by a Regular Newton Process. IEEE Trans. Circuit Theory 1964, 11, 210–213. [Google Scholar] [CrossRef]

- He, Q.Y.; Yu, B.; Yuan, X. Carlson iterating rational approximation and performance analysis of fractional operator with arbitrary order. Chin. Phys. B 2017, 26, 66–74. [Google Scholar] [CrossRef]

- Pu, Y.F.; Yuan, X.; Yu, B. Analog Circuit Implementation of Fractional-Order Memristor: Arbitrary-Order Lattice Scaling Fracmemristor. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 2903–2916. [Google Scholar] [CrossRef]

- Yu, B.; He, Q.; Yuan, X. Scaling fractal-lattice franctance approximation circuits of arbitrary order and irregular lattice type scaling equation. Acta Phys. Sin. 2018, 67, 070202. [Google Scholar]

- He, Q.Y.; Pu, Y.F.; Yu, B.; Yuan, X. Scaling Fractal-Chuan Fractance Approximation Circuits of Arbitrary Order. Circuits Syst. Signal Process. 2019, 38, 4933–4958. [Google Scholar] [CrossRef]

- He, Q.Y.; Pu, Y.F.; Yu, B.; Yuan, X. A class of fractal-chain fractance approximation circuit. Int. J. Electron. 2020, 107, 1588–1608. [Google Scholar] [CrossRef]

- Pu, Y.F.; Yu, B.; Yuan, X. Ladder Scaling Fracmemristor: A Second Emerging Circuit Structureof Fractional-Order Memristor. IEEE Des. Test 2021, 38, 104–111. [Google Scholar] [CrossRef]

- Yu, D.S.; Zhao, X.Q.; Sun, T.T.; Iu, H.H.C.; Fernando, T. A Simple Floating Mutator for Emulating Memristor, Memcapacitor, and Meminductor. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1334–1338. [Google Scholar] [CrossRef]

- Liang, Y.; Wang, G.; Xia, C.; Lu, Z. Simple modelling of S-type NbOx locally active memristor. Electron. Lett. 2021, 57, 630–632. [Google Scholar] [CrossRef]

- Bao, B.C.; Zhu, Y.X.; Ma, J.; Bao, H.; Chen, M. Memristive neuron model with an adapting synapse and its hardware experiments. Sci. China Technol. Sci. 2021, 64, 1107–1117. [Google Scholar] [CrossRef]

- Shen, J.; Cong, J.; Chai, Y.; Shang, D.; Shen, S.; Zhai, K.; Tian, Y.; Sun, Y. A non-volatile memory based on nonlinear magnetoelectric effects. Phys. Rev. Appl. 2016, 6, 021001. [Google Scholar] [CrossRef] [Green Version]

- ADI. AD5544/AD5554 Data Sheet. [EB/OL]. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/AD5544_5554.pdf (accessed on 6 July 2022).

- Yu, B.; He, Q.; Yuan, X.; Yang, L. Approximation performance analyses and applications of f characteristics in fractance approximation circuit. J. Sichuan Univ. 2018, 55, 301–306. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).