Photonic Integrated Circuits: Research Advances and Challenges in Interconnection and Packaging Technologies

Abstract

1. Introduction

2. The Application of PIC

2.1. Neural Network Computing

2.2. Optical Phased Array

2.3. Programmable Photonic Integrated Circuit

2.4. Biomedical Sensing

2.5. Communication in 6G

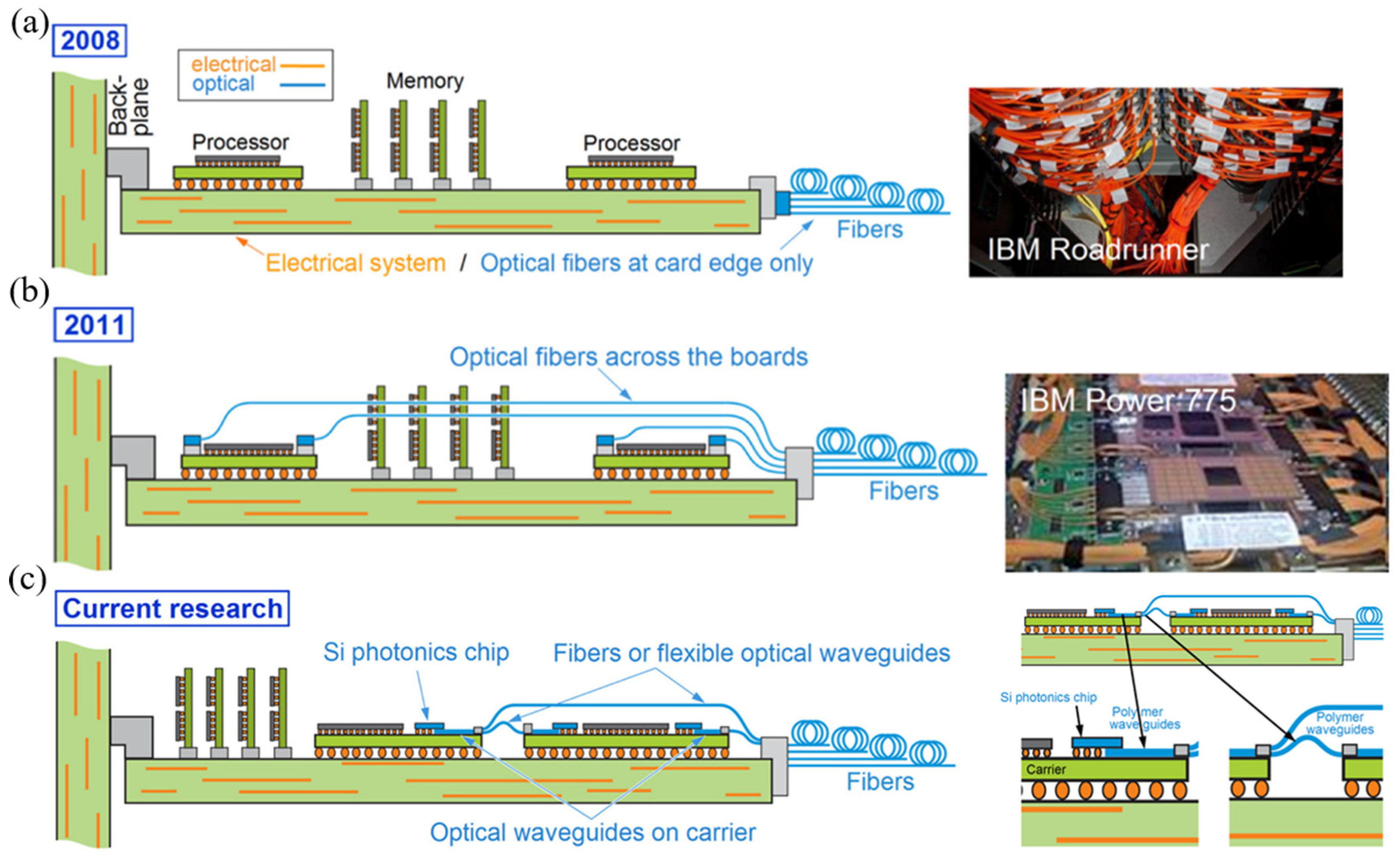

3. Optical Interconnection Technologies

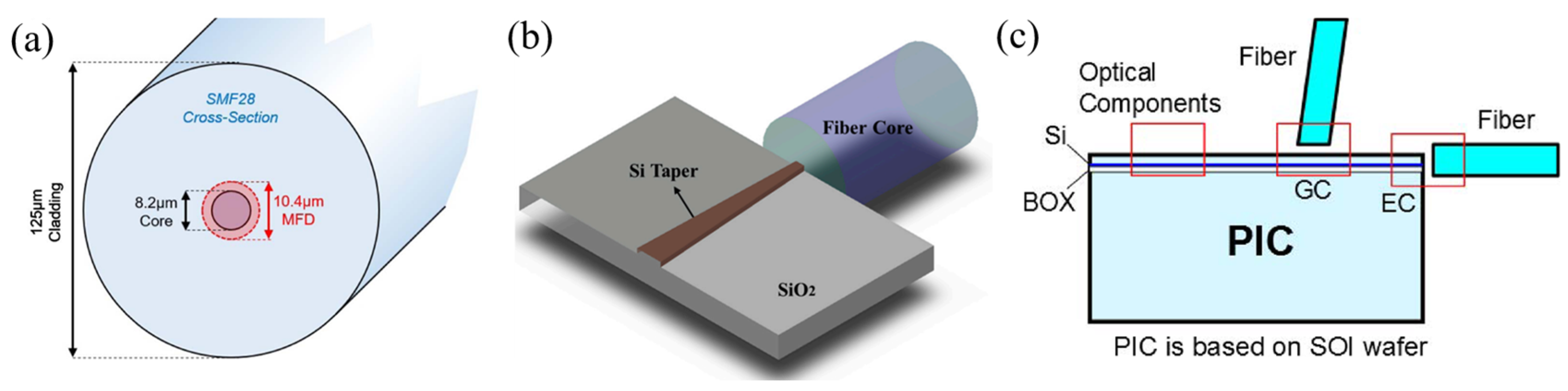

3.1. Fiber-to-Chip Coupling

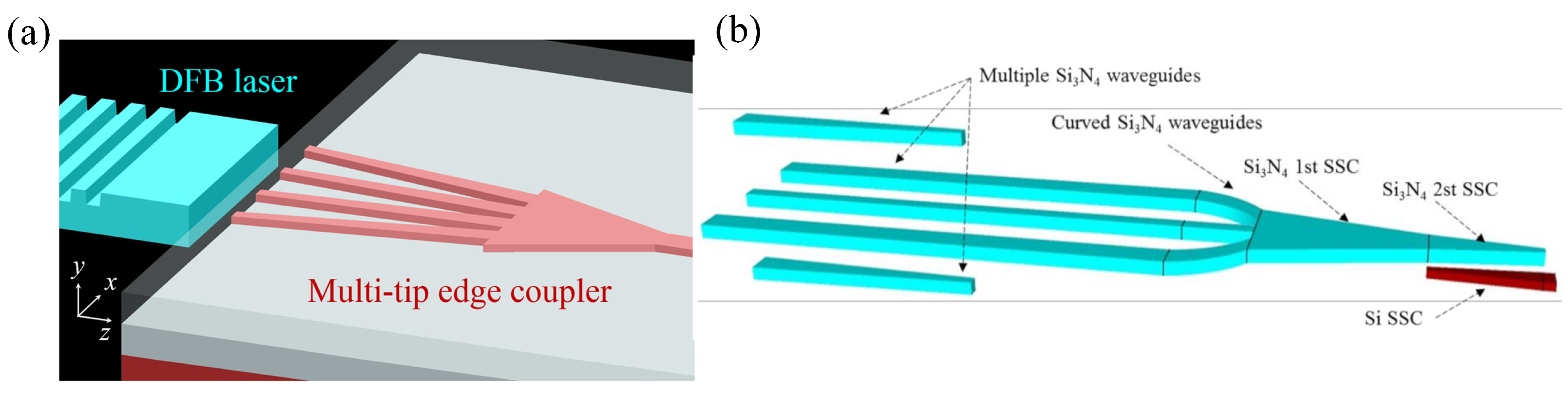

3.1.1. Edge Coupler Based on Inverted Spot-Size Converters

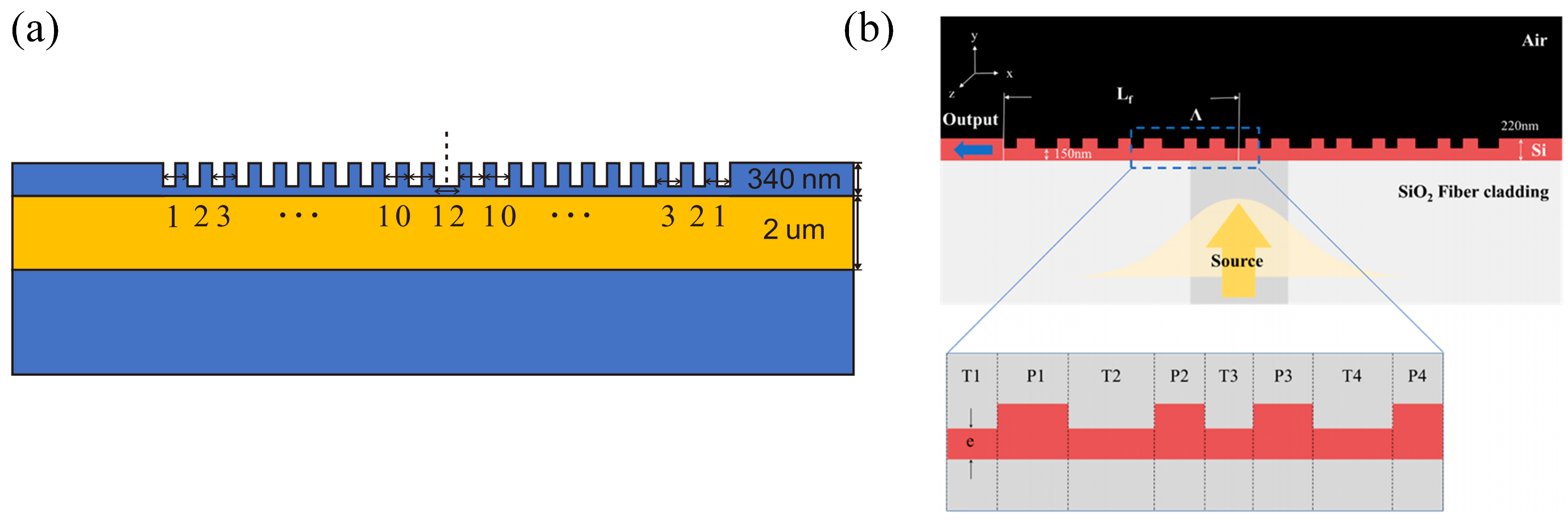

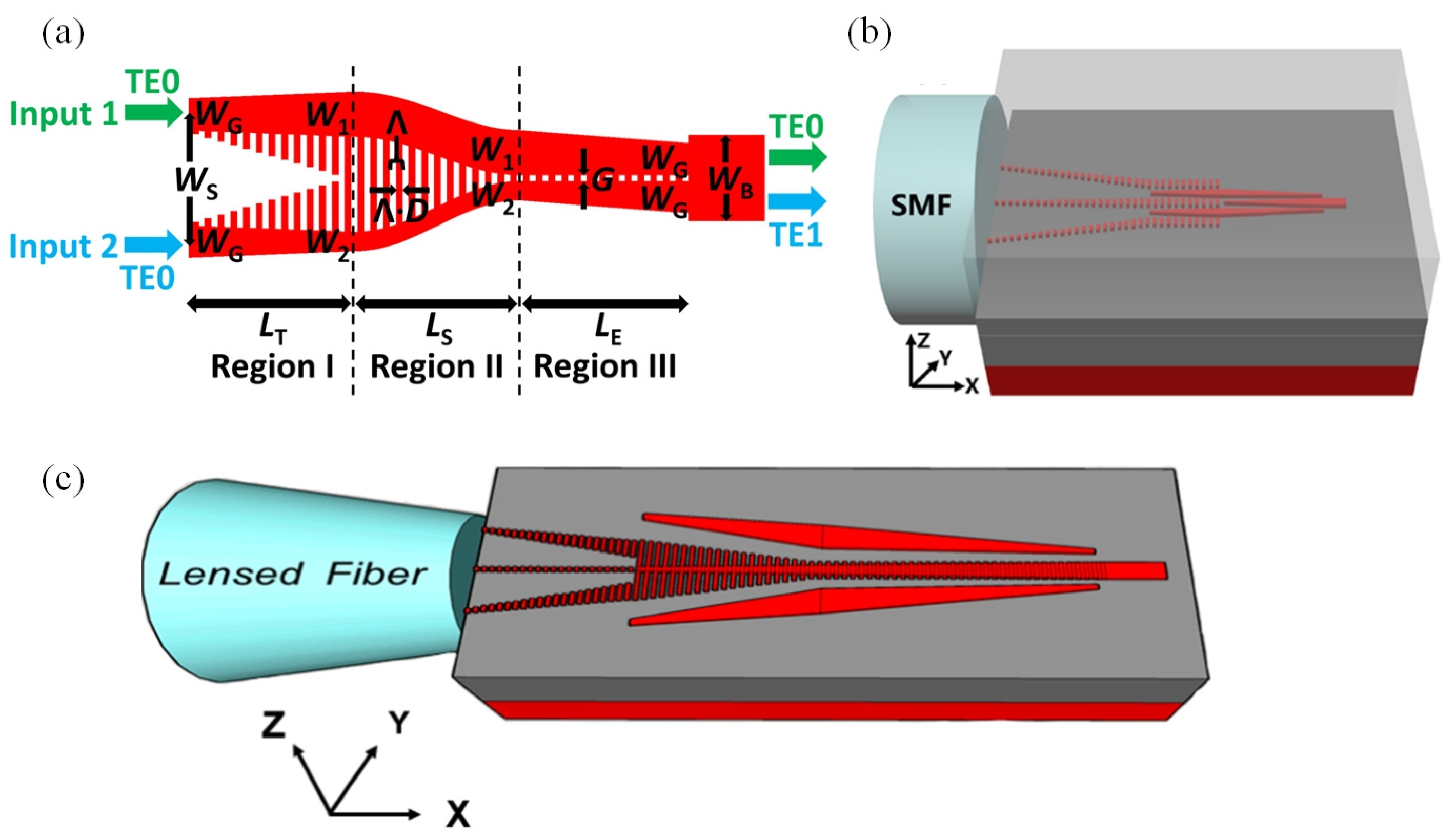

3.1.2. Edge Coupler Based on Subwavelength Grating

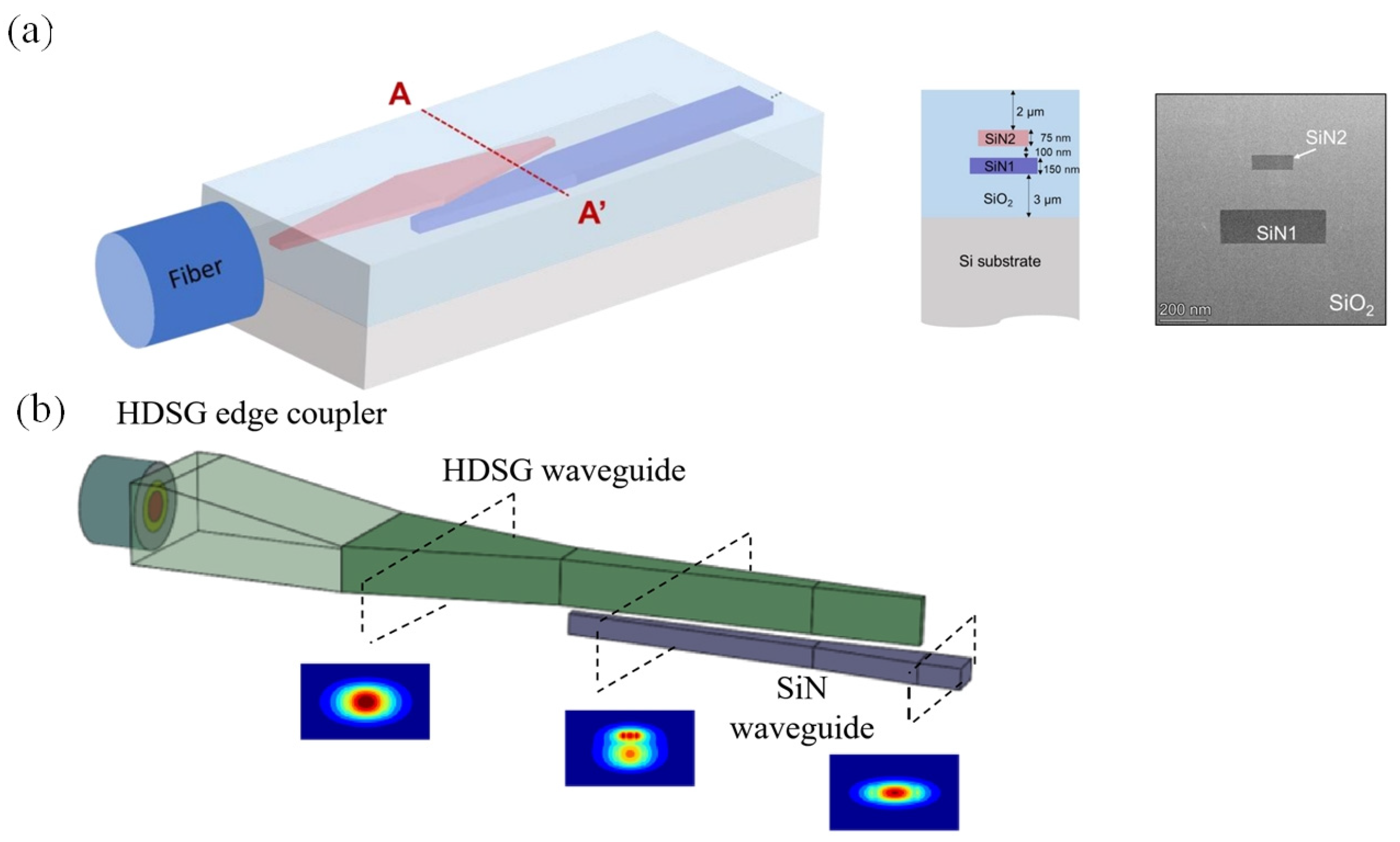

3.1.3. Edge Coupling of Multi-Layer Structures

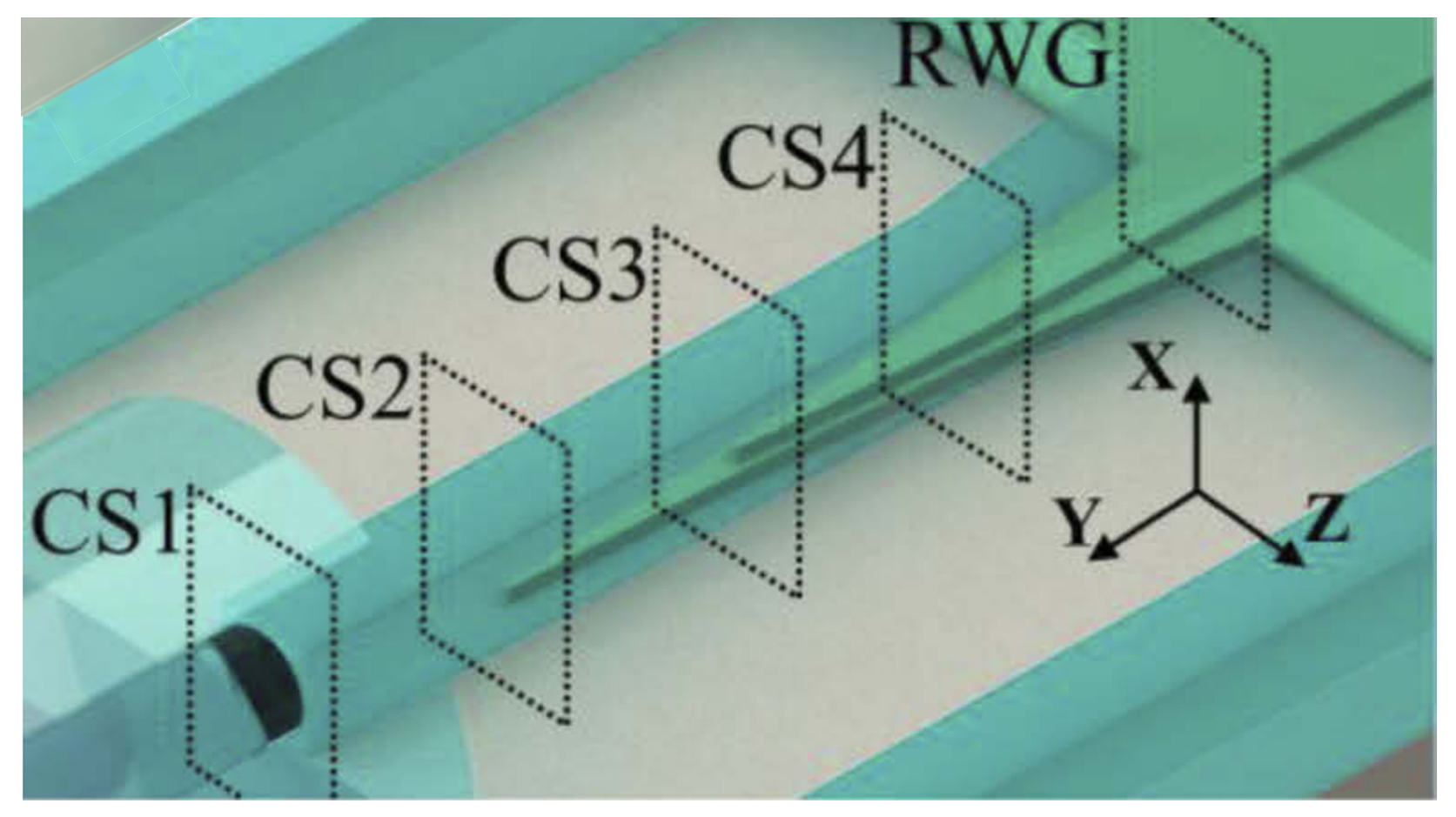

3.1.4. Grating Couplers

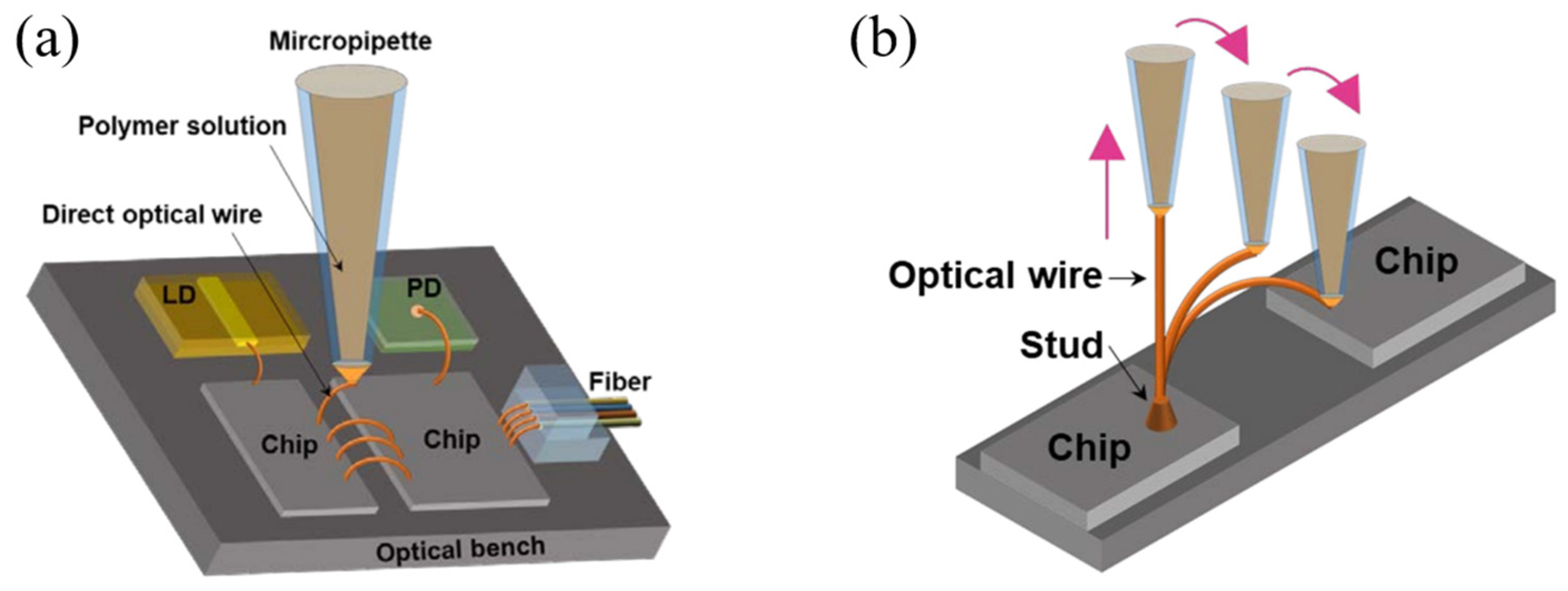

3.2. Photonic Wire Bonding

4. Co-Packaged Optics

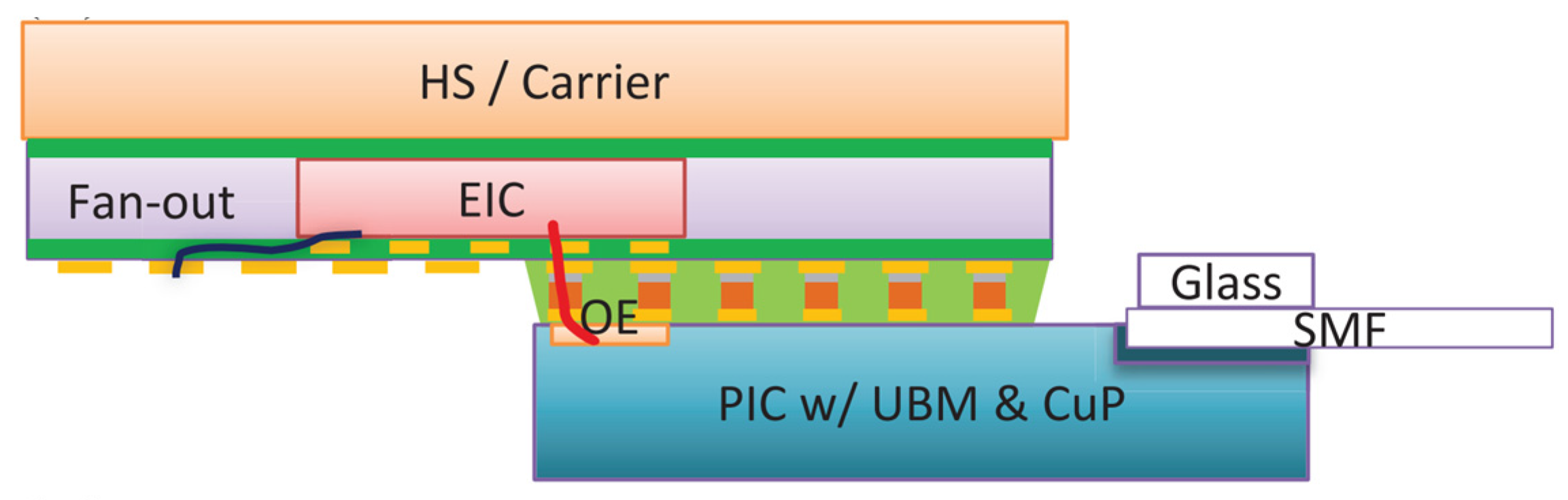

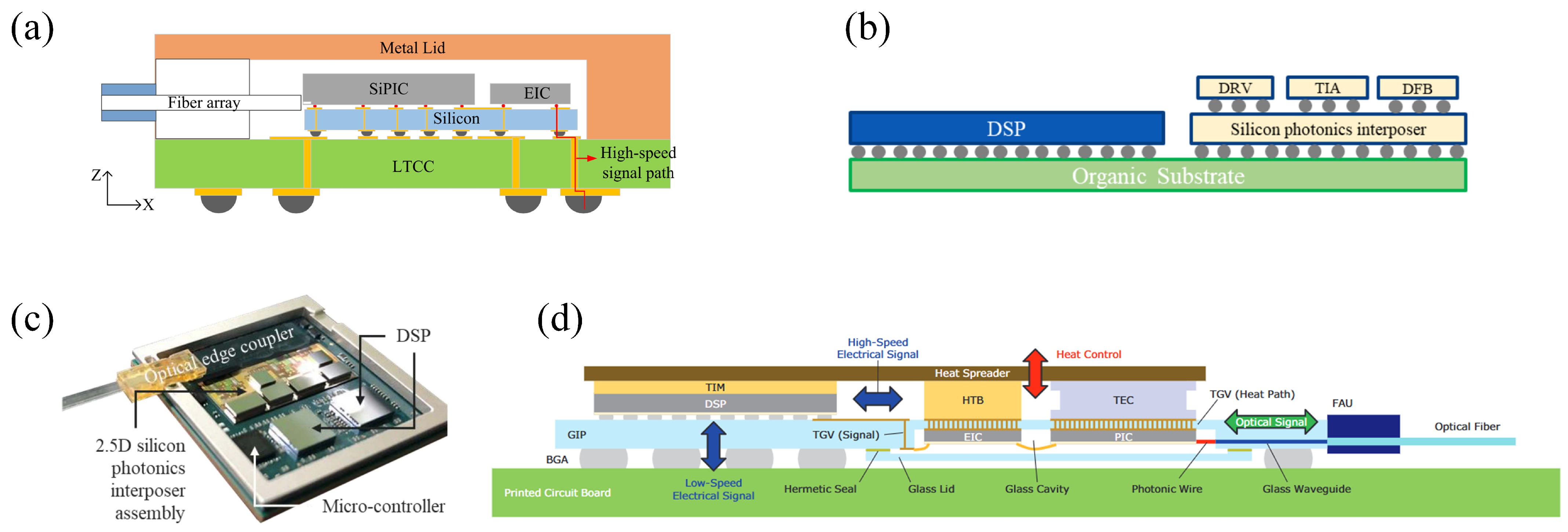

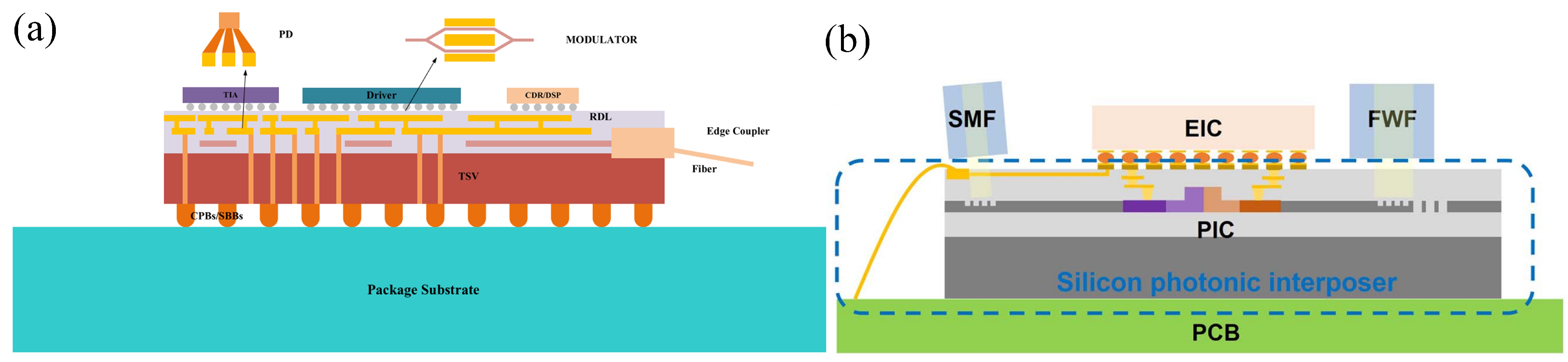

4.1. Two-Dimensional CPO

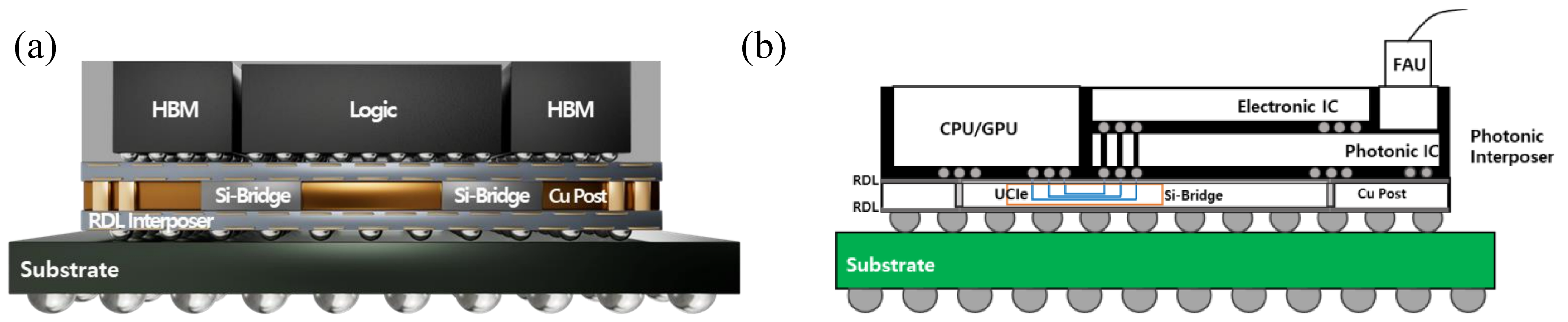

4.2. The 2.5D CPO

4.3. Three-Dimensional CPO

5. Challenges in Photonic Chip Packaging

5.1. Challenges in Optical Packaging

5.2. Challenges in Co-Packaged Optics

5.3. The Thermal Dissipation Challenges of Chips

5.4. Standardization of Packaging Design Rules

6. Summary and Outlook

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| CMOS | Complementary Metal-Oxide-Semiconductor |

| CPO | Co-packaged optics |

| D2NN | Diffractive deep neural network |

| DRC | Design Rule Check |

| EC | Edge coupler |

| EIC | Electronic Integrated Circuit |

| GC | Grating coupler |

| GIP | Glass interposer |

| IDNN | Integrated diffractive neural network |

| MNIST | Mixed National Institute of Standards and Technology database |

| MZM | Mach–Zehnder Modulator |

| NPO | Near-Package Optics |

| OBO | On-Board Optics |

| OE | Optical engine |

| OPA | Optical phased array |

| PDK | Packaging Design Kit |

| PDRs | Packaging design rules |

| PIC | Photonic Integrated Circuit |

| QSFP | Quad Small-Form-Factor Pluggable |

| SFP | Small-Form-Factor Pluggable |

| Si-PIC | Silicon Photonic Integrated Chip |

| SMF | Single-mode fiber |

| SOA | Semiconductor optical amplifier |

| SOI | Silicon-on-insulator |

| SWG | Sub-wavelength grating |

| TFLN | Thin-film Lithium Niobate |

| TSV | Through-silicon via |

References

- De Lima, T.F.; Peng, H.-T.; Tait, A.N.; Nahmias, M.A.; Miller, H.B.; Shastri, B.J.; Prucnal, P.R. Machine Learning With Neuromorphic Photonics. J. Light. Technol. 2019, 37, 1515–1534. [Google Scholar] [CrossRef]

- Tian, W.; Li, B.; Li, Z.; Cui, H.; Shi, J.; Wang, Y.; Zhao, J. Using Chiplet Encapsulation Technology to Achieve Processing-in-Memory Functions. Micromachines 2022, 13, 1790. [Google Scholar] [CrossRef]

- Siew, S.Y.; Li, B.; Gao, F.; Zheng, H.Y.; Zhang, W.; Guo, P.; Xie, S.W.; Song, A.; Dong, B.; Luo, L.W.; et al. Review of Silicon Photonics Technology and Platform Development. J. Light. Technol. 2021, 39, 4374–4389. [Google Scholar] [CrossRef]

- Shi, Y.; Zhang, Y.; Wan, Y.; Yu, Y.; Zhang, Y.; Hu, X.; Xiao, X.; Xu, H.; Zhang, L.; Pan, B. Silicon Photonics for High-Capacity Data Communications. Photonics Res. 2022, 10, A106–A134. [Google Scholar] [CrossRef]

- Xiang, C.; Jin, W.; Bowers, J.E. Silicon Nitride Passive and Active Photonic Integrated Circuits: Trends and Prospects. Photonics Res. 2022, 10, A82–A96. [Google Scholar] [CrossRef]

- Ji, X.; Liu, J.; He, J.; Wang, R.N.; Qiu, Z.; Riemensberger, J.; Kippenberg, T.J. Compact, Spatial-Mode-Interaction-Free, Ultralow-Loss, Nonlinear Photonic Integrated Circuits. Commun. Phys. 2022, 5, 84. [Google Scholar] [CrossRef]

- Ma, Y.; Zhao, J.; Yang, T.; Mei, Y.; Sun, Z.; Lu, J.; Li, S.; Ma, X.; Chen, X. Hybrid-Integrated 200 Gb/s REC-DML Array Transmitter Based on Photonic Wire Bonding Technology. Chin. Opt. Lett. 2024, 22, 081401. [Google Scholar] [CrossRef]

- Chen, S.; Li, W.; Wu, J.; Jiang, Q.; Tang, M.; Shutts, S.; Elliott, S.N.; Sobiesierski, A.; Seeds, A.J.; Ross, I.; et al. Electrically Pumped Continuous-Wave III–V Quantum Dot Lasers on Silicon. Nat. Photonics 2016, 10, 307–311. [Google Scholar] [CrossRef]

- Wang, C.; Li, Z.; Riemensberger, J.; Lihachev, G.; Churaev, M.; Kao, W.; Ji, X.; Zhang, J.; Blesin, T.; Davydova, A.; et al. Lithium Tantalate Photonic Integrated Circuits for Volume Manufacturing. Nature 2024, 629, 784–790. [Google Scholar] [CrossRef]

- Han, C.; Zheng, Z.; Shu, H.; Jin, M.; Qin, J.; Chen, R.; Tao, Y.; Shen, B.; Bai, B.; Yang, F.; et al. Slow-Light Silicon Modulator with 110-GHz Bandwidth. Sci. Adv. 2023, 9, eadi5339. [Google Scholar] [CrossRef]

- Maiti, R.; Patil, C.; Saadi, M.A.S.R.; Xie, T.; Azadani, J.G.; Uluutku, B.; Amin, R.; Briggs, A.F.; Miscuglio, M.; Van Thourhout, D.; et al. Strain-Engineered High-Responsivity MoTe2 Photodetector for Silicon Photonic Integrated Circuits. Nat. Photonics 2020, 14, 578–584. [Google Scholar] [CrossRef]

- Yin, J.; Liu, L.; Zang, Y.; Ying, A.; Hui, W.; Jiang, S.; Zhang, C.; Yang, T.; Chueh, Y.-L.; Li, J.; et al. Engineered Tunneling Layer with Enhanced Impact Ionization for Detection Improvement in Graphene/Silicon Heterojunction Photodetectors. Light Sci. Appl. 2021, 10, 113. [Google Scholar] [CrossRef] [PubMed]

- Guo, J.; Li, J.; Liu, C.; Yin, Y.; Wang, W.; Ni, Z.; Fu, Z.; Yu, H.; Xu, Y.; Shi, Y.; et al. High-Performance Silicon−graphene Hybrid Plasmonic Waveguide Photodetectors beyond 1.55 Μm. Light Sci. Appl. 2020, 9, 29. [Google Scholar] [CrossRef] [PubMed]

- Makvandi, M.; Maleki, M.; Soroosh, M. Compact All-Optical Encoder Based on Silicon Photonic Crystal Structure. J. Appl. Res. Electr. Eng. 2020, 1–7. [Google Scholar] [CrossRef]

- Dangel, R.; Hofrichter, J.; Horst, F.; Jubin, D.; La Porta, A.; Meier, N.; Soganci, I.M.; Weiss, J.; Offrein, B.J. Polymer Waveguides for Electro-Optical Integration in Data Centers and High-Performance Computers. Opt. Express 2015, 23, 4736. [Google Scholar] [CrossRef]

- Feldmann, J.; Youngblood, N.; Wright, C.D.; Bhaskaran, H.; Pernice, W.H.P. All-Optical Spiking Neurosynaptic Networks with Self-Learning Capabilities. Nature 2019, 569, 208–214. [Google Scholar] [CrossRef]

- Tait, A.N.; De Lima, T.F.; Zhou, E.; Wu, A.X.; Nahmias, M.A.; Shastri, B.J.; Prucnal, P.R. Neuromorphic Photonic Networks Using Silicon Photonic Weight Banks. Sci. Rep. 2017, 7, 7430. [Google Scholar] [CrossRef]

- Zhu, H.H.; Zou, J.; Zhang, H.; Shi, Y.Z.; Luo, S.B.; Wang, N.; Cai, H.; Wan, L.X.; Wang, B.; Jiang, X.D.; et al. Space-Efficient Optical Computing with an Integrated Chip Diffractive Neural Network. Nat. Commun. 2022, 13, 1044. [Google Scholar] [CrossRef]

- Chen, Z.; Sludds, A.; Davis, R., III; Christen, I.; Bernstein, L.; Ateshian, L.; Heuser, T.; Heermeier, N.; Lott, J.A.; Reitzenstein, S.; et al. Deep learning with coherent VCSEL neural networks. Nat. Photonics 2023, 17, 723–730. [Google Scholar] [CrossRef]

- He, J.; Dong, T.; Xu, Y. Review of Photonic Integrated Optical Phased Arrays for Space Optical Communication. IEEE Access 2020, 8, 188284–188298. [Google Scholar] [CrossRef]

- Ashtiani, F.; Aflatouni, F. N × N Optical Phased Array with 2N Phase Shifters. Opt. Express 2019, 27, 27183. [Google Scholar] [CrossRef]

- Liu, Y.; Hu, H. Silicon Optical Phased Array with a 180-Degree Field of View for 2D Optical Beam Steering. Optica 2022, 9, 903. [Google Scholar] [CrossRef]

- Shen, Y.; Harris, N.C.; Skirlo, S.; Prabhu, M.; Baehr-Jones, T.; Hochberg, M.; Sun, X.; Zhao, S.; Larochelle, H.; Englund, D.; et al. Deep Learning with Coherent Nanophotonic Circuits. Nat. Photonics 2017, 11, 441–446. [Google Scholar] [CrossRef]

- Liu, C.; Ma, Q.; Luo, Z.J.; Hong, Q.R.; Xiao, Q.; Zhang, H.C.; Miao, L.; Yu, W.M.; Cheng, Q.; Li, L.; et al. A Programmable Diffractive Deep Neural Network Based on a Digital-Coding Metasurface Array. Nat. Electron. 2022, 5, 113–122. [Google Scholar] [CrossRef]

- Altug, H.; Oh, S.-H.; Maier, S.A.; Homola, J. Advances and Applications of Nanophotonic Biosensors. Nat. Nanotechnol. 2022, 17, 5–16. [Google Scholar] [CrossRef] [PubMed]

- You, X.; Wang, C.-X.; Huang, J.; Gao, X.; Zhang, Z.; Wang, M.; Huang, Y.; Zhang, C.; Jiang, Y.; Wang, J.; et al. Towards 6G Wireless Communication Networks: Vision, Enabling Technologies, and New Paradigm Shifts. Sci. China Inf. Sci. 2021, 64, 110301. [Google Scholar] [CrossRef]

- Marchetti, R.; Lacava, C.; Carroll, L.; Gradkowski, K.; Minzioni, P. Coupling Strategies for Silicon Photonics Integrated Chips [Invited]. Photonics Res. 2019, 7, 201–239. [Google Scholar] [CrossRef]

- Mu, X.; Wu, S.; Cheng, L.; Fu, H.Y. Edge Couplers in Silicon Photonic Integrated Circuits: A Review. Appl. Sci. 2020, 10, 1538. [Google Scholar] [CrossRef]

- Hsia, H.; Tsai, C.H.; Ting, K.C.; Kuo, F.W.; Lin, C.C.; Wang, C.T.; Hou, S.Y.; Chiou, W.C.; Yu, D.C.H. Heterogeneous Integration of a Compact Universal Photonic Engine for Silicon Photonics Applications in HPC. In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 1 June–4 July 2021; IEEE: New York, NY, USA, 2021; pp. 263–268. [Google Scholar]

- Ren, G.; Chen, S.; Cheng, Y.; Zhai, Y. Study on Inverse Taper Based Mode Transformer for Low Loss Coupling between Silicon Wire Waveguide and Lensed Fiber. Opt. Commun. 2011, 284, 4782–4788. [Google Scholar] [CrossRef]

- Wang, J.; Xuan, Y.; Lee, C.; Niu, B.; Liu, L.; Liu, G.N.; Qi, M. Low-Loss and Misalignment-Tolerant Fiber-to-Chip Edge Coupler Based on Double-Tip Inverse Tapers. In Proceedings of the Optical Fiber Communication Conference, Anaheim, CA, USA, 20–24 March 2016; OSA: Washington, DC, USA, 2016; p. M2I.6. [Google Scholar]

- Tu, Y.-C.; Fu, P.-H.; Huang, D.-W. High-Efficiency Ultra-Broadband Multi-Tip Edge Couplers for Integration of Distributed Feedback Laser With Silicon-on-Insulator Waveguide. IEEE Photonics J. 2019, 11, 6602113. [Google Scholar] [CrossRef]

- Sun, S.; Chen, Y.; Sun, Y.; Liu, F.; Cao, L. Novel Low-Loss Fiber-Chip Edge Coupler for Coupling Standard Single Mode Fibers to Silicon Photonic Wire Waveguides. Photonics 2021, 8, 79. [Google Scholar] [CrossRef]

- Brunetti, G.; Heuvink, R.; Schreuder, E.; Armenise, M.N.; Ciminelli, C. Silicon Nitride Spot Size Converter With Very Low-Loss Over the C-Band. IEEE Photonics Technol. Lett. 2023, 35, 1215–1218. [Google Scholar] [CrossRef]

- Xu, L.; Wang, Y.; Mao, D.; Zhang, J.; Xing, Z.; El-Fiky, E.; Saber, M.G.; Kumar, A.; D’Mello, Y.; Jacques, M.; et al. Ultra-Broadband and Compact Two-Mode Multiplexer Based on Subwavelength-Grating-Slot-Assisted Adiabatic Coupler for the Silicon-on-Insulator Platform. J. Light. Technol. 2019, 37, 5790–5800. [Google Scholar] [CrossRef]

- He, A.; Guo, X.; Wang, T.; Su, Y. Ultracompact Fiber-to-Chip Metamaterial Edge Coupler. ACS Photonics 2021, 8, 3226–3233. [Google Scholar] [CrossRef]

- Xiao, Y.; Xu, Y.; Dong, Y.; Zhang, B.; Ni, Y. A 60 Μm-Long Fiber-to-Chip Edge Coupler Assisted by Subwavelength Grating Structure with Ultralow Loss and Large Bandwidth. Photonics 2022, 9, 413. [Google Scholar] [CrossRef]

- Lin, Y.; Mak, J.C.C.; Chen, H.; Mu, X.; Stalmashonak, A.; Jung, Y.; Luo, X.; Lo, P.G.-Q.; Sacher, W.D.; Poon, J.K.S. Low-Loss Broadband Bi-Layer Edge Couplers for Visible Light. Opt. Express 2021, 29, 34565. [Google Scholar] [CrossRef] [PubMed]

- Zhu, X.; Li, G.; Wang, X.; Li, Y.; Davidson, R.; Little, B.E.; Chu, S.T. Low-Loss Fiber-to-Chip Edge Coupler for Silicon Nitride Integrated Circuits. Opt. Express 2023, 31, 10525. [Google Scholar] [CrossRef]

- Yu, Z.; Yin, Y.; Huang, X.; Tu, D.; Yu, H.; Guan, H.; Jiang, L.; Yan, W.; Li, Z. Silicon Nitride Assisted Tri-Layer Edge Coupler on Lithium Niobate-on-Insulator Platform. Opt. Lett. 2023, 48, 3367. [Google Scholar] [CrossRef] [PubMed]

- Hu, C.; Pan, A.; Li, T.; Wang, X.; Liu, Y.; Tao, S.; Zeng, C.; Xia, J. High-Efficient Coupler for Thin-Film Lithium Niobate Waveguide Devices. Opt. Express 2021, 29, 5397. [Google Scholar] [CrossRef] [PubMed]

- Kopp, C.; Bernabé, S.; Bakir, B.B.; Fedeli, J.; Orobtchouk, R.; Schrank, F.; Porte, H.; Zimmermann, L.; Tekin, T. Silicon Photonic Circuits: On-CMOS Integration, Fiber Optical Coupling, and Packaging. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 498–509. [Google Scholar] [CrossRef]

- Zhou, X.; Wang, Y.; Zhang, Z.; Tsang, H.K. Resonance-Enhanced Wideband Grating for Efficient Perfectly Vertical Coupling. IEEE Photonics Technol. Lett. 2024, 36, 555–558. [Google Scholar] [CrossRef]

- Chen, J.-H.; Bouamra, A.D.; Wu, C.-L.; Fiore, A.; Tseng, S.-Y. High-Tolerance Grating Couplers for Vertical Backside Coupling. Appl. Sci. 2024, 14, 11015. [Google Scholar] [CrossRef]

- Hong, J.; Qiu, F.; Spring, A.M.; Yokoyama, S. Silicon Waveguide Grating Coupler Based on a Segmented Grating Structure. Appl. Opt. 2018, 57, 3301. [Google Scholar] [CrossRef]

- Yu, J.; Yamada, H. Design and Investigation of a Dual-Layer Grating Coupler for Efficient Vertical Fiber-Chip Coupling. Appl. Phys. Express 2019, 12, 012004. [Google Scholar] [CrossRef]

- Sikder, R.I.; Fasih, M.; Kim, J.-Y.; Park, H.-H.; Yoon, H.; Kurt, H. Grating Coupler Using Angle-Polished Optical Fiber. In Proceedings of the Nanophotonics, Micro/Nano Optics, and Plasmonics VIII, Beijing, China, 14–16 October 2022; Zhou, Z., Wada, K., Tong, L., Fang, Z., Tanaka, T., Eds.; SPIE: Bellingham, WA, USA, 2023; p. 25. [Google Scholar]

- Yu, L.; Liu, L.; Zhou, Z.; Wang, X. High Efficiency Binary Blazed Grating Coupler for Perfectly-Vertical and near-Vertical Coupling in Chip Level Optical Interconnections. Opt. Commun. 2015, 355, 161–166. [Google Scholar] [CrossRef]

- Lomonte, E.; Stappers, M.; Lenzini, F.; Pernice, W. Highly Efficient Silicon Nitride Grating Couplers with Metal Back-Reflector Enabled by Cryogenic Deep Silicon Etching. In Proceedings of the Integrated Photonics Platforms II, Strasbourg, France, 4–7 April 2022; Baets, R.G., O’Brien, P., Vivien, L., Eds.; SPIE: Bellingham, WA, USA, 2022; p. 4. [Google Scholar]

- Lindenmann, N.; Balthasar, G.; Hillerkuss, D.; Schmogrow, R.; Jordan, M.; Leuthold, J.; Freude, W.; Koos, C. Photonic Wire Bonding: A Novel Concept for Chip-Scale Interconnects. Opt. Express 2012, 20, 17667. [Google Scholar] [CrossRef]

- Rhee, H.-W.; You, J.B.; Kim, J.; Kim, H.; Kim, M.; Kim, C.K.; Park, H.-H. Chip-to-Chip Optical Interconnect Using Direct Optical Wire Bonding. In Proceedings of the Optical Interconnects XXII, San Francisco, CA, USA, 22–27 January 2022; Schröder, H., Chen, R.T., Eds.; SPIE: Bellingham, WA, USA, 2022; p. 41. [Google Scholar]

- Rhee, H.-W.; Shim, J.; Kim, J.-Y.; Bang, D.J.; Yoon, H.; Kim, M.; Kim, C.C.; You, J.-B.; Park, H.-H. Direct Optical Wire Bonding through Open-to-Air Polymerization for Silicon Photonic Chips. Opt. Lett. 2022, 47, 714. [Google Scholar] [CrossRef]

- Shekhar, S.; Bogaerts, W.; Chrostowski, L.; Bowers, J.E.; Hochberg, M.; Soref, R.; Shastri, B.J. Roadmapping the next Generation of Silicon Photonics. Nat. Commun. 2024, 15, 751. [Google Scholar] [CrossRef]

- Lindenmann, N.; Dottermusch, S.; Goedecke, M.L.; Hoose, T.; Billah, M.R.; Onanuga, T.P.; Hofmann, A.; Freude, W.; Koos, C. Connecting Silicon Photonic Circuits to Multicore Fibers by Photonic Wire Bonding. J. Light. Technol. 2015, 33, 755–760. [Google Scholar] [CrossRef]

- Gu, Z.; Amemiya, T.; Ishikawa, A.; Hiratani, T.; Suzuki, J.; Nishiyama, N.; Tanaka, T.; Arai, S. Optical Transmission between III-V Chips on Si Using Photonic Wire Bonding. Opt. Express 2015, 23, 22394. [Google Scholar] [CrossRef] [PubMed]

- Zvagelsky, R.D.; Chubich, D.A.; Kolymagin, D.A.; Korostylev, E.V.; Kovalyuk, V.V.; Prokhodtsov, A.I.; Tarasov, A.V.; Goltsman, G.N.; Vitukhnovsky, A.G. Three-Dimensional Polymer Wire Bonds on a Chip: Morphology and Functionality. J. Phys. Appl. Phys. 2020, 53, 355102. [Google Scholar] [CrossRef]

- Blaicher, M.; Billah, M.R.; Kemal, J.; Hoose, T.; Marin-Palomo, P.; Hofmann, A.; Kutuvantavida, Y.; Kieninger, C.; Dietrich, P.-I.; Lauermann, M.; et al. Hybrid Multi-Chip Assembly of Optical Communication Engines by in Situ 3D Nano-Lithography. Light Sci. Appl. 2020, 9, 71. [Google Scholar] [CrossRef]

- Moughames, J.; Porte, X.; Thiel, M.; Ulliac, G.; Larger, L.; Jacquot, M.; Kadic, M.; Brunner, D. Three-Dimensional Waveguide Interconnects for Scalable Integration of Photonic Neural Networks. Optica 2020, 7, 640. [Google Scholar] [CrossRef]

- Billah, M.R.; Blaicher, M.; Hoose, T.; Dietrich, P.-I.; Marin-Palomo, P.; Lindenmann, N.; Nesic, A.; Hofmann, A.; Troppenz, U.; Moehrle, M.; et al. Hybrid Integration of Silicon Photonics Circuits and InP Lasers by Photonic Wire Bonding. Optica 2018, 5, 876. [Google Scholar] [CrossRef]

- Xu, Y.; Maier, P.; Blaicher, M.; Dietrich, P.-I.; Marin-Palomo, P.; Hartmann, W.; Bao, Y.; Peng, H.; Billah, M.R.; Singer, S.; et al. Hybrid External-Cavity Lasers (ECL) Using Photonic Wire Bonds as Coupling Elements. Sci. Rep. 2021, 11, 16426. [Google Scholar] [CrossRef]

- Franken, C.A.A.; Cheng, R.; Powell, K.; Kyriazidis, G.; Rosborough, V.; Musolf, J.; Shah, M.; Barton, D.R.; Hills, G.; Johansson, L.; et al. High-Power and Narrow-Linewidth Laser on Thin-Film Lithium Niobate Enabled by Photonic Wire Bonding. APL Photonics 2025, 10, 026107. [Google Scholar] [CrossRef]

- Lin, B.; Witt, D.; Young, J.F.; Chrostowski, L. Cryogenic Optical Packaging Using Photonic Wire Bonds. APL Photonics 2023, 8, 126109. [Google Scholar] [CrossRef]

- Li, Z.; Tian, W.; Huang, S.; Chen, Z.; Wang, Y. Analysis and Optimization of Cu/SiO2 Hybrid Bonding Interfacial Reliability Based on FEA and GABP-NSGA II Algorithm. Mater. Sci. Semicond. Process. 2025, 198, 109782. [Google Scholar] [CrossRef]

- Hsia, H.; Tai, S.P.; Liu, C.S.; Tseng, C.W.; Lu, S.W.; Wu, Y.; Chang, C.C.; Wu, J.; Yee, K.C.; Wu, C.Y.; et al. Integrated Optical Interconnect Systems (iOIS) for Silicon Photonics Applications in HPC. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; IEEE: New York, NY, USA, 2023; pp. 612–616. [Google Scholar]

- Lau, J.H. Co-Packaged Optics—Heterogeneous Integration of Photonic Integrated Circuits and Electronic Integrated Circuits. J. Electron. Packag. 2025, 147, 011004. [Google Scholar] [CrossRef]

- Tian, W.; Hou, H.; Dang, H.; Cao, X.; Li, D.; Chen, S.; Ma, B. Progress in Research on Co-Packaged Optics. Micromachines 2024, 15, 1211. [Google Scholar] [CrossRef]

- Minkenberg, C.; Krishnaswamy, R.; Zilkie, A.; Nelson, D. Co-packaged Datacenter Optics: Opportunities and Challenges. IET Optoelectron. 2021, 15, 77–91. [Google Scholar] [CrossRef]

- Maniotis, P.; Schares, L.; Lee, B.G.; Taubenblatt, M.A.; Kuchta, D.M. Toward Lower-Diameter Large-Scale HPC and Data Center Networks with Co-Packaged Optics. J. Opt. Commun. Netw. 2021, 13, A67. [Google Scholar] [CrossRef]

- Chou, B.; Sawyer, B.M.; Lyu, G.; Timurdugan, E.; Minkenberg, C.; Zilkie, A.J.; McCann, D. Demonstration of Fan-out Silicon Photonics Module for Next Generation Co-Packaged Optics (CPO) Application. In Proceedings of the 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–3 June 2022; IEEE: New York, NY, USA, 2022; pp. 394–402. [Google Scholar]

- He, H.; Xue, H.; Sun, Y.; Liu, F.; Cao, L. Design and Realization of Multi-Channel and High-Bandwidth 2.5D Transmitter Integrated With Silicon Photonic MZM. J. Light. Technol. 2022, 40, 5201–5215. [Google Scholar] [CrossRef]

- Nagarajan, R.; Ding, L.; Coccioli, R.; Kato, M.; Tan, R.; Tumne, P.; Patterson, M.; Liu, L. 2.5D Heterogeneous Integration for Silicon Photonics Engines in Optical Transceivers. IEEE J. Sel. Top. Quantum Electron. 2023, 29, 8200209. [Google Scholar] [CrossRef]

- Tian, W.; Wu, S.; Li, W. Research of Vertical via Based on Silicon, Ceramic and Glass. Micromachines 2023, 14, 1391. [Google Scholar] [CrossRef]

- Uemura, H.; Misawa, T.; Mizuno, Y.; Itabashi, N.; Arao, H.; Nakanishi, T.; Tanaka, K.; Sano, T.; Uesaka, K.; Miyairi, M.; et al. A Surface-Mount Photonic Package with a Photonic-Wire-Bonded Glass Interposer as a Hybrid Integration Platform for Co-Packaged Optics. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; IEEE: New York, NY, USA, 2024; pp. 90–95. [Google Scholar]

- Fotouhi, P.; Werner, S.; Lowe-Power, J.; Yoo, S.J.B. Enabling Scalable Chiplet-Based Uniform Memory Architectures with Silicon Photonics. In Proceedings of the International Symposium on Memory Systems, Washington, DC, USA, 30 September–3 October 2019; ACM: New York, NY, USA, 2019; pp. 222–334. [Google Scholar]

- Shi, L.-F.; Tan, X.-L.; Xin, D.-J.; Hou, Z.-Y. Optimization Design of Fixed-Length Bond-Wire Interconnection in Multichips Module. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 9, 2290–2297. [Google Scholar] [CrossRef]

- Zheng, Q.; Yang, P.; Xue, H.; He, H.; Cao, R.; Dai, F.; Sun, S.; Liu, F.; Wang, Q.; Cao, L.; et al. Research on 3D Optical Module Integrating Edge Coupler and TSV. J. Light. Technol. 2022, 40, 6190–6200. [Google Scholar] [CrossRef]

- Wang, X.; Du, J.; Shen, W.; Xu, K.; He, Z. High-Density MDM-WDM Silicon Photonic Transmitter Chiplet Based on MRMs and Dual-Mode GC for 4 × 56 Gbps 3D Co-Packaged Optical Interconnects. Chin. Opt. Lett. 2024, 22, 120001. [Google Scholar] [CrossRef]

- Prasad, A.; Muzio, C.; Ton, P.; Razdaan, S. Advanced 3D Packaging of 3.2Tbs Optical Engine for Co-Packaged Optics (CPO) in Hyperscale Data Center Networks. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; IEEE: New York, NY, USA; pp. 101–106. [Google Scholar]

- Kannan, S.; Chang, R.; Potluri, H.; Zhang, S.; Li, J.; Xu, B.; Hsu, H.-C. High Density Integration of Silicon Photonic Chiplets for 51.2T Co-Packaged Optics. In Proceedings of the 2024 IEEE 74th Electronic Components and Technology Conference (ECTC), Denver, CO, USA, 28–31 May 2024; IEEE: New York, NY, USA; pp. 81–84. [Google Scholar]

- Zhang, Y.; Tian, W.; Wang, H.; Wang, L.; Yang, Z.; Shao, W.; Chen, Z.; Zhou, B. High-Frequency Transmission Characteristic Analysis of TSV-RDL Interconnects. IEEE Trans. Compon. Packag. Manuf. Technol. 2024, 14, 89–97. [Google Scholar] [CrossRef]

- Shin, J.; Eslampour, H.; Jeong, S.; Kim, W.; Yong, S.; Ahn, S.-O.; Park, E.; Song, S. Signal Integrity of Die-to-Die Interface with Advanced Packages for Co-Packaged Optics. In Proceedings of the 2024 IEEE 33rd Conference on Electrical Performance of Electronic Packaging and Systems (EPEPS), Toronto, ON, Canada, 6–9 October 2024; IEEE: New York, NY, USA; pp. 1–3. [Google Scholar]

- Jiang, W.; Miao, J.; Li, T. Compact Silicon 10-Mode Multi/Demultiplexer for Hybrid Mode- and Polarisation-Division Multiplexing System. Sci. Rep. 2019, 9, 13223. [Google Scholar] [CrossRef]

- Barwicz, T.; Peng, B.; Leidy, R.; Janta-Polczynski, A.; Houghton, T.; Khater, M.; Kamlapurkar, S.; Engelmann, S.; Fortier, P.; Boyer, N.; et al. Integrated Metamaterial Interfaces for Self-Aligned Fiber-to-Chip Coupling in Volume Manufacturing. IEEE J. Sel. Top. Quantum Electron. 2019, 25, 4700313. [Google Scholar] [CrossRef]

- Ranno, L.; Gupta, P.; Gradkowski, K.; Bernson, R.; Weninger, D.; Serna, S.; Agarwal, A.M.; Kimerling, L.C.; Hu, J.; OBrien, P. Integrated Photonics Packaging: Challenges and Opportunities. ACS Photonics 2022, 9, 3467–3485. [Google Scholar] [CrossRef]

- Pavarelli, N.; Lee, J.S.; Rensing, M.; Scarcella, C.; Zhou, S.; Ossieur, P.; OBrien, P.A. Optical and Electronic Packaging Processes for Silicon Photonic Systems. J. Light. Technol. 2015, 33, 991–997. [Google Scholar] [CrossRef]

- Pavesi, L.; Lockwood, D.J. (Eds.) Silicon Photonics III: Systems and Applications; Topics in Applied Physics; Springer: Berlin/Heidelberg, Germany, 2016; Volume 122, ISBN 978-3-642-10502-9. [Google Scholar]

- Mahajan, R.; Li, X.; Fryman, J.; Zhang, Z.; Nekkanty, S.; Tadayon, P.; Jaussi, J.; Shumarayev, S.; Agrawal, A.; Jadhav, S.; et al. Co-Packaged Photonics For High Performance Computing: Status, Challenges And Opportunities. J. Light. Technol. 2022, 40, 379–392. [Google Scholar] [CrossRef]

- Tian, W.; Dang, H.; Li, D.; Cong, Y.; Chen, Y. Reliability Simulation Analysis of TSV Structure in Silicon Interposer under Temperature Cycling. Micromachines 2024, 15, 986. [Google Scholar] [CrossRef]

- Carroll, L.; Lee, J.-S.; Scarcella, C.; Gradkowski, K.; Duperron, M.; Lu, H.; Zhao, Y.; Eason, C.; Morrissey, P.; Rensing, M.; et al. Photonic Packaging: Transforming Silicon Photonic Integrated Circuits into Photonic Devices. Appl. Sci. 2016, 6, 426. [Google Scholar] [CrossRef]

- Gupta, R.; Kumar, A.; Kumar, M.; Singh, R.; Gehlot, A.; Pandey, P.S.; Yadav, N.; Pandey, K.; Yadav, A.; Gupta, N.; et al. The Integration of Microelectronic and Photonic Circuits on a Single Silicon Chip for High-Speed and Low-Power Optoelectronic Technology. Nano Mater. Sci. 2025, 7, 305–315. [Google Scholar] [CrossRef]

- Snigirev, V.; Riedhauser, A.; Lihachev, G.; Churaev, M.; Riemensberger, J.; Wang, R.N.; Siddharth, A.; Huang, G.; Möhl, C.; Popoff, Y.; et al. Ultrafast Tunable Lasers Using Lithium Niobate Integrated Photonics. Nature 2023, 615, 411–417. [Google Scholar] [CrossRef]

- Wei, W.-Q.; He, A.; Yang, B.; Wang, Z.-H.; Huang, J.-Z.; Han, D.; Ming, M.; Guo, X.; Su, Y.; Zhang, J.-J.; et al. Monolithic Integration of Embedded III-V Lasers on SOI. Light Sci. Appl. 2023, 12, 84. [Google Scholar] [CrossRef]

- Zhang, P.; Huang, H.; Jiang, Y.; Han, X.; Xiao, H.; Frigg, A.; Nguyen, T.G.; Boes, A.; Ren, G.; Su, Y.; et al. High-Speed Electro-Optic Modulator Based on Silicon Nitride Loaded Lithium Niobate on an Insulator Platform. Opt. Lett. 2021, 46, 5986. [Google Scholar] [CrossRef]

- Liu, X.; Xiong, B.; Sun, C.; Wang, J.; Hao, Z.; Wang, L.; Han, Y.; Li, H.; Yu, J.; Luo, Y. Wideband Thin-Film Lithium Niobate Modulator with Low Half-Wave-Voltage Length Product. Chin. Opt. Lett. 2021, 19, 060016. [Google Scholar] [CrossRef]

- Wang, X.-X.; Zeng, G.; Yu, Q.-J.; Shen, L.; Shi, C.-Y.; Lu, H.-L. Photodetectors Integrating Waveguides and Semiconductor Materials. Nanoscale 2024, 16, 5504–5520. [Google Scholar] [CrossRef]

- Li, X.; Peng, L.; Liu, Z.; Zhou, Z.; Zheng, J.; Xue, C.; Zuo, Y.; Chen, B.; Cheng, B. 30 GHz GeSn Photodetector on SOI Substrate for 2 Μm Wavelength Application. Photonics Res. 2021, 9, 494–500. [Google Scholar] [CrossRef]

- Bernson, R.; Witte, A.; Clark, G.; Saha, M.; Zimmermann, M.; Leenheer, A.; Chen, K.C.; Gilbert, G.; Englund, D.; O’Brien, P. Scalable Low Loss Cryogenic Packaging of Quantum Memories in CMOS-Foundry Processed Photonic Chips. arXiv 2025, arXiv:2503.14704. [Google Scholar]

- Maghrabie, H.M.; Olabi, A.G.; Sayed, E.T.; Wilberforce, T.; Elsaid, K.; Doranehgard, M.H.; Abdelkareem, M.A. Microchannel Heat Sinks with Nanofluids for Cooling Electronic Components: Performance Enhancement, Challenges, and Limitations. Therm. Sci. Eng. Prog. 2023, 37, 101608. [Google Scholar] [CrossRef]

| Name | Platform | Bandwidth (GHz) | Coupling Loss | Alignment Tolerance |

|---|---|---|---|---|

| Fiber-to-chip edge coupler based on double-tip inverse tapers [31] | SOI | 1480–1630 nm | 1.10 dB (TE) 1.52 dB (TM) | X ± 1.25 µm (3 dB) Y ± 0.95 µm (3 dB) |

| Multi-tip edge coupler [32] | SOI | 1260–1675 nm | 0.4249 dB (1550 nm) | horizontal direction ± 0.77 μm (1 dB) vertical direction ± 0.41 μm (1 dB) |

| Novel low-loss fiber-chip edge coupler [33] | SiN | 1550 nm ± 50 nm | 0.44 dB (TE) 0.04–0.08 dB (TM) | 2.8 μm |

| Silicon nitride spot-size converter with very low loss over the C-band [34] | SiN | 1530–1570 nm | 0.18 dB | N/A |

| Two-mode multiplexer based on subwavelength grating slot-assisted adiabatic coupler [35] | SOI | 1260–2000 nm (simulation) 1260–1360 nm (measurement) 1500–1630 nm (measurement) | 0.32 dB (simulation) 2.6 dB (measurement) | 20 nm (0.76 dB) |

| SWG metamaterial edge coupler [36] | SOI | 1508–1628 nm | 2.22 dB (TE) 2.53 dB (TM) | ±10 nm |

| Fiber-to-chip edge coupler assisted by SWG [37] | SOI | 240 nm | 0.23 dB | −40–200 nm (0.5 dB) |

| Low-loss broadband bi-layer edge couplers [38] | SiN | 445–640 nm | 4 dB | X ± 0.88 µm (1 dB) Y ± 1.15 µm (1 dB) |

| Low-loss fiber-to-chip edge coupler for silicon nitride integrated circuits [39] | SiN | 1525–1630 nm | 0.8 dB | ±2 μm (1 dB) |

| Silicon-nitride-assisted tri-layer edge coupler [40] | LNOI | N/A | 0.64 dB | ±3.1 μm (0.5 dB) |

| Highly efficient, polarization-independent edge coupler based on LNOI [41] | LNOI | 1527–1630 nm | 1 dB | ±1 μm (0.6 dB) |

| Name | Platform | Bandwidth (GHz) | Coupling Loss |

|---|---|---|---|

| Segmented-waveguide grating coupler [45] | SOI | 71.4 nm, (covers the entire C-band) | 2.86 dB |

| Dual-layer grating coupler [46] | Si-SiN | 34 nm (1.56 μm, TM) 49 nm (1.56 μm, TE) 47 nm (1.32 μm, TM) | 4.83 dB (1.56 μm, TM) 3.87 dB (1.56 μm, TE) 5.68 dB (1.32 μm, TM) |

| Two-layer grating coupler [47] | SOI | 203 nm (1540 nm, chip-to-fiber) 62 nm (1550 nm, fiber-to-chip) | 0.97 dB (1540 nm, chip-to-fiber) 1.54 dB (1550 nm, fiber-to-chip) |

| PVBGC [43] | SOI | 147 nm (3 dB) 121 nm (1 dB) | 3.78 dB (simulation) 4.6 dB (experiment) |

| Nearly vertical binary blazed grating coupler [48] | SOI | 42 nm (1 dB) 68 nm (3 dB) | 90% (coupling efficiency) |

| Silicon grating coupler for vertical backside coupling [44] | SiN | 20 nm (1 dB) | 3.97 dB |

| Grating couplers with metal back-reflector [49] | SiN | 100 nm | 0.61 dB (TE) 0.95 dB (TM) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tian, W.; Wang, Y.; Dang, H.; Hou, H.; Xi, Y. Photonic Integrated Circuits: Research Advances and Challenges in Interconnection and Packaging Technologies. Photonics 2025, 12, 821. https://doi.org/10.3390/photonics12080821

Tian W, Wang Y, Dang H, Hou H, Xi Y. Photonic Integrated Circuits: Research Advances and Challenges in Interconnection and Packaging Technologies. Photonics. 2025; 12(8):821. https://doi.org/10.3390/photonics12080821

Chicago/Turabian StyleTian, Wenchao, Yifan Wang, Haojie Dang, Huahua Hou, and Yuanyuan Xi. 2025. "Photonic Integrated Circuits: Research Advances and Challenges in Interconnection and Packaging Technologies" Photonics 12, no. 8: 821. https://doi.org/10.3390/photonics12080821

APA StyleTian, W., Wang, Y., Dang, H., Hou, H., & Xi, Y. (2025). Photonic Integrated Circuits: Research Advances and Challenges in Interconnection and Packaging Technologies. Photonics, 12(8), 821. https://doi.org/10.3390/photonics12080821