Large-Scale Reconfigurable Integrated Circuits for Wideband Analog Photonic Computing

Abstract

1. Introduction

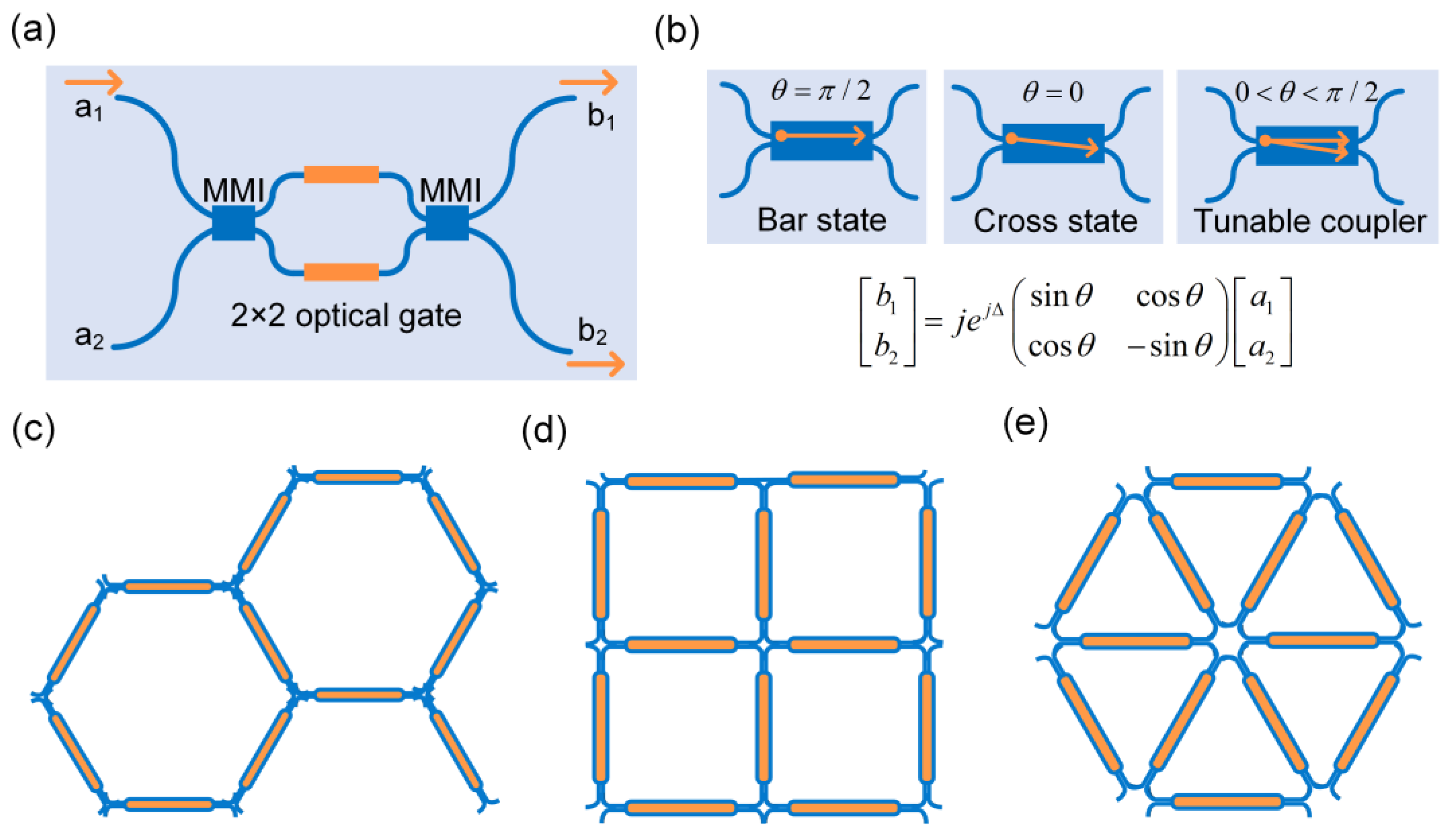

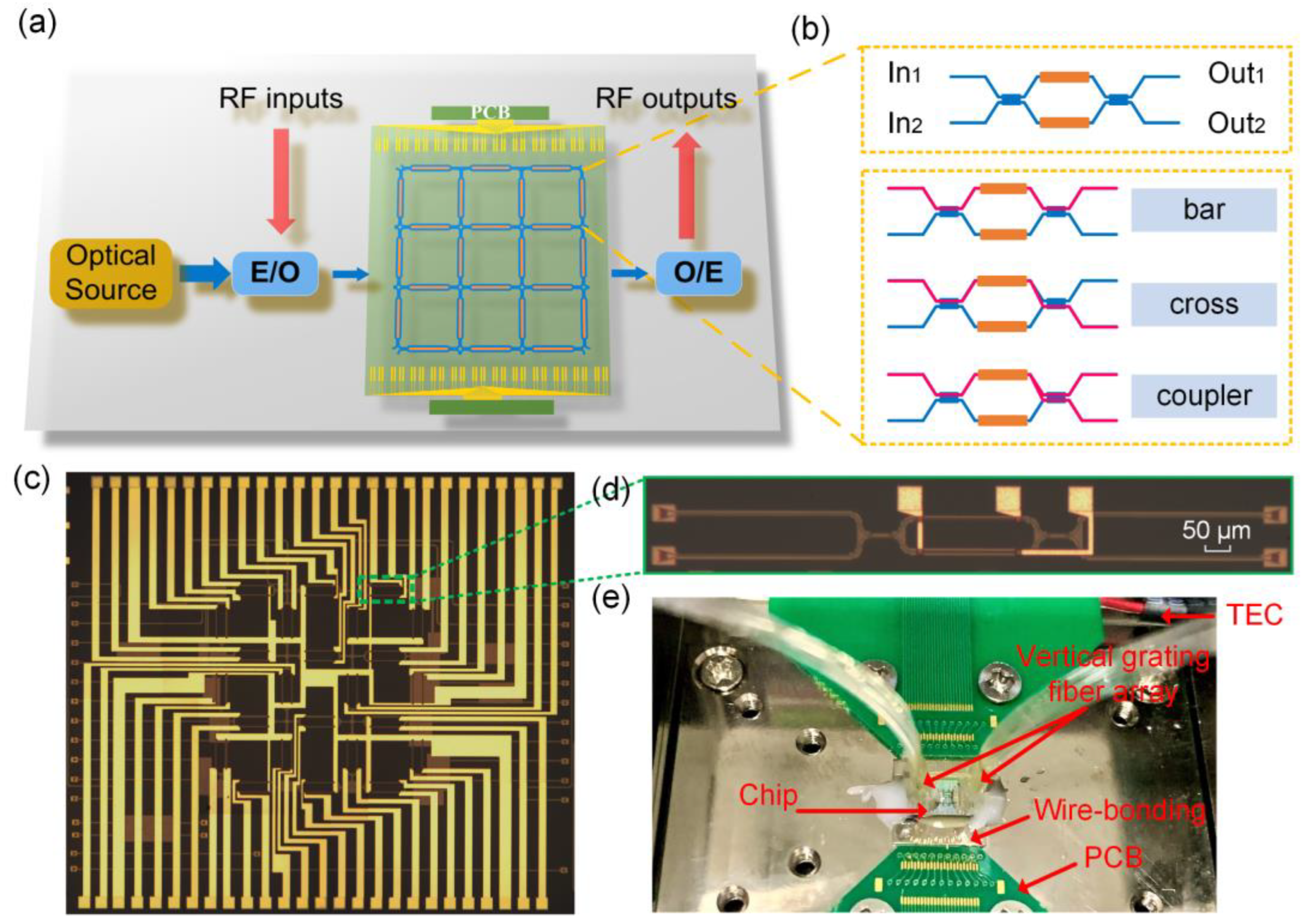

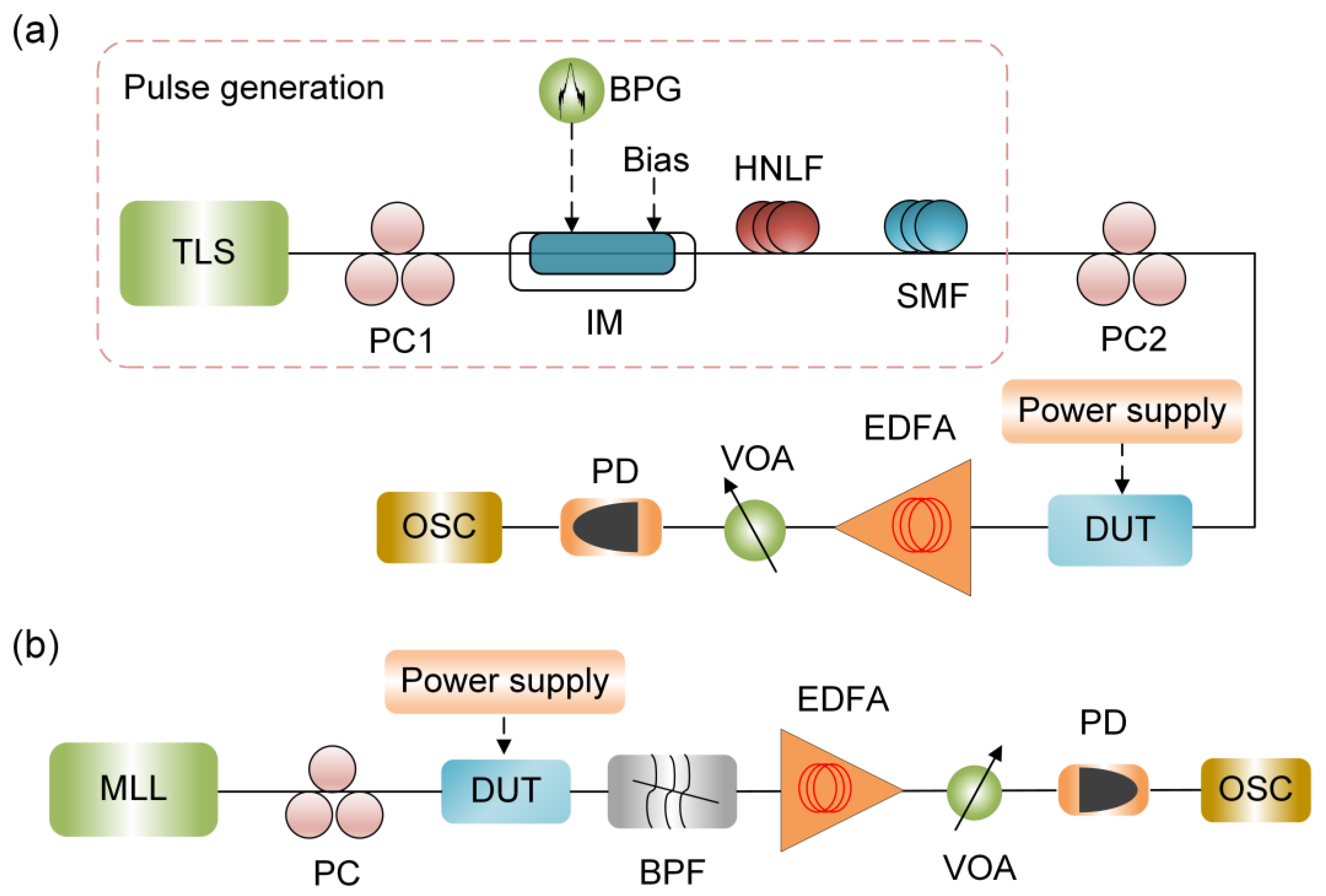

2. Methods

3. Results

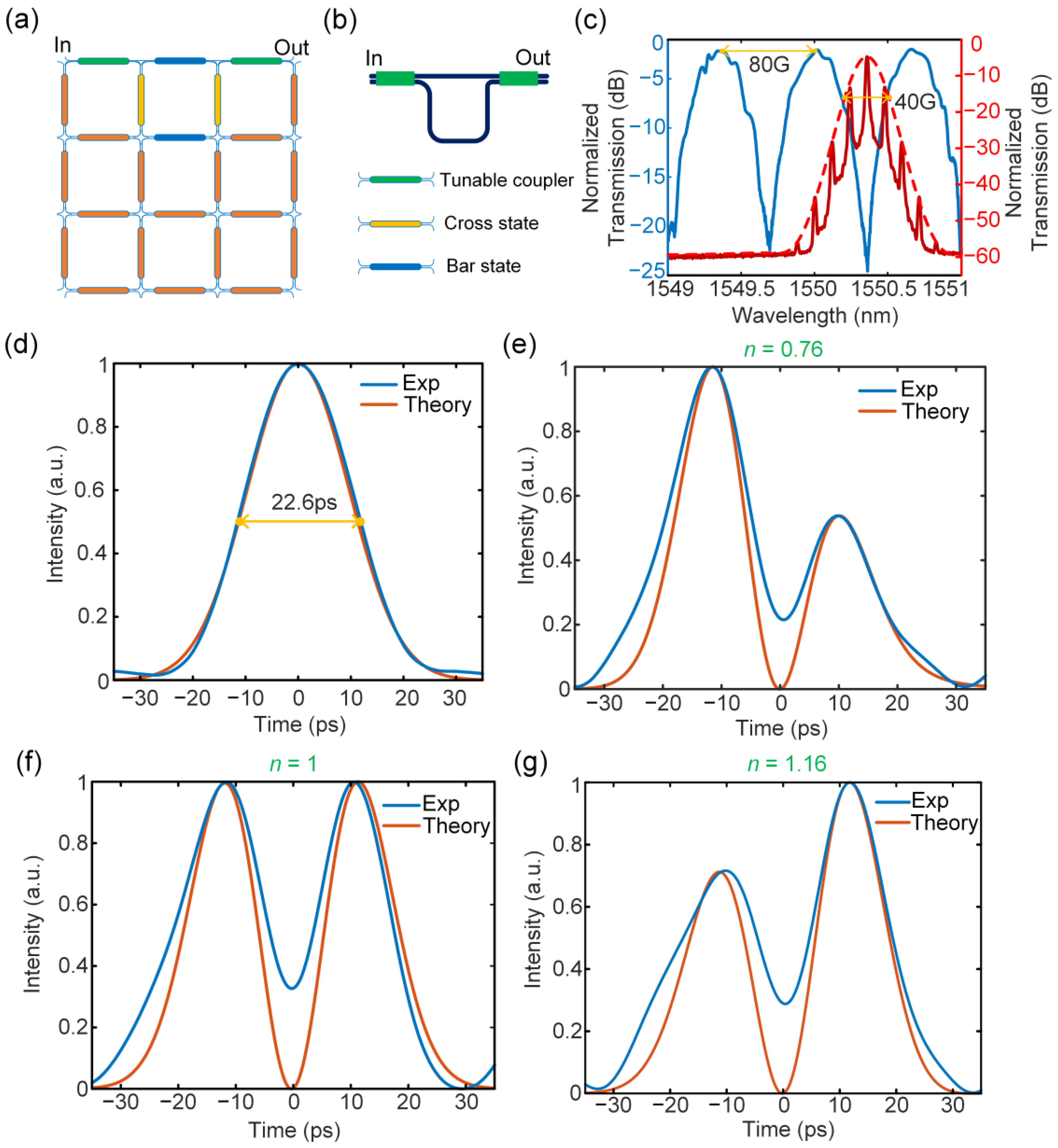

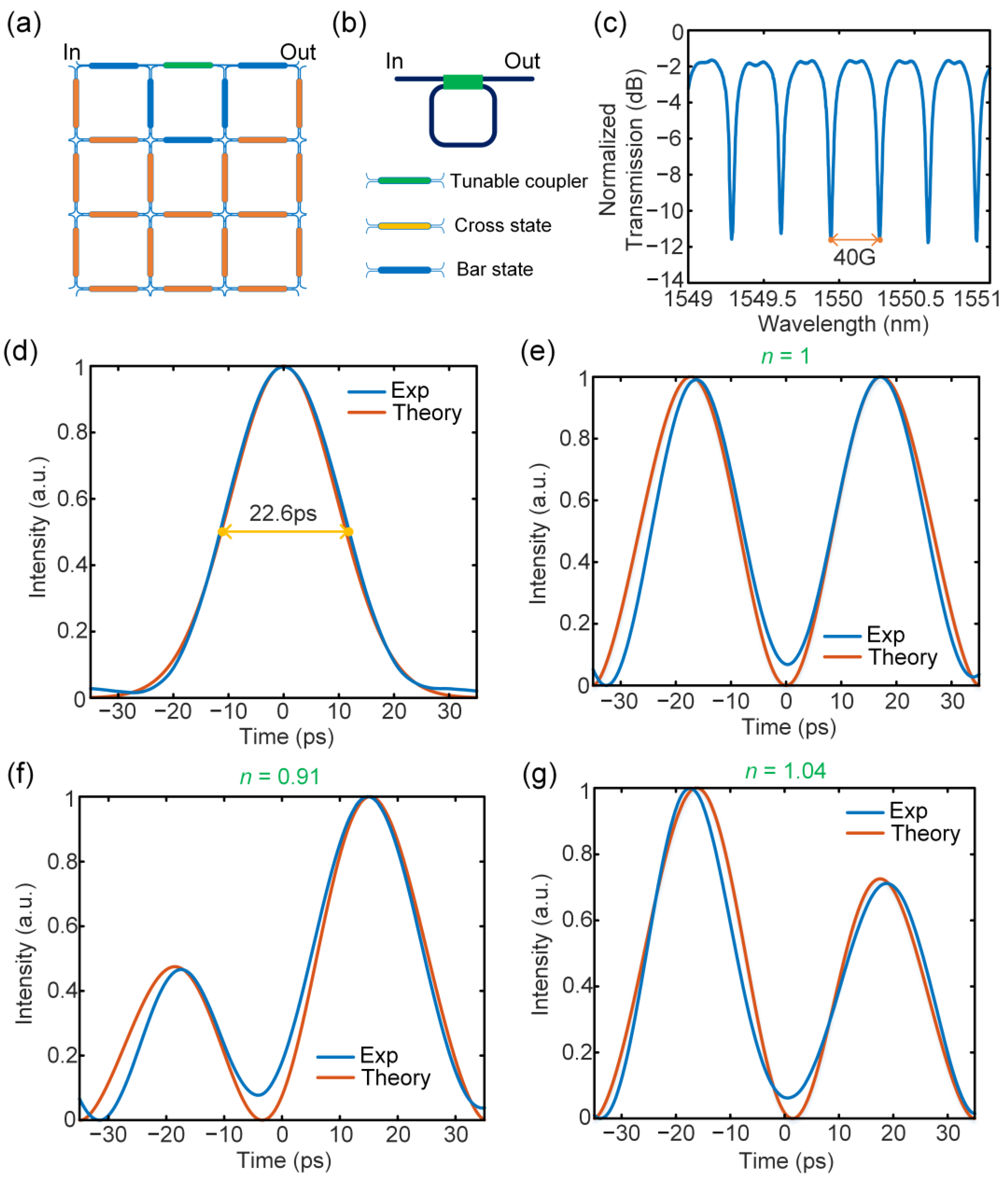

3.1. Photonic Temporal Differentiation

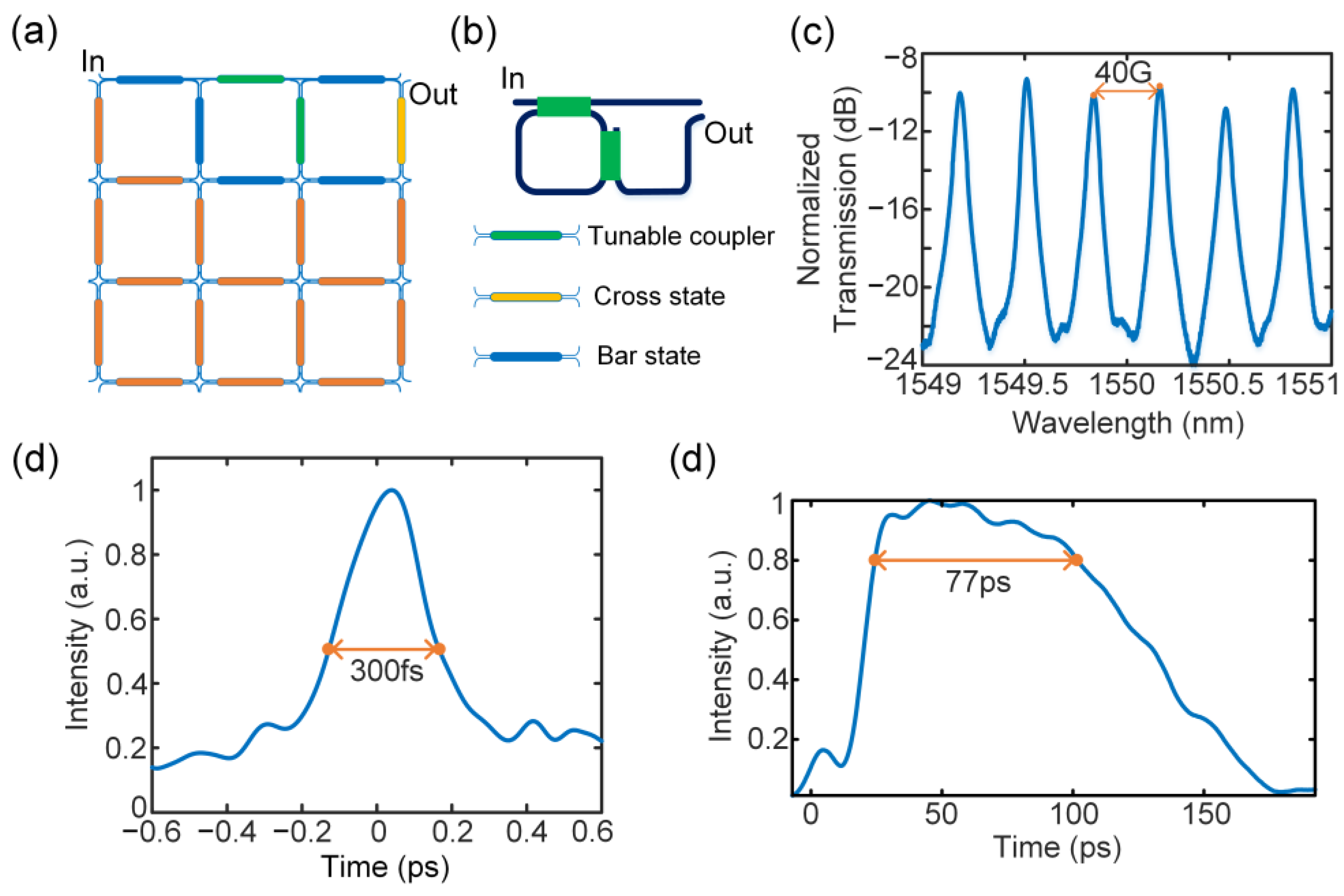

3.2. Photonic Temporal Hilbert Transformation

3.3. Photonic Temporal Integration

4. Discussion

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Appendix A

| Figure of Merit | Hexagonal | Quadrilateral | Triangular |

|---|---|---|---|

| Possible arm length mismatch for constructing MZIs/unit | 2n | 2,4n | 3n |

| Possible cavity length for constructing MRRs/unit | 6,10 + 2n | 4n | 3n |

| MZI reconfiguring resolution step/unit | 2 | 4 | 3 |

| MRR reconfiguring resolution step/unit | 2 | 4 | 3 |

| MZI maximum achievable FSR/GHz | 80 | 80 | 53.3 |

| MRR maximum achievable FSR/GHz | 26.67 | 40 | 53.3 |

References

- Tsai, C.-W.; Lai, C.-F.; Chao, H.-C.; Vasilakos, A.V. Big data analytics: A survey. J. Big Data 2015, 2, 21. [Google Scholar] [CrossRef]

- Chen, X.; Milosevic, M.M.; Stankovic, S.; Reynolds, S.; Bucio, T.D.; Li, K.; Thomson, D.J.; Gardes, F.; Reed, G.T. The Emergence of Silicon Photonics as a Flexible Technology Platform. Proc. IEEE 2018, 106, 2101–2116. [Google Scholar] [CrossRef]

- Coldren, L.A.; Nicholes, S.C.; Johansson, L.; Ristic, S.; Guzzon, R.S.; Norberg, E.J.; Krishnamachari, U. High Performance InP-Based Photonic ICs—A Tutorial. J. Light. Technol. 2011, 29, 554–570. [Google Scholar] [CrossRef]

- Heck, M.J.R.; Bauters, J.F.; Davenport, M.L.; Doylend, J.K.; Jain, S.; Kurczveil, G.; Srinivasan, S.; Tang, Y.; Bowers, J.E. Hybrid Silicon Photonic Integrated Circuit Technology. IEEE J. Sel. Top. Quantum Electron. 2013, 19, 6100117. [Google Scholar] [CrossRef]

- Zhang, W.; Yao, J. Photonic integrated field-programmable disk array signal processor. Nat. Commun. 2020, 11, 406. [Google Scholar] [CrossRef]

- Shen, Y.; Harris, N.C.; Skirlo, S.; Prabhu, M.; Baehr-Jones, T.; Hochberg, M.; Sun, X.; Zhao, S.; Larochelle, H.; Englund, D.; et al. Deep learning with coherent nanophotonic circuits. Nat. Photonics 2017, 11, 441–446. [Google Scholar] [CrossRef]

- Harris, N.C.; Steinbrecher, G.R.; Prabhu, M.; Lahini, Y.; Mower, J.; Bunandar, D.; Chen, C.; Wong, F.N.C.; Baehr-Jones, T.; Hochberg, M.; et al. Quantum transport simulations in a programmable nanophotonic processor. Nat. Photonics 2017, 11, 447–452. [Google Scholar] [CrossRef]

- Qiang, X.; Zhou, X.; Wang, J.; Wilkes, C.M.; Loke, T.; O’Gara, S.; Kling, L.; Marshall, G.D.; Santagati, R.; Ralph, T.C.; et al. Large-scale silicon quantum photonics implementing arbitrary two-qubit processing. Nat. Photonics 2018, 12, 534–539. [Google Scholar] [CrossRef]

- Wang, J.; Shen, H.; Fan, L.; Wu, R.; Niu, B.; Varghese, L.T.; Xuan, Y.; Leaird, D.E.; Wang, X.; Gan, F.; et al. Reconfigurable radio-frequency arbitrary waveforms synthesized in a silicon photonic chip. Nat. Commun. 2015, 6, 5957. [Google Scholar] [CrossRef]

- Jiang, H.; Yan, L.; Marpaung, D. Chip-based arbitrary radio-frequency photonic filter with algorithm-driven reconfigurable resolution. Opt. Lett. 2018, 43, 415–418. [Google Scholar] [CrossRef] [PubMed]

- Capmany, J.; Pérez, D. Programmable Integrated Photonics; Oxford University Press: Oxford, UK, 2020. [Google Scholar] [CrossRef]

- Bogaerts, W.; Perez, D.; Capmany, J.; Miller, D.A.B.; Poon, J.; Englund, D.; Morichetti, F.; Melloni, A. Programmable photonic circuits. Nature 2020, 586, 207–216. [Google Scholar] [CrossRef] [PubMed]

- Xu, X.; Ren, G.; Feleppa, T.; Liu, X.; Boes, A.; Mitchell, A.; Lowery, A.J. Self-calibrating programmable photonic integrated circuits. Nat. Photonics 2022, 16, 595–602. [Google Scholar] [CrossRef]

- Carroll, L.; Lee, J.-S.; Scarcella, C.; Gradkowski, K.; Duperron, M.; Lu, H.; Zhao, Y.; Eason, C.; Morrissey, P.; Rensing, M.; et al. Photonic Packaging: Transforming Silicon Photonic Integrated Circuits into Photonic Devices. Appl. Sci. 2016, 6, 426. [Google Scholar] [CrossRef]

- Annoni, A.; Guglielmi, E.; Carminati, M.; Ferrari, G.; Sampietro, M.; Miller, D.A.; Melloni, A.; Morichetti, F. Unscrambling light-automatically undoing strong mixing between modes. Light. Sci. Appl. 2017, 6, e17110. [Google Scholar] [CrossRef]

- Pérez, D.; Gasulla, I.; Capmany, J. Software-defined reconfigurable microwave photonics processor. Opt. Express 2015, 23, 14640–14654. [Google Scholar] [CrossRef] [PubMed]

- Xie, Y.; Geng, Z.; Zhuang, L.; Burla, M.; Taddei, C.; Hoekman, M.; Leinse, A.; Roeloffzen, C.G.H.; Boller, K.-J.; Lowery, A.J. Programmable optical processor chips: Toward photonic RF filters with DSP-level flexibility and MHz-band selectivity. Nanophotonics 2017, 7, 421–454. [Google Scholar] [CrossRef]

- Miller, D.A.B. Perfect optics with imperfect components. Optica 2015, 2, 747. [Google Scholar] [CrossRef]

- Miller, D.A.B. Self-configuring universal linear optical component [Invited]. Photonics Res. 2013, 1, 1–15. [Google Scholar] [CrossRef]

- Clements, W.R.; Humphreys, P.C.; Metcalf, B.J.; Kolthammer, W.S.; Walmsley, I.A. Optimal design for universal multiport interferometers. Optica 2016, 3, 1460–1465. [Google Scholar] [CrossRef]

- Harris, N.C.; Carolan, J.; Bunandar, D.; Prabhu, M.; Hochberg, M.; Baehr-Jones, T.; Fanto, M.L.; Smith, A.M.; Tison, C.C.; Alsing, P.M.; et al. Linear programmable nanophotonic processors. Optica 2018, 5, 1623–1631. [Google Scholar] [CrossRef]

- Zheng, D.; Doménech, J.D.; Pan, W.; Zou, X.; Yan, L.; Pérez, D. Low-loss broadband 5 × 5 non-blocking Si3N4 optical switch matrix. Opt. Lett. 2019, 44, 2629–2632. [Google Scholar] [CrossRef]

- Miller, D.A.B. Self-aligning universal beam coupler. Opt. Express 2013, 21, 6360–6370. [Google Scholar] [CrossRef]

- Ribeiro, A.; Ruocco, A.; Vanacker, L.; Bogaerts, W. Demonstration of a 4 × 4-port universal linear circuit. Optica 2016, 3, 1348–1357. [Google Scholar] [CrossRef]

- Liu, W.; Li, M.; Guzzon, R.S.; Norberg, E.J.; Parker, J.S.; Lu, M.; Coldren, L.A.; Yao, J. A fully reconfigurable photonic integrated signal processor. Nat. Photonics 2016, 10, 190–195. [Google Scholar] [CrossRef]

- Perez, D.; Gasulla, I.; Capmany, J. Field-programmable photonic arrays. Opt. Express 2018, 26, 27265–27278. [Google Scholar] [CrossRef] [PubMed]

- Perez-Lopez, D.; Lopez, A.; DasMahapatra, P.; Capmany, J. Multipurpose self-configuration of programmable photonic circuits. Nat. Commun. 2020, 11, 6359. [Google Scholar] [CrossRef] [PubMed]

- Perez, D.; Gasulla, I.; Capmany, J.; Soref, R.A. Reconfigurable lattice mesh designs for programmable photonic processors. Opt. Express 2016, 24, 12093–12106. [Google Scholar] [CrossRef] [PubMed]

- Perez, D.; Gasulla, I.; Fraile, F.J.; Crudgington, L.; Thomson, D.J.; Khokhar, A.Z.; Li, K.; Cao, W.; Mashanovich, G.Z.; Capmany, J. Silicon Photonics Rectangular Universal Interferometer. Laser Photonics Rev. 2017, 11, 1700219. [Google Scholar] [CrossRef]

- Pérez, D.; Capmany, J. Scalable analysis for arbitrary photonic integrated waveguide meshes. Optica 2019, 6, 19–27. [Google Scholar] [CrossRef]

- Zhuang, L.; Roeloffzen, C.G.H.; Hoekman, M.; Boller, K.-J.; Lowery, A.J. Programmable photonic signal processor chip for radiofrequency applications. Optica 2015, 2, 854–859. [Google Scholar] [CrossRef]

- Pérez, D.; Gasulla, I.; Crudgington, L.; Thomson, D.J.; Khokhar, A.Z.; Li, K.; Cao, W.; Mashanovich, G.Z.; Capmany, J. Multipurpose silicon photonics signal processor core. Nat. Commun. 2017, 8, 636. [Google Scholar] [CrossRef] [PubMed]

- Li, F.; Park, Y.; Azaña, J. Complete temporal pulse characterization based on phase reconstruction using optical ultrafast differentiation (PROUD). Opt. Lett. 2007, 32, 3364–3366. [Google Scholar] [CrossRef] [PubMed]

- Park, Y.; Azaña, J.; Slavík, R. Ultrafast all-optical first- and higher-order differentiators based on interferometers. Opt. Lett. 2007, 32, 710–712. [Google Scholar] [CrossRef]

- Mathieu, B.; Melchior, P.; Oustaloup, A.; Ceyral, C. Fractional differentiation for edge detection. Signal Process. 2003, 83, 2421–2432. [Google Scholar] [CrossRef]

- Tan, M.; Mitchell, A.; Moss, D.J.; Xu, X.; Corcoran, B.; Wu, J.; Boes, A.; Nguyen, T.G.; Chu, S.T.; Little, B.E.; et al. Microwave and RF Photonic Fractional Hilbert Transformer Based on a 50 GHz Kerr Micro-Comb. J. Light. Technol. 2019, 37, 6097–6104. [Google Scholar] [CrossRef]

- Shahoei, H.; Dumais, P.; Yao, J. Continuously tunable photonic fractional Hilbert transformer using a high-contrast germanium-doped silica-on-silicon microring resonator. Opt. Lett. 2014, 39, 2778–2781. [Google Scholar] [CrossRef]

- Ghelfi, P.; Laghezza, F.; Scotti, F.; Serafino, G.; Capria, A.; Pinna, S.; Onori, D.; Porzi, C.; Scaffardi, M.; Malacarne, A.; et al. A fully photonics-based coherent radar system. Nature 2014, 507, 341–345. [Google Scholar] [CrossRef] [PubMed]

- Waterhouse, R.; Novack, D. Realizing 5G: Microwave Photonics for 5G Mobile Wireless Systems. IEEE Microw. Mag. 2015, 16, 84–92. [Google Scholar] [CrossRef]

- Carolan, J.; Harrold, C.; Sparrow, C.; Martín-López, E.; Russell, N.J.; Silverstone, J.W.; Shadbolt, P.J.; Matsuda, N.; Oguma, M.; Itoh, M.; et al. Universal linear optics. Science 2015, 349, 711–716. [Google Scholar] [CrossRef] [PubMed]

- Hill, M.T.; Dorren, H.J.S.; de Vries, T.; Leijtens, X.J.M.; den Besten, J.H.; Smalbrugge, B.; Oei, Y.-S.; Binsma, H.; Khoe, G.-D.; Smit, M.K. A fast low-power optical memory based on coupled micro-ring lasers. Nature 2004, 432, 206–209. [Google Scholar] [CrossRef]

- Ferrera, M.; Park, Y.; Razzari, L.; Little, B.E.; Chu, S.T.; Morandotti, R.; Moss, D.J.; Azana, J. On-chip CMOS-compatible all-optical integrator. Nat. Commun. 2010, 1, 29. [Google Scholar] [CrossRef] [PubMed]

- Ferrera, M.; Park, Y.; Razzari, L.; Little, B.E.; Chu, S.T.; Morandotti, R.; Moss, D.J.; Azaña, J. All-optical 1st and 2nd order integration on a chip. Opt. Express 2011, 19, 23153–23161. [Google Scholar] [CrossRef] [PubMed]

- Zangeneh-Nejad, F.; Fleury, R. Topological analog signal processing. Nat. Commun. 2019, 10, 2058. [Google Scholar] [CrossRef] [PubMed]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yao, Y.; Wei, Y.; Dong, J.; Li, M.; Zhang, X. Large-Scale Reconfigurable Integrated Circuits for Wideband Analog Photonic Computing. Photonics 2023, 10, 300. https://doi.org/10.3390/photonics10030300

Yao Y, Wei Y, Dong J, Li M, Zhang X. Large-Scale Reconfigurable Integrated Circuits for Wideband Analog Photonic Computing. Photonics. 2023; 10(3):300. https://doi.org/10.3390/photonics10030300

Chicago/Turabian StyleYao, Yuhan, Yanxian Wei, Jianji Dong, Ming Li, and Xinliang Zhang. 2023. "Large-Scale Reconfigurable Integrated Circuits for Wideband Analog Photonic Computing" Photonics 10, no. 3: 300. https://doi.org/10.3390/photonics10030300

APA StyleYao, Y., Wei, Y., Dong, J., Li, M., & Zhang, X. (2023). Large-Scale Reconfigurable Integrated Circuits for Wideband Analog Photonic Computing. Photonics, 10(3), 300. https://doi.org/10.3390/photonics10030300