A Novel, Single-Step 3D-Printed Shadow Mask Fabrication Method for TFTs

Abstract

1. Introduction

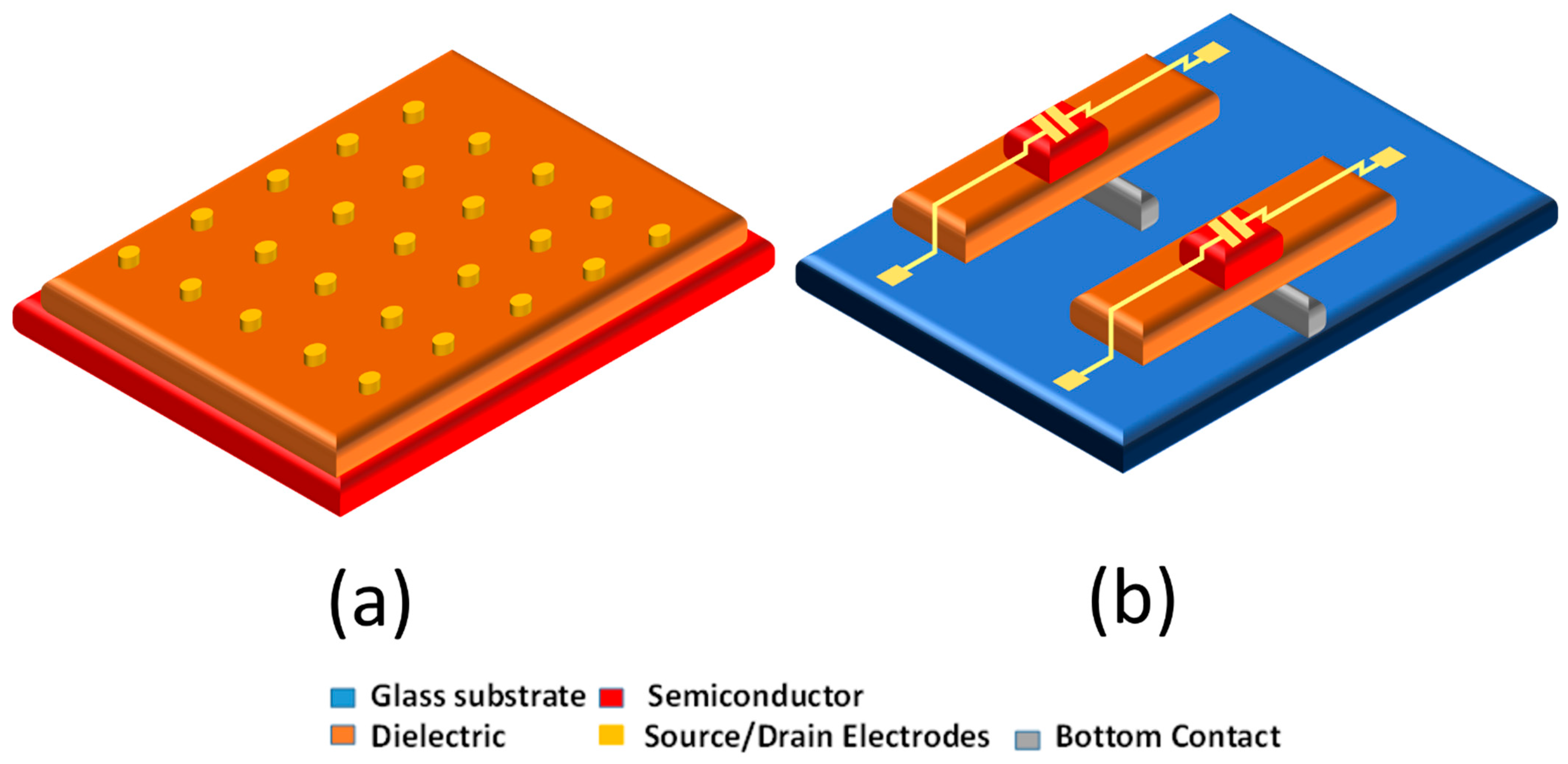

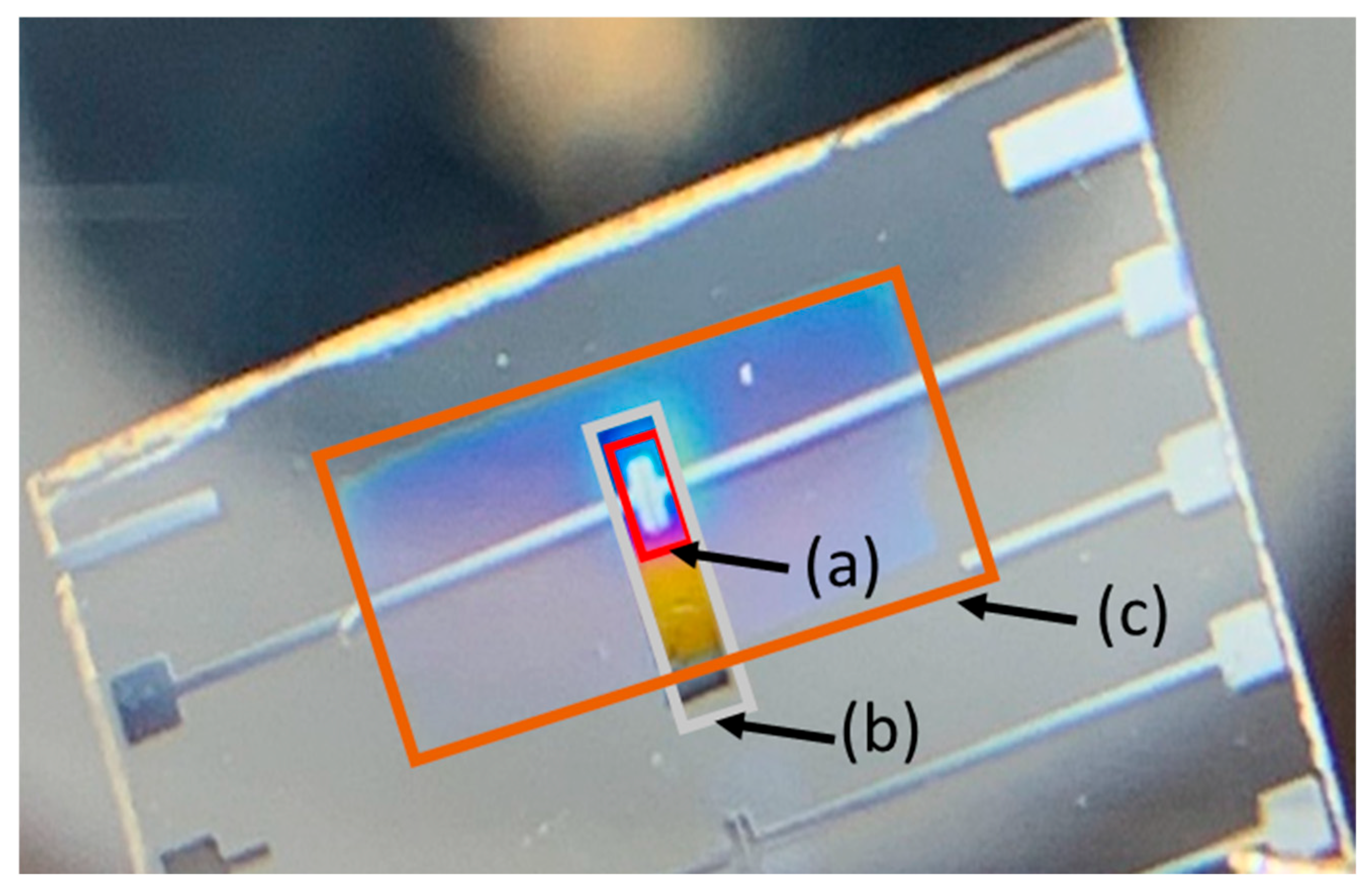

2. Experiment/Methods

2.1. Materials Deposition

2.2. Shadow Mask Development

3. Device Fabrication

4. Results and Discussion

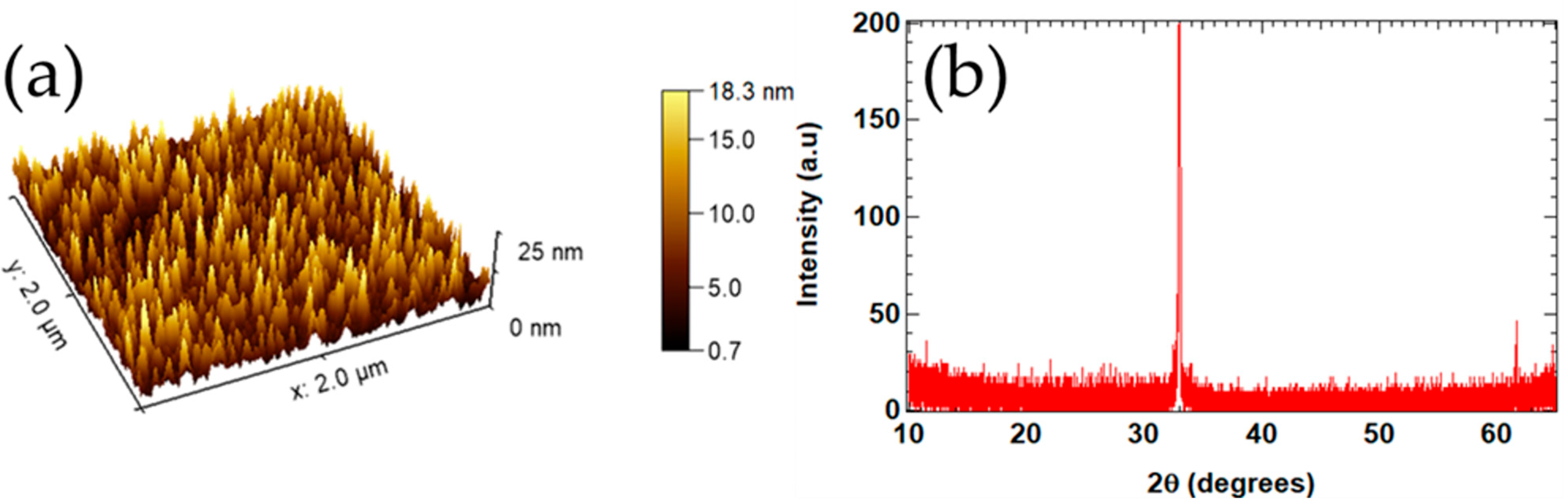

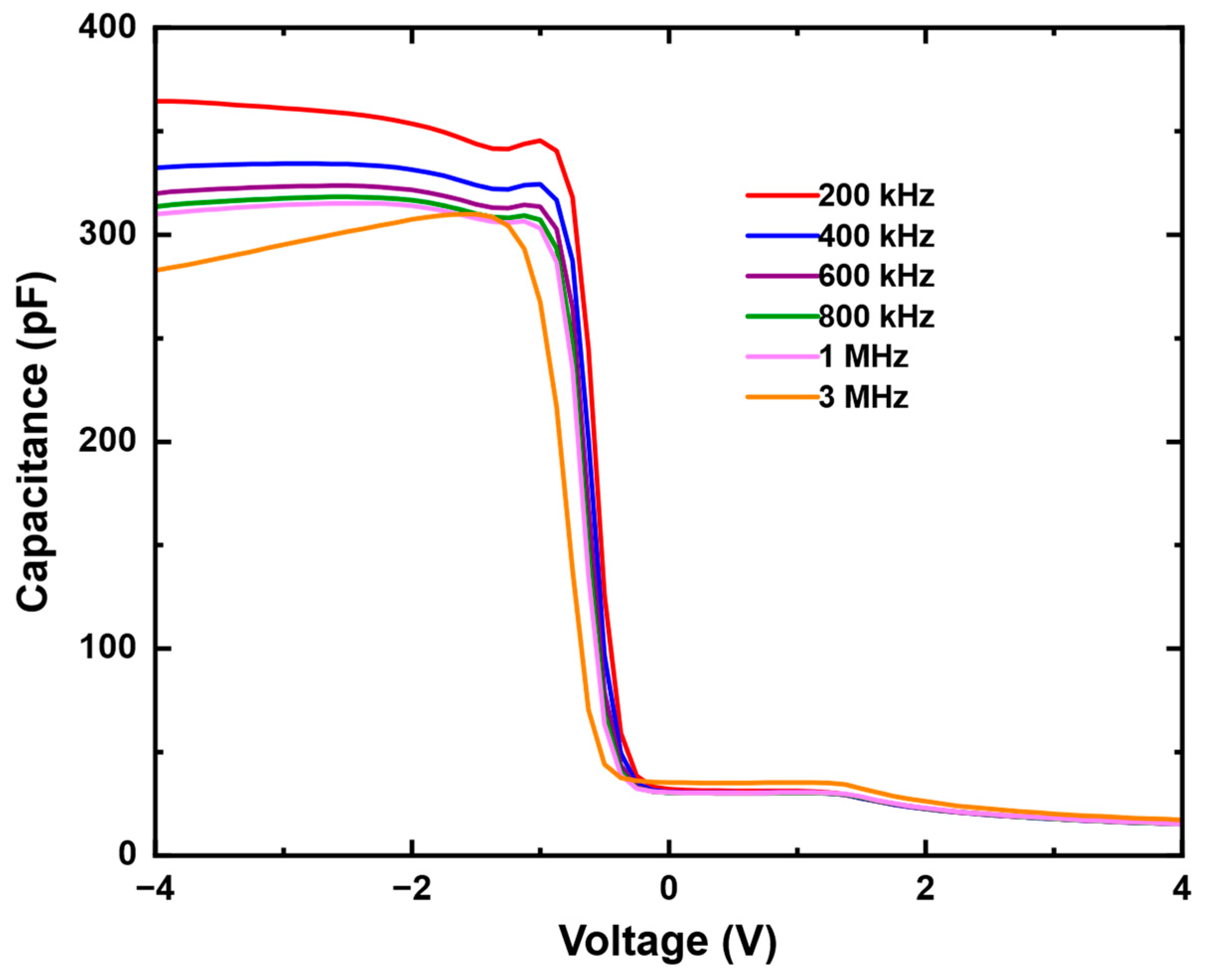

4.1. ZrO2 Dielectric Characterization

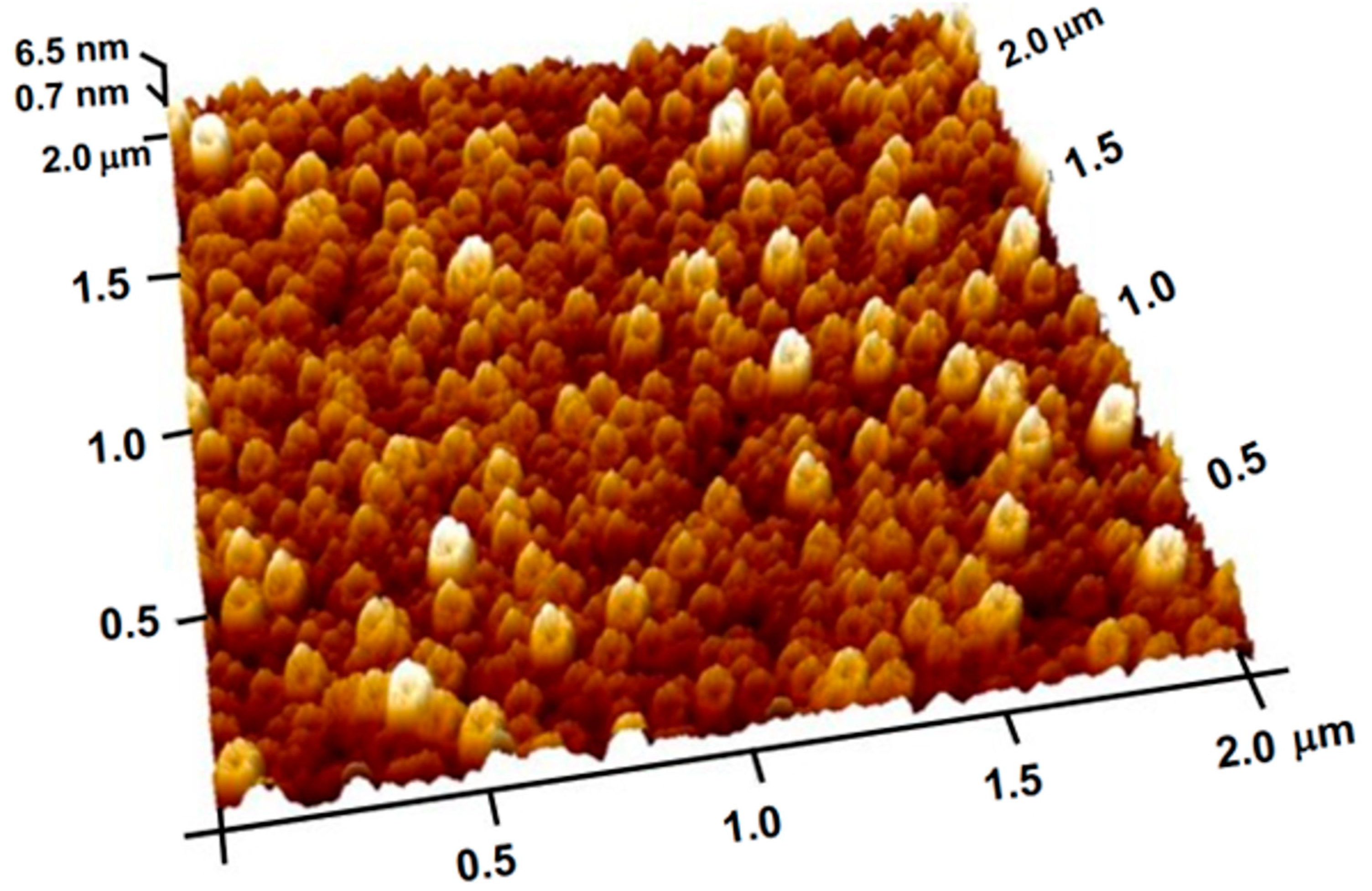

4.2. AZO Semiconductor Layer Characterization

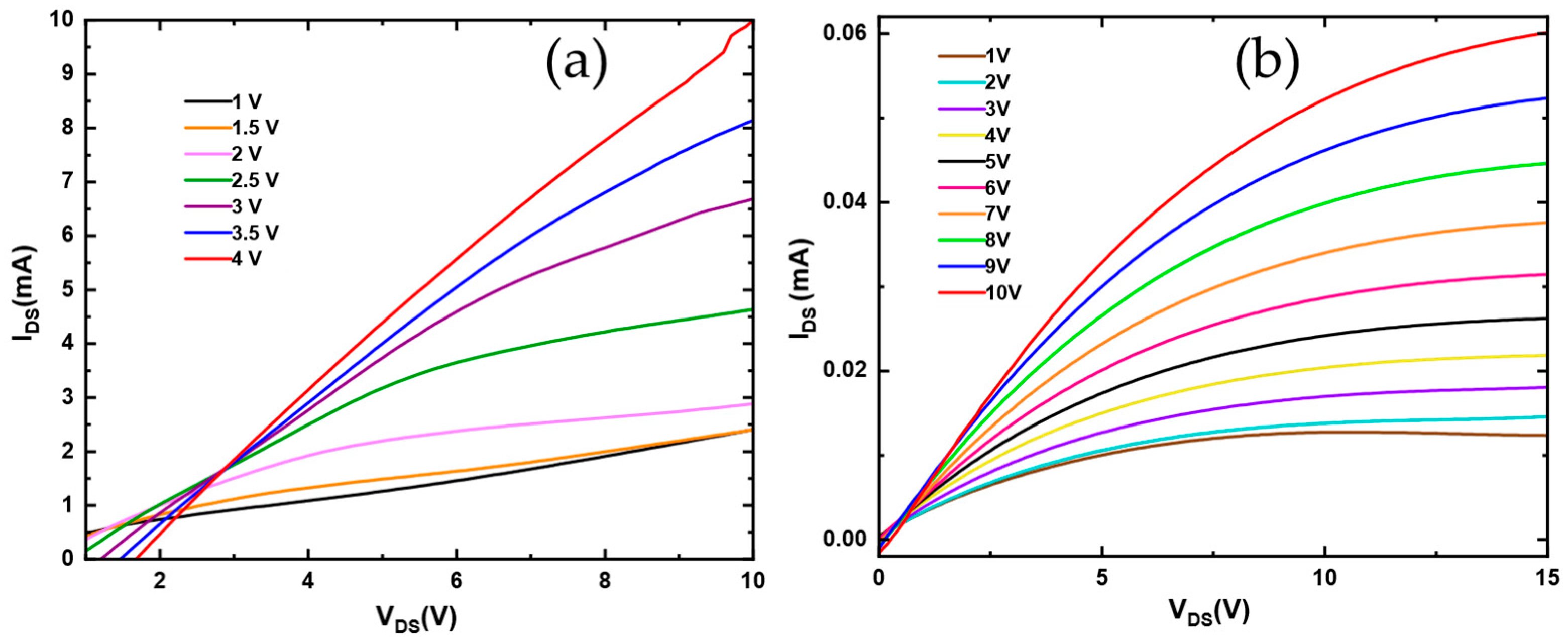

4.3. TFT Performance

| Material/Device (Structure) | Mobility (cm2/V·s) | Vth (V) | Ion/Ioff | Key Notes | Reference |

|---|---|---|---|---|---|

| This work (3D-printed mask) | 13.1 | ~4.1 | 104 | Room-temperature, indium-free, no annealing | This work |

| a-IGZO TFT with AZO/IGZO bi-layer S/D contacts | 13.7 | 0.6 | 106 | Heterojunction S/D contacts | [64] |

| ZnO/AZO or AZO/ZnO double-active-layer TFTs (sputtered, RT + anneal) | 0.01 | 2.9 | 105 | Anneal optimization required | [65] |

| Indium-free ZnO/AZO double-active-layer TFT (sputtered, RT) | 4 × 10−3 | 9.5 | 104 | Room temp, indium-free | [65] |

| a-IGZO/flexible IGZO TFTs (HfO2/Al2O3/HfO2 dielectric) | 10 | 0.35 | 106 | Low-voltage flexible circuits | [66] |

| a-IGZO/a-GIZO high-mobility engineering | 74 | −1.3 | 108 | PEALD, patterned metal insertion | [67] |

| Indium-free ZnO/AZO double-active-layer TFT (sputtered, RT) | 2.9 × 10−3 | 103 | Room temp, indium-free | [65] | |

| a-InSnO/IGZO heterojunction TFT (ALD) | 14.1 | −0.5 | 108 | High stability ALD | [68] |

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Choi, J.H.; Yang, J.H.; Pi, J.E.; Hwang, C.Y.; Kim, Y.H.; Kim, G.H.; Kim, H.O.; Hwang, C.S. The New Route for Realization of 1-µm-Pixel-Pitch High-Resolution Displays. J. Soc. Inf. Disp. 2019, 27, 487–496. [Google Scholar] [CrossRef]

- Ohara, M.; Kohda, T.; Furuichi, S.; Nakada, T.; Kawase, K.; Kohda, Y.; Ishikawa, T.; Sumiyoshi, K.; Funakoshi, A. 13.2: Invited Paper: Recent Progress and Future Trend of Ultra-High-Resolution Large-Sized TFT-LCD Monitor Electronics. SID Symp. Dig. Tech. Pap. 2002, 33, 168–171. [Google Scholar] [CrossRef]

- Kaya, S.; Schmidl, D.; Schmetterer, L.; Witkowska, K.J.; Unterhuber, A.; Aranha Dos Santos, V.; Baar, C.; Garhofer, G.; Werkmeister, R.M. Effect of Hyaluronic Acid on Tear Film Thickness as Assessed with Ultra-High Resolution Optical Coherence Tomography. Acta Ophthalmol. 2015, 93, 439–443. [Google Scholar] [CrossRef]

- Komatsu, R.; Nakazato, R.; Sasaki, T.; Suzuki, A.; Senda, N.; Kawata, T.; Jimbo, Y.; Aoyama, T.; Ohno, N.; Kawashima, S.; et al. Repeatedly Foldable AMOLED Display. J. Soc. Inf. Disp. 2015, 23, 41–49. [Google Scholar] [CrossRef]

- Noda, M.; Kobayashi, N.; Katsuhara, M.; Yumoto, A.; Ushikura, S.; Yasuda, R.; Hirai, N.; Yukawa, G.; Yagi, I.; Nomoto, K.; et al. An OTFT-driven rollable OLED display. J. Soc. Inf. Disp. 2011, 19, 316–322. [Google Scholar] [CrossRef]

- Yarbrough, K.A.; Behera, M.K.; Beckford, J.; Pradhan, S.K.; Bahoura, M. Observation of MOSFET like behavior of a TFT based on amorphous oxide semiconductor channel layer with suitable integration of atomic layered deposited high-k gate dielectrics. AIP Adv. 2023, 13, 025041. [Google Scholar] [CrossRef]

- Jia, Y.; Liu, Z.; Wu, D.; Chen, J.; Meng, H. Mechanical Simulation of Foldable AMOLED Panel with a Module Structure. Org. Electron. 2019, 65, 185–192. [Google Scholar] [CrossRef]

- Mizukami, M.; Cho, S.-I.; Watanabe, K.; Abiko, M.; Suzuri, Y.; Tokito, S.; Kido, J. Flexible Organic Light-Emitting Diode Displays Driven by Inkjet-Printed High-Mobility Organic Thin-Film Transistors. IEEE Electron Device Lett. 2018, 39, 39–42. [Google Scholar] [CrossRef]

- Mativenga, M.; Geng, D.; Kim, B.; Jang, J. Fully Transparent and Rollable Electronics. ACS Appl. Mater. Interfaces 2015, 7, 1578–1585. [Google Scholar] [CrossRef]

- Jin, D.-U.; Kim, T.-W.; Koo, H.-W.; Stryakhilev, D.; Kim, H.-S.; Seo, S.-J.; Kim, M.-J.; Min, H.-K.; Chung, H.-K.; Kim, S.S. Highly Robust Flexible AMOLED Display on Plastic Substrate with New Structure. SID Symp. Dig. Tech. Pap. 2010, 41, 703–705. [Google Scholar] [CrossRef]

- Jang, H.J.; Lee, J.Y.; Kwak, J.; Lee, D.; Park, J.-H.; Lee, B.; Noh, Y.Y. Progress of Display Performances: AR, VR, QLED, OLED, and TFT. J. Inf. Disp. 2019, 20, 1–8. [Google Scholar] [CrossRef]

- Peng, C.; Huang, H.; Xu, M.; Chen, L.; Li, X.; Zhang, J. A Simple Doping Process Achieved by Modifying the Passivation Layer for Self-Aligned Top-Gate In-Ga-Zn-O Thin-Film Transistors at 200 °C. Nanomaterials 2022, 12, 4021. [Google Scholar] [CrossRef]

- Peng, C.; Xu, M.; Chen, L.; Li, X.; Zhang, J. Improvement of Properties of Top-gate IGZO TFT by Oxygen-Rich Ultrathin in Situ ITO Active Layer. Jpn. J. Appl. Phys. 2022, 61, 070914. [Google Scholar] [CrossRef]

- Peng, C.; Yang, S.; Pan, C.; Li, X.; Zhang, J. Effect of Two-Step Annealing on High Stability of a-IGZO Thin-Film Transistor. IEEE Trans. Electron Devices 2020, 67, 4262–4268. [Google Scholar] [CrossRef]

- Liu, Y.; Li, X.; Ge, L.; Zhang, Z. Ultralarge-Area Stitchless Scanning Probe Lithography and In Situ Characterization System Using a Compliant Nanomanipulator. IEEE/ASME Trans. Mechatron. 2024, 29, 924–935. [Google Scholar] [CrossRef]

- Wu, Y.; Chiu, G. Modeling Height Profile for Drop-on-Demand Print of UV Curable Ink. In Proceedings of the ASME 2019 Dynamic Systems and Control Conference, Park City, UT, USA, 8–11 October 2019; 8p. [Google Scholar] [CrossRef]

- Zaho, K.; Ye, Z.; Su, Z.; Cao, W.; Shi, D.; Hao, X.; Zhang, S.; Wang, Z.; Xu, X.; Zhu, J. A diffusion-controlled kinetic model for binder burnout in a green part fabricated by binder jetting based on the thermal decomposition kinetics of TEG-DMA. Add. Manuf. 2025, 105, 104793. [Google Scholar]

- Wu, W.; Chen, Y.; Xie, B.; Wu, H.; Cheng, L.; Guo, Y.; Cai, C.; Hou, M.; Chen, X. Microdynamic behaviors of Au/Ni-assisted chemical etching in fabricating silicon nanostructures. Appl. Surf. Sci. 2025, 696, 162915. [Google Scholar] [CrossRef]

- Moyen, E.; Kim, J.H.; Kim, J.; Jang, J. Zno Nanoparticles for Quantum-Dot-Based Light-Emitting Diodes. ACS Appl. Nano Mater. 2020, 3, 5203–5211. [Google Scholar] [CrossRef]

- Han, W.; Oh, S.; Lee, C.; Kim, J.; Park, H.-H. Zno Nanocrystal Thin Films for Quantum-Dot Light-Emitting Devices. ACS Appl. Nano Mater. 2020, 3, 7535–7542. [Google Scholar] [CrossRef]

- Xiong, S.X.; Hu, L.; Hu, L.; Sun, L.L.; Qin, F.; Liu, X.J.; Fahlman, M.; Zhou, Y.H. 12.5% Flexible Nonfullerene Solar Cells by Passivating the Chemical Interaction Between the Active Layer and Polymer Interfacial Layer. Adv. Mater. 2019, 31, 1806616. [Google Scholar] [CrossRef]

- Wei, J.F.; Ji, G.Q.; Zhang, C.J.; Yan, L.P.; Luo, Q.; Wang, C.; Chen, Q.; Yang, J.L.; Chen, L.W.; Ma, C.Q. Silane-Capped ZnO Nanoparticles for Use as the Electron Transport Layer in Inverted Organic Solar Cells. ACS Nano 2018, 12, 5518–5529. [Google Scholar] [CrossRef]

- Guo, L.; Yang, Z.; Dou, X. Artificial Olfactory System for Trace Identification of Explosive Vapors Realized by Optoelectronic Schottky Sensing. Adv. Mater. 2017, 29, 1604528. [Google Scholar] [CrossRef]

- Nasiri, N.; Bo, R.H.; Wang, F.; Fu, L.; Tricoli, A. Ultraporous Electron-Depleted Zno Nanoparticle Networks for Highly Sensitive Portable Visible-Blind Uv Photodetectors. Adv. Mater. 2015, 27, 4336–4343. [Google Scholar] [CrossRef]

- Xie, J.; Cao, Y.; Jia, D.; Li, Y.; Wang, Y. Solid-State Synthesis of Y-Doped ZnO Nanoparticles with Selective-Detection Gas-Sensing Performance. Ceram. Int. 2016, 42, 90–96. [Google Scholar] [CrossRef]

- Gurav, K.V.; Gang, M.G.; Shin, S.W.; Patil, U.M.; Deshmukh, P.R.; Agawane, G.L.; Suryawanshi, M.P.; Pawar, S.M.; Patil, P.S.; Lokhande, C.D.; et al. Gas Sensing Properties of Hydrothermally Grown ZnO Nanorods with Different Aspect Ratios. Sens. Actuators B Chem. 2014, 190, 439–445. [Google Scholar] [CrossRef]

- Huang, K.; Wu, J.; Chen, Z.; Xu, H.; Wu, Z.; Tao, K.; Yang, T.; Wu, Q.; Zhou, H.; Huang, B.; et al. Nanostructured High-Performance Thin-Film Transistors and Photo-transistors Fabricated by a High-Yield and Versatile Near-Field Nanolithography Strategy. ACS Nano 2019, 13, 6618–6630. [Google Scholar] [CrossRef]

- Park, J.-H.; Park, J.H.; Biswas, P.; Kwon, D.K.; Han, S.W.; Baik, H.K.; Myoung, J.-M. Adopting Novel Strategies in Achieving High-Performance Single-Layer Network Structured ZnO Nanorods Thin Film Transistors. ACS Appl. Mater. Interfaces 2016, 8, 11564–11574. [Google Scholar] [CrossRef]

- Beckford, J.; Behera, M.K.; Yarbrough, K.A.; Pradhan, S.K.; Bahoura, M. Influence of oxygen on the optical, electrical, and heating properties of gallium-doped zinc oxide (GZO) films. AIP Adv. 2023, 13, 025249. [Google Scholar] [CrossRef]

- Beckford, J.; Behera, M.K.; Yarbrough, K.A.; Obasogie, B.; Pradhan, S.K.; Bahoura, M. Gallium doped zinc oxide thin films as transparent conducting oxide for thin-film heaters. AIP Adv. 2021, 11, 075208. [Google Scholar] [CrossRef]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef]

- Lokanc, M.; Eggert, R.; Redkinger, M. The Availability of Indium: The Present, Medium Term, and Long Term. Available online: https://www.nrel.gov/docs/fy16osti/62409.pdf (accessed on 8 September 2025).

- Oh, H.; Yoon, S.M.; Ryu, M.K.; Hwang, C.S.; Yang, S.; Park, S.H.K. Photon-Accelerated Negative Bias Instability Involving Sub-Gap States Creation in Amorphous In–Ga–Zn–O Thin Film Transistor. Appl. Phys. Lett. 2010, 9, 183502. [Google Scholar] [CrossRef]

- Migliorato, P.; Chowdhury, M.D.H.; Um, J.G.; Seok, M.; Jang, J. Light/negative Bias Stress Instabilities in Indium Gallium Zinc Oxide Thin Film Transistors Explained by Creation of a Double Donor. Appl. Phys. Lett. 2012, 101, 123502. [Google Scholar] [CrossRef]

- Oh, H.; Yoon, S.M.; Ryu, M.K.; Hwang, C.S.; Yang, S.; Park, S.H.K. Transition of Dominant Instability Mechanism Depending on Negative Gate Bias Under Illumination in Amorphous In-Ga-Zn-O Thin Film Transistor. Appl. Phys. Lett. 2011, 98, 033504. [Google Scholar] [CrossRef]

- Chowdhury, M.D.H.; Ryu, S.H.; Migliorato, P.; Jang, J. Effect Of Annealing Time on Bias Stress and Light-Induced Instabilities in Amorphous Indium–Gallium–Zinc-Oxide Thin Film Transistors. J. Appl. Phys. 2011, 110, 114503. [Google Scholar] [CrossRef]

- Ueoka, Y.; Ishikawa, Y.; Bermundo, J.P.; Yamazaki, H.; Urakawa, S.; Fujii, M.; Horita, M.; Uraoka, Y. Density of States in Amorphous In-Ga-Zn-O Thin Film Transistor Under Negative Bias Illumination Stress. ECS J. Solid State Sci. Technol. 2014, 3, Q3001–Q3004. [Google Scholar] [CrossRef]

- Lu, B.; Li, D.; Tian, X. Development Trends in Additive Manufacturing and 3D printing. Engineering 2015, 1, 85–89. [Google Scholar] [CrossRef]

- Vazquez-Mena, O.; Villanueva, L.G.; Savu, V.; Sidler, K.; Langlet, P.; Brugger, J. Analysis of the Blurring in Stencil Lithography. Nanotechnology 2009, 20, 415303. [Google Scholar] [CrossRef]

- Bhaskar, P.; Mathioudakis, S.; Olschewski, T.; Muckel, F.; Bindel, J.R.; Pratzer, M.; Liebmann, M.; Morgenstern, M. Mask Aligner for Ultrahigh Vacuum with Capacitive Distance Control. Appl. Phys. Lett. 2018, 112, 161602. [Google Scholar] [CrossRef]

- Lishchynska, M.; Bourenkov, V.; van den Boogaart, M.A.F.; Doeswijk, L.; Brugger, J.; Greer, J.C. Predicting Mask Distortion, Clogging and Pattern Transfer for Stencil Lithography. Microelectron. Eng. 2007, 84, 42–53. [Google Scholar] [CrossRef]

- Decker, W.; Belan, R.; Heydemann, V.D.; Armstrong, S.; Fisher, T. Novel Low Pressure Sputtering Source and Improved Vacuum Deposition of Small Patterned Features Using Precision Shadow Masks. In Proceedings of the 59th Annual Technical Conference Proceedings, Indianapolis, IN, USA, 9–13 May 2016. [Google Scholar] [CrossRef]

- Yi, S.M.; Jin, S.H.; Lee, J.D.; Chu, C.N. Fabrication of a High-Aspect-Ratio Stainless Steel Shadow Mask and Its Application to Pentacene Thin-Film Transistors. J. Micromech. Microeng. 2005, 15, 263–269. [Google Scholar] [CrossRef]

- Bartsch, H.; Jaziri, N.; Jaekel, K.; Nessimian, N.; Müller, J. Shadow Masks as an Alternative Method to Lithography for the Structuring of Thin Film Layers on LTCC Substrates. In Proceedings of the IMAPS 2023 Joint Conferences—HiTEC, CICMT, Power Packaging, Albuquerque, NM, USA, 17–20 April 2023. [Google Scholar]

- Cha, C.; Jo, E.; Kim, Y.; Choi, A.J.; Han, K. 3D-Printed Shadow Masks for Micro-Patterned Electrodes. RSC Adv. 2024, 14, 34586–34593. [Google Scholar] [CrossRef]

- Rahiminejad, S.; Köhler, E.; Enoksson, P. Direct 3D Printed Shadow Mask on Silicon. J. Phys. Conf. Ser. 2016, 757, 012021. [Google Scholar] [CrossRef]

- Marques, J.P. Development of High-Resolution Shadow Masks Using Thin Membranes: Limitations Imposed by Mask Thickness and Aspect Ratio; University of Lisbon: Lisbon, Portugal, 2019. [Google Scholar]

- Stencils Unlimited. Shadow Masks for Deposition Design Guidelines. Tech. Blog 2023. Available online: https://www.stencilsunlimited.com/blog/shadow-masks-for-deposition-design-guidelines/ (accessed on 8 September 2025).

- Nanoscribe GmbH. Two-Photon Polymerization (2PP): High-Resolution 3D Printing Technology for Submicron Features. Prod. Technol. Overv. 2025. Available online: https://www.nanoscribe.com/en/microfabrication-technologies/2pp-two-photon-polymerization/ (accessed on 8 September 2025).

- Microlight3D. Two-Photon Polymerization Technology: Achieving Voxel Resolutions ~0.2 µm. Technol. Brief 2025. Available online: https://www.microlight3d.com/technology/two-photon-polymerization (accessed on 8 September 2025).

- LLNL. Parallel Two-Photon Polymerization (TPL) for Scalable Submicron Additive Manufacturing: Less than 350 nm In-Plane Resolution and <5 µm Depth Resolution. Technol. Descr. 2025. Available online: https://ipo.llnl.gov/technologies/advanced-manufacturing/parallel-two-photon-polymerization-scalable-submicron-additive (accessed on 8 September 2025).

- Gierałtowska, S.; Sztenkiel, D.; Guziewicz, E.; Godlewski, M.; Luka, G.; Witkowski, B.S.; Wachnicki, Ł.; Łusakowska, E.; Dietl, T.; Sawicki, M. Properties and Characterization of ALD Grown Dielectric Oxides for MIS Structures. Acta Phys. Pol. A 2011, 119, 692–695. [Google Scholar] [CrossRef]

- Carrasco, I.S.S.; To, T.B.T.; Reis, F.D.A.A. Scaling of Surface Roughness in Film Deposition with Height-Dependent Step Edge Barriers. Phys. Rev. E 2023, 108, 064802. [Google Scholar] [CrossRef] [PubMed]

- Das, S.; Neogi, S.; Mukherjee, M. Effect of Temperature and Deposition Rate on the Surface Morphology of Thin Al Metal Films on Glass Substrate Application in Solar Cell. J. Phys. Conf. Ser. 2020, 1579, 012019. [Google Scholar] [CrossRef]

- Ding, S.; Zhao, J.; Yu, Q. Effect of Zirconia Polymorph on Vapor Phase Ketonization of Propoionic Acid. Catalysts 2019, 9, 768. [Google Scholar] [CrossRef]

- Mih, T.; Paul, S.; Milanov, A.; Bhakta, R.; Devi, A. Capacitance-Voltage Analysis of ZrO2 Thin Films Deposited by Thermal MOCVD Technique. ECS Trans. 2009, 25, 901. [Google Scholar] [CrossRef]

- Kim, S.; Moon, Y.; Moon, D.; Hong, M.; Jeon, Y.; Park, J. Influence of Oxygen on the Electrical Properties of Aluminum Doped Zinc-Oxide Thin Films. J. Kor. Phys. Soc. 2006, 49, 1256–1259. [Google Scholar]

- Look, D.C. Recent Advances in ZnO Materials and Devices. Mater. Sci. Eng. 2001, 80, 383–387. [Google Scholar] [CrossRef]

- Novák, P.; Nedvědová, L.; Kozák, T.; Šotová, P.; Bláhová, O.; Jansa, Z.; Medlín, R.; Netrvalová, M.F.; Minár, J. Investigation of Carrier Transport in ZnO and ZnO: Al Thin Films Sputtered at Different Oxygen Conditions. Thin Solid Films 2023, 780, 139942. [Google Scholar] [CrossRef]

- Zhang, S.B.; Wei, S.H.; Zunger, A. Intrinsic n-Type versus p-Type Doping Asymmetry and the Defect Physics of ZnO. Phys. Rev. 2001, 63, 075205. [Google Scholar] [CrossRef]

- Ellmer, K. Resistivity of Polycrystalline Zinc Oxide Films: Current Status and Physical Limit. J. Phys. D Appl. Phys. 2001, 34, 3097–3108. [Google Scholar] [CrossRef]

- Chung, J.H.; Lee, J.Y.; Kim, H.S.; Jang, N.W.; Kim, J.H. Effect of thickness of ZnO active layer on ZNO-TFT’s characteristic. Thin Solid Films 2008, 516, 5597–5601. [Google Scholar] [CrossRef]

- Zeng, Y.; Ning, H.; Zheng, Z.; Zhang, H.; Fang, Z.; Yao, R.; Xu, M.; Wang, L.; Lan, L.; Peng, J.; et al. Island-like AZO/Al2O3 bilayer channel structure for thin film transistors. Adv. Mater. Interfaces 2017, 4, 1700063. [Google Scholar] [CrossRef]

- Zou, X.; Fang, G.; Wan, J.; Liu, N.; Long, H.; Wang, H.; Zhao, X. Enhanced Performance of a-IGZO Thin-Film Transistors by Forming AZO/IGZO Heterojunction Source/Drain Contacts. Semicond. Sci. Technol. 2011, 26, 055003. [Google Scholar] [CrossRef]

- Yan, X.; Song, K.; Li, B.; Zhang, Y.; Yang, F.; Wang, Y.; Wang, C.; Chi, Y.; Yang, X. Performance Enhancement for Indium-Free Metal Oxide Thin-Film Transistors with Double-Active-Layers by Magnetron Sputtering at Room Temperature. Micromachines 2022, 13, 2024. [Google Scholar] [CrossRef] [PubMed]

- Bao, B.; Karnaushenko, D.D.; Xu, J.; Wang, S.; Bandari, V.K.; Schmidt, O.G.; Karnaushenko, D. Flexible IGZO TFT Technology for Shift Register Drivers. Adv. Electron. Mater. 2024, 10, 2400036. [Google Scholar] [CrossRef]

- Sheng, J.; Hong, T.; Lee, H.M.; Kim, K.; Sasase, M.; Kim, J.; Hosono, H.; Park, J.S. Amorphous IGZO TFT with High Mobility of ∼70 cm2 V−1 s−1 via Vertical Dimension Control Using PEALD. ACS Appl. Mater. Interfaces 2019, 11, 40401–40409. [Google Scholar] [CrossRef]

- Huang, X.; Chen, C.; Sun, F.; Chen, X.; Xu, W.; Li, L. Enhancing the Carrier Mobility and Bias Stability in Metal–Oxide Thin Film Transistors with Bilayer InSnO/a-InGaZnO Heterojunction Structure. Micromachines 2024, 15, 512. [Google Scholar] [CrossRef] [PubMed]

| Aspect | FDM (ABS) Shadow Masks | High-Definition 3D (MJP) | Multiphoton/µSLA Techniques |

|---|---|---|---|

| Feature resolution | ≈100–400 µm (no finer than nozzle size) | ~1 mm features, better fidelity | Sub-micron to ~100 nm achievable |

| Mask thickness | ~1–2 mm for stability | Similar or thicker | Thin, high-fidelity masks via resin structures |

| Sub-micron feasibility | No | No | Yes, in principle (via different methods) |

| Large-area scaling | Limited by alignment, deformation, deposition | Improved but still limited | Not typical; fundamentally different process |

| Material constraints | ABS (thermal, mechanical limitations) | Photopolymers (post-processing needed) | Resin materials, special development |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yarbrough, K.A.; Behera, M.K.; Pradhan, S.K.; Bahoura, M. A Novel, Single-Step 3D-Printed Shadow Mask Fabrication Method for TFTs. Processes 2025, 13, 2976. https://doi.org/10.3390/pr13092976

Yarbrough KA, Behera MK, Pradhan SK, Bahoura M. A Novel, Single-Step 3D-Printed Shadow Mask Fabrication Method for TFTs. Processes. 2025; 13(9):2976. https://doi.org/10.3390/pr13092976

Chicago/Turabian StyleYarbrough, Kelsea A., Makhes K. Behera, Sangram K. Pradhan, and Messaoud Bahoura. 2025. "A Novel, Single-Step 3D-Printed Shadow Mask Fabrication Method for TFTs" Processes 13, no. 9: 2976. https://doi.org/10.3390/pr13092976

APA StyleYarbrough, K. A., Behera, M. K., Pradhan, S. K., & Bahoura, M. (2025). A Novel, Single-Step 3D-Printed Shadow Mask Fabrication Method for TFTs. Processes, 13(9), 2976. https://doi.org/10.3390/pr13092976