Sub-THz Small-Signal Equivalent Circuit Model and Parameter Extraction for 3 nm Gate-All-Around Nanosheet Transistor

Abstract

:1. Introduction

2. Material and Methods

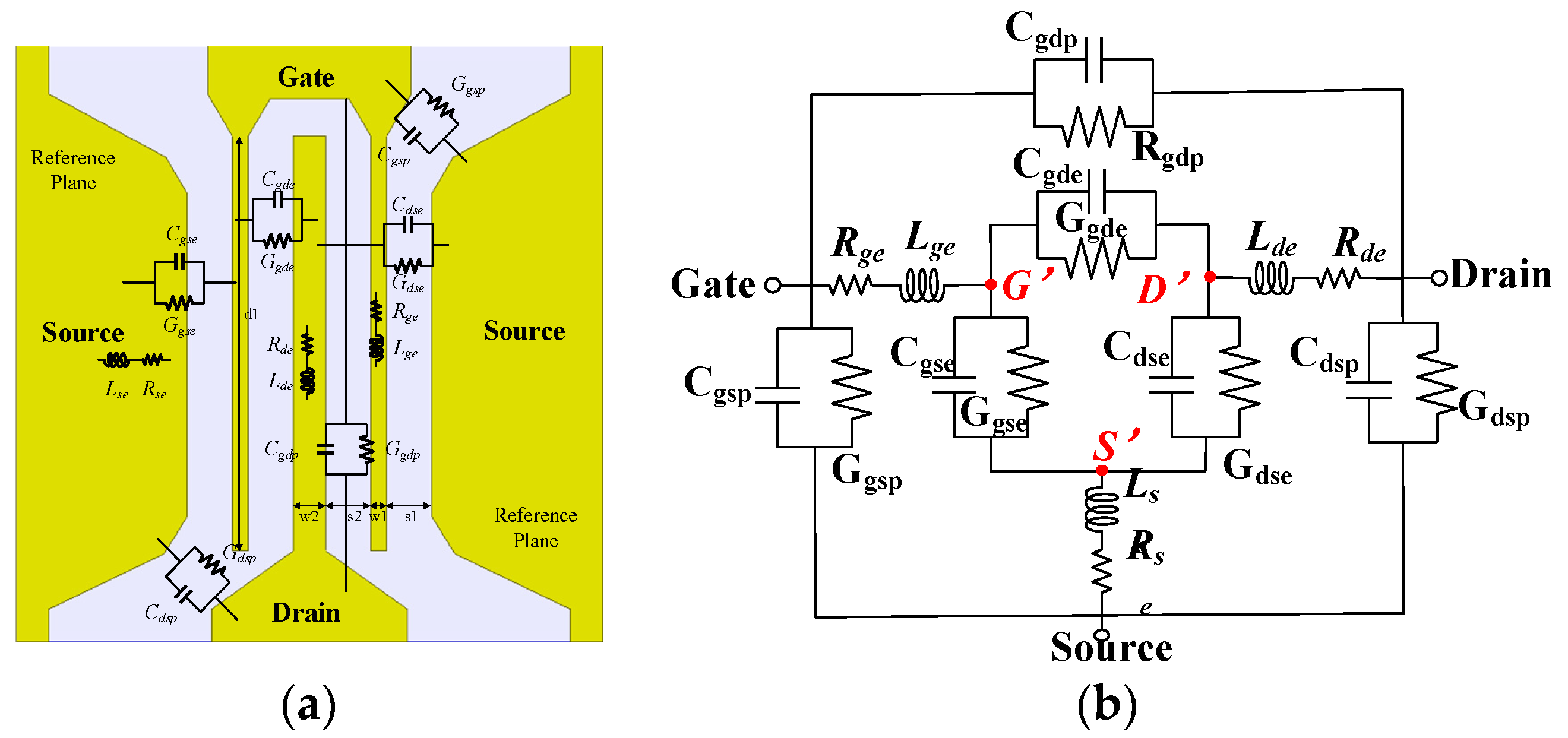

2.1. Device Structure and Equivalent Circuit Model

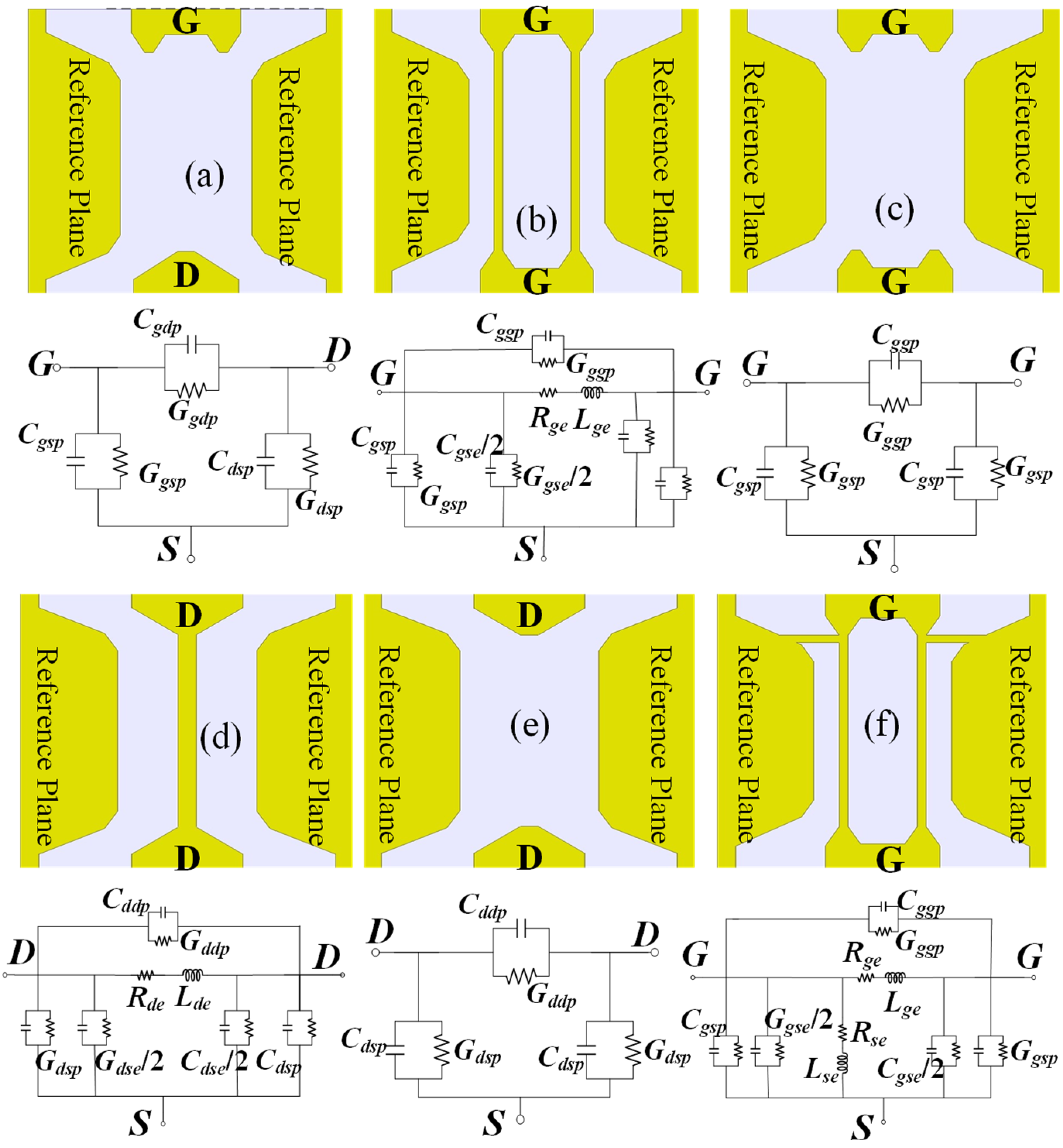

2.2. Extrinsic Layout Test Structures and Parameter Extraction Algorithm

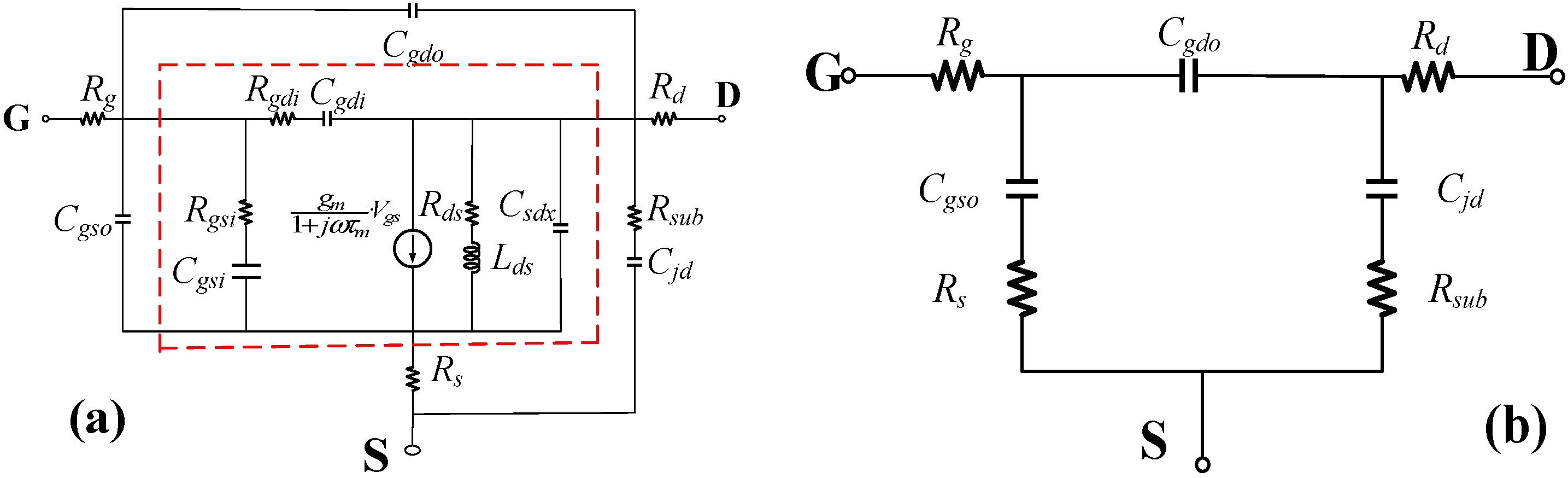

2.3. Improved Extraction Method of Intrinsic Device Equivalent Circuit

3. Result and Discussion

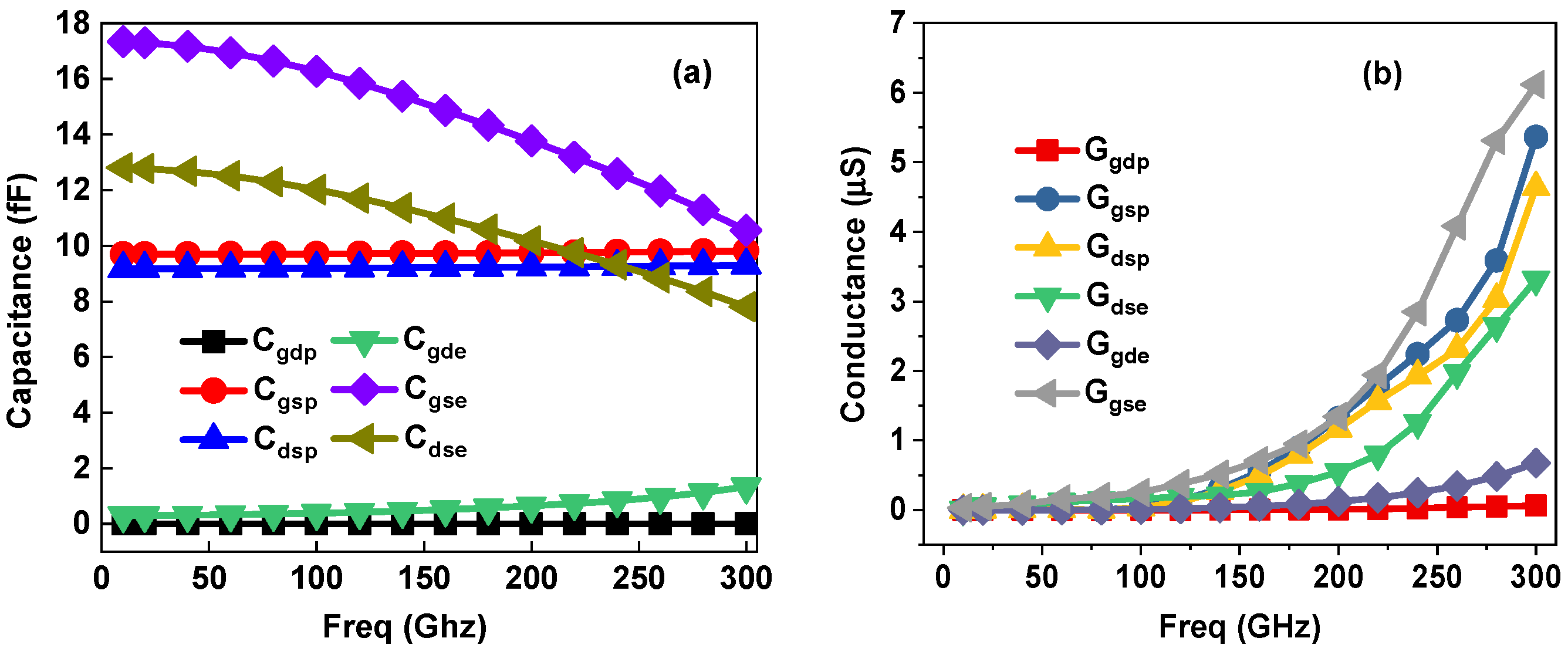

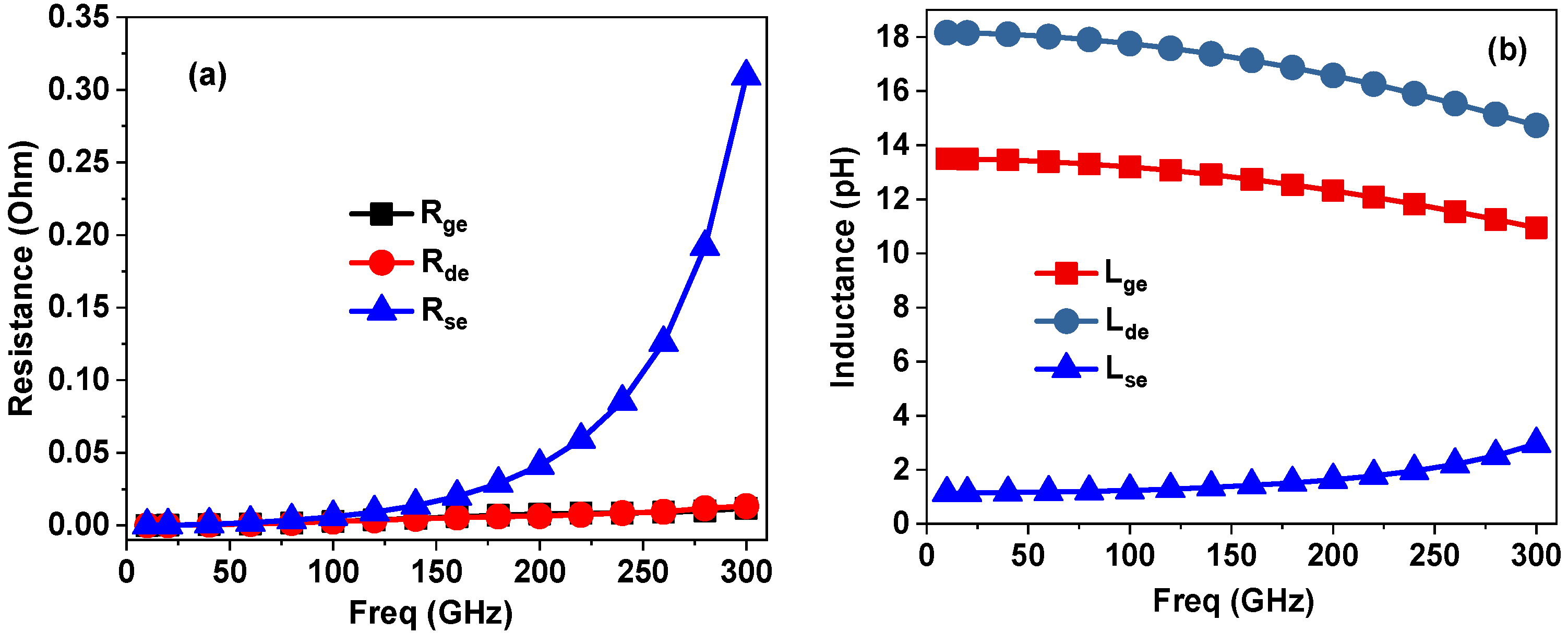

3.1. Validation of Extraction Method for Extrinsic Layout

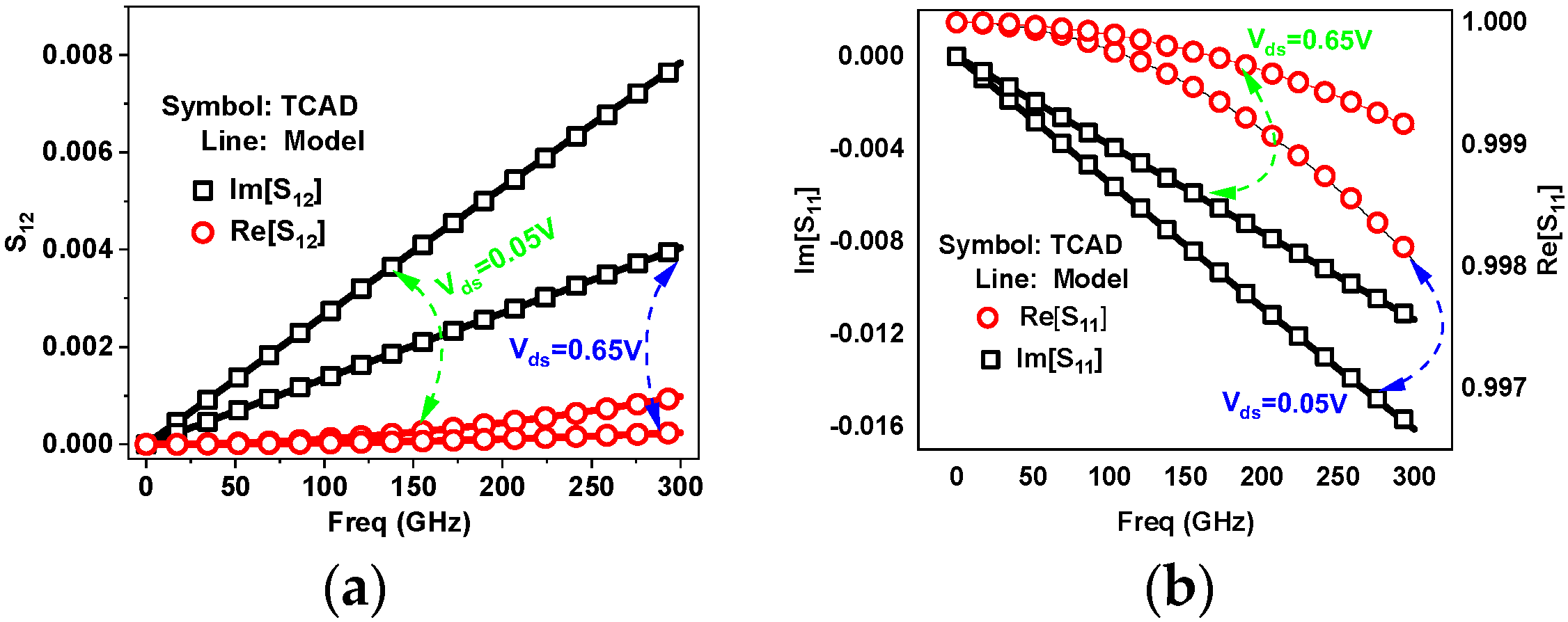

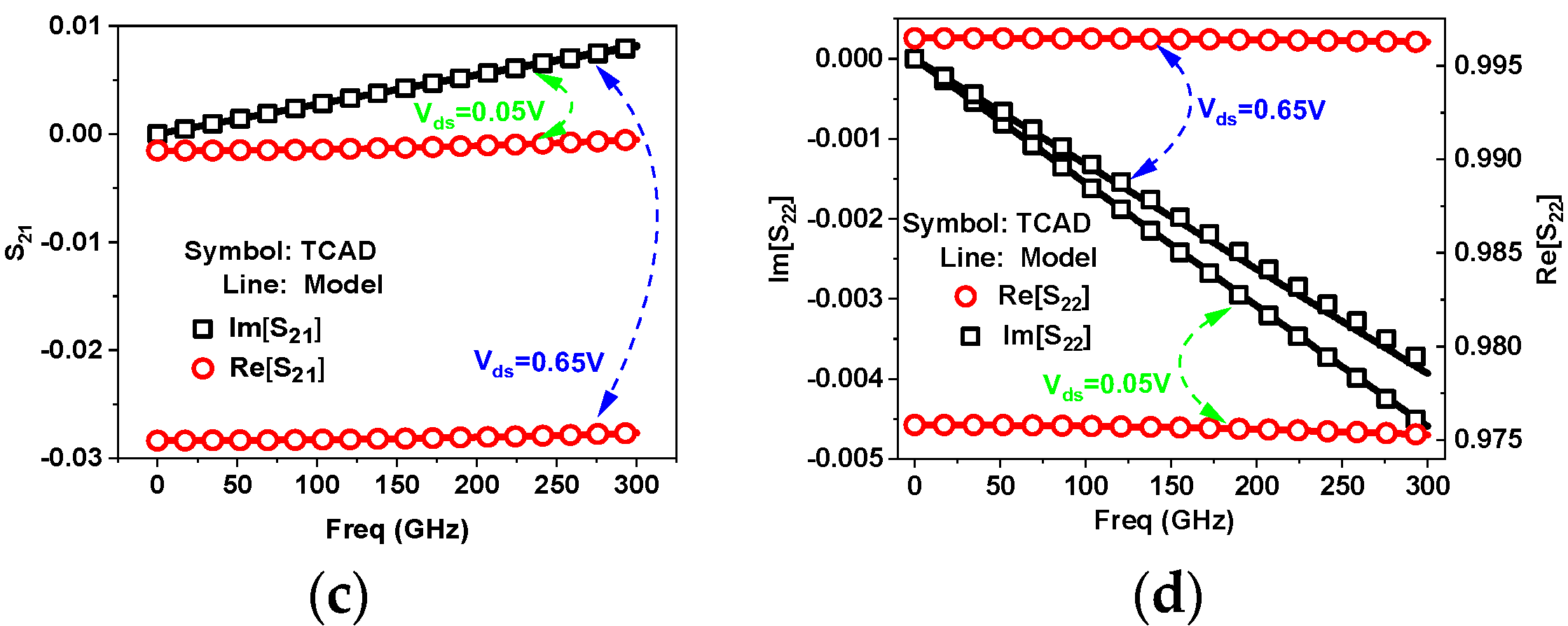

3.2. Validation of Extraction Method for Intrinsic Device

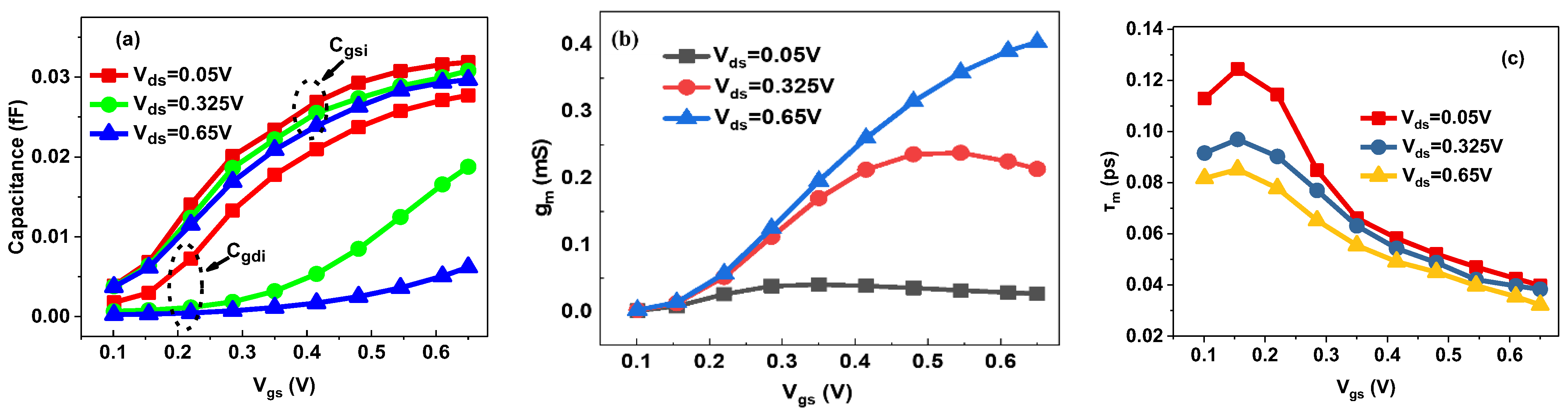

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- D’Agostino, F.; Quercia, D. Short-Channel Effects in MOSFETs. In Integrated Nanoelectronics. NanoScience and Technology; Springer: New Delhi, India, 2016. [Google Scholar] [CrossRef]

- Lee, H.J.; Rami, S.; Ravikumar, S.; Neeli, V.; Phoa, K.; Sell, B.; Zhang, Y. Intel 22nm FinFET (22FFL) Process Technology for RF and mmWave Applications and Circuit Design Optimization for FinFET Technology. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Heydari, B.; Bohsali, M.; Adabi, E.; Niknejad, A.M. Millimeter-wave devices and circuit blocks up to 104 GHz in 90 nm CMOS. IEEE J. Solid-State Circuits 2007, 42, 2893–2903. [Google Scholar] [CrossRef] [Green Version]

- Qin, M.; Sun, Y.; Li, X.; Shi, Y. Analytical parameter extraction for small-signal equivalent Circuit of 3D FinFET into Sub-THz range. IEEE Access 2018, 6, 19752–19761. [Google Scholar] [CrossRef]

- Sun, Y.; Gao, H.; Li, X.; Yang, X.; Liu, Z.; Liu, Y.; Li, X.; Shi, Y. Impact of process fluctuations on RF small-signal parameter of gate-all-around nanosheet transistor beyond 3 nm node. IEEE Trans. Electron. Devices 2021, 69, 31–38. [Google Scholar] [CrossRef]

- Zhang, W.; Yin, S.; Hu, W.; Wang, Y. Novel Physics-based small-signal modeling and characterization for advanced RF bulk FinFETs. IEEE Trans. Electron. Devices 2021, 68, 2160–2166. [Google Scholar] [CrossRef]

- Koolen, M.; Geelen, J.; Versleijen, M. An improved de-embedding technique for on-wafer high-frequency characterization. In Proceedings of the 1991 Bipolar Circuits and Technology Meeting, Minneapolis, MN, USA, 9–10 September 1991. [Google Scholar]

- Crupi, G.; Schreurs, D.M.-P.; Caddemi, A. Accurate silicon dummy structure model for nonlinear microwave FinFET modeling. Microelectron. J. 2010, 41, 574–578. [Google Scholar] [CrossRef]

- Karisan, Y.; Caglayan, C.; Trichopoulos, G.C.; Sertel, K. Lumped-element equivalent-circuit modeling of millimeter-wave HEMT parasitics through full-wave electromagnetic analysis. IEEE Trans. Microw. Theory Tech. 2016, 64, 1419–1430. [Google Scholar] [CrossRef]

- Liu, Z.; Huang, X.; Lee, F.C.; Li, Q. Package parasitic inductance extraction and simulation model development for the high-voltage cascode GaN HEMT. IEEE Trans. Power Electron. 2013, 29, 1977–1985. [Google Scholar] [CrossRef]

- Karisan, Y.; Sertel, K. Extraction of parasitics in GaN HEMTs via full-wave electromagnetic modeling. In Proceedings of the NAECON 2014-IEEE National Aerospace and Electronics Conference, Dayton, OH, USA, 24–27 June 2014; pp. 306–307. [Google Scholar]

- Jung, J.-H.; Lee, J.-H. Extraction of substrate resistance in bulk FinFETs through RF modeling. IEEE Microw. Wirel. Compon. Lett. 2007, 17, 358–360. [Google Scholar] [CrossRef]

- Deschrijver, D.; Avolio, G.; Schreurs, D.; Dhaene, T.; Crupi, G.; Knockaert, L. Microwave small-signal modelling of FinFETs using multi-parameter rational fitting method. Electron. Lett. 2011, 47, 1084–1086. [Google Scholar] [CrossRef] [Green Version]

- Chalkiadaki, M.-A.; Enz, C.C. RF Small-signal and noise modeling including parameter extraction of nanoscale MOSFET from weak to strong inversion. IEEE Trans. Microw. Theory Tech. 2015, 63, 2173–2184. [Google Scholar] [CrossRef]

- Crupi, G.; Schreurs, D.; Parvais, B.; Caddemi, A.; Mercha, A.; Decoutere, S. Scalable and multibias high frequency modeling of multi-fin FETs. Solid-State Electron. 2006, 50, 1780–1786. [Google Scholar] [CrossRef]

- Kang, I.M.; Shin, H. Non-quasi-static small-signal modeling and analytical parameter extraction of SOI FinFETs. IEEE Trans. Nanotechnol. 2006, 5, 205–210. [Google Scholar] [CrossRef]

- Zhu, G.; Chang, C.; Xu, Y.; Zhang, Z.; Al-saman, A.A.; Lin, F. A millimeter-wave scalable small-signal modeling approach based on FW-EM for AlGaNGaN HEMT up to 110_GHz. Microw. Opt. Technol. Lett. 2020, 63, 2145–2152. [Google Scholar] [CrossRef]

- Jia, Y.; Xu, Y.; Xu, R.; Li, Y. An accurate parasitic parameters extraction method based on FW-EM for AlGaNGaN HEMT up to 110 GHz. Int. J. Numer. Model. Electron. Netw. Devices Fields 2017, 31, 2270. [Google Scholar] [CrossRef]

- Choe, K.; An, T.; Kim, S. Accurate fringe capacitance model considering RSD and metal contact for realistic FinFETs and circuit performance simulation. In Proceedings of the 2014 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Yokohama, Japan, 9–11 September 2014; pp. 29–32. [Google Scholar]

- Chen, Y.; Zhang, Y.; Xu, Y.; Sun, Y.; Cheng, W.; Lu, H.; Xiao, F.; Xu, R. Investigation of Terahertz 3D EM Simulation on Device Modeling and A New InP HBT Dispersive Inter-Electrode Impedance Extraction Method. IEEE Access 2018, 6, 45772–45781. [Google Scholar] [CrossRef]

- Zheng, J.; Hahm, Y.-C.; Tripathi, V.; Weisshaar, A. CAD-oriented equivalent-circuit modeling of on-chip interconnects on lossy silicon substrate. IEEE Trans. Microw. Theory Tech. 2000, 48, 1443–1451. [Google Scholar] [CrossRef] [Green Version]

- Tsividis, Y. Operation and Modeling of MOS Transistor; McGraw-Hill: New York, NY, USA, 1999. [Google Scholar]

| Parameters | Values | Confidence Intervals (CIs) |

|---|---|---|

| N10 (1 × 10−31) | 3.747 | (3.745, 3.749) |

| N20 (1 × 10−31) | 1.995 | (1.991, 1.998) |

| N30 (1 × 10−17) | 1.466 | (1.465, 1.467) |

| N40 (1 × 10−31) | 2.185 | (2.179, 2.182) |

| N50 (1 × 10−17) | 1.565 | (1.564, 1.566) |

| Parameters | Values | Confidence Intervals (CIs) |

|---|---|---|

| K10 (1 × 10−16) | 0.2968 | (0.2968, 0.2968) |

| K20 (1 × 10−31) | 8.072 | (8.07, 8.075) |

| K30 (1 × 10−16) | 0.2772 | (0.2772, 0.2773) |

| K40 (1 × 10−31) | 10.23 | (10.23, 10.24) |

| K50 (1 × 10−18) | −0.8724 | (–0.8726, –0.8721) |

| K60 (1 × 10−4) | 0.2706 | (0.2705, 0.2706) |

| K70 (1 × 10−17) | –1.187 | (–1.188, –1.187) |

| K80 (1 × 10−3) | 2.357 | (2.357, 2.357) |

| K90 (1 × 10−23) | 0.2484 | (0.2469, 0.2498) |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, Y.; Gao, H.; Hu, S.; Liu, Z.; Li, X.; Liu, Y.; Shi, Y. Sub-THz Small-Signal Equivalent Circuit Model and Parameter Extraction for 3 nm Gate-All-Around Nanosheet Transistor. Processes 2022, 10, 1198. https://doi.org/10.3390/pr10061198

Sun Y, Gao H, Hu S, Liu Z, Li X, Liu Y, Shi Y. Sub-THz Small-Signal Equivalent Circuit Model and Parameter Extraction for 3 nm Gate-All-Around Nanosheet Transistor. Processes. 2022; 10(6):1198. https://doi.org/10.3390/pr10061198

Chicago/Turabian StyleSun, Yabin, Hengbin Gao, Shaojian Hu, Ziyu Liu, Xiaojin Li, Yun Liu, and Yanling Shi. 2022. "Sub-THz Small-Signal Equivalent Circuit Model and Parameter Extraction for 3 nm Gate-All-Around Nanosheet Transistor" Processes 10, no. 6: 1198. https://doi.org/10.3390/pr10061198

APA StyleSun, Y., Gao, H., Hu, S., Liu, Z., Li, X., Liu, Y., & Shi, Y. (2022). Sub-THz Small-Signal Equivalent Circuit Model and Parameter Extraction for 3 nm Gate-All-Around Nanosheet Transistor. Processes, 10(6), 1198. https://doi.org/10.3390/pr10061198