Analog Implementation of a Spiking Neuron with Memristive Synapses for Deep Learning Processing

Abstract

1. Introduction

2. Materials and Methods

2.1. Neuron Modeling

2.2. Memristor Modeling

Vourkas Memristor Model

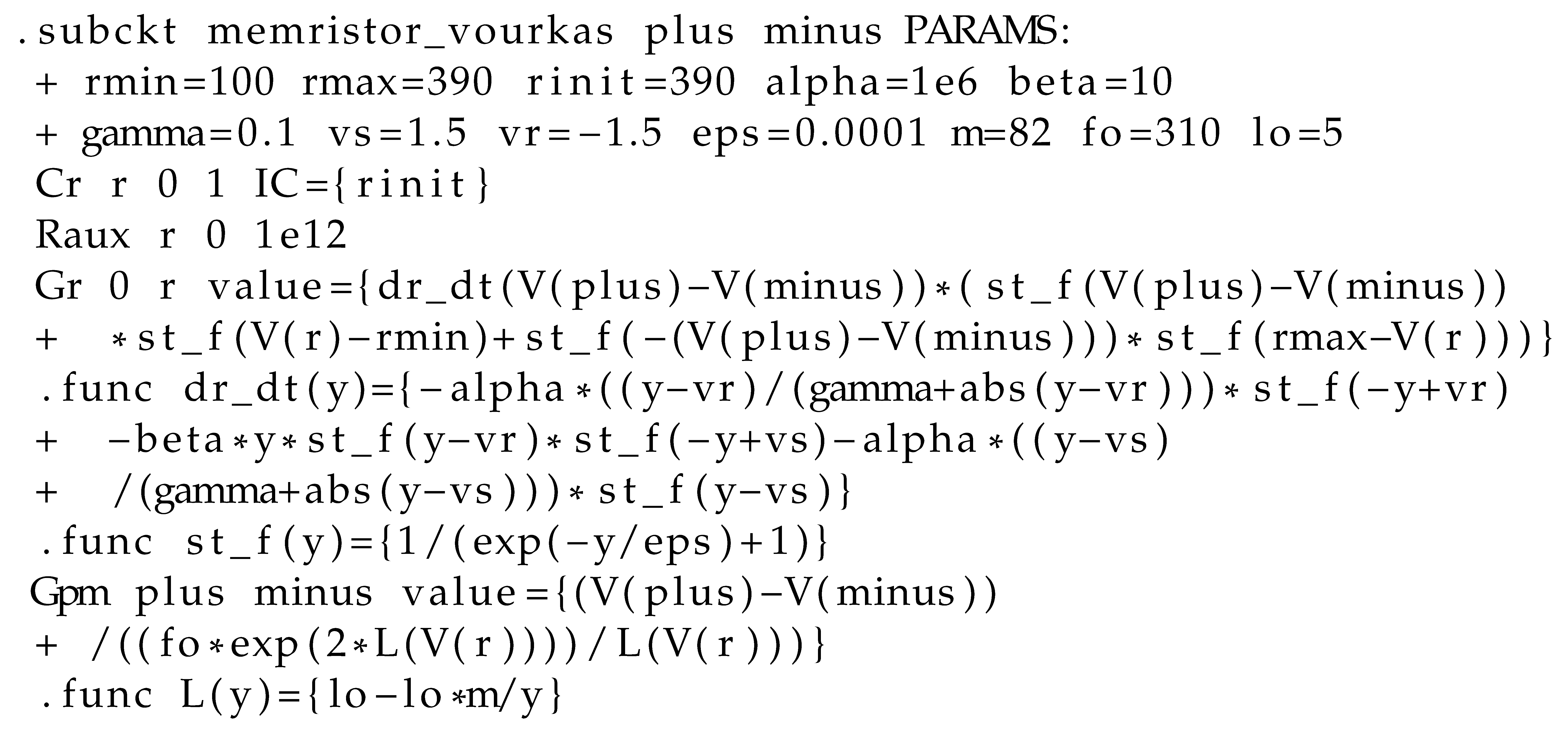

| Listing 1. SPICE code for the Vourkas macromodel. |

|

2.3. Synaptic Weight Adjustment in Neurons

2.3.1. Long-Term Potentiation and Long-Term Depression on Memristive Synapses

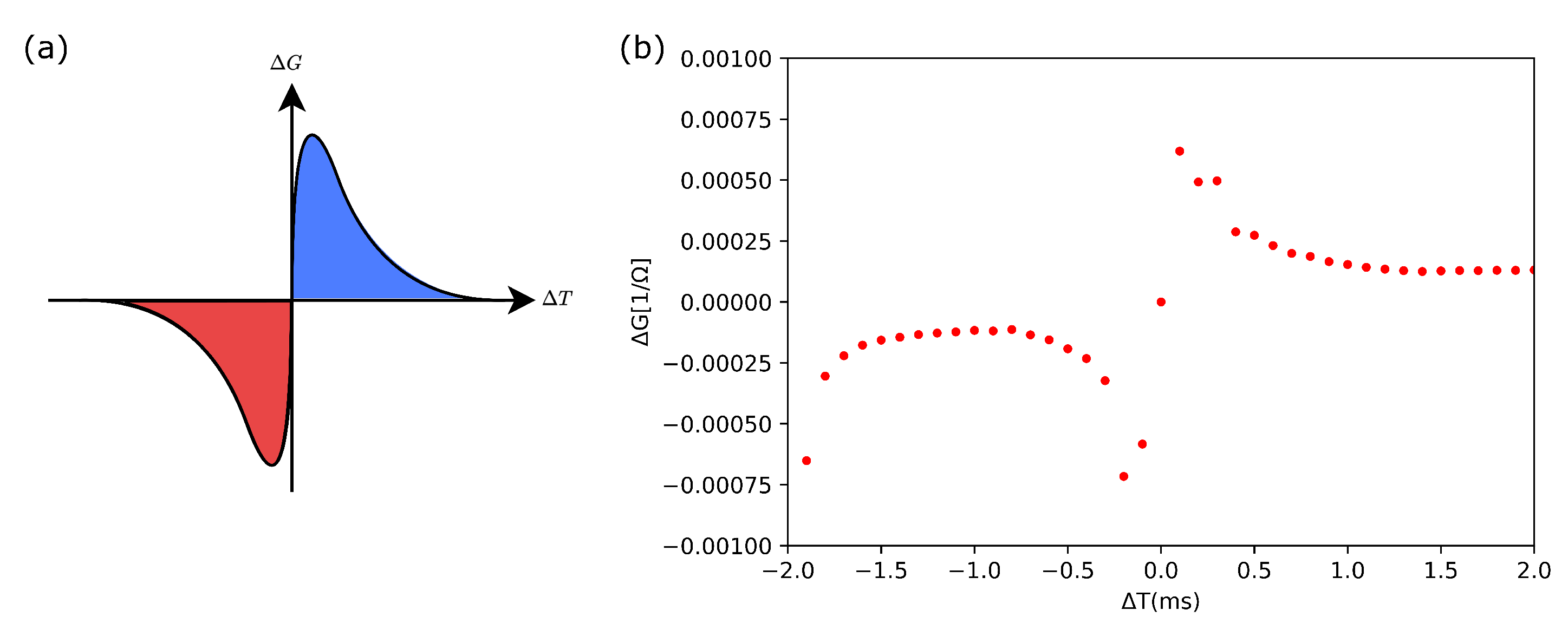

2.3.2. Spike-Timing-Dependent Plasticity

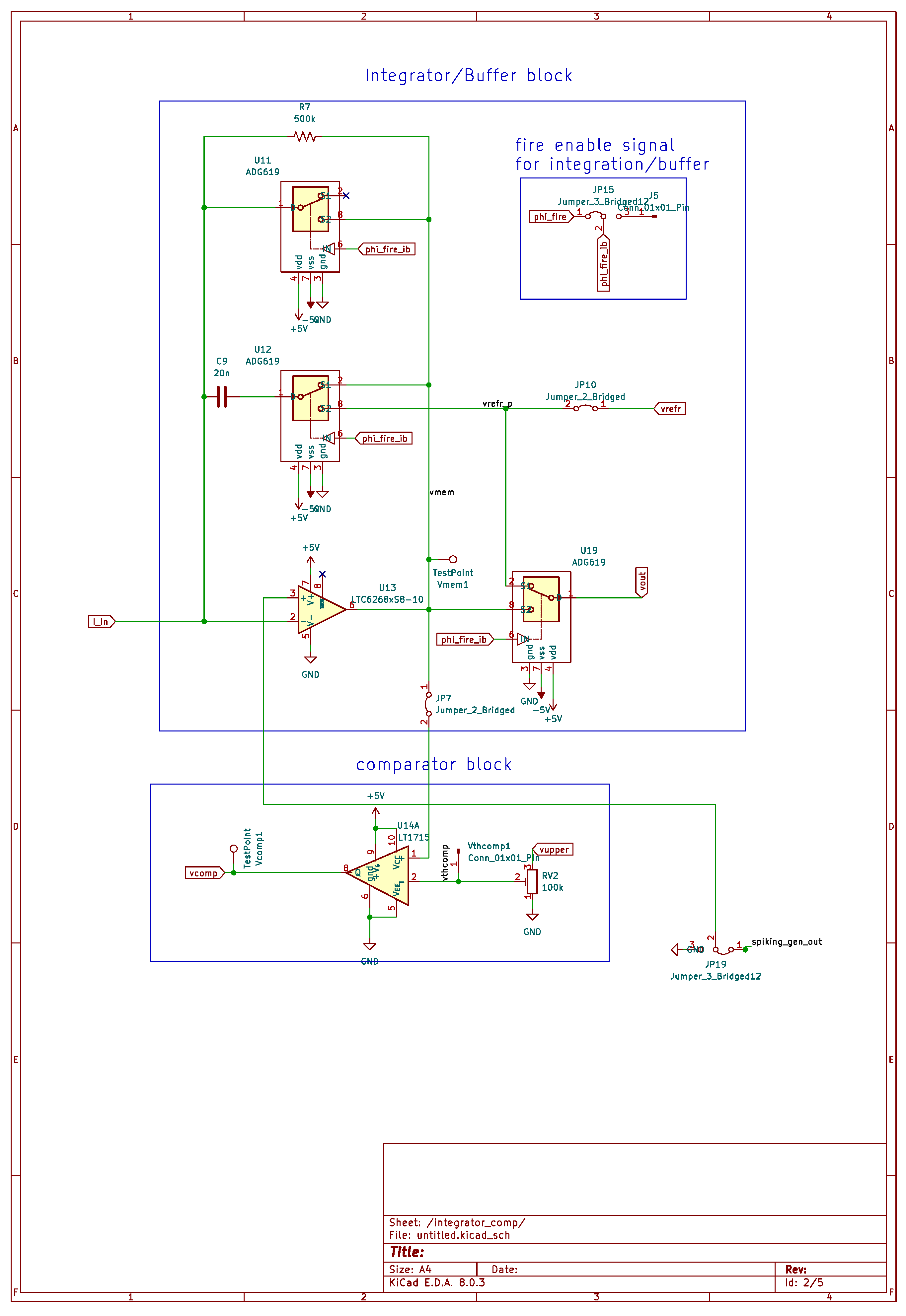

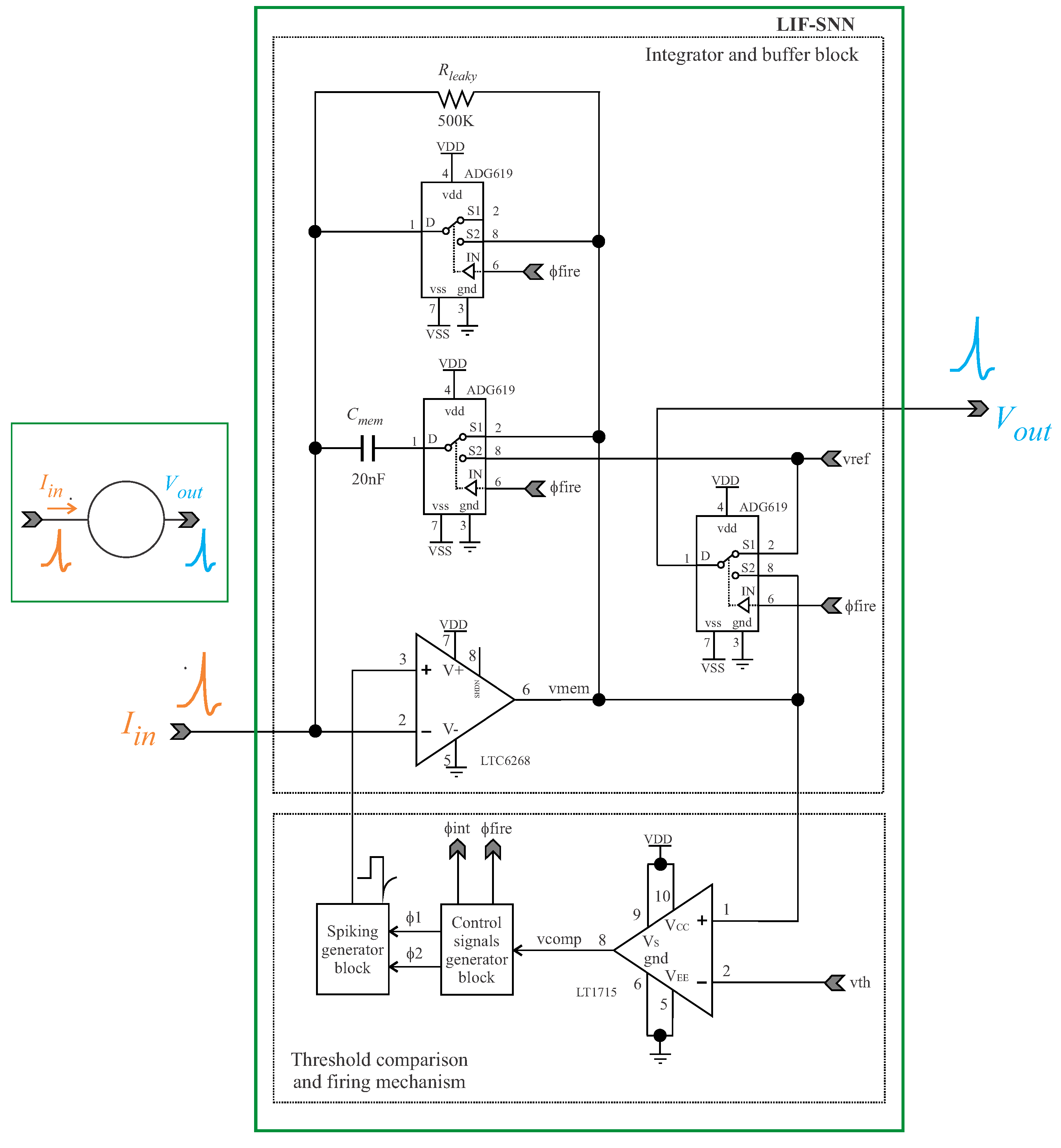

2.4. Analog Leaky Integrate-and-Fire Functional Blocks and Control Signals

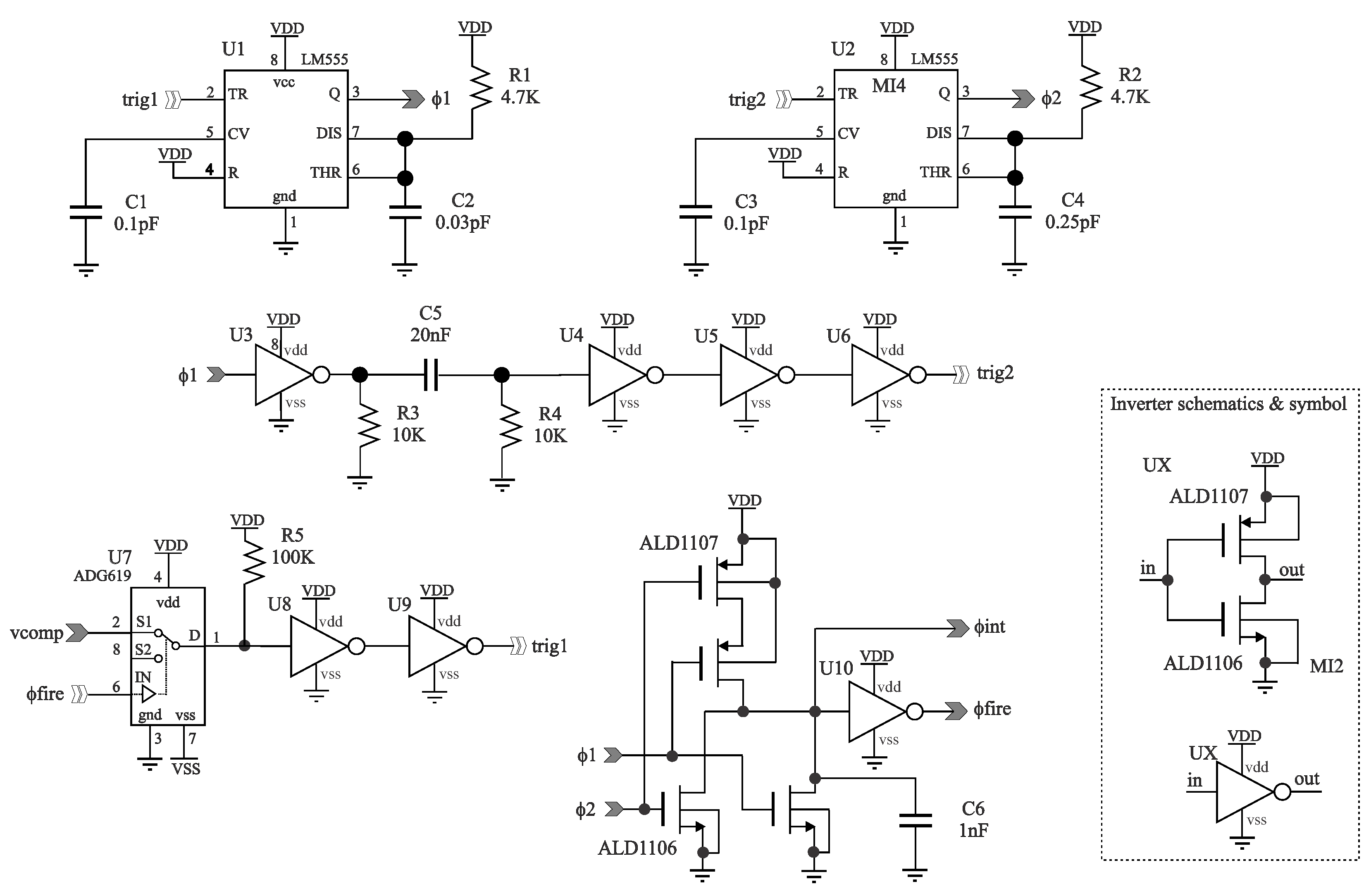

Phase Control for Reconfiguration of the LIF Neuron

2.5. Electrical Characteristics of the Block Components of the LIF Neuron

2.5.1. Integration/Buffer and Comparator Module

2.5.2. Selection of Transmission Gates Modules

2.5.3. Spiking Generator Block Design

- The commercial memristors by Knowm exhibit the greatest change in memristance at a low frequency (1 Hz) and the smallest change at a high frequency (1 KHz) [42].

- A total relaxation time of 1.25 ms is within the absolute refractory period of mammal neurons, where neurons cannot generate new output spikes [43], contributing to sparse computing with low power.

3. Results

3.1. Electrical Simulation of the LIF Neuron

| Algorithm 1: Least squares regression algorithm for logarithm fitting. |

|

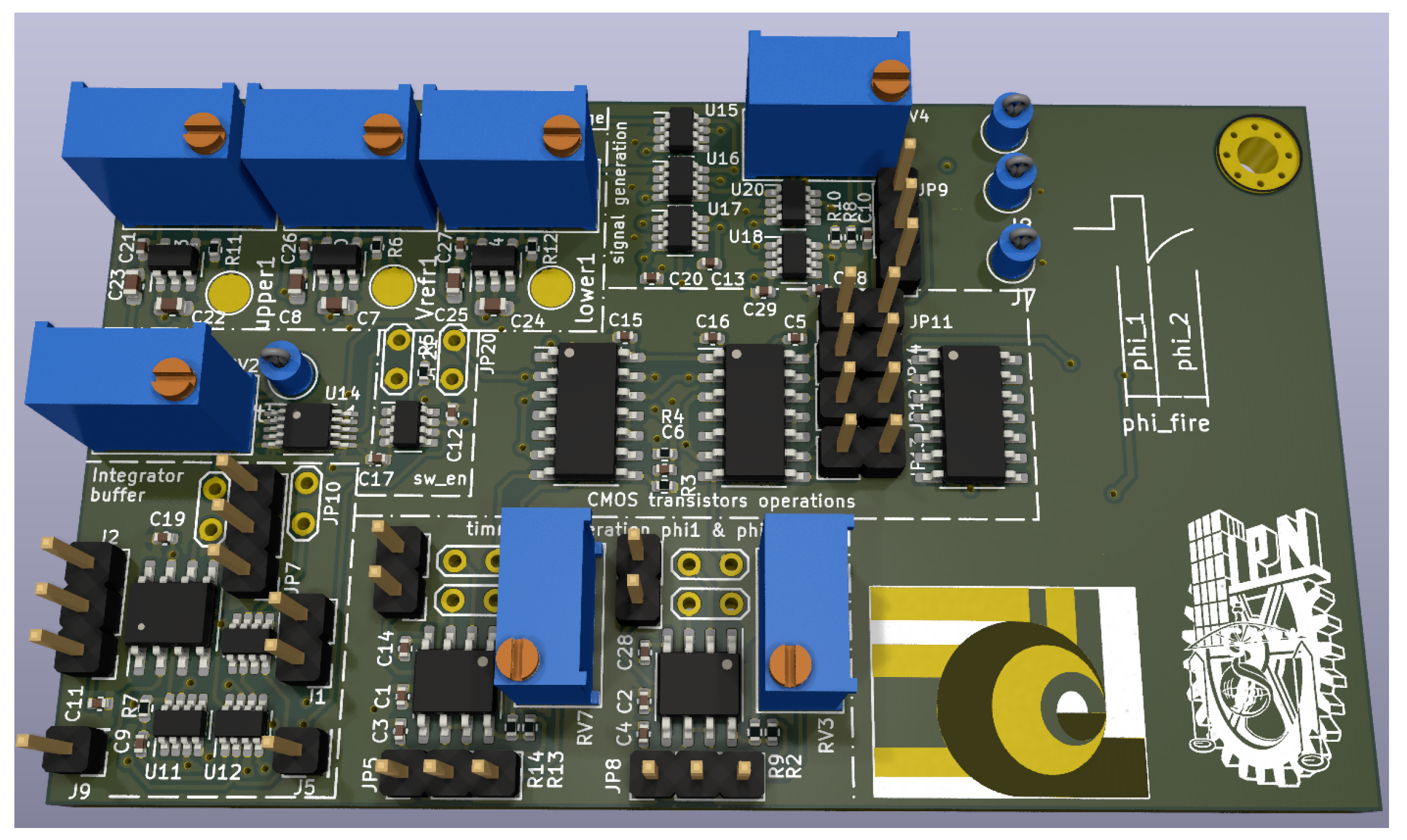

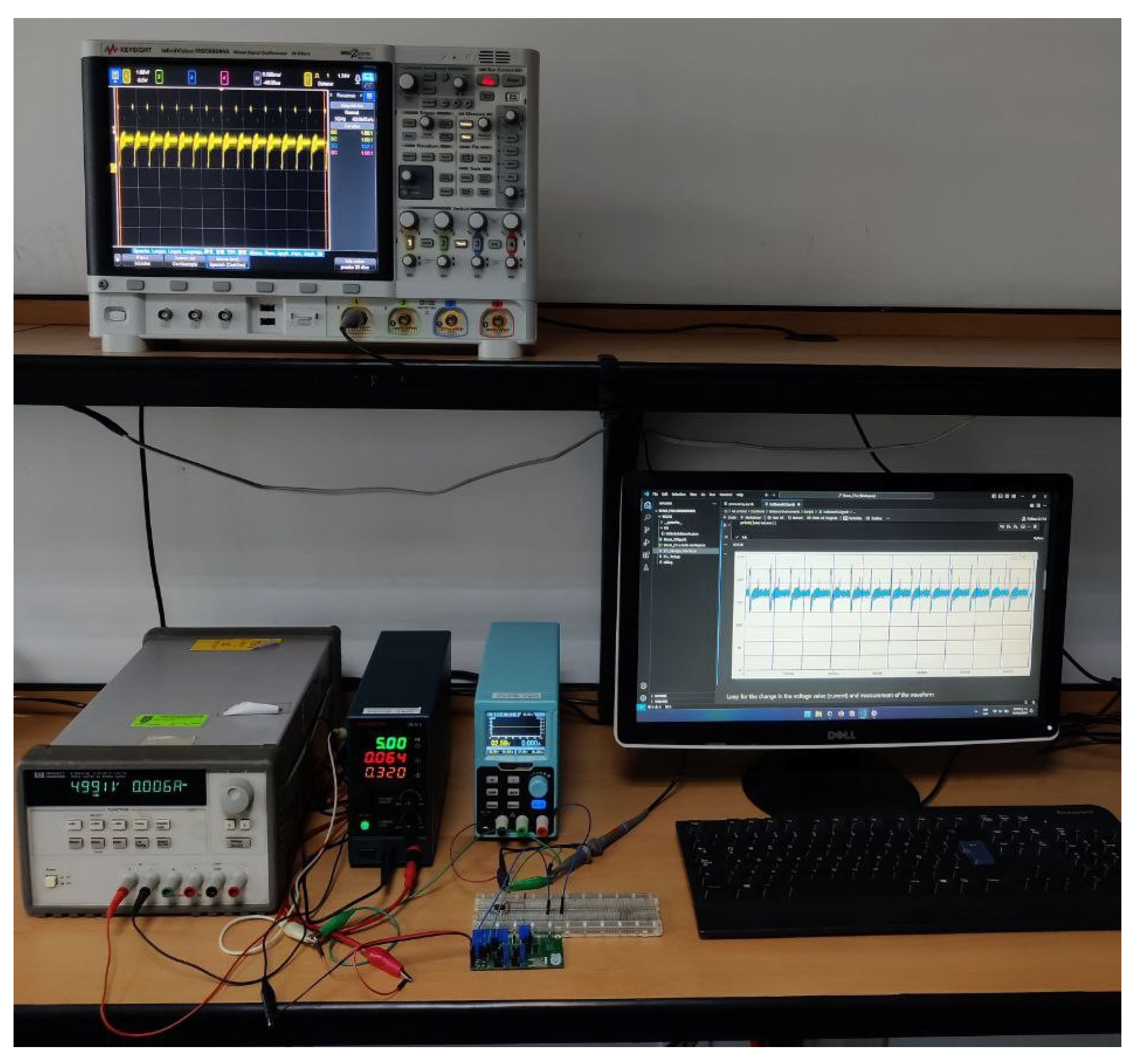

3.2. Hardware Implementation of the LIF Neuron

Methodology for the Characterization of the Physical LIF Neuron

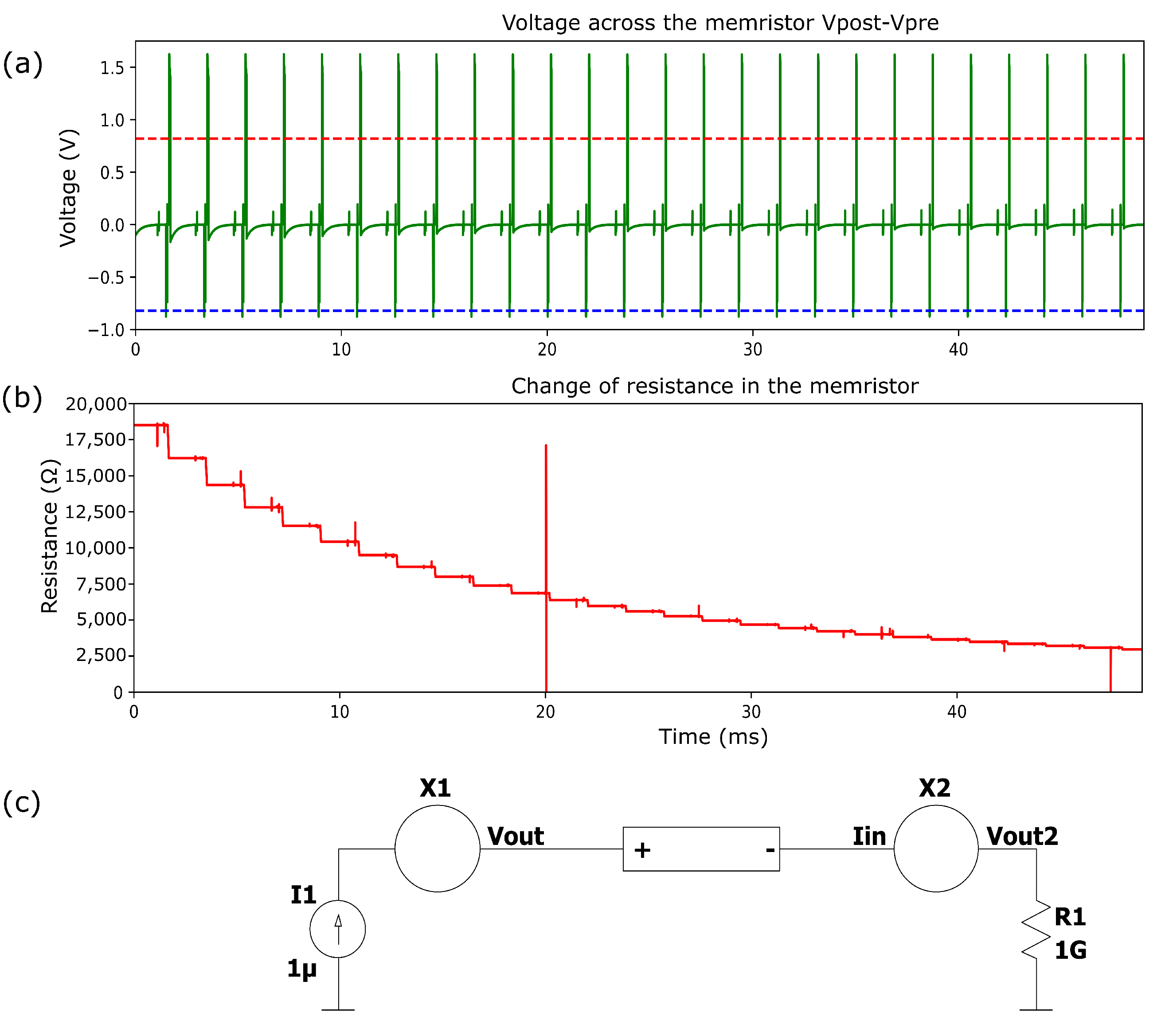

3.3. Simulation of the Synaptic Weight Adjustment of a Memristive Synapse

3.3.1. Long-Term Potentiation on Memristive Synapse

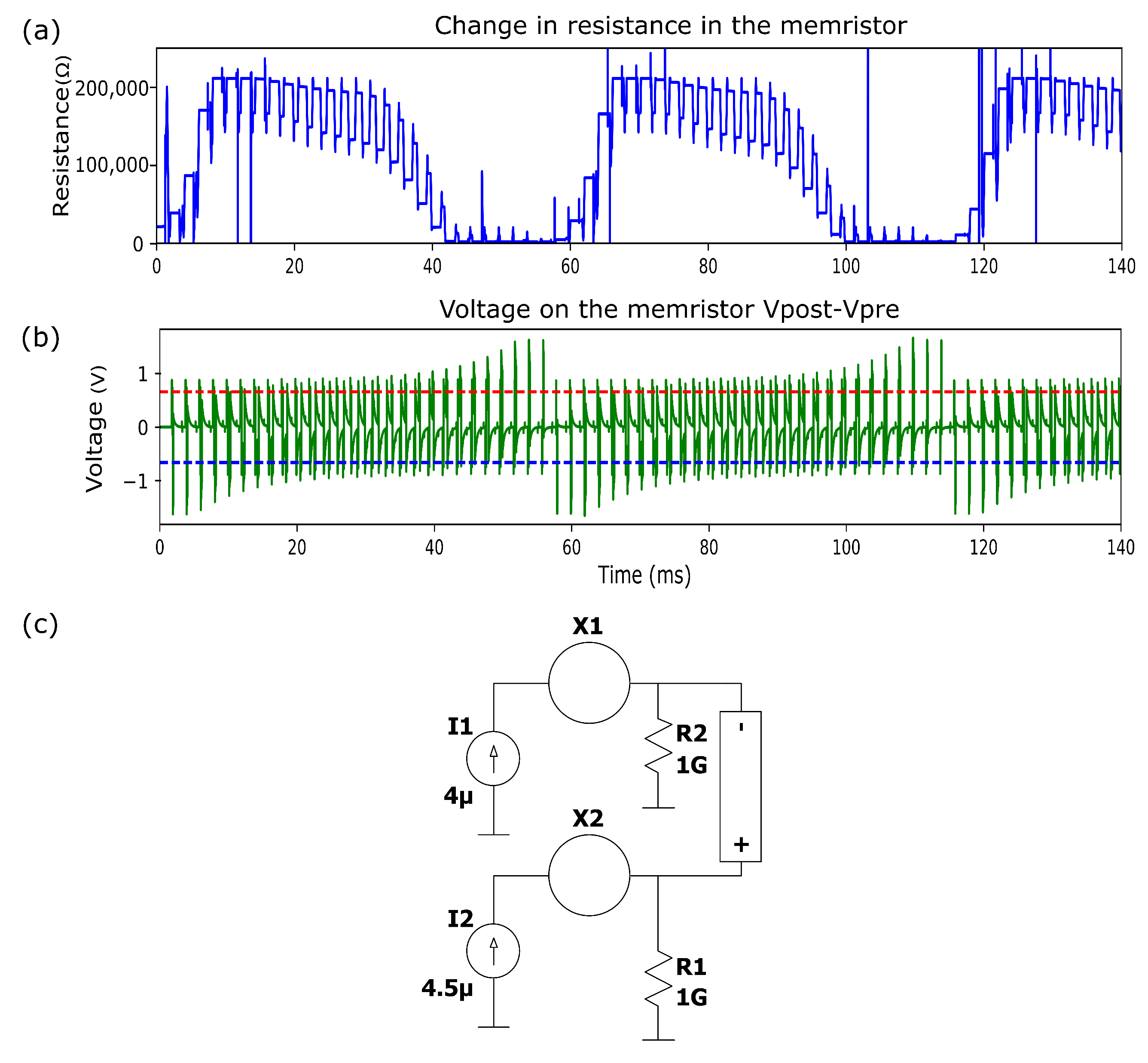

3.3.2. Spike-Timing-Dependent Plasticity (STDP) Process on a Memristive Synapse

4. Conclusions

Future Work

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Abbreviations

| Opamp | Operational amplifier |

| LIF | Leaky integrate-and-fire |

| STDP | Spike timing-dependent plasticity |

| LTP | Long-term potentiation |

| LTD | Long-term depression |

Appendix A

References

- Brown, T.B.; Mann, B.; Ryder, N.; Subbiah, M.; Kaplan, J.; Dhariwal, P.; Neelakantan, A.; Shyam, P.; Sastry, G.; Askell, A.; et al. Language Models are Few-Shot Learners. arXiv 2020, arXiv:2005.14165. [Google Scholar]

- Ramesh, A.; Dhariwal, P.; Nichol, A.; Chu, C.; Chen, M. Hierarchical Text-Conditional Image Generation with CLIP Latents. arXiv 2022, arXiv:2204.06125. [Google Scholar]

- Luccioni, A.S.; Viguier, S.; Ligozat, A.L. Estimating the Carbon Footprint of BLOOM, a 176B Parameter Language Model. arXiv 2022, arXiv:2211.02001. [Google Scholar]

- Mead, C.; Ismail, M. (Eds.) Analog VLSI Implementation of Neural Systems; Springer: New York, NY, USA, 1989. [Google Scholar] [CrossRef]

- Canales-Verdial, J.I.; Wagner, J.R.; Schmucker, L.A.; Wetzel, M.; Proctor, P.; Carson, M.; Meng, J.; Withers, N.J.; Harris, C.T.; Nogan, J.J.; et al. Energy-Efficient Neuromorphic Architectures for Nuclear Radiation Detection Applications. Sensors 2024, 24, 2144. [Google Scholar] [CrossRef] [PubMed]

- Udaya Mohanan, K. Resistive Switching Devices for Neuromorphic Computing: From Foundations to Chip Level Innovations. Nanomaterials 2024, 14, 527. [Google Scholar] [CrossRef]

- Vohra, S.K.; Thomas, S.A.; Sakare, M.; Das, D.M. Circuit implementation of on-chip trainable spiking neural network using CMOS based memristive STDP synapses and LIF neurons. Integration 2024, 95, 102122. [Google Scholar] [CrossRef]

- Maass, W. Networks of spiking neurons: The third generation of neural network models. Neural Netw. 1997, 10, 1659–1671. [Google Scholar] [CrossRef]

- Rana, A.; Kim, K.K. Electrocardiography Classification with Leaky Integrate-and-Fire Neurons in an Artificial Neural Network-Inspired Spiking Neural Network Framework. Sensors 2024, 24, 3426. [Google Scholar] [CrossRef] [PubMed]

- Padovano, D.; Carpegna, A.; Savino, A.; Di Carlo, S. SpikeExplorer: Hardware-Oriented Design Space Exploration for Spiking Neural Networks on FPGA. Electronics 2024, 13, 1744. [Google Scholar] [CrossRef]

- Passias, A.; Tsakalos, K.A.; Kansizoglou, I.; Kanavaki, A.M.; Gkrekidis, A.; Menychtas, D.; Aggelousis, N.; Michalopoulou, M.; Gasteratos, A.; Sirakoulis, G.C. A Biologically Inspired Movement Recognition System with Spiking Neural Networks for Ambient Assisted Living Applications. Biomimetics 2024, 9, 296. [Google Scholar] [CrossRef]

- Costandi, M. Neuroplasticity; The MIT Press Essential Knowledge Series; MIT Press: London, UK, 2016. [Google Scholar]

- Chakraborty, I.; Jaiswal, A.; Saha, A.K.; Gupta, S.K.; Roy, K. Pathways to efficient neuromorphic computing with non-volatile memory technologies. Appl. Phys. Rev. 2020, 7, 021308. [Google Scholar] [CrossRef]

- Kornijcuk, V.; Lim, H.; Seok, J.Y.; Kim, G.; Kim, S.K.; Kim, I.; Choi, B.J.; Jeong, D.S. Leaky Integrate-and-Fire Neuron Circuit Based on Floating-Gate Integrator. Front. Neurosci. 2016, 10, 212. [Google Scholar] [CrossRef] [PubMed]

- Linares-Barranco, B.; Serrano-Gotarredona, T.; Camuñas-Mesa, L.; Perez-Carrasco, J.; Zamarreño-Ramos, C.; Masquelier, T. On Spike-Timing-Dependent-Plasticity, Memristive Devices, and Building a Self-Learning Visual Cortex. Front. Neurosci. 2011, 5, 26. [Google Scholar] [CrossRef]

- Chua, L. Memristor-The missing circuit element. IEEE Trans. Circuit Theory 1971, 18, 507–519. [Google Scholar] [CrossRef]

- AI hardware has an energy problem. Nat. Electron. 2023, 6, 463. [CrossRef]

- Feng, R.; Li, J.; Xie, S.; Mao, X. Efficient Training Method for Memristor-Based Array Using 1T1M Synapse. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 2410–2414. [Google Scholar] [CrossRef]

- Wang, D.; Xu, J.; Li, F.; Zhang, L.; Cao, C.; Stathis, D.; Lansner, A.; Hemani, A.; Zheng, L.R.; Zou, Z. A Memristor-Based Learning Engine for Synaptic Trace-Based Online Learning. IEEE Trans. Biomed. Circuits Syst. 2023, 17, 1153–1165. [Google Scholar] [CrossRef] [PubMed]

- Barraj, I.; Mestiri, H.; Masmoudi, M. Overview of Memristor-Based Design for Analog Applications. Micromachines 2024, 15, 505. [Google Scholar] [CrossRef]

- Hodgkin, A.L.; Huxley, A.F. A quantitative description of membrane current and its application to conduction and excitation in nerve. J. Physiol. 1952, 117, 500–544. [Google Scholar] [CrossRef]

- Gerstner, W.; Kistler, W.M.; Naud, R.; Paninski, L. Neuronal Dynamics: From Single Neurons to Networks and Models of Cognition; Cambridge University Press: Cambridge, UK, 2014. [Google Scholar] [CrossRef]

- Wang, J.; Mao, S.; Zhu, S.; Hou, W.; Yang, F.; Sun, B. Biomemristors-based synaptic devices for artificial intelligence applications. Org. Electron. 2022, 106, 106540. [Google Scholar] [CrossRef]

- Strukov, D.B.; Snider, G.S.; Stewart, D.R.; Williams, R.S. The missing memristor found. Nature 2008, 453, 80–83. [Google Scholar] [CrossRef]

- Joglekar, Y.N.; Wolf, S.J. The elusive memristor: Properties of basic electrical circuits. Eur. J. Phys. 2009, 30, 661. [Google Scholar] [CrossRef]

- Vourkas, I.; Sirakoulis, G.C. Memristor-Based Nanoelectronic Computing Circuits and Architectures; Springer International Publishing: Berlin/Heidelberg, Germany, 2016. [Google Scholar] [CrossRef]

- Hebb, D.O. The Organization of Behavior; Psychology Press: Philadelphia, PA, USA, 2002. [Google Scholar]

- Dayan, P.; Abbott, L.F. Theoretical Neuroscience; Computational neuroscience; MIT Press: London, UK, 2001. [Google Scholar]

- Caporale, N.; Dan, Y. Spike Timing–Dependent Plasticity: A Hebbian Learning Rule. Annu. Rev. Neurosci. 2008, 31, 25–46. [Google Scholar] [CrossRef]

- Rastogi, M.; Lu, S.; Islam, N.; Sengupta, A. On the Self-Repair Role of Astrocytes in STDP Enabled Unsupervised SNNs. Front. Neurosci. 2021, 14, 603796. [Google Scholar] [CrossRef]

- Zhang, J. Gradient Descent based Optimization Algorithms for Deep Learning Models Training. arXiv 2019. [Google Scholar] [CrossRef]

- Tholeti, T.; Kalyani, S. Concavifiability and convergence: Necessary and sufficient conditions for gradient descent analysis. arXiv 2019. [Google Scholar] [CrossRef]

- Lobo, J.L.; Del Ser, J.; Bifet, A.; Kasabov, N. Spiking Neural Networks and online learning: An overview and perspectives. Neural Netw. 2020, 121, 88–100. [Google Scholar] [CrossRef] [PubMed]

- Rozenberg, M.J.; Schneegans, O.; Stoliar, P. An ultra-compact leaky-integrate-and-fire model for building spiking neural networks. Sci. Rep. 2019, 9, 11123. [Google Scholar] [CrossRef] [PubMed]

- Wu, X.; Saxena, V.; Zhu, K.; Balagopal, S. A CMOS Spiking Neuron for Brain-Inspired Neural Networks With Resistive Synapses and In Situ Learning. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 1088–1092. [Google Scholar] [CrossRef]

- Analog Devices. 500 MHz Ultra-Low Bias Current FET Input Op Amp; Analog Devices Inc.: Norwood, MA, USA, 2017. [Google Scholar]

- Analog Devices. High Speed, Low Cost, Op Amp; Analog Devices Inc.: Norwood, MA, USA, 2006. [Google Scholar]

- Banerjee, W.; Nikam, R.D.; Hwang, H. Prospect and challenges of analog switching for neuromorphic hardware. Appl. Phys. Lett. 2022, 120, 060501. [Google Scholar] [CrossRef]

- Analog Devices. CMOS, ±5 V/+5 V, 4 Ω, Single SPDT Switches; Analog Devices Inc.: Norwood, MA, USA, 2011. [Google Scholar]

- Analog Devices. CMOS, 2.5 Ω Low Voltage, Triple/Quad SPDT Switches; Analog Devices Inc.: Norwood, MA, USA, 2001. [Google Scholar]

- Analog Devices. 2.5 Ω, 1.8 V to 5.5 V, ±2.5 V Triple/Quad SPDT Switches in Chip Scale Packages; Analog Devices Inc.: Norwood, MA, USA, 2015. [Google Scholar]

- Knowm. Memristors to Machine Intelligence. Available online: https://knowm.org/ (accessed on 10 February 2024).

- Maida, A. Chapter 2—Cognitive Computing and Neural Networks: Reverse Engineering the Brain. In Cognitive Computing: Theory and Applications; Gudivada, V.N., Raghavan, V.V., Govindaraju, V., Rao, C., Eds.; Handbook of Statistics; Elsevier: Amsterdam, The Netherlands, 2016; Volume 35, pp. 39–78. [Google Scholar] [CrossRef]

- Butts, D.A.; Goldman, M.S. Tuning Curves, Neuronal Variability, and Sensory Coding. PLoS Biol. 2006, 4, e92. [Google Scholar] [CrossRef] [PubMed]

- Keysight. InfiniiVision X-Series Oscilloscope LabVIEW Instrument Drivers. Available online: https://www.keysight.com (accessed on 10 February 2024).

- Stoliar, P.; Yamada, H.; Toyosaki, Y.; Sawa, A. Spike-shape dependence of the spike-timing dependent synaptic plasticity in ferroelectric-tunnel-junction synapses. Sci. Rep. 2019, 9, 17740. [Google Scholar] [CrossRef] [PubMed]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ramirez-Morales, R.R.; Ponce-Ponce, V.H.; Molina-Lozano, H.; Sossa-Azuela, H.; Islas-García, O.; Rubio-Espino, E. Analog Implementation of a Spiking Neuron with Memristive Synapses for Deep Learning Processing. Mathematics 2024, 12, 2025. https://doi.org/10.3390/math12132025

Ramirez-Morales RR, Ponce-Ponce VH, Molina-Lozano H, Sossa-Azuela H, Islas-García O, Rubio-Espino E. Analog Implementation of a Spiking Neuron with Memristive Synapses for Deep Learning Processing. Mathematics. 2024; 12(13):2025. https://doi.org/10.3390/math12132025

Chicago/Turabian StyleRamirez-Morales, Royce R., Victor H. Ponce-Ponce, Herón Molina-Lozano, Humberto Sossa-Azuela, Oscar Islas-García, and Elsa Rubio-Espino. 2024. "Analog Implementation of a Spiking Neuron with Memristive Synapses for Deep Learning Processing" Mathematics 12, no. 13: 2025. https://doi.org/10.3390/math12132025

APA StyleRamirez-Morales, R. R., Ponce-Ponce, V. H., Molina-Lozano, H., Sossa-Azuela, H., Islas-García, O., & Rubio-Espino, E. (2024). Analog Implementation of a Spiking Neuron with Memristive Synapses for Deep Learning Processing. Mathematics, 12(13), 2025. https://doi.org/10.3390/math12132025