Over the past decades, the CMOS technology downscaling trend, which involves—among other factors—the shrinking of transistor dimensions, the reduction of supply voltages, and the increase in operating frequencies, has rendered modern Integrated Circuits (ICs) substantially susceptible to radiation-induced Single Event Transients (SETs) [

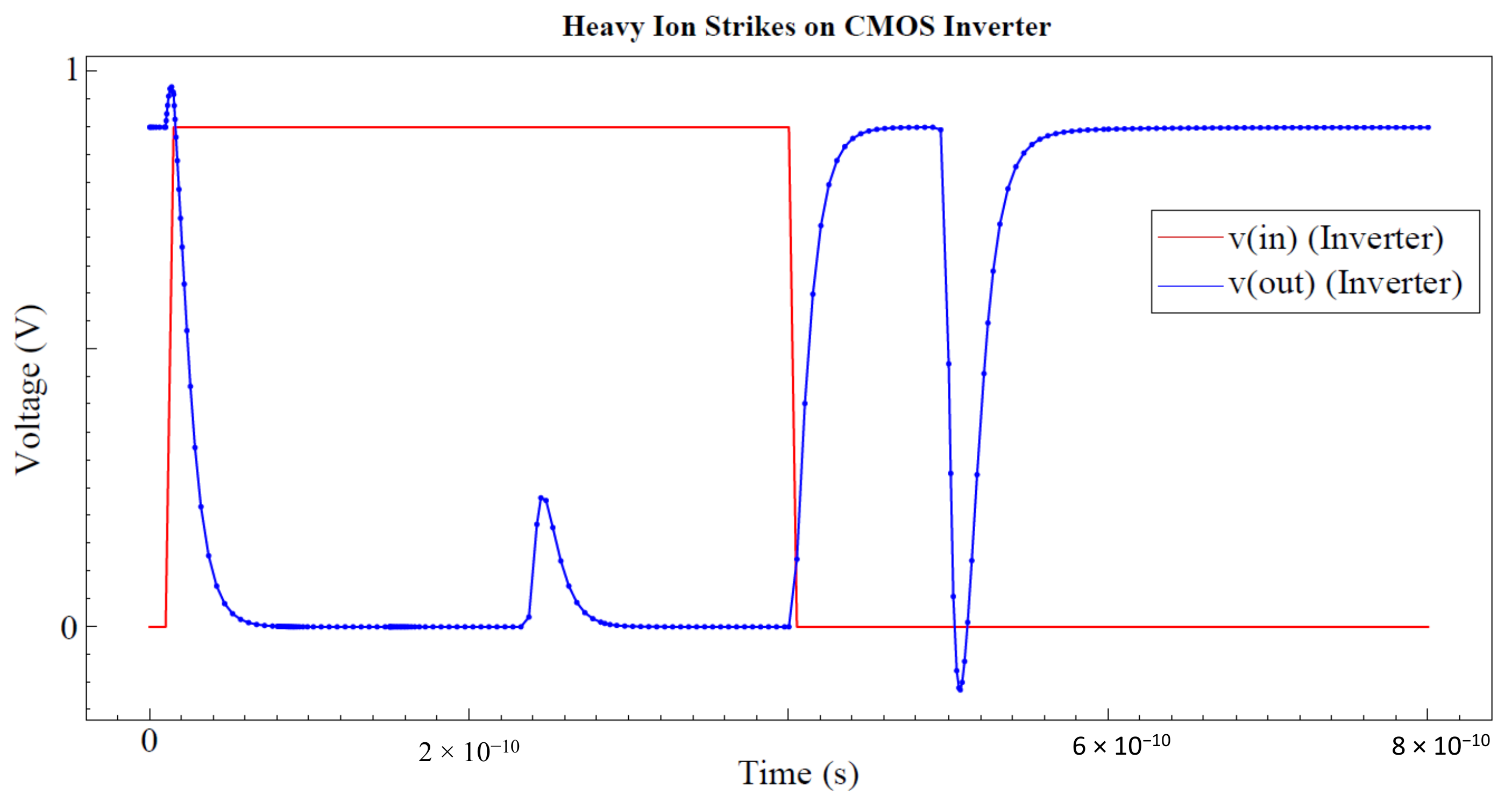

1]. Thus, ICs’ reliability regarding Soft Errors constitutes a challenging field of research, especially when it concerns critical systems. A radiation particle of sufficient energy that strikes on a gate may generate, under certain circumstances, a glitch at the output. At the circuit level, a soft error emerges when a SET is captured by at least one storage element. While the soft errors are not permanent, they could potentially pose a severe threat to vulnerable modern chips, especially critical ones. A factor that aggravates this problem is the emergence of Single Event Multiple Transients (SEMTs) that, primarily due to the increase in the circuit device density, as a consequence of the Moore’s law, have become more prevalent recently [

2]. In light of the above, the accurate evaluation of the Soft Error Rate (SER) constitutes a vital process to determine the ICs susceptibility to radiation hazards. Usually, the SER is measured in terms of FIT (Failures In Time), which is a widely-used reliable metric across different SER estimation tools for the assessment of chips’ reliability.

To accurately estimate the SER of a design, it is indispensable to model sufficiently and accurately the three mechanisms that are able to impede an SET from propagating through a circuit and, eventually, being latched by the flip-flops (FFs), thus producing a soft error. These effects are logical, electrical, and timing-masking [

3]. The logical masking occurs when an SET is masked on a subsequent gate because one of the other inputs is in a controlling value. For example, the controlling value of an AND gate is logic 0, whereas logic 1 is the controlling value of an OR gate. The electrical masking is associated with the electrical properties of the gates and the SET pulse characteristics and occurs as the SET pulse attenuates during the propagation through the logic gates, becoming too small to be reliably latched at the FFs. Finally, the timing-masking occurs when an SET arrives outside the latching window of the FF as this is determined by setup and hold times.

The modeling of the three masking mechanisms is equally significant in obtaining an accurate estimation of a circuit’s vulnerability to radiation hazards. The logical masking is quite straightforward to model, and there are no major differences among the various SER estimation works, with the more prevalent model being the utilization of a simple logic level simulator. However, the electrical and timing-maskings can be modeled in many different ways, which determine the overall accuracy of the SER estimation. Plenty of work that attempts to model accurately the electrical masking mechanism has been proposed so far. Generally, there are two types of approaches that dominate the bibliography. The first is based on SPICE simulations to accurately characterize the propagated SET pulses and form LookUp Tables (LUTs), whereas the other attempts to estimate the effect of electrical masking through analytical modeling. The advantage of the former is its accuracy, even though it is expensive in terms of time, whereas the latter is more efficient but lacks accuracy. A closed-form approximation of the logic level waveforms, induced by α-particles on inverters considering the transistor’s pull-up and pull-down network, the particle charge, and the capacitive loads, is presented in [

4]. In [

5], a closed-form expression is introduced to calculate the output voltage (amplitude) of a propagated transient fault. However, in [

6] a simple ramp approximation equation is used to estimate the SET pulse width at the gate output. An approach that utilizes discrete values of the input waveform to approximate the whole output pulse (amplitude and duration) is presented in [

7]. In [

8], a pre-characterization library process, based on the SET pulse height and width at the gate input, is carrried out to extract parameters and form simple analytical continuous functions for pulse propagation. In [

9], a two-phase pre-characterization process is performed with SPICE, forming LUTs utilized in the extraction of SET propagation mathematical equations. In [

10,

11], SPICE simulations are performed to characterize the SET width. Other approaches use transistor models to effectively model the electrical masking effect [

12,

13]. Recent works have revealed another significant aspect of SET propagation that affects its pulse width. In particular, the investigation of the SETs production and propagation in CMOS logic circuits, in [

14], has shown that they may propagate without attenuation when they are generated from particle strikes of certain linear energy transfer. In [

15], the authors present the Propagation-Induced Pulse-Broadening (PIPB) effect that a SET is subjected to as it propagates through long inverter chains. A direct relationship is reported between the SET pulse attenuation or broadening with the circuit design parameters and the gate delay [

16,

17]. The TCAD simulations of inverter chains in [

18] relate the PIPB effect to the transistor voltage threshold. The impact of the propagation paths (including reconvergent paths), the input patterns, and the polarity of the SET on the PIPB effect is presented in [

19]. The authors in [

20] characterize the PIPB effect on SETs generated from a heavy ion microbeam and associate the transistor size with its confinement. All these works indicate that this aspect should be taken into account to achieve an accurate SER evaluation. A similar phenomenon of SET pulse broadening after narrowing (PBAN) due to the charge sharing is examined in [

21]. As regards the timing-masking modeling, there is a lack of information in the bibliography upon the impact of each timing analysis approach on the SER estimation. A modified static timing analysis for the timing-masking modeling is proposed in [

22], but the utilized delay model is not clarified, and the interconnection delay is ignored, which may underestimate or overestimate the results.

The rest of this work is organized as follows.

Section 2 presents a TCAD simulation-based approach to achieve an accurate characterization of the radiation-induced SET pulses.

Section 3 elaborates on the analysis and modeling of electrical masking and discusses the relationship of this model with the timing analysis approach selected for the SER estimation.

Section 4 briefly highlights the main steps of the integrated SER evaluation flow that the aforementioned masking models are incorporated into.

Section 5 verifies the electrical and timing-masking models and presents a series of experimental results on a variety of benchmarks regarding the impact of these models on SER estimation. Finally,

Section 6 concludes this work.