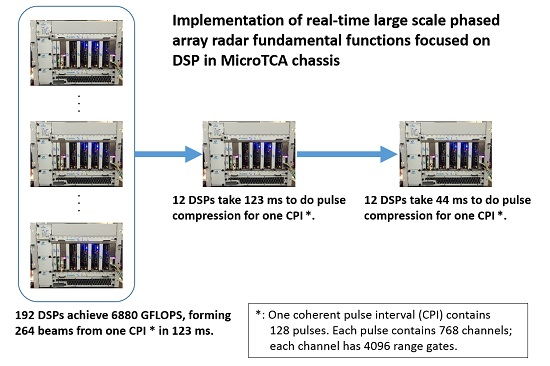

An Implementation of Real-Time Phased Array Radar Fundamental Functions on a DSP-Focused, High-Performance, Embedded Computing Platform

Abstract

:1. Introduction

1.1. Real-Time, Large-Scale, Phased Array Radar Systems

1.2. High-Performance Embedded Computing Platforms

1.3. Comparison of Different Multiprocessor Clusters

1.4. Paper Structure

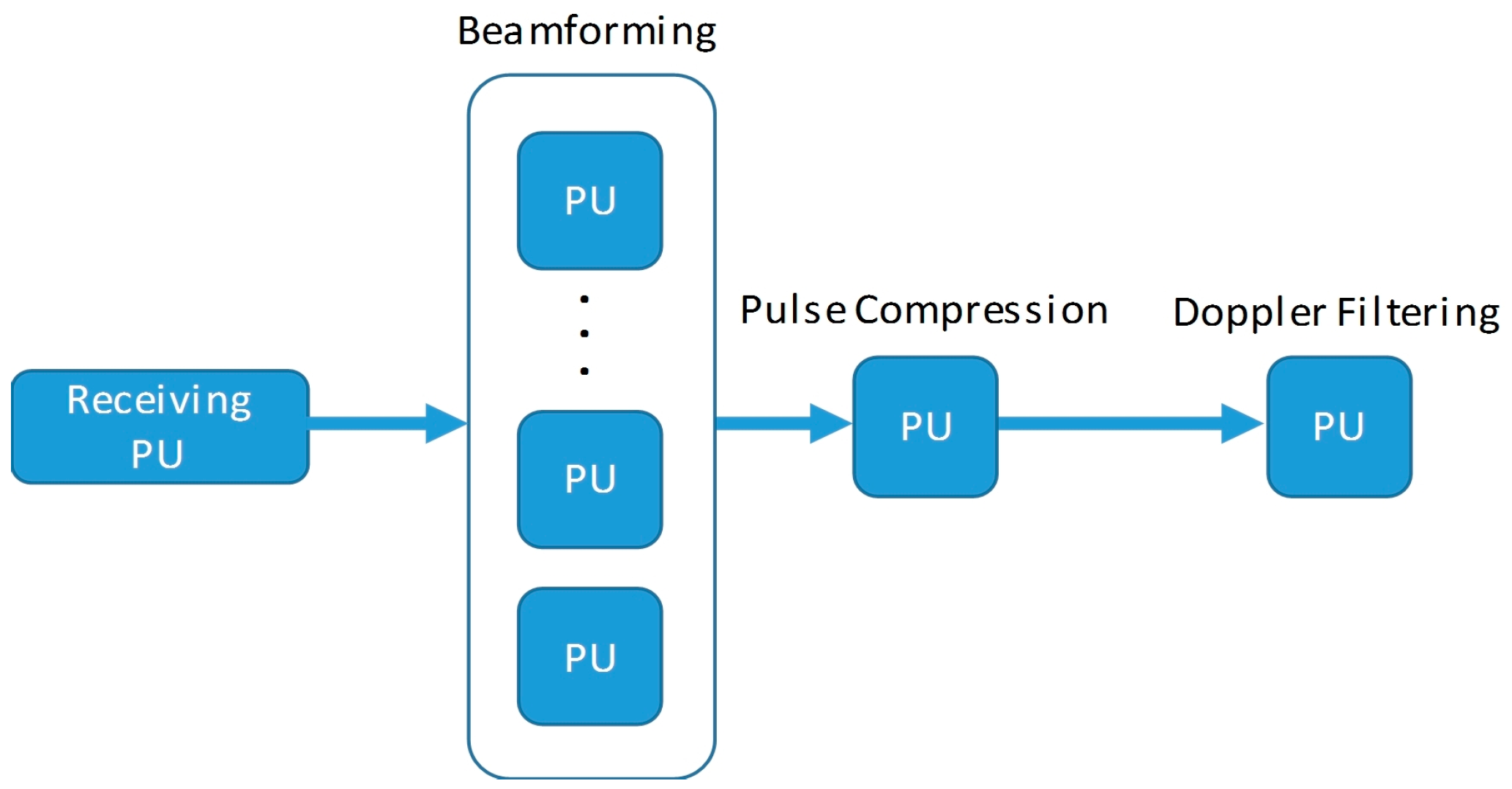

2. Backend System Architecture

2.1. Overview

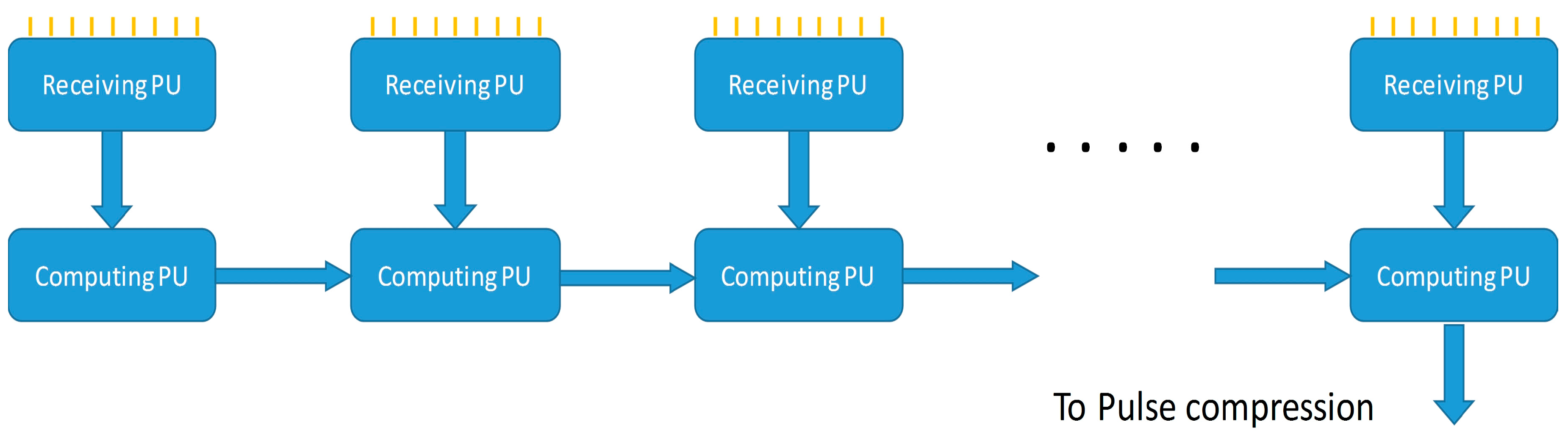

2.2. Scalable Backend System Architecture

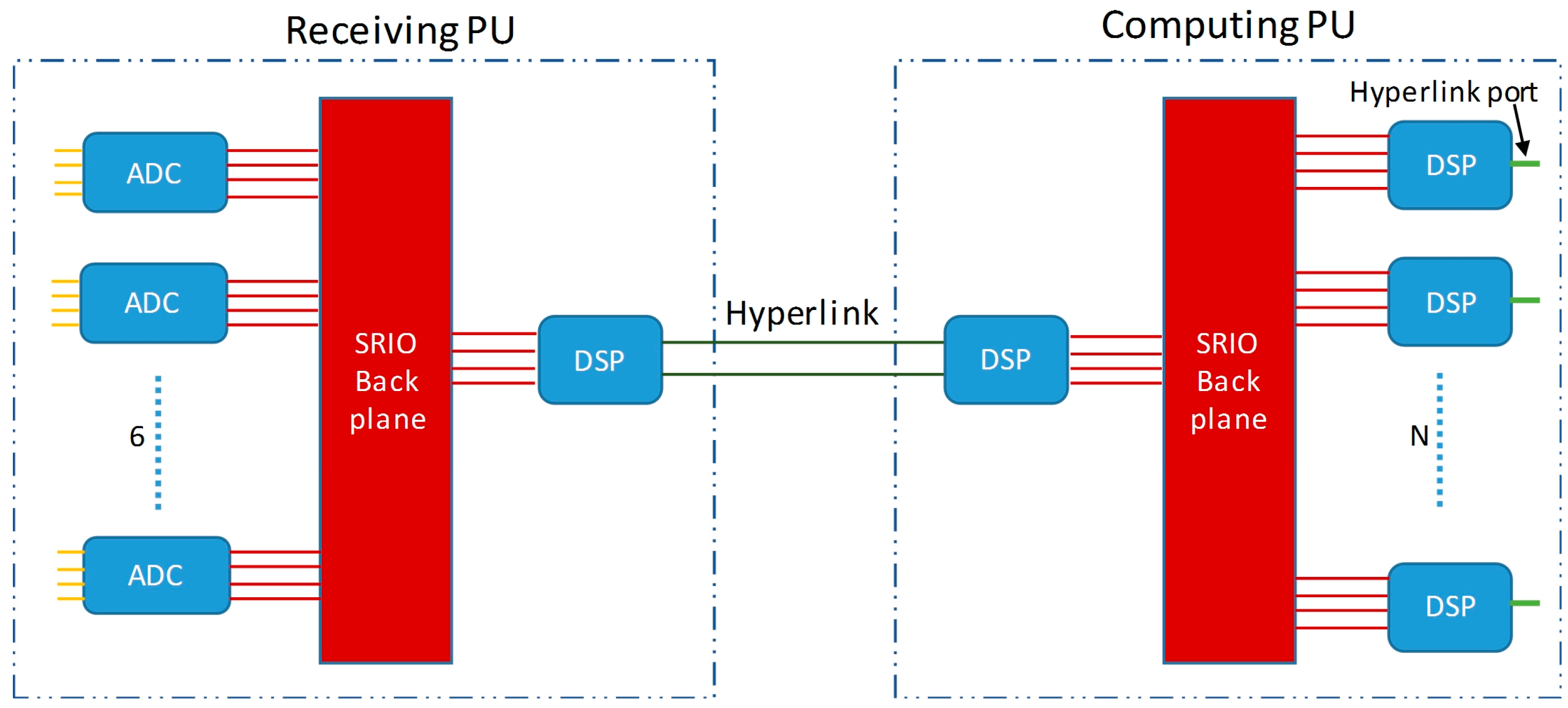

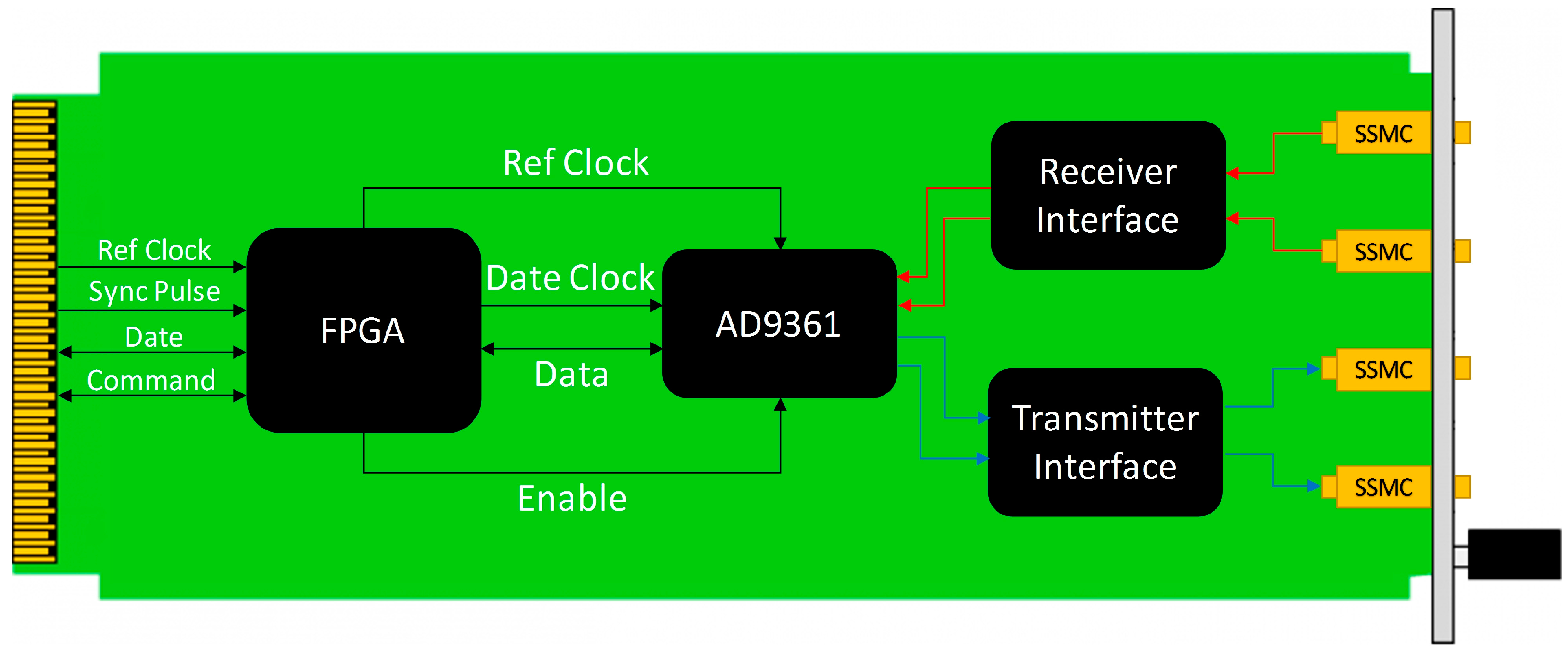

2.3. Processing Unit Architecture

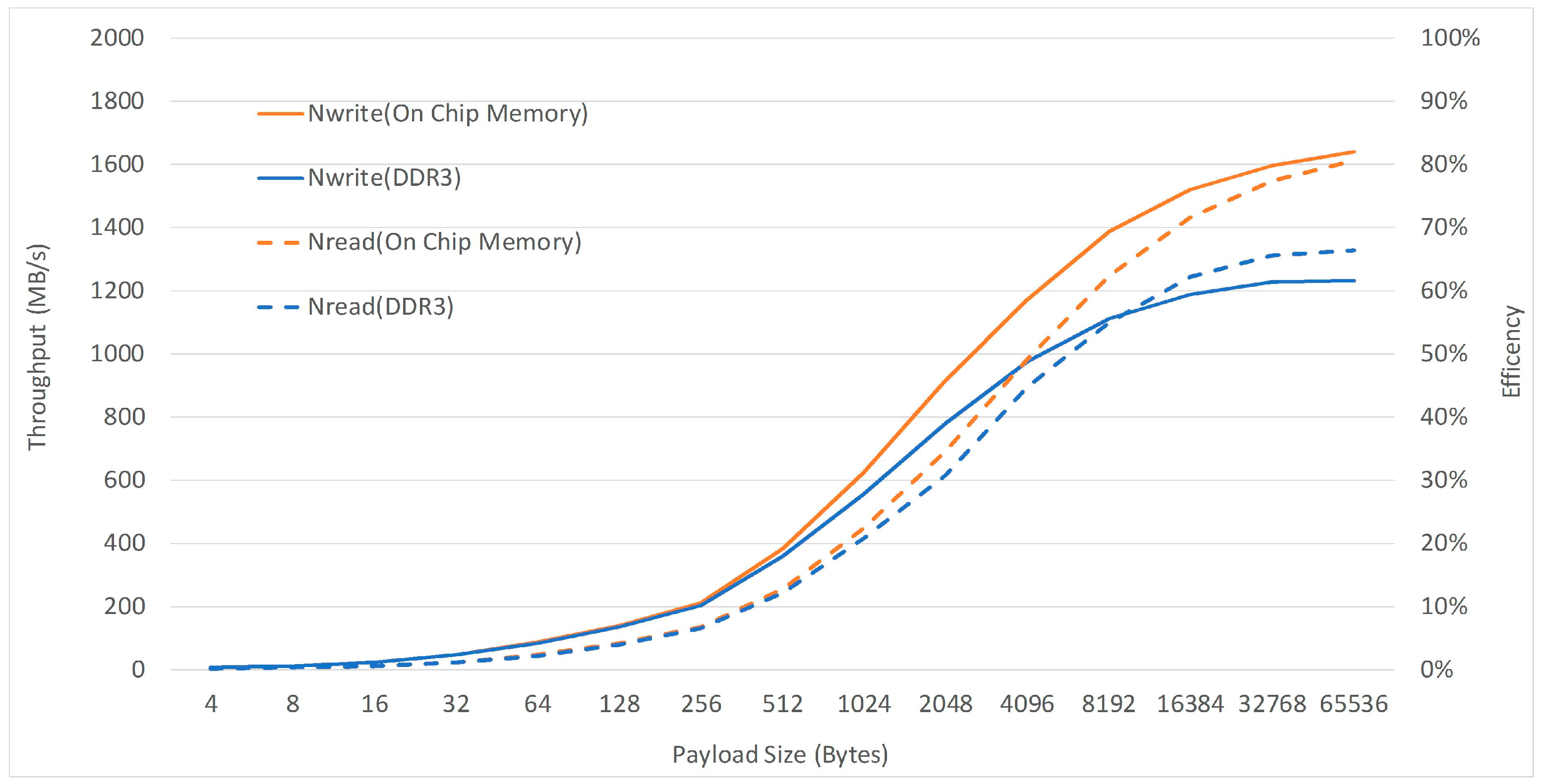

2.4. Selecting a Backplane Data Transmission Protocol

2.5. System Calibration and Multichannel Synchronization

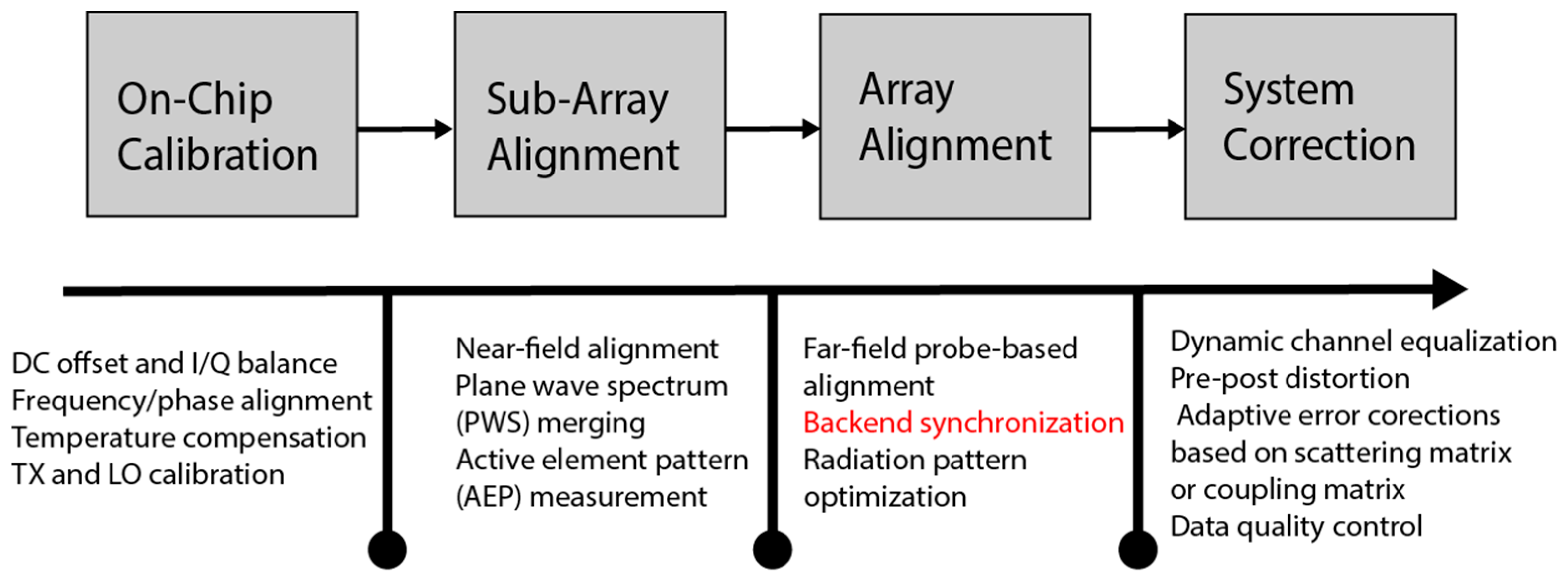

2.5.1. General Calibration Procedures

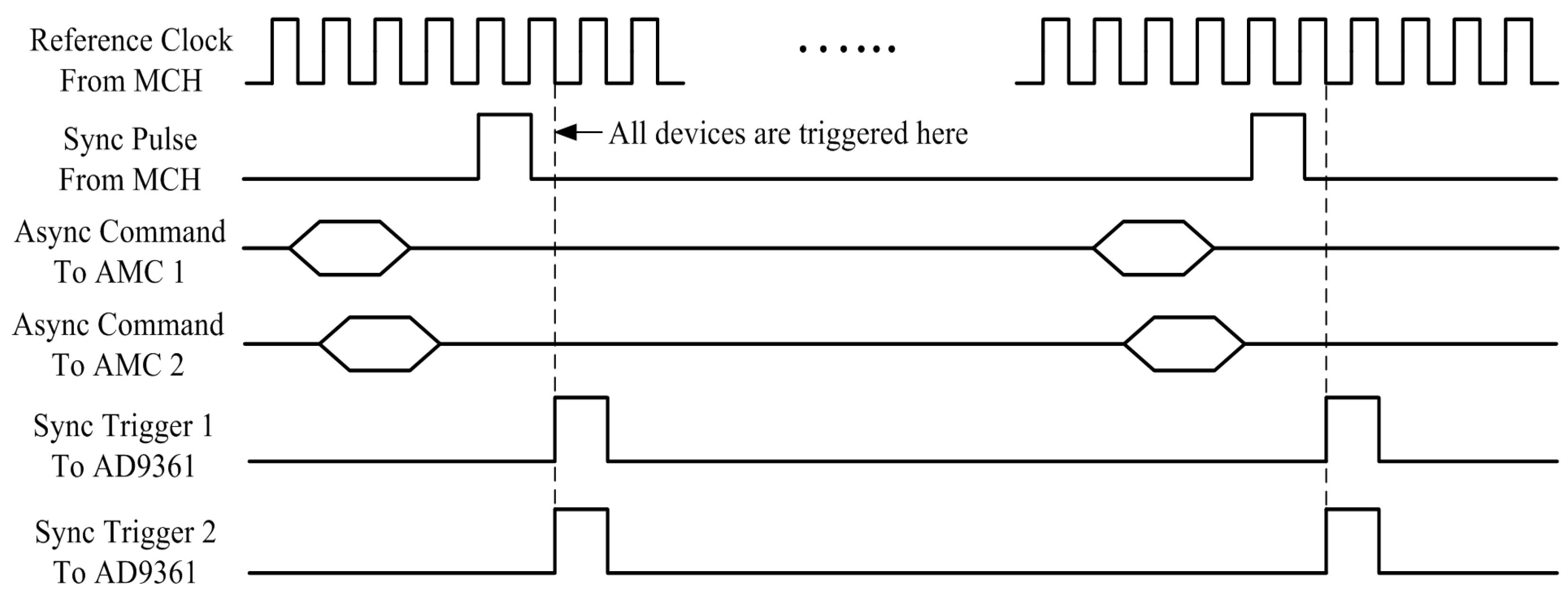

2.5.2. Backend Synchronization

2.6. Backend System Performance Metrics

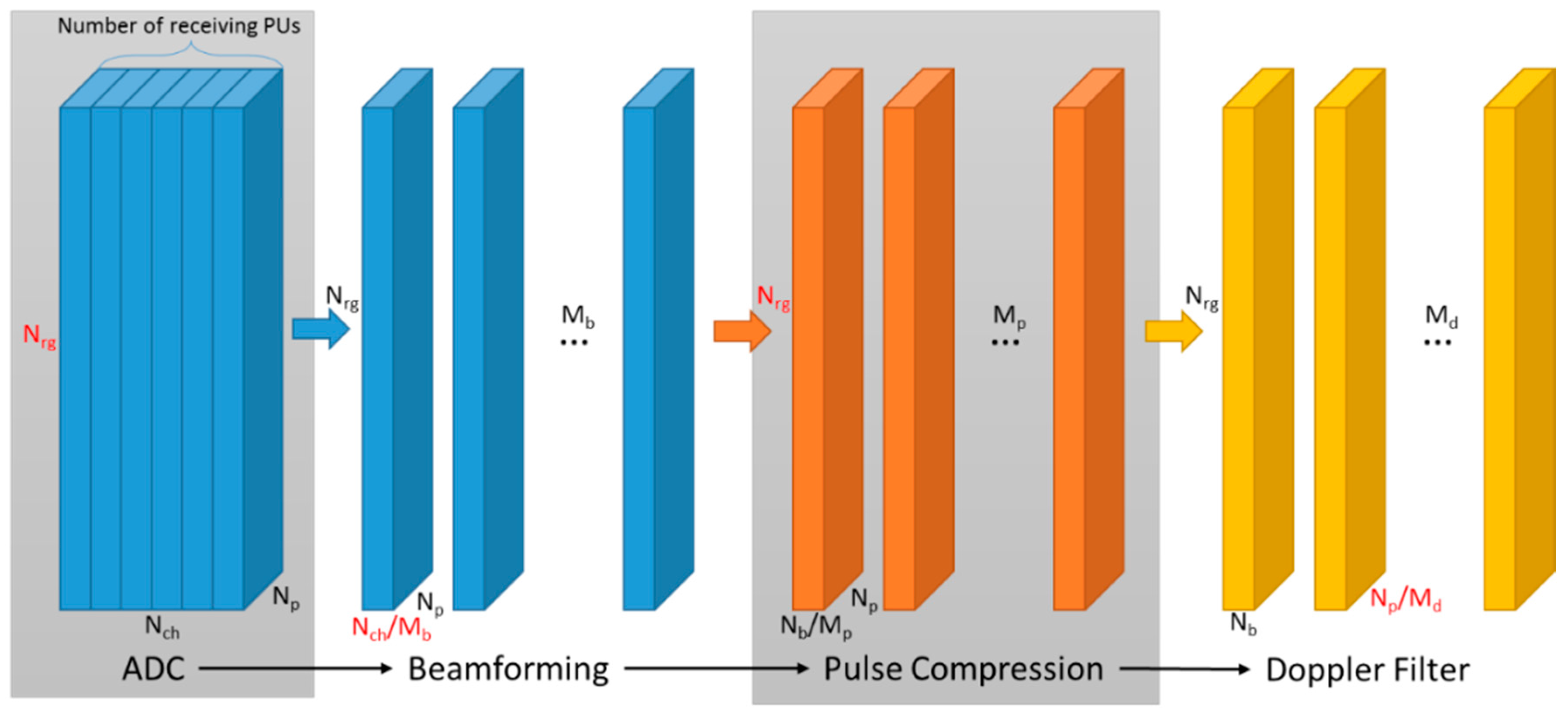

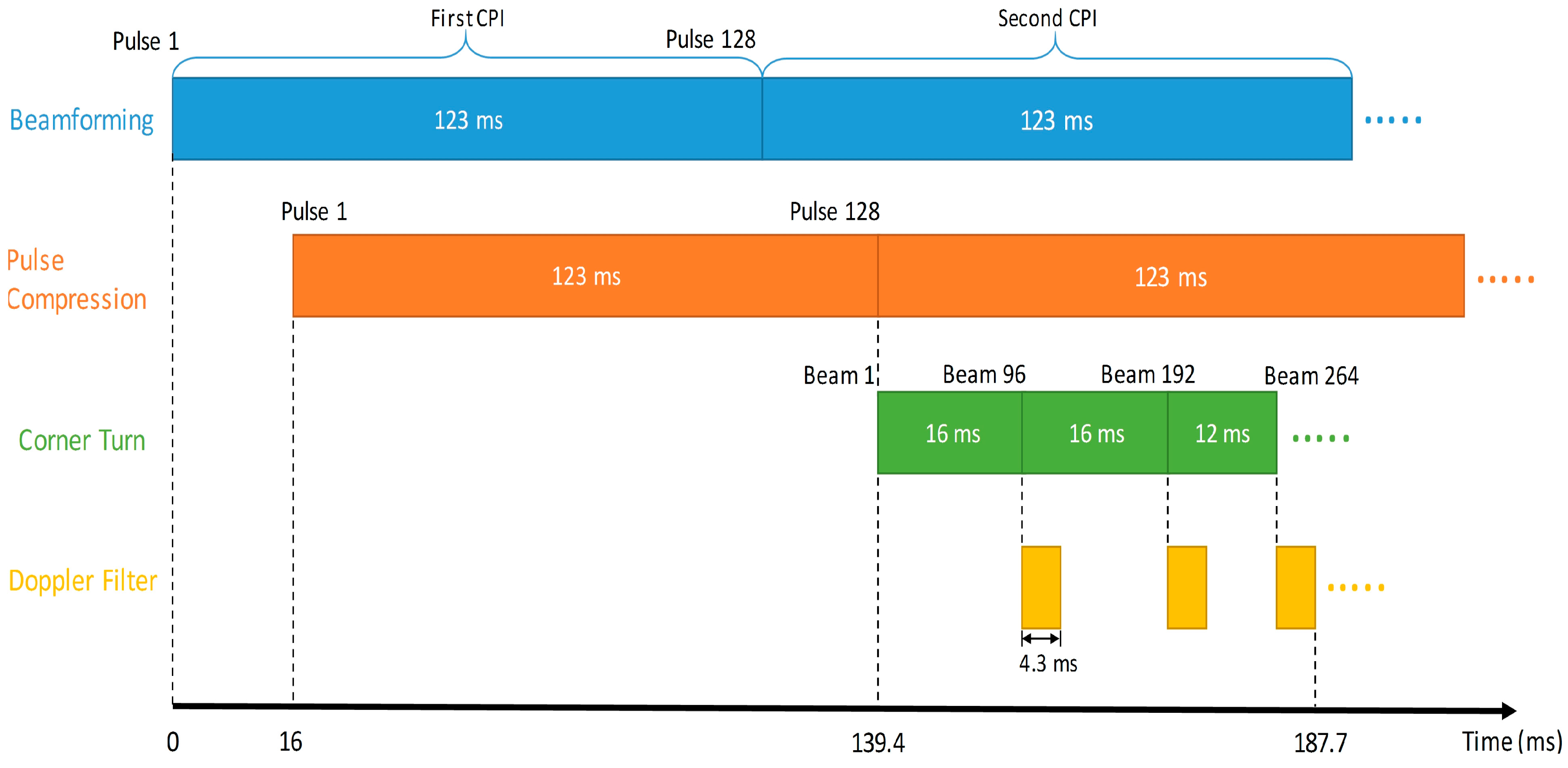

3. Real-Time Implementation of a Digital Array Radar Processing Chain

3.1. Beamforming Implementation

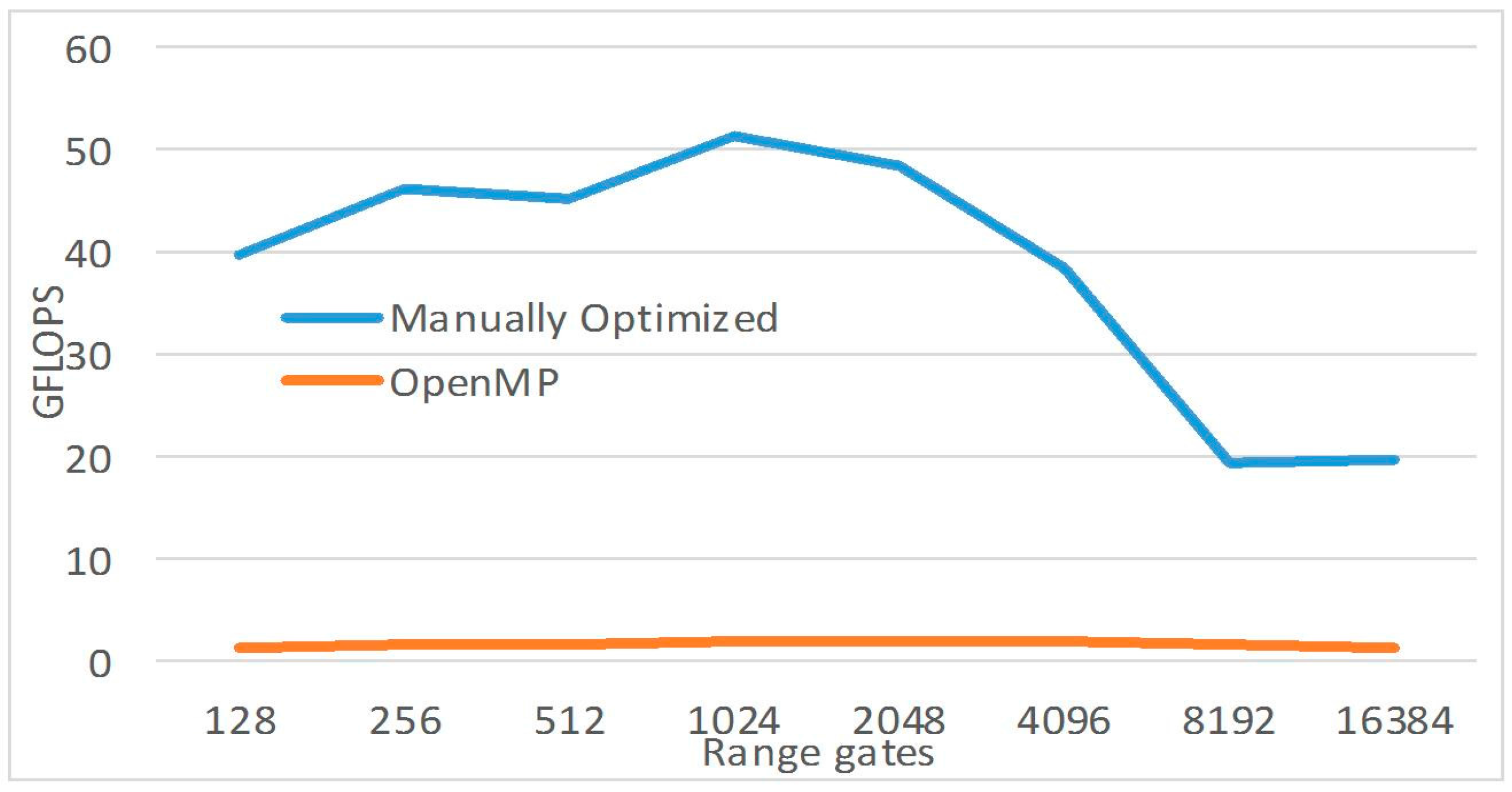

3.2. Pulse Compression Implementation

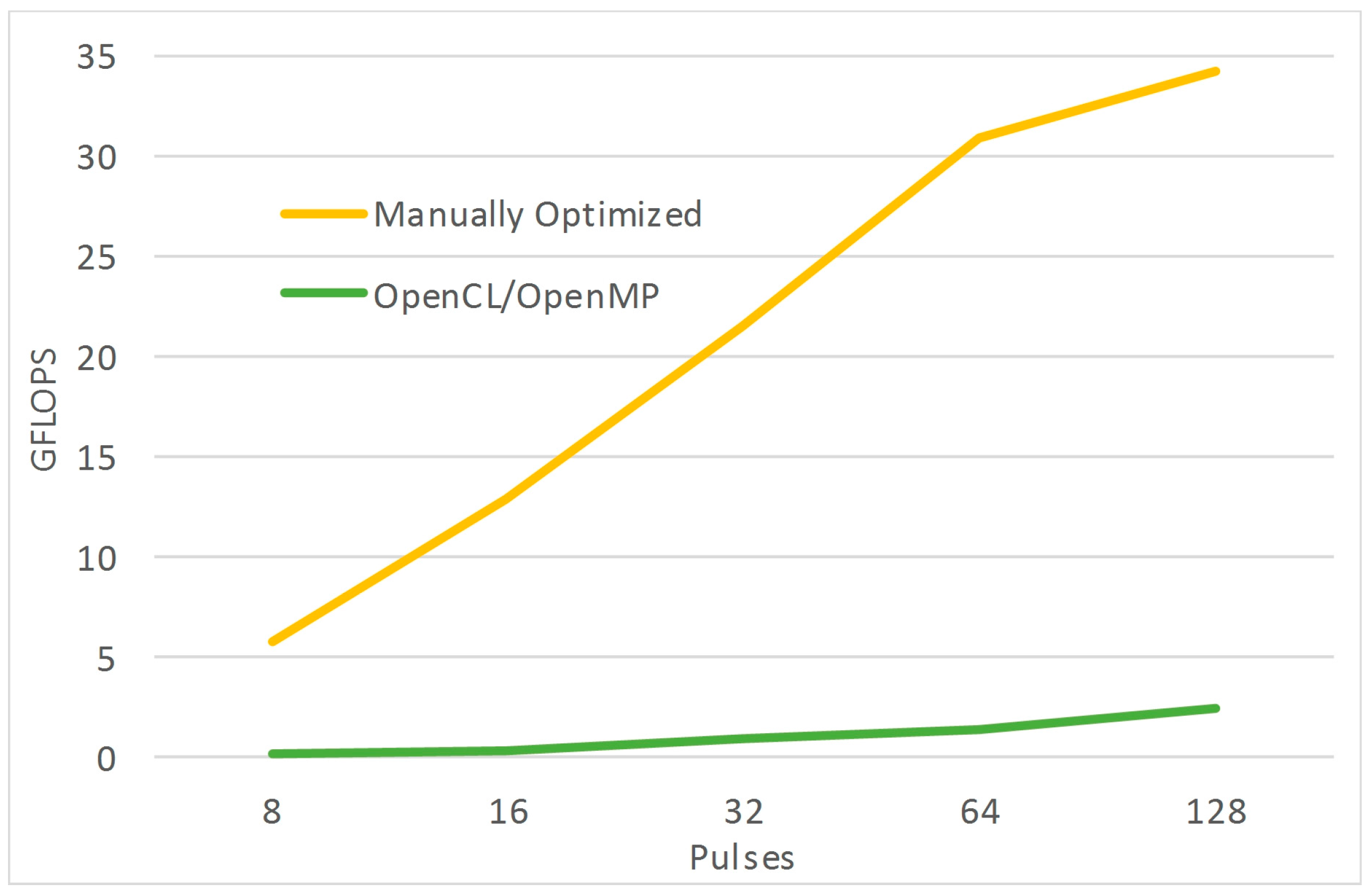

3.3. Doppler Processing and Corner Turn

4. Performance Analysis of Complete Signal Processing Chain

5. Parallel Implementation Using Open Computing Language (OpenCL)/Open Multi-Processing (OpenMP)

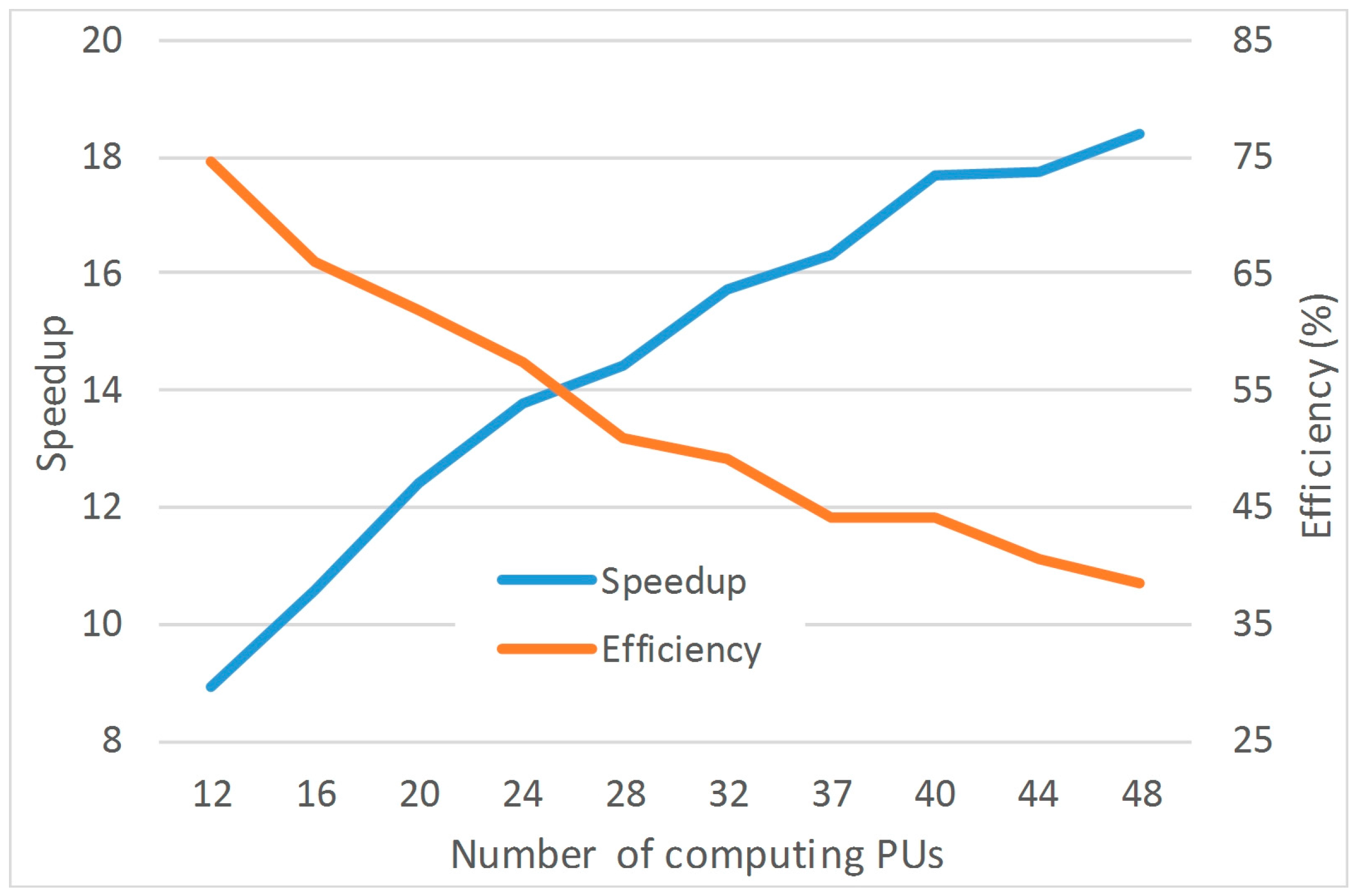

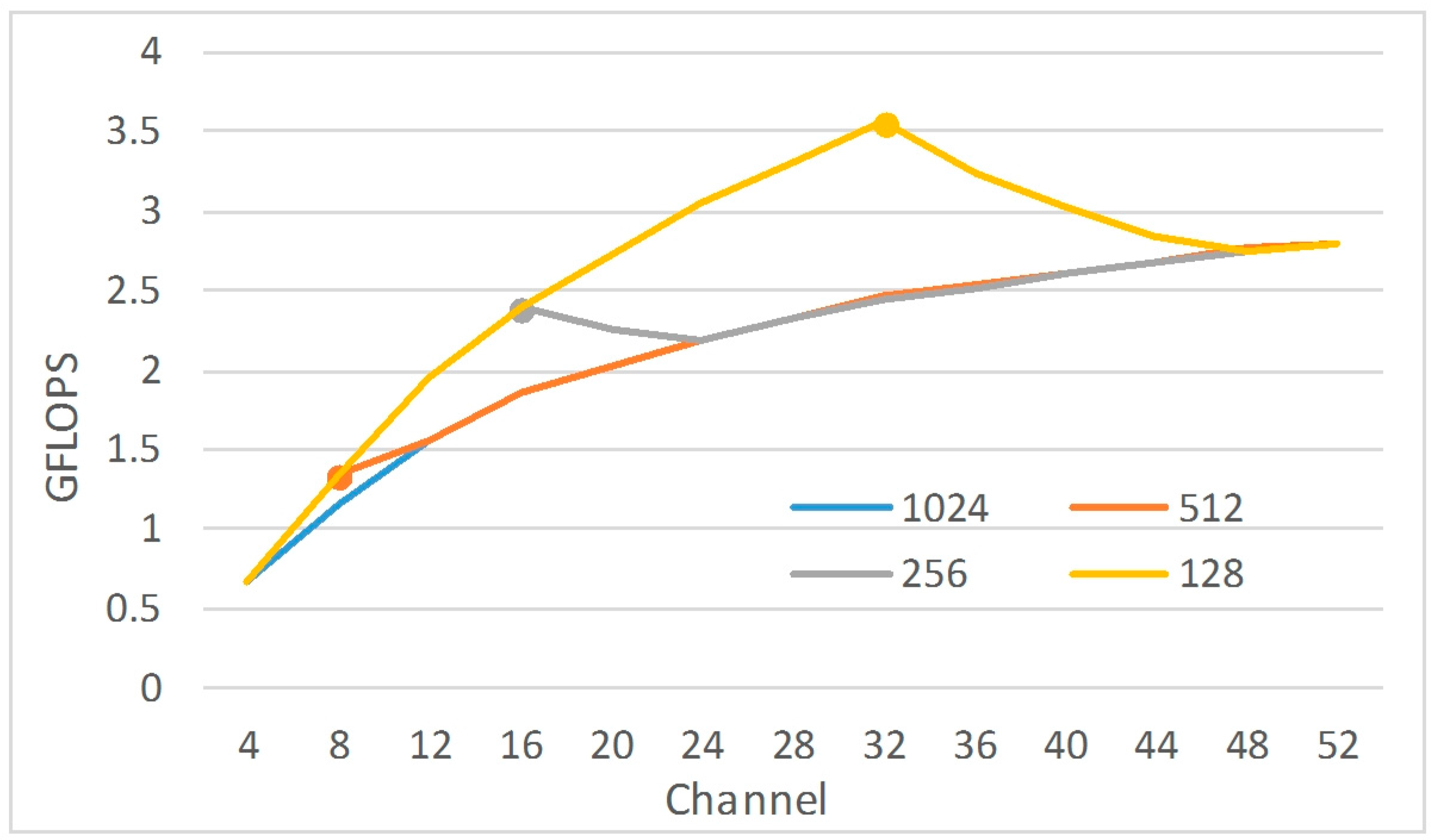

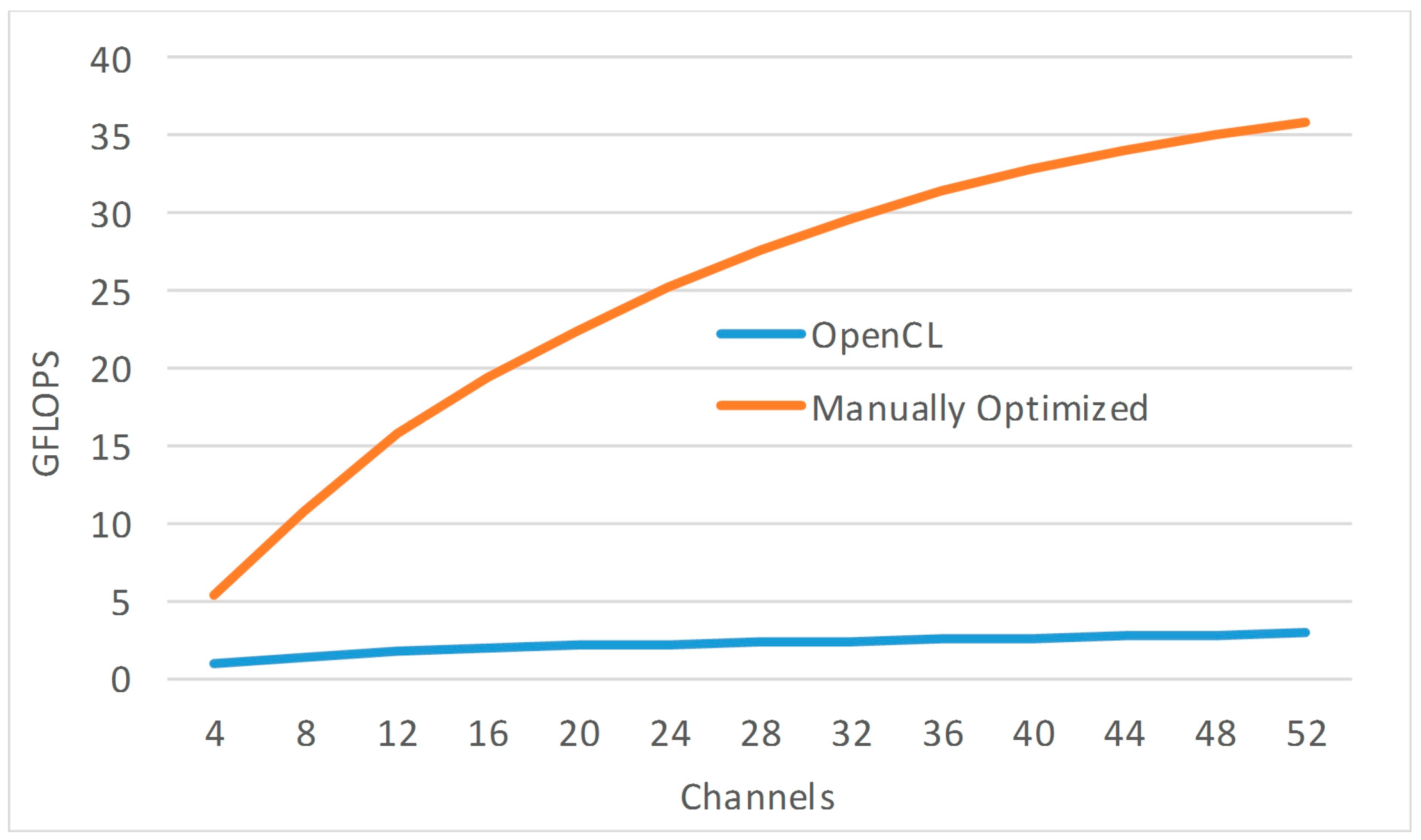

5.1. Beamforming Implementation with OpenCL/OpenMP

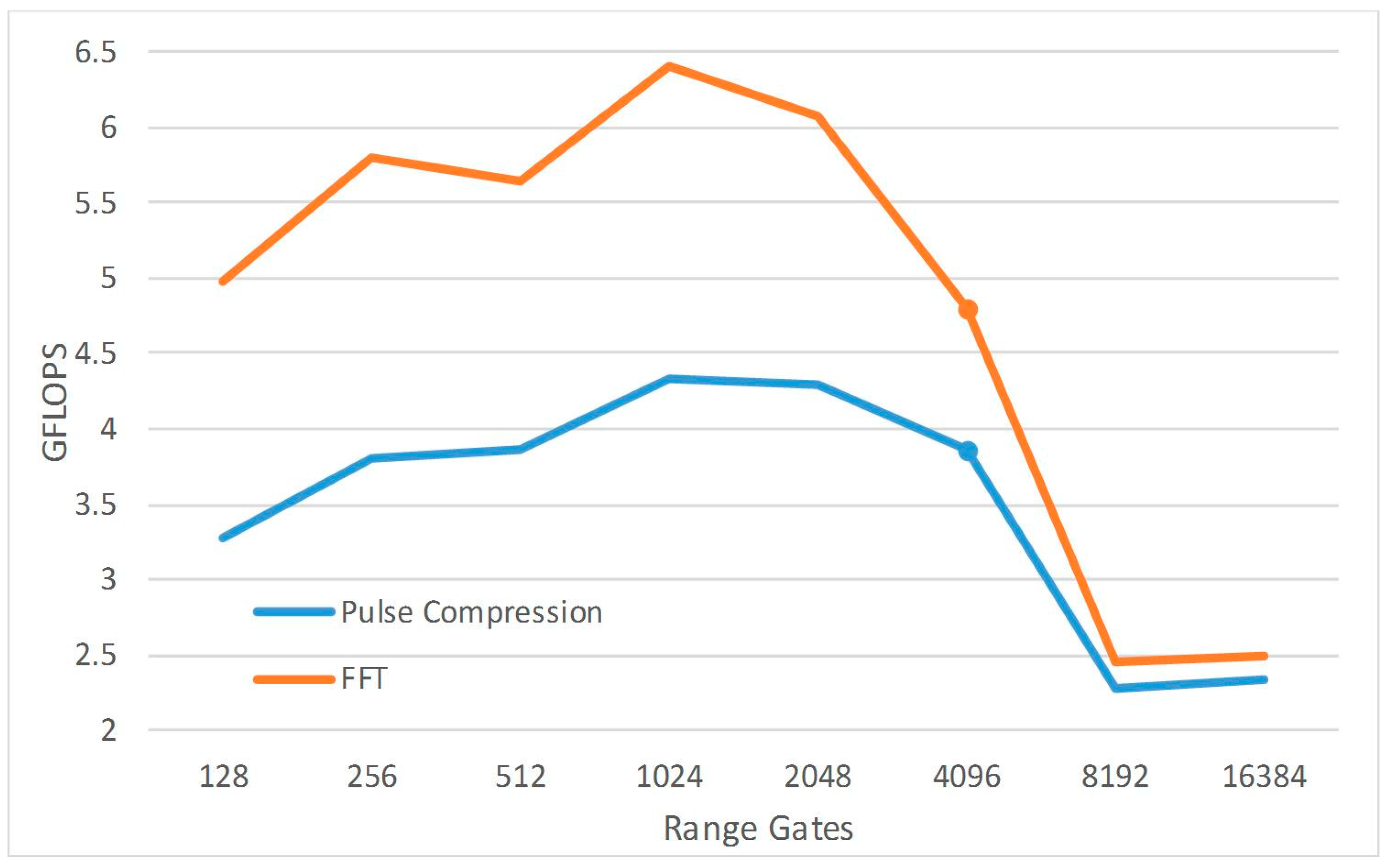

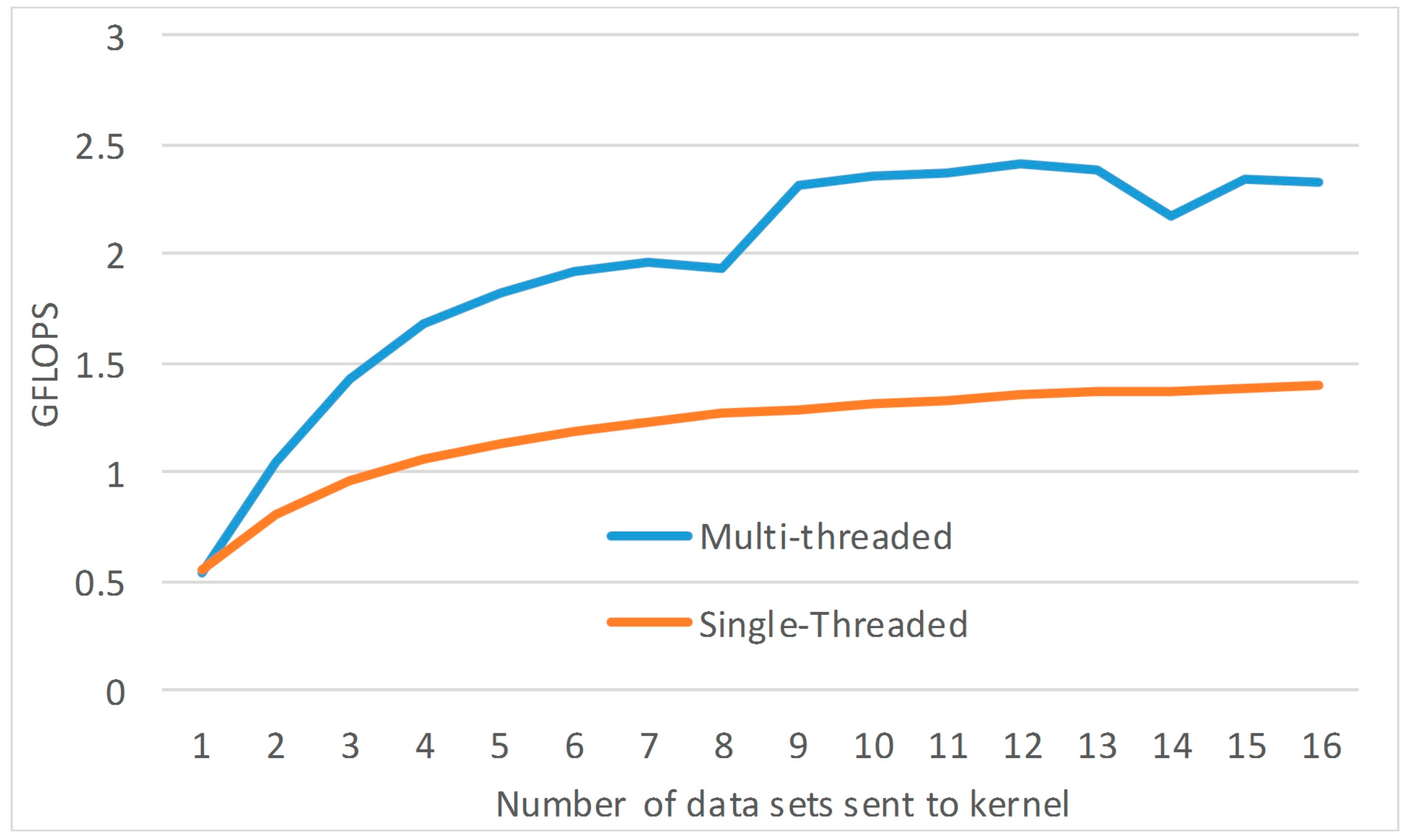

5.2. Pulse Compression Implementation with OpenCL/OpenMP

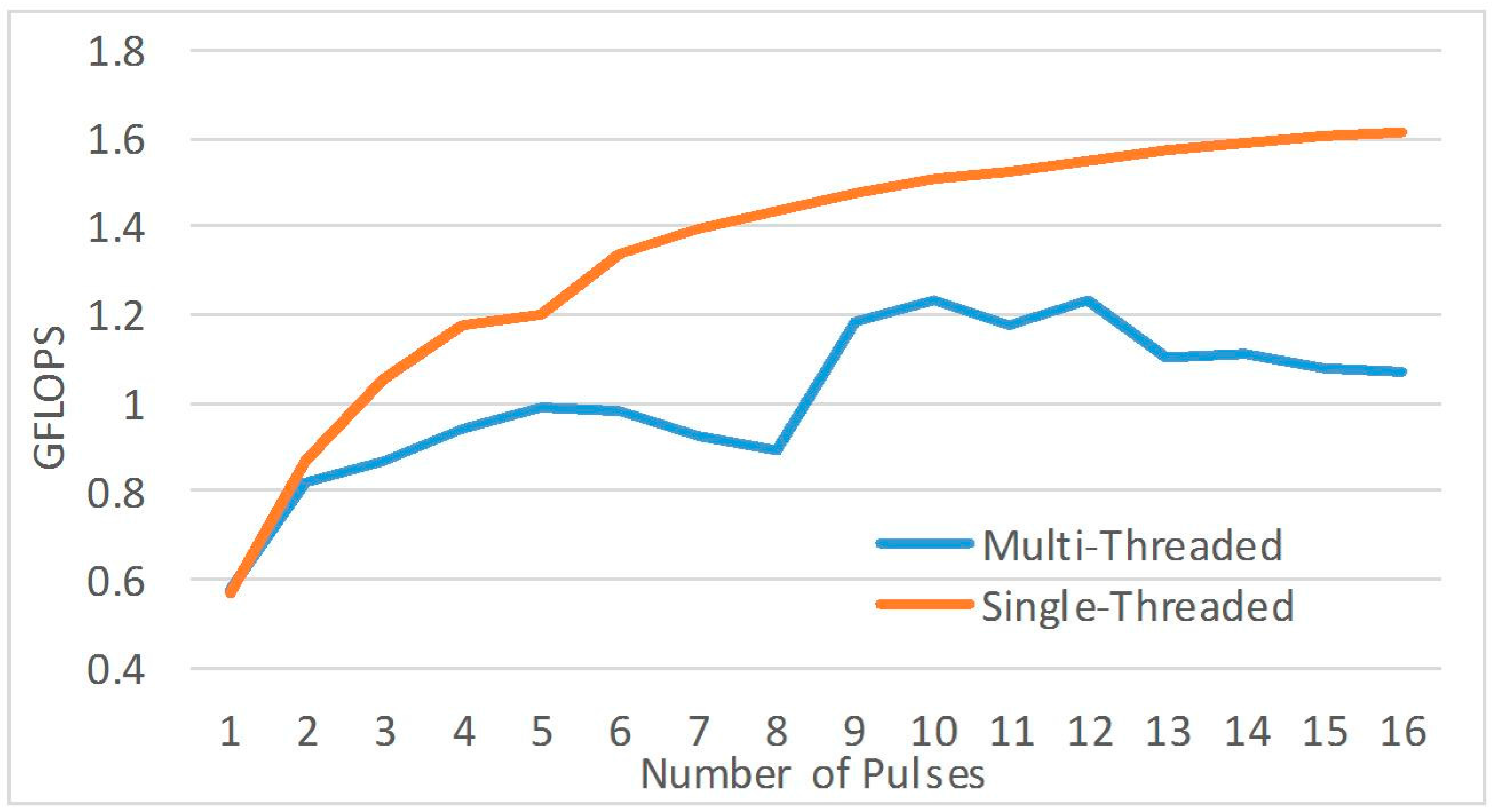

5.3. Doppler Processing Implementation with OpenCL/OpenMP

6. Summary

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Yu, X.; Zhang, Y.; Patel, A.; Zahrai, A.; Weber, M. An Implementation of Real-Time Phased Array Radar Fundamental Functions on DSP-Focused, High Performance Embedded Computing Platform. In Proc. SPIE 9829, Proceedings of Radar Sensor Technology XX, Baltimore, MD, USA, 17 April 2016; pp. 982913–982918.

- Hendrix, R. Aerospace System Improvements Enabled by Modern Phased Array Radar. In Proceedings of the 2008 IEEE Radar Conference, Rome, Italy, 26–30 May 2008; pp. 1–6.

- Tuzlukov, V. Signal Processing in Radar Systems; CRC Press: Boca Raton, FL, USA, 2013. [Google Scholar]

- Weber, M.E.; Cho, J.; Flavin, J.; Herd, J.; Vai, M. Muti-Function Phased Array Radar for U.S. Civil-Sector Surveillance Needs. In Proceedings of 32nd Conference on Radar Meteorology, Albuquerque, NM, USA, 22–29 October 2005.

- Martinez, D.; Moeller, T.; Teitelbaum, K. Application of reconfigurable computing to a high performance front-end radar signal processor. J. VLSI Signal Process. Syst. Signal Image Video Technol. 2001, 28, 63–83. [Google Scholar] [CrossRef]

- Martinez, D.R.; Bond, R.A.; Vai, M.M. High Performance Embedded Computing Handbook: A Systems Perspective; CRC Press: Boca Raton, FL, USA, 2008. [Google Scholar]

- Stone, L.D.; Streit, R.L.; Corwin, T.L.; Bell, K.L. Bayesian Multiple Target Tracking, 2nd ed.; Artech House: Norwood, MA, USA, 2013. [Google Scholar]

- Atoche, A.C.; Castillo, J.V. Dual super-systolic core for real-time reconstructive algorithms of high-resolution radar/sar imaging systems. Sensors 2012, 12, 2539–2560. [Google Scholar] [CrossRef] [PubMed]

- PICMG. AdvancedTCA® Base Specification; PCIMG: Wakefield, MA, USA, 2008. [Google Scholar]

- PCIMG. Micro Telecommunications Computing Architecture Short Form Specification; PCIMG: Wakefield, MA, USA, 2006. [Google Scholar]

- Entwistle, P.; Lawrie, D.; Thompson, H.; Jones, D.I. A Eurocard computer using transputers for control systems applications. In Proceedings of the IEE Colloquium on Eurocard Computers—A Solution to Low Cost Control? London, UK, 29 September 1989; pp. 611–613.

- Vollrath, D.; Körte, H.; Manus, T. Now is the time to change your VME and CPCI computing platform to MTCA! Boards & Solutions/ECE Magazine, 2 April 2015. [Google Scholar]

- Smetana, D. Beamforming: FPGAs rise to the challenge. Military Embedded Systems. 2 February 2015. Available online: http://mil-embedded.com/articles/beamforming-fpgas-rise-the-challenge/ (accessed on 1 July 2016).

- Altera. Radar Processing: FPGAs or GPUs? Altera: San Jose, CA, USA, May 2013. Available online: https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/wp/wp-01197-radar-fpga-or-gpu.pdf (accessed on 1 July 2016).

- Keller, J. Radar processing shifts to FPGAs and Altivec. Military Aerospace Electronics. 1 June 2003. Available online: http://www.militaryaerospace.com/articles/print/volume-14/issue-6/features/special-report/radar-processing-shifts-to-fpgas-and-altivec.html (accessed on 1 July 2016).

- Fuller, S. The opportunity for sub microsecond interconnects for processor connectivity. RapidIO: Austin, TX, USA. Available online: http://www.rapidio.org/technology-comparisons/ (accessed on 1 July 2016).

- Grama, A. Introduction to Parallel Computing, 2nd ed.; Addison-Wesley: Harlow, UK; New York, NY, USA, 2003. [Google Scholar]

- PRODRIVE. AMC-TK2: ARM and DSP AMC. PRODRIVE Technologies: Son, The Netherlands. Available online: https://prodrive-technologies.com/products/arm-dsp-amc/ (accessed on 1 July 2016).

- Texas Instruments. Multicore DSP+ARM Keystone II System-on-chip (SoC); Texas Instruments Inc.: Dallas, TX, USA, 2013. [Google Scholar]

- IEEE Standard for Floating-Point Arithmetic, IEEE Std 754-2008; IEEE: Piscataway, NJ, USA, 29 August 2008; pp. 1–70.

- AD9361 Data Sheet (Rev. E.); Analog Devices, Inc.: Norwood, MA, USA, 2014.

- Fuller, S. RapidIO: The Embedded System Interconnect; John Wiley & Sons, Ltd.: Chichester, UK; Hoboken, NJ, USA, 2005. [Google Scholar]

- Barry Wood, T. Backplane tutorial: RapidIO, PCIe and Ethernet. EE Times, 14 January 2009. [Google Scholar]

- Bueno, D.; Conger, C.; George, A.D.; Troxel, I.; Leko, A. RapidIO for radar processing in advanced space systems. ACM Trans. Embed. Comput. Syst. 2007, 7, 1. [Google Scholar] [CrossRef]

- Fishburn, J.P. Clock skew optimization. IEEE Trans. Comput. 1990, 39, 945–951. [Google Scholar] [CrossRef]

- What Is NTP? Available online: http://www.ntp.org/ntpfaq/NTP-s-def.htm (accessed on 1 July 2016).

- How Accurate Will My Clock Be? Available online: http://www.ntp.org/ntpfaq/NTP-s-algo.htm (accessed on 1 July 2016).

- IEEE Standard for A Precision Clock Synchronization Protocol for Networked Measurement and Control Systems (1588-2008); IEEE: Piscataway, NJ, USA, 24 July 2008; pp. 1–269.

- Anand, D.M.; Fletcher, J.G.; Li-Baboud, Y.; Moyne, J. A practical implementation of distributed system control over an asynchronous ethernet network using time stamped data. In Proceedings of the 2010 IEEE International Conference on Automation Science and Engneering, Toronto, ON, Canada, 21–24 Auugst 2010; pp. 515–520.

- Lewandowski, W.; Thomas, C. GPS time transfer. Proc. IEEE 1991, 79, 991–1000. [Google Scholar] [CrossRef]

- Reddaway, S.F.; Bruno, P.; Rogina, P.; Pancoast, R. Ultra-high performance, low-power, data parallel radar implementations. IEEE Aerosp. Electron. Syst. Mag. 2006, 21, 3–7. [Google Scholar] [CrossRef]

- Kung, H.T.; Leiserson, C.E. Systolic arrays (for VLSI). In Sparse Matrix Proceedings 1978; SIAM: Philadelphia, PA, USA, 1979; pp. 256–282. [Google Scholar]

- CPU Cache. Available online: https://en.wikipedia.org/wiki/CPU_cache (accessed on 1 July 2016).

- Kowarschik, M.; Weiß, C. An overview of cache optimization techniques and cache-aware numerical algorithms. In Algorithms for Memory Hierarchies: Advanced Lectures; Meyer, U., Sanders, P., Sibeyn, J., Eds.; Springer: Berlin/Heidelberg, Germany, 2003; pp. 213–232. [Google Scholar]

- Richards, M.A.; Scheer, J.A.; Holm, W.A. Priniciples of Modern Radar; Scitech Publishing: Edison, NJ, USA, 2010. [Google Scholar]

- Klilou, A.; Belkouch, S.; Elleaume, P.; Le Gall, P.; Bourzeix, F.; Hassani, M.M.R. Real-time parallel implementation of pulse-doppler radar signal processing chain on a massively parallel machine based on multi-core DSP and serial rapidio interconnect. EURASIP J. Adv. Signal Process. 2014, 2014, 161. [Google Scholar] [CrossRef]

- Texas Instruments. Enhanced Direct Memory Access 3 (EDMA3) for KeyStone Devices User's Guide (Rev. B); Texas Instruments Inc.: Dallas, TX, USA, 2015. [Google Scholar]

- Kaeli, D.R.; Mistry, P.; Schaa, D.; Zhang, D.P. Heterogeneous Computing with OpenCL 2.0, 3rd ed.; Morgan Kaufmann: Waltham, MA, USA, 2015. [Google Scholar]

- Collins, R.T.; Lipton, A.J.; Fujiyoshi, H.; Kanade, T. Algorithms for cooperative multisensor surveillance. Proc. IEEE 2001, 89, 1456–1477. [Google Scholar] [CrossRef]

- Hsueh-Jyh, L.; Rong-Yuan, L. Utilization of multiple polarization data for aerospace target identification. IEEE Trans. Antennas Propag. 1995, 43, 1436–1440. [Google Scholar] [CrossRef]

- Karimkashi, S.; Zhang, G. Design and manufacturing of a cylindrical polarimetric phased array radar (CPPAR) antenna for weather sensing applications. In Proceedings of the 2014 IEEE Antennas and Propagation Society International Symposium (APSURSI), Memphis, TN, USA, 6–11 July 2014; pp. 1151–1152.

| Parameter | Definition |

|---|---|

| C | Number of channels obtained by each PU |

| B | Number of beams processed by each PE |

| M | Numbers of PUs |

| N | Numbers of PEs in a PU |

| Total number of receiving channels | |

| Total number of beams | |

| The number of weight vectors for the ith receiving channel | |

| The ith receiving channel | |

| The number of formed beams from total of channels |

| Channel | Range Gates (Subsets) | |||

|---|---|---|---|---|

| 1024 (16) | 512 (8) | 256 (4) | 128 (2) | |

| 4 | 0.67 | 0.67 | 0.67 | 0.67 |

| 8 | 1.34 | 1.34 | 1.34 | 1.33 |

| 12 | 1.97 | 1.96 | 1.96 | 1.95 |

| 16 | 2.42 | 2.42 | 2.41 | 2.40 |

| 20 | 2.81 | 2.81 | 2.80 | 2.78 |

| 24 | 3.15 | 3.15 | 3.14 | 3.12 |

| 28 | 3.45 | 3.44 | 3.43 | 3.40 |

| 32 | 3.71 | 3.70 | 3.67 | 3.66 |

| 36 | 3.92 | 3.91 | 3.87 | 3.82 |

| 40 | 4.10 | 4.09 | 4.04 | 3.96 |

| 44 | 4.25 | 4.24 | 4.19 | 4.08 |

| 48 | 4.39 | 4.38 | 4.34 | 4.23 |

| 52 | 4.19 | 4.48 | 4.46 | 4.35 |

| Range Gates | Pulses | ||||

|---|---|---|---|---|---|

| 8 | 16 | 32 | 64 | 128 | |

| 1024 | 0.7293 | 1.6036 | 2.6852 | 3.8543 | 4.2866 |

| 2048 | 0.7294 | 1.6000 | 2.6841 | 3.8543 | 4.2867 |

| 4096 | 0.7294 | 1.5999 | 2.6842 | 3.8544 | 4.2867 |

| 8192 | 0.7295 | 1.6000 | 2.6842 | 3.8544 | 4.2732 |

| Range Gates | Pulses | ||||

|---|---|---|---|---|---|

| 8 | 16 | 32 | 64 | 128 | |

| 1024 | 21 | 33 | 64 | 126 | 253 |

| 2048 | 40 | 66 | 130 | 254 | 502 |

| 4096 | 135 | 265 | 513 | 1011 | 2028 |

| 8192 | 528 | 1025 | 2033 | 4070 | 8107 |

| Parameters | Value | Depends on |

|---|---|---|

| Range gates | 4096 | Pulse Compression |

| Pulses | 128 | Doppler Filtering |

| Channels per chassis | 48 | Beamforming |

| Beams per PE | 22 | Number of channels per chassis |

| PRI | 1 ms | Pulse compression computing time |

| CPI | 128 ms | PRI × number of pulses |

| No. of beamforming PU | 16 | Total number of antennas required by application |

| No. of PE in each PU | 12 | Total number of beams required by application |

| Total No. of Beams | 264 | PE × number of beams per PE |

| Total No. of Channels | 768 | PM × number of channels per chassis |

| Total No. of PU | 18 | Beamforming + Match Filter + Doppler Processing |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yu, X.; Zhang, Y.; Patel, A.; Zahrai, A.; Weber, M. An Implementation of Real-Time Phased Array Radar Fundamental Functions on a DSP-Focused, High-Performance, Embedded Computing Platform. Aerospace 2016, 3, 28. https://doi.org/10.3390/aerospace3030028

Yu X, Zhang Y, Patel A, Zahrai A, Weber M. An Implementation of Real-Time Phased Array Radar Fundamental Functions on a DSP-Focused, High-Performance, Embedded Computing Platform. Aerospace. 2016; 3(3):28. https://doi.org/10.3390/aerospace3030028

Chicago/Turabian StyleYu, Xining, Yan Zhang, Ankit Patel, Allen Zahrai, and Mark Weber. 2016. "An Implementation of Real-Time Phased Array Radar Fundamental Functions on a DSP-Focused, High-Performance, Embedded Computing Platform" Aerospace 3, no. 3: 28. https://doi.org/10.3390/aerospace3030028

APA StyleYu, X., Zhang, Y., Patel, A., Zahrai, A., & Weber, M. (2016). An Implementation of Real-Time Phased Array Radar Fundamental Functions on a DSP-Focused, High-Performance, Embedded Computing Platform. Aerospace, 3(3), 28. https://doi.org/10.3390/aerospace3030028