1. Introduction

Most of the efforts on DC/AC converters including the recent developments have been focused on improving renewable energy technologies such as photovoltaic (PV) systems. These technologies require robust and reliable power electronics topology to be associated with to get an efficient output [

1]. Many topologies have been developed for achieving higher reliability and efficient performance. Neutral point clamped (NPC) converters have received considerable attention because of their very high efficiency and low leakage current. This topology was initially proposed in Baker’s patent in the 1970s and was published by Nabae et al. in 1981 [

2]. Additionally, NPC topology does not produce common-mode (CM) current, thus it is more suitable for PV generation systems [

3,

4] and can support longer device lifetime with a lower instantaneous rate of voltage change (

dv/dt) [

5]. However, NPC topology suffers from unequal heat distribution among the semiconductor devices owing to uneven power loss distribution, as reported in [

6,

7,

8,

9]. To overcome this problem, the active clamped diodes were replaced by active switches, achieving and an active neutral point clamped (ANPC) topology [

9]. Although two more switches are used, it provides an additional switching state to facilitate loss distribution balancing for the whole system [

10,

11,

12,

13,

14]. Among the many studies undertaken on new modulation schemes for controlling the ANPC converter, the authors of [

15] proposed a new modulation scheme to perform a new commutation loop that offers better switching performance with lower stress on each switch. They discussed the proposed method based on quantitative analysis and comparison with different switching schemes. It is reported that the conventional virtual space vector modulation (VSVM) depends on selecting the nearest three vectors to form a linear combination of real vectors. This can control the neutral point (NP) at any modulation index (

MI), but it cannot reduce the switching losses or suppress the CM voltage. Therefore, an improved VSVM to reduce the efficiency and switching losses by selecting two pairs of small vectors based on the NP charge and the pulse sequence was developed [

16]. The results of the improved VSVM method confirm the flexibility in balancing the NP voltage with different

MI. Similar works can be found in [

17,

18,

19,

20].

Among the various control switching strategies, better combinations for the same topology used in industrial applications can be achieved by a higher switching frequency by using a wide band gap (WBG). In this regard, a creative method was presented to improve the reliability of wind turbine generation (WTG), by proposing an open-circuit fault detection method using back-to-back converters using the NPC topology as shown in [

21] and similarly in [

22], while a new hybrid combination including two different types of switches to perform hybrid ANPC (HANPC) converters has been recently considered by many researchers. Although Si-IGBTs are the commonly used technology in power converters, they have some limitations in terms of switching frequency. Therefore, the trends are to move toward using SiC-MOSFETs as they can work under higher switching frequency with lower switching losses, as shown in [

23]. However, the usage of full SiC-MOSFET topology is regarded as uneconomical because the cost of SiC-MOSFETs is up to a factor of 8 higher than that of Si-IGBTs and almost a factor of 2 higher than that of Si-MOSFETs [

24]. Conventional NPC, ANPC, and HANPC converters are opposed to fault during operation. Meanwhile, in some systems, reliable and continuous operation is highly important because of the sensitivity, cost, and critical application of these systems. Therefore, the need for fault tolerance and the capability of re-operating the power system adequately and safely has drawn considerable interest during the past decade [

25]. In general, most studies have focused on tolerating faults by adding new parts to the main topology [

26]. The authors of [

27] maintained a fault tolerance strategy for full-SiC devices in an ANPC inverter by adding an additional leg to the inverter. The main objective was to obtain the output waveforms for safe operation. Similarly, another study added two additional switches and six diodes to the middle switches of all phases in T-type converters [

28]. The main purpose was to maintain additional paths for the current in the case of device failure. Similarly, in [

29] and [

30], the fault-tolerant capability for different topologies converters was investigated; where the proposed fault-tolerant method in [

29] focused on the equivalent substitution of voltage space vector for cascaded H-bridge multilevel inverter. While, in [

30], the proposed method applied for NPC/H-bridge (CNHB) inverters. It mainly works on maintaining the three-phase equilibrium and minimizing the imbalance between the stacks. Nevertheless, in some of the fault scenarios, the inverter has to be controlled with decreased

MI. Furthermore, some studies consider the diagnosis and fault tolerance for different T-type and NPC inverters as shown in [

31,

32,

33,

34,

35,

36]. In these studies, the diagnosis was performed for the open-circuit fault within the proposed topology concerning the turn-on time for fault control.

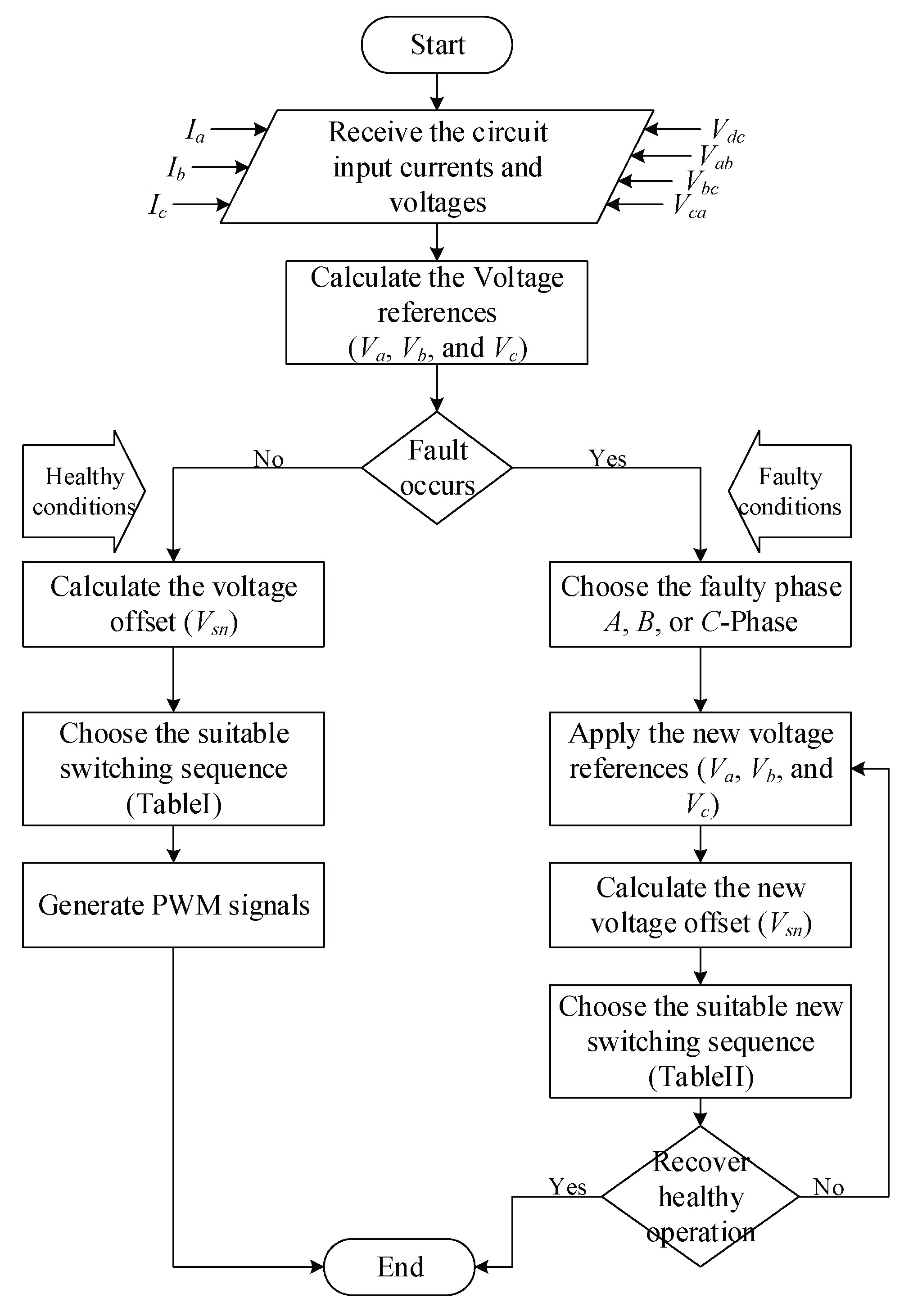

Generally, most of the previous methods require additional devices such as fuses, switches, or entire legs to be added to the standard inverter topology for tolerating device failure. Moreover, the systems exhibited low response, higher ripple output, or lower output waveforms (from three to two levels), which would increase the cost and could even reduce the reliability of the inverters and drive systems. In these regards, this paper proposed an effective method that can be applied for HANPC to recover the healthy operation and eliminate the fault effects on the system without the need for adding any extra devices. Therefore, it results in recovering the healthy operation, improving the reliability of the converter’s applications, eliminating the output distortion that clearly appears in the total harmonic distortion (THD), and works on balancing the DC link voltages.

2. Physical Model of HANPC Inverters

The proposed algorithm in this paper focuses on HANPC topology, where this topology built and operated mainly for high-efficiency and high-power appliance. Besides, it has unique switching sequences and circuit combination as it includes a hybrid combination of Si-IGBT and SiC-MOSFET devices, which is built and developed with reference to other topologies such as the standard NPC and the conventional ANPC topologies. NPC topology is a common three-level topology, and it is widely used in medium and high-power photovoltaic inverters. The voltage stress on each power device of the NPC is only half of the bus voltage thus smaller rating devices are used. Moreover, its output voltage harmonic content is lower compared with the two-level inverters. In these regards, the NPC converters seem to be one of the most promising and used topologies in different industrial applications. While multilevel converters are regarded as an industry-standard solution to realize AC–DC or DC–AC power conversion in high power applications. They have been applied to a medium voltage drive system, wind energy generation system, photovoltaic generation system, battery charging system for electric vehicles, and power supplies for modern data centers, etc. It is worth mentioning that three-level converters are the most popular choices in the family of multilevel converters and the most available in different industrial applications. Compared with other multi-level topologies, three-level converters have low switching losses, smaller AC side filter size, and less complexity, as well as the lowest associated costs [

36]. Among all the existing three-level topologies, the NPC converters are the most popular topologies [

24,

37].

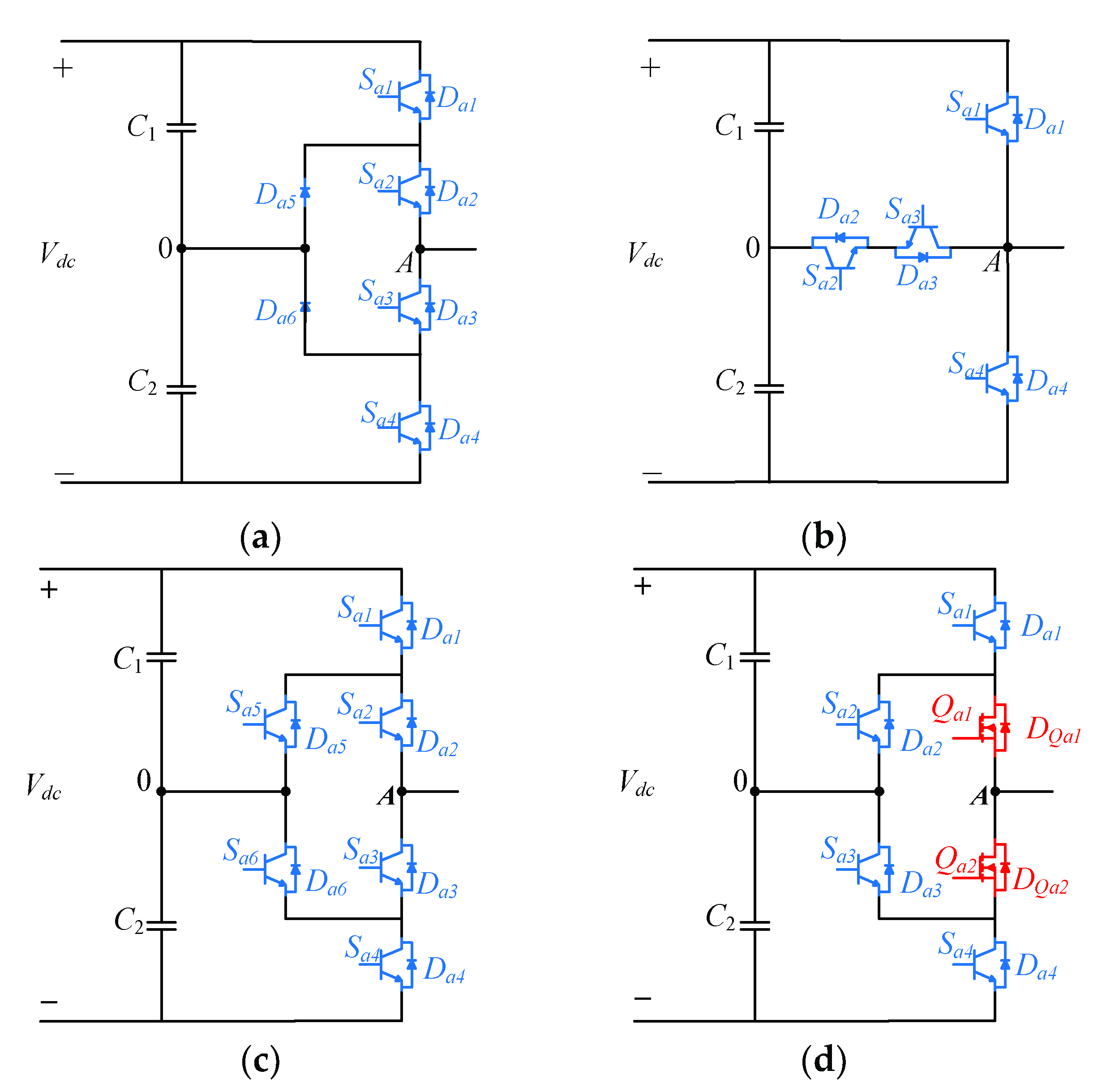

The basic idea of the HANPC circuit has been developed from the conventional NPC and T-type topologies as shown in

Figure 1.

Figure 1a,b present the optimal single leg configuration of the conventional three-level NPC and T-Type converters, respectively. The NPC converter consists of 4-IGBT switches (

Sx1/

Dx1 to

Sx4/

Dx4) with the associated diodes in addition to 2-active diodes (

Dx5 to

Dx6) in each phase. Similarly, the T-type converter is combined of 4-IGBTs (

Sx1/

Dx1 to

Sx4/

Dx4) two of them work as half-bridge and two as neutral point IGBTs. Where

x represents A-, B-, or C-phases. For the NPC topology, there are two loops for commutation paths. The first path includes the inner loop which starts when the current flows through the clamping diode (

Da6) with the outer switch (

Sa4). While the second loop starts when the inner switch (

Sa2) with either the inner diode (

Da3) or the outer diode (

Da4) being based on the modulation scheme where due to the symmetrical structure of the top and bottom these loops, it can reflect the remaining commutation loops. In the same manner, in the T-type two main loops are performed; the first when the current pass through the upper switch (

Sa1) and the inner switch (

Sa2) while the other loop goes through the lower switch (

Sa4) and the inner switch (

Sa3) depending on the modulation scheme. Meanwhile, the NPC inverter uses two switches connected in series to block the full DC link voltages compared to one switch in T-type inverters. Consequently, the basic configuration of the conventional ANPC is shown in

Figure 1c. It consists of six Si-IGBT (

Sx1/

Dx1 to

Sx4/

Dx6) in each phase leg, where the main advantage of the ANPC is balancing the switching losses that appear in the NPC topology, as explained in the literature. Meanwhile, the HANPC topology is shown in

Figure 1d. it consists of four Si-IGBT (

Sx1/

Dx1 to

Sx4/

Dx4) and two SiC-MOSFET (

Qx1/

DQx1 and

Qx2/

DQx2) switches alongside with the associated diodes in each phase leg. A total of 12 Si-IGBT and 6 SiC-MOSFET switches. It is worth mentioning that the total number of the switches in HANPC is the same when compared to the conventional ANPC but the HANPC is considered as a new topology that can reduce the switching losses and enhancing the system performance by reducing the total harmonic distortion (THD) and work on higher switching frequencies with its unique switching sequences [

30]. It also replaces the inner two IGBTs (

Sa1/

Da1 – Sa4/

Da4) with two MOSFETs (

Qa1/

DQa1 and

Qa2/

DQa2) switches.

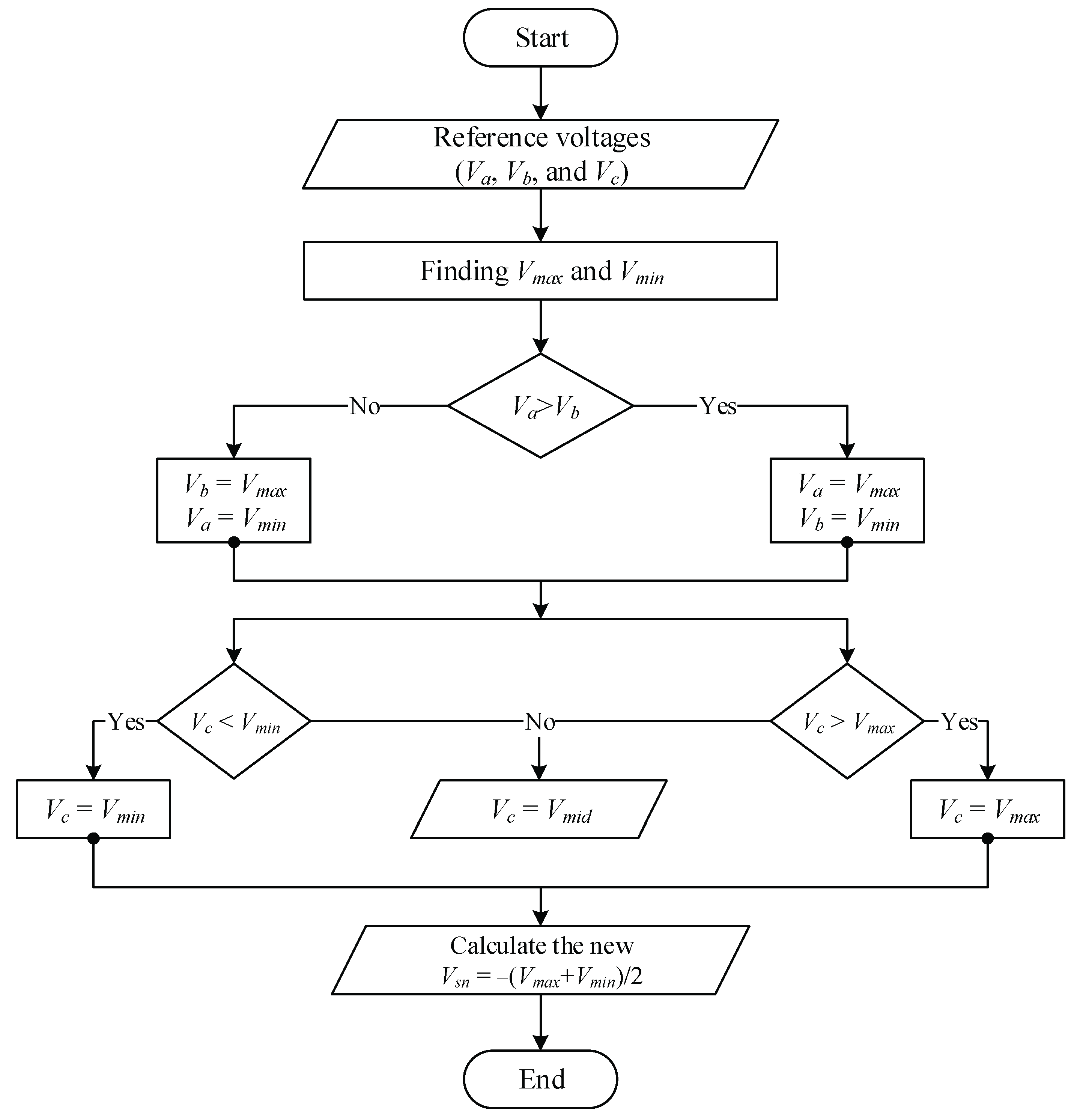

The new and conventional switching sequence of all topologies is shown in

Figure 2.

Figure 2a shows the conventional switching sequences of the NPC, T-type, and ANPC topologies. While

Figure 2b shows the new switching sequences for HANPC topology. These changes have the advantage of using the IGBT switches on the lowest possible frequencies (fundamental frequency 50 Hz) and the MOSFET switches on high frequency (30 kHz) due to the fact that the switching losses are lower than the conduction losses for the MOSFETs while having the potential to operate at a higher junction temperature than regular Si-IGBT switches. On the other hand, the opposite is correct for the IGBTs [

24].

Therefore, balancing the losses distribution is unnecessary between the different switching devices. Besides, by using the hybrid combination of these switches offers an affordable price with almost the same efficiency as the full SiC-MOSFET converters. In this work, we consider the A-phase for offering the necessary explanation.

The detailed switching sequences of the HANPC are shown in

Table 1. The proposed modulation scheme depends on working based on four different switching states (

P, O+,

O–, and

N) as shown in

Table 1. In this table, the three-voltage states

O,

P, and

N represent the zero, positive, and negative voltage levels, respectively.

Additionally, the On-Off switching states for all Si-IGBT and SiC-MOSFET switches under healthy conditions (i.e., with no-fault occurring). During the healthy operation, the IGBT switches are working in pairs with complementary behavior (Sa1/Da1 and Sa3/Da3) and (Sa2/Da2 and Sa4/Da4). While the SiC-MOSFET switches have the same complementary procedure between Qa1/DQa1 and Qa2/DQa2. Subsequently, in the positive half cycle, Sa1/Da1 and Sa3/Da3 are in the On-state 1, and Sa2/Da2 and Sa4/Da4 are in the off-state 0, at the same rate of the fundamental frequency. While a complementary operation at 30 kHz is applied by Qa1/DQa1 and Qa2/DQa2. The opposite occurs during the negative half cycle.

Accordingly, numerous fault tolerance methods were proposed in the literature for conventional topologies. Some researchers have focused on tolerating the faults by inserting additional hardware parts to the basic topology, which results in increasing the system cost which could be regarded as a huge drawback and adding complexity to the control and the hardware design [

27,

28,

29,

30]. Accordingly, the usage of the available vectors instead of the impossible vectors are applied for T-type inverter as shown in [

31]. However, such control scheme relatively eliminates the current distortion when an open-circuit fault occurs. Besides, it still limited to the proposed topology and inapplicable for other topologies such as HANPC, due to the differences in the topology configuration and working principle as shown in previous sections. Consecutively, in the case of the fault, the conventional methods are inapplicable for HANPC topology. Therefore, the need of finding a new method that can be applied to the HANPC is highly needed.

4. Simulation Verification and Performance Analysis

To clarify the effects of an open-circuit fault on any switch, an analyzed simulation using PSIM and Visual Studio software is carried-out.

Table 3 shows the simulation parameters. In

Figure 8, shows the line-to-line voltage (

Vab), pole voltage (

Van), three-phase load currents, and the DC link voltages (

VC1 and

VC2) of A-phase before and after a fault in

Sa1/

Da1. Meanwhile, the fault is assumed to happen and detected at

t = 0.05 s. Regarding the results shown in

Figure 8a, shows the effects of open-circuit fault in

Sa1/

Da1 before applying the proposed algorithm, the influence on the pole voltage and load current is clear as described in

Section 3.1.

As clarified in

Table 2, the proposed fault tolerant strategy should be able to keep hybrid switching frequency to avoid any further conduction losses or additional load on any IGBT or SiC-MOSFET devices for each case of the fault at

Sa1/

Da1,

Sa2/

Da2, and

Qa1/

DQa1. The other switching sequences can be obtained by following the proposed switching sequences which are shown in

Table 2.

The results in

Figure 8b show the resuming of the normal operation and the effects on the THD as it improved from 52.47% at fault to 2.75% using the proposed method compared with 1.17% in the healthy condition.

Figure 8c shows the distribution of the THD after applying the proposed control strategy. However, the maximum

MI is reduced to 0.577 of the original value at healthy conditions due to the fault and changing the reference voltages as described in

Section 3.1. Meanwhile, hybrid switching should be kept as mentioned earlier, by considering inverting the switching sequence for the MOSFET switches (

Qa1/

DQa1 and

Qa2/

DQa2), as illustrated in

Table 2.

Additionally, the loss balancing capability of the HANPC converter should be satisfied to some extent with respect to the location of the fault. Moreover, the loss balancing capability of the HANPC converter should be satisfied to some extent with respect to the location of the fault.

Figure 9 presents the result of simulating the fault in

Sa2/

Da2.

It shows a slight difference in the output signal after applying the proposed algorithm since in this case, the inverter is applicable to re-operate with the full

MI as is it in the healthy conditions. This is due to operating the faulty leg (

A-phase) as a conventional leg NPC, as clarified in

Figure 4 for the vectors’ selection. While the other leg still worked according to the HANPC strategy. Therefore, the inverter is still capable of balancing the losses distribution. In this case,

Sa2/

Da2 is open due to the open-circuit fault, and in the tolerance control strategy.

Sa3/

Da3 is forced to be open and then changing the switching sequence to operate similarly to the conventional NPC inverter. However, due to the physical limitation of the IGBT switches, the switching frequency of the MOSFET and IGBT switches is set to 10 kHz only, while the results are shown in

Figure 9b the resuming of the normal operation and the effects on the THD as it improved from 8.58% at fault to 1.19% using the proposed method compared with 1.17% at the healthy condition.

Figure 9c shows the distribution of the FFT after applying the proposed control strategy. The simulation result is shown in

Figure 10a. For

Qa1/

DQa1 open-circuit fault, the tolerance general operational performance is similar to

Sa1/

Da1 in terms of reducing the

MI as described in

Section 3.1 by following the switching sequence that is described in

Table 2. Additionally, the loss balancing capability of the HANPC converter should be satisfied to some extent with respect to the location of the fault. Meanwhile,

Figure 10b shows the simulation result under

Qa1/

DQa1 open-circuit with the effects on the THD of 52.44% to 2.74% using the proposed method before and after using the proposed method. While

Figure 10c shows the distribution of the THD after applying the proposed control strategy. Accordingly, the proposed switching sequences under an open-circuit fault are shown in

Figure 11.

The description of

Figure 11 can be clarified with respect to

Figure 3. Under the device failure condition, due to the symmetrical structure of HANPC topology, the failure of

Sa1/

Da1 and

Sa4/

Da4 has similar effects on the inverter, and this is also valid for the other pairs:

Sa2/

Da2 and

Sa3/

Da3,

Qa1/

DQa1, and

Qa2/

DQa2. Therefore, only one from each pair of devices in

A-phase is analyzed.

Figure 3 shows the examples of the current flow path at different output voltage levels under the open failure of

Sa1/

Da1,

Sa2/

Da2, and

Qa1/

DQa1, respectively. The positive current direction is defined as flowing out of the phase. As seen, when

Sa1 open failure occurs at “

P” state, if

Ia > 0, as shown in

Figure 3a, then the phase output is connected to the neutral point (NP) of DC link instead of the positive DC bus. In

Figure 3e,

Qa1 open failure occurs at ‘

O−’ state when

Ia > 0, then the phase output is connected to the negative DC bus terminal rather than NP of DC link.

Figure 3d shows that

Sa2 open failure occurs at ‘

O−’ state when

Ia < 0, then the phase output is connected to the positive DC bus instead of NP of dc-link. Due to the incorrect output voltage, the output current will become unsymmetrical and the NP of the DC link will be unbalanced. Moreover, when

Da1 open fault occurs at ‘

P’ state and

Ia < 0, as shown in

Figure 3b, the condition is even worse since the phase current

Ia becomes discontinuous due to the cutoff of the conduction path, then the induced voltage on the load inductor and loop inductor may cause overvoltage on the inverter and cause damage. For other device failure cases, the circuit can be analyzed in a similar way.

In these regards, the modified switching sequences for the fault-tolerant operation under open failure are given in

Table 2. After device open failure, the inverter is no longer operates under the normal conditions and it changes to operate under fault tolerant operation (faulty conditions). A new switching sequence is selected to generate each switching state in a specific order with respect to the fault. In this case, when an open circuit fault occurred at

Sa1/

Da1 as shown in

Figure 11a, the HANPC inverter is derived into an unnormal operation which leads to disturbing the output terminal of the faulty phase and results in unbalanced output. Therefore, the faulty phase needs to be connected to the NP of the DC link. While the modulation signals also need to be modified in order to maintain the balanced three-phase line-to-line voltages. When the faulty phase can only output ‘0’ voltage level, instead of using the balanced phase voltages as the reference signals, it must modify the reference signals to ensure that the line-to-line voltages are balanced in HANPC inverters while the pole voltage is clamped to the NP. Therefore, the proposed switching sequences are shown in

Figure 11a, the new switching sequences aim always to clamp the faulty phase to the NP as explained earlier. For example, when the switches

Qa1/

DQa1, and

Qa2/

DQa2 are switching in a complementary order at 30 kHz while

Sa2/

Da2 and

Sa3/

Da3 operate at the fundamental frequency 50 Hz. The complementary working principle is still necessary to keep the value of the maximum DC link voltage to half (0.5) of its maximum value, so every switch is still needed to block half of the DC link value without being proposed to the overvoltage. Besides,

Ia is connected to NP of the DC link, instead of the positive DC bus terminal, which causes an unbalance of NP voltage and thus unbalanced output current. Therefore, the output current would be always clamped to the NP which is the main point of the proposed strategy.

Figure 11b, shows the proposed switching sequence after an open circuit happened at

Sa2/

Da2. The main principle of the proposed method when an open circuit fault occurred at

Sa2/

Da2 is to operate at a switching frequency of 10 kHz for all IGBTs (the allowable frequency for the Si-IGBTs [

38]), and reduce the switching frequency of the SiC-MOSFET switches from 30 kHz to 10 kHz. Besides, when

Sa2/

Da2 fails to open, the HANPC inverter is derived into a similar configuration as the conventional NPC inverter. The faulty phase is still able to output three voltage levels, and the maximum modulation index and the output voltage waveform almost the same as normal operation. Moreover, the device power loss balancing function can still be implemented to some extent during fault-tolerant operation as explained earlier. For more clarifications, if only

Da2 fails, while

Sa2 is healthy, then besides the ‘

O+’ switching states, the faulty phase can still generate ‘

O−’ switch in states when the phase current is negative, which can be used for power loss balancing as well. However, in only

Sa2 fails, while

Da2 is healthy, then the ‘

O+’ and ‘

O−’ switching states could be generated at the positive cycle of the current.

Figure 11c shows the proposed switching sequence after an open circuit happened at

Qa1/

DQa1. In the proposed method, after an open circuit fault occurred at

Qa1/

DQa1, its necessary to clamp the faulty phase to the NP. This is carried out by changing the switching states of the faulty phase by cutting the current paths to the (+) and (−) terminals; in this way, the ‘

P’ and ‘

N’ status are terminated. Consequently, the upper switches and lower switches (i.e.,

Sa1/

Da1 and

Sa4/

Da4) state are set to ‘0’. In these regards, and to clamp the faulty phase to the NP when

Qa1 has an open circuit, the switching of the

Qa2 should be kept switching, therefore it works on providing a path of the current to the NP. Following the switching sequence that is clarified in

Table 2. In addition, it still necessary to provide a new set of voltage references as shown in Equations (1) and (2). As seen, to avoid over modulation, the maximum modulation index is limited to 0.577 during fault-tolerant operation, which is 1/√3 of that in normal operation.

5. Experimental Verification

To verify the proposed fault tolerant method a 15 kW HANPC inverter Prototype is used.

Figure 12, shows the experimental setup in this paper. The power devices used are Si IGBTs (SK75GBB066T, Semikron, Nuremberg, Germany) and SiC MOSFETs (C2M0040120D, Cree, NC, USA), modules, using TMS320F28335 digital signal processor (DSP) control board from Texas Instruments (TI, TX, USA). Owing to hardware limitations, the DC-link voltage is reduced to 200 V.

The fault effects on the circuit after an open-circuit fault occurred at

Sa1/Da1 is shown in

Figure 13a. The effects of the fault are clear on the three-level line-to-line voltage, pole voltage, and three-phase currents. On the other hand, applying the proposed figure results in recovering the healthy operation of the inverter as

Figure 13b. However, the proposed method restored the normal operation, but the

MI is reduced to 0.577 of it is the original value at the normal operation. This is due to the loss of large and medium voltage vector due to cutting the current path as explained in

Section 3.1 and

Section 3.2.

Figure 13c, shows the effectiveness of the proposed method in balancing the DC link voltages. The left part of

Figure 13c shows the result of an open-circuit fault at

Sa1/Da1 on unbalancing DC link voltages before applying the proposed control strategy. On the other hand, the right part of

Figure 13c confirmed the capability of balancing the system after applying the proposed strategy, where the reduction in the

MI and the usage of the small vectors unaffected the system performance in balancing the DC link voltages and marinating healthy operation of the HANPC inverter.

Figure 14 shows the experimental results for open fault at

Sa2/

Da2 before and after applying the proposed algorithm. In this case of the fault, the inverter is still capable to operate at its full

MI without any reduction in it. This is due to following the proposed switching sequences to re-operate the HANPC inverter is derived into a similar configuration as the conventional NPC inverter. The faulty phase is still able to output three voltage levels, and the output voltage waveform quality is the same as normal operation. in

Figure 14a, the fault effects on the output voltage and current waveforms are presented. While

Figure 14b confirms the capability of the proposed method in obtaining the full

MI and recovering the healthy operation under the fault case. By comparing the result of this figure and the healthy operation which is shown in

Figure 13b, the output showed the three-level line-to-line voltage, pole voltage, and three-phase currents. Moreover,

Figure 14c shows the effects of the fault on the DC link voltage. The left part of the figure shows the unbalance DC link voltages, while the right part of the figure shows the result of applying the proposed fault tolerance strategy in balancing the DC link voltages.

Furthermore, it is noticed that in the case of an open fault in this switch, the inverter is still capable of working on the full

MI in a similar way to the healthy operation despite the increased level of the THD as shown in

Section 4. For the open-circuit fault at

Qa1/

DQa1, the results are shown in

Figure 15a. It is clear that the operational behavior of the healthy conditions is operated with reduced

MI unlike the case of

Sa2/

Da2 open-circuit failure where the

MI can be totally recovered to be the same as in the healthy conditions. By applying the proposed fault tolerance strategy, the

MI is reduced to 0.577 of it is the original value.

Figure 15b shows obtaining a healthy operation after applying the proposed algorithm on the line-to-line voltage, pole voltage, and three-phase currents. Also, the proposed method results in balancing the DC link voltages as shown in

Figure 15c. The unbalanced DC link voltages is shown in the left part of the figure, while the right part confirms the capability of the proposed method in balancing the DC link voltages.

Based on the experimental result for the various cases of the fault at Sa1/Da1, Sa2/Da2, and Qa1/DQa1, it could be concluded that the experimental results confirmed the effectiveness of the proposed control strategy under the faulty conditions. By maintaining the same operation as the simulation results accurately for each case. Therefore, the experimental results guarantee that the proposed method performs the fault tolerance of open-circuit faults for the three-level HANPC inverters.