A V-Band Phase-Locked Loop with a Novel Phase-Frequency Detector in 65 nm CMOS

Abstract

1. Introduction

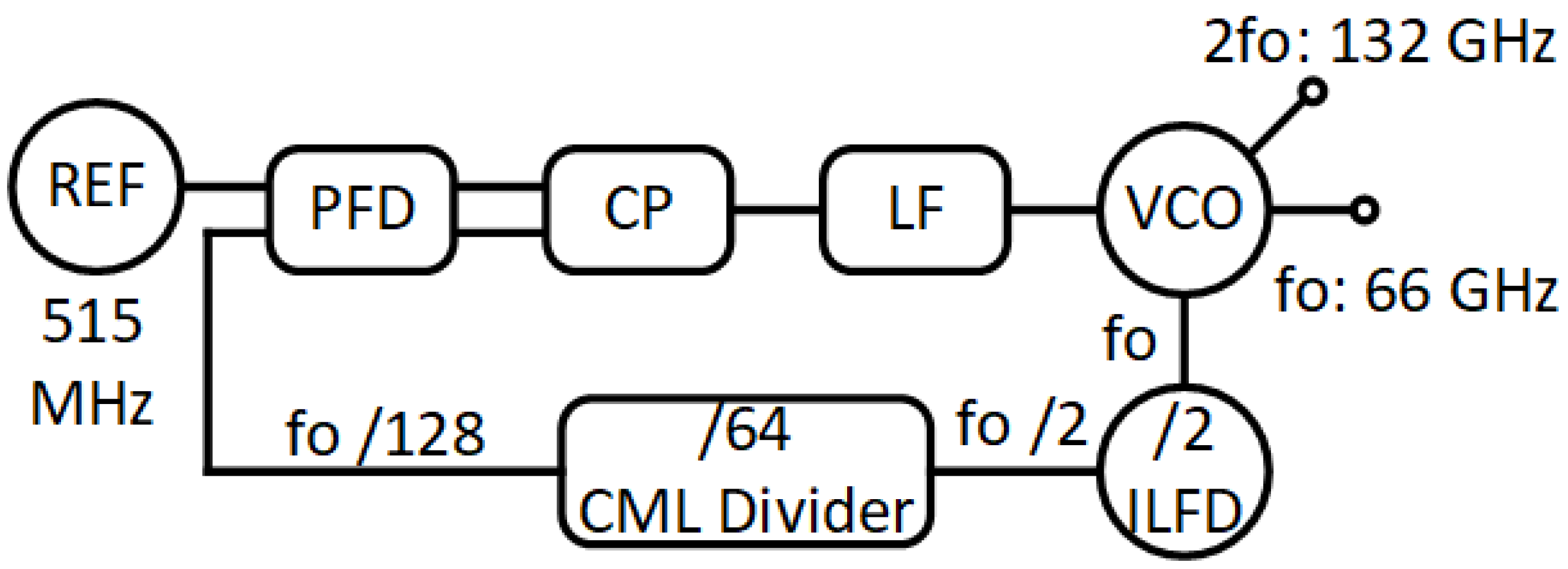

2. PLL Architecture

3. Design Details

3.1. Voltage-Controlled Oscillator (VCO)

3.2. Injection-Locked Frequency Divider (ILFD)

3.3. CML Frequency Divider Chain

3.4. Phase-Frequency Detector (PFD)

3.5. Charge Pump (CP) and Loop Filter (LF)

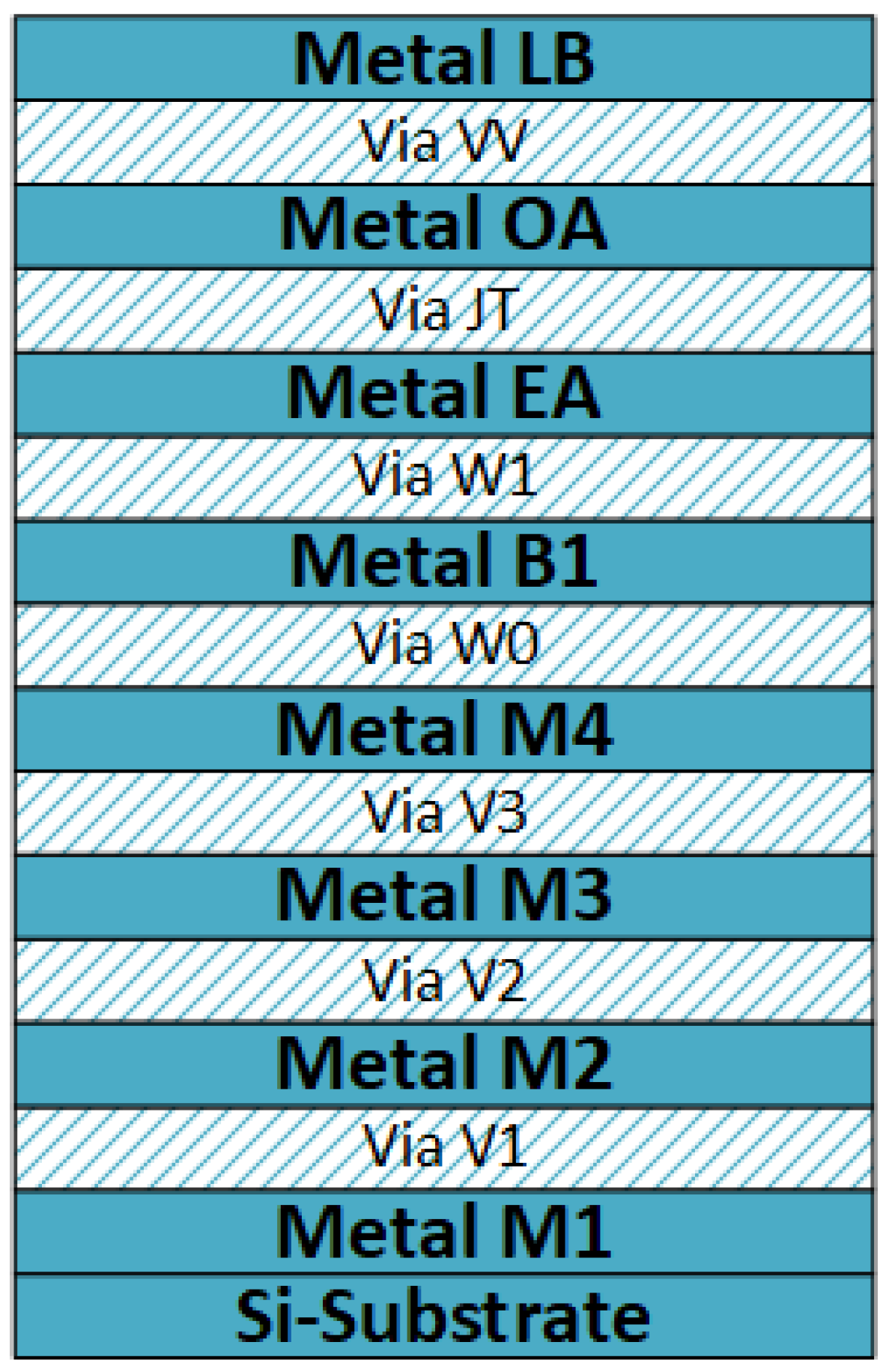

3.6. Layout Designing

4. Measured Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kim, N.; Song, K.; Yun, J.; Yoo, J.; Rieh, J. Two 122-GHz Phase-Locked Loops in 65-nm CMOS Technology. IEEE Trans. Microw. Theory Tech. 2016, 64, 2623–2630. [Google Scholar] [CrossRef]

- Jain, S.; Zhang, N.; Belostotski, L. Millimeter-wave CMOS PLL using a push-push oscillator. In Proceedings of the IEEE 30th Canadian Conference on Electrical and Computer Engineering (CCECE), Windsor, ON, Canada, 30 April–3 May 2017; pp. 1–4. [Google Scholar]

- Tsai, K.; Liu, S. A 104-GHz Phase-Locked Loop Using a VCO at Second Pole Frequency. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2012, 20, 80–88. [Google Scholar] [CrossRef]

- Shahramian, S.; Hart, A.; Tomkins, A.; Carusone, C.A.; Garcia, P.; Chevalier, P.; Voinigescu, S.P. Design of a Dual W- and D-Band PLL. IEEE J. Solid State Circuits 2011, 46, 1011–1022. [Google Scholar] [CrossRef]

- Chiang, P.; Wang, Z.; Momeni, O.; Heydari, P. A 300GHz frequency synthesizer with 7.9% locking range in 90nm SiGe BiCMOS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 260–261. [Google Scholar]

- Zhao, Y.; Chen, Z.Z.; Du, Y.; Li, Y.; Hadi, R.A.; Virbila, G.; Xu, Y.; Kim, Y.; Tang, A.; Reck, T.J.; et al. A 0.56 THz Phase-Locked Frequency Synthesizer in 65 nm CMOS Technology. IEEE J. Solid State Circuits 2016, 51, 3005–3019. [Google Scholar] [CrossRef]

- He, J.; Xiong, Y.Z.; Li, J.; Hou, D.; Hu, S.; Yan, D.L.; Arasu, M.A.; Zhang, Y.P. A fully integrated 166-GHz frequency synthesizer in 0.13-μm SiGe BiCMOS for D-band applications. In Proceedings of the 2014 International Symposium on Integrated Circuits (ISIC), Singapore, 10–12 December 2014; pp. 156–159. [Google Scholar]

- Yeh, Y.; Lin, X.; Chang, H.; Chen, K. A V-band 65 nm CMOS low DC power low phase noise PLL using divide-by-three injection-locked frequency divider. In Proceedings of the 2016 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), Taipei, Taiwan, 24–26 August 2016; pp. 1–3. [Google Scholar]

- Chen, H.; Wang, T.; Lu, S. A Millimeter-Wave CMOS Triple-Band Phase-Locked Loop with A Multimode LC-Based ILFD. IEEE Trans. Microw. Theory Tech. 2011, 59, 1327–1338. [Google Scholar] [CrossRef]

- Parvais, B.; Scheir, K.; Vidojkovic, V.; Vandebriel, R.; Vandersteen, G.; Soens, C.; Wambacq, P. A 40 nm LP CMOS PLL for high-speed mm-wave communication. In Proceedings of the 2010 ESSCIRC, Seville, Spain, 13–17 September 2010; pp. 254–257. [Google Scholar]

- Xu, Z.; Gu, Q.J.; Wu, Y.; Jian, H.; Wang, F.; Chang, M.F. An integrated frequency synthesizer for 81–86GHz satellite communications in 65nm CMOS. In Proceedings of the 2010 IEEE Radio Frequency Integrated Circuits Symposium, Anaheim, CA, USA, 23–25 May 2010; pp. 57–60. [Google Scholar]

- Abedi, R.; Kananizadeh, R.; Esmaili, A.; Momeni, O.; Heydari, P. A 53–61GHz Low-Power PLL With Harmonic Positive Feedback VCO in 65nm CMOS. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Garg, S.K.; Singh, B. A novel design of an efficient Low Power Phase Frequency Detector for Delay Locked Loop. In Proceedings of the 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 4–6 July 2016; pp. 1–4. [Google Scholar]

- Ali, I.; Oh, S.J.; Abbasizadeh, H.; Rikan, B.H.; Rehman, M.R.U.; Lee, D.S.; Lee, K.Y. An ultra-low power fully synthesizable digital phase and frequency detector for ADPLL applications in 55 nm CMOS technology. In Proceedings of the 2017 13th International Conference on Emerging Technologies (ICET), Islamabad, Pakistan, 27–28 December 2017; pp. 1–6. [Google Scholar]

- Huang, Q.; Zhan, C.; Burm, J. A low-complexity fast-locking digital PLL with multi-output bang-bang phase detector. In Proceedings of the 2016 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Jeju, Korea, 25–28 October 2016; pp. 418–420. [Google Scholar]

- Nasrollahpour, M.; Agrawal, P.; Sreekumar, R.; Yen, C.H.; Aldacher, M.; Ye, S.; Hamedi- Hagh, S. Design of a 65-69 GHz 1000:1 FMCW PLL in 65nm CMOS Technology. In Proceedings of the 2019 IEEE Texas Symposium on Wireless and Microwave Circuits and Systems (WMCS), Waco, TX, USA, 28–29 March 2019; pp. 1–5. [Google Scholar]

- Abdulaziz, M.; Forsberg, T.; Tormanen, M.; Sjoland, H. A 10-mW mm-Wave Phase-Locked Loop with Improved Lock Time in 28-nm FD-SOI CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 1588–1600. [Google Scholar] [CrossRef]

- Kuncham, S.S.; Gadiyar, M.; Sushmitha, D.K.; Lad, K.K.; Laxminidhi, T. A Novel Zero Blind Zone Phase Frequency Detector for Fast Acquisition in Phase Locked Loops. In Proceedings of the 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), Pune, India, 6–10 January 2018; pp. 167–170. [Google Scholar]

- Ahmad, A.A.; Ali, S.H.M.; Kamal, N.; Abdul Rahman, S.R.; Othman, M. Design of Phase Frequency Detector (PFD), Charge Pump (CP) and Programmable Frequency Divider for PLL in 0.18um CMOS Technology. In Proceedings of the 2018 IEEE International Conference on Semiconductor Electronics (ICSE), Kuala Lumpur, Malaysia, 15–17 August 2018; pp. 242–245. [Google Scholar]

- Jandhyala, S.; Tapse, S. A power efficient phase frequency detector and low mismatch charge pump in on-chip clock generator. In Proceedings of the 2016 IEEE Distributed Computing, VLSI, Electrical Circuits and Robotics (DISCOVER), Mangalore, India, 13–14 August 2016; pp. 57–61. [Google Scholar]

- Kumar, N.; Kumar, M. Design of low power and high-speed phase detector. In Proceedings of the 2016 2nd International Conference on Contemporary Computing and Informatics (IC3I), Noida, India, 14–17 December 2016; pp. 676–680. [Google Scholar]

| Parameter | [8] | [9] | [10] | [11] | [12] | [16] | [17] | Our Work |

|---|---|---|---|---|---|---|---|---|

| Technology (nm) | 65 | 90 | 40 LP | 65 | 65 | 65 | 28 | 65 LP |

| Frequency (GHz) | 58.5–58.9 | 60.2–62.4 | 63–70 | 70–78 | 53–61 | 65–69 | 54.1–57 | 65.15–67.4 |

| Supply Voltage (V) | 1.2 | 1.5 | 1.1 | 1 | 0.8 | 1.2 | - | 1.4 |

| PN@1MHz (dBc/Hz) | −83.5 | −69.92 | −85 | −83 | −88 | −98.5 ** | −93 | −84.43 |

| Ref. Frequency (MHz) | 150 | 78 | - | - | 56 | 67 | 2280 | 515 |

| Power Consumption (mW) | 43 | 106.6 | 79.2 | 65 | 48 | 72.44 | 10 | 88 |

| Active Chip Area (excluding pads) () | 1 * | 1.12 * | 0.192 | 0.31 | 0.32 | 3.24 * | 0.19 | 0.37 |

| Output Power (dBm) | −14 | −9.5 | - | - | - | - | - | −11.6 |

| FOM (dBc/Hz) | 119.16 | 116.5 | 142.9 | 142.9 | 148.6 | 152.58 | 152.24 | 132.58 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Abbas, W.; Mehmood, Z.; Seo, M. A V-Band Phase-Locked Loop with a Novel Phase-Frequency Detector in 65 nm CMOS. Electronics 2020, 9, 1502. https://doi.org/10.3390/electronics9091502

Abbas W, Mehmood Z, Seo M. A V-Band Phase-Locked Loop with a Novel Phase-Frequency Detector in 65 nm CMOS. Electronics. 2020; 9(9):1502. https://doi.org/10.3390/electronics9091502

Chicago/Turabian StyleAbbas, Waseem, Zubair Mehmood, and Munkyo Seo. 2020. "A V-Band Phase-Locked Loop with a Novel Phase-Frequency Detector in 65 nm CMOS" Electronics 9, no. 9: 1502. https://doi.org/10.3390/electronics9091502

APA StyleAbbas, W., Mehmood, Z., & Seo, M. (2020). A V-Band Phase-Locked Loop with a Novel Phase-Frequency Detector in 65 nm CMOS. Electronics, 9(9), 1502. https://doi.org/10.3390/electronics9091502