An Ultra-Low-Power Area-Efficient Non-Coherent Binary Phase-Shift Keying Demodulator for Implantable Biomedical Microsystems

Abstract

1. Introduction

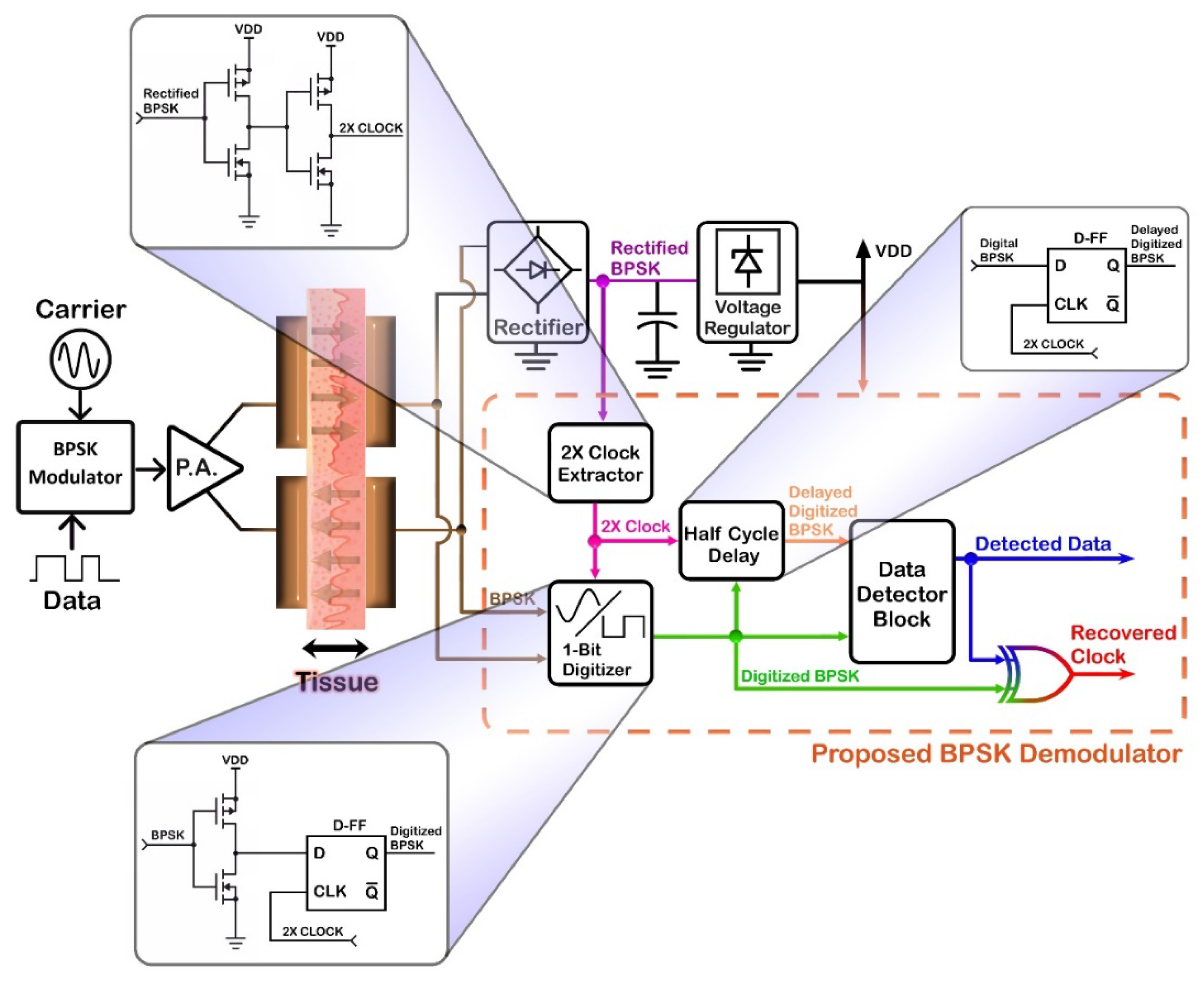

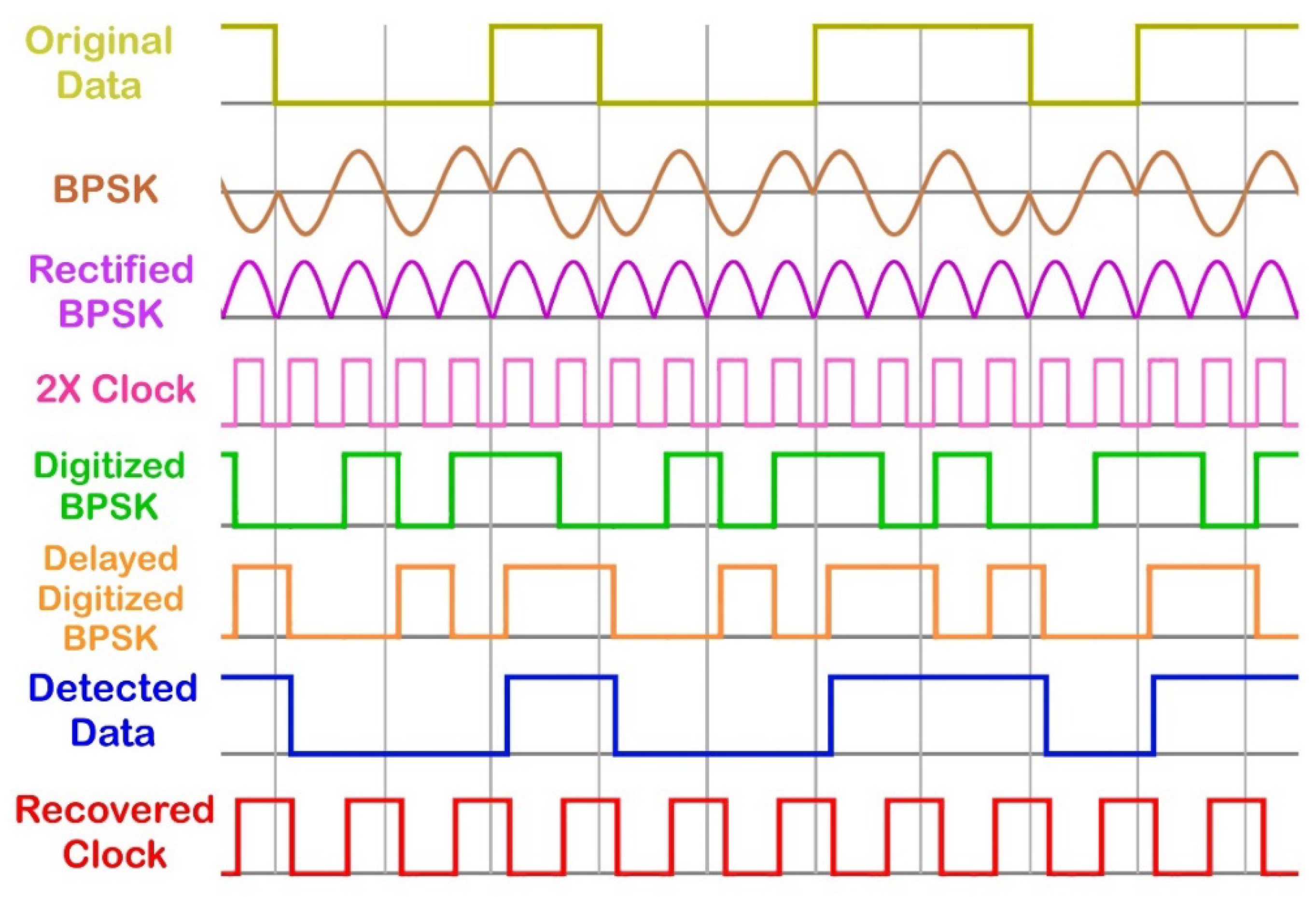

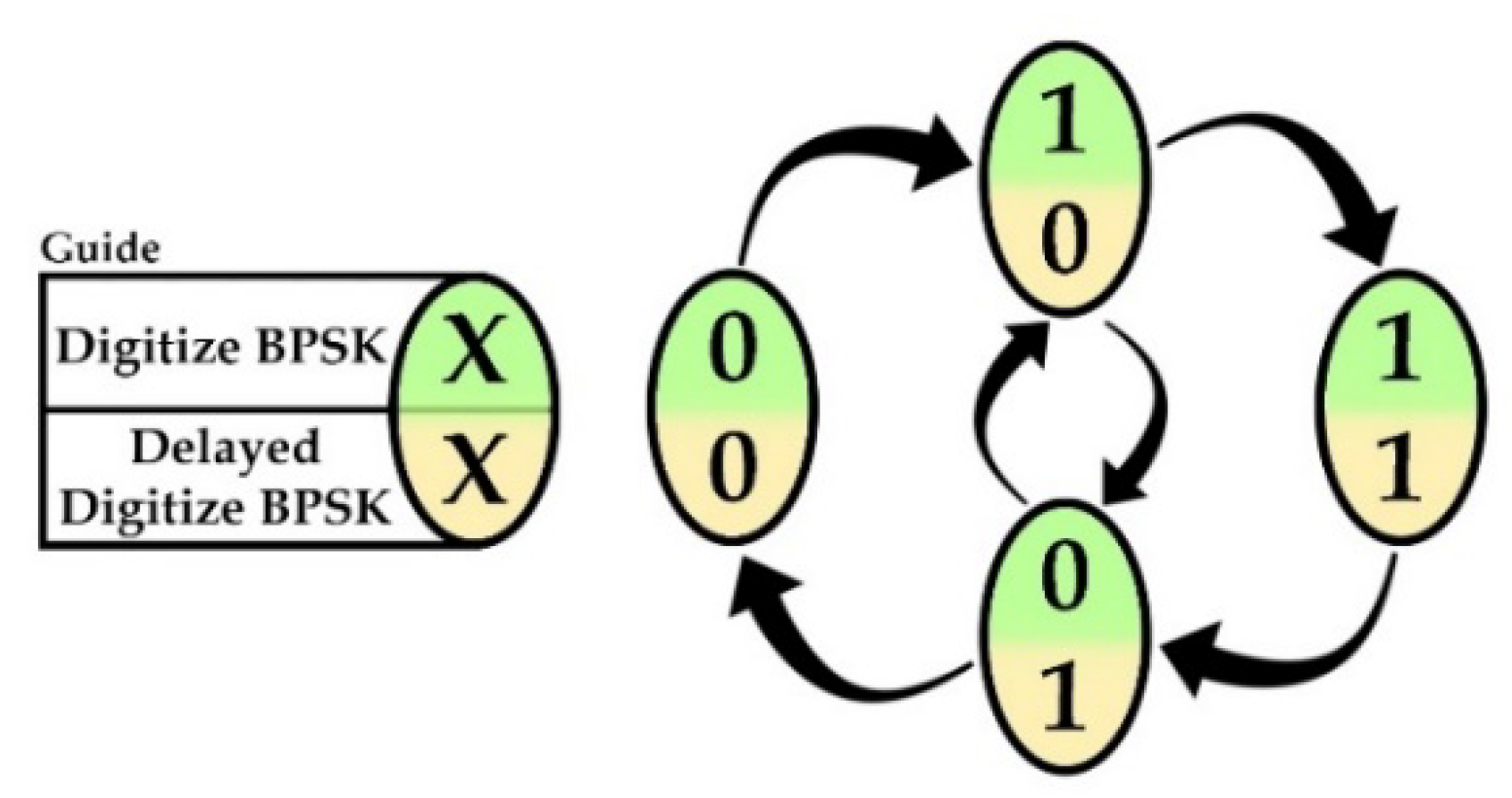

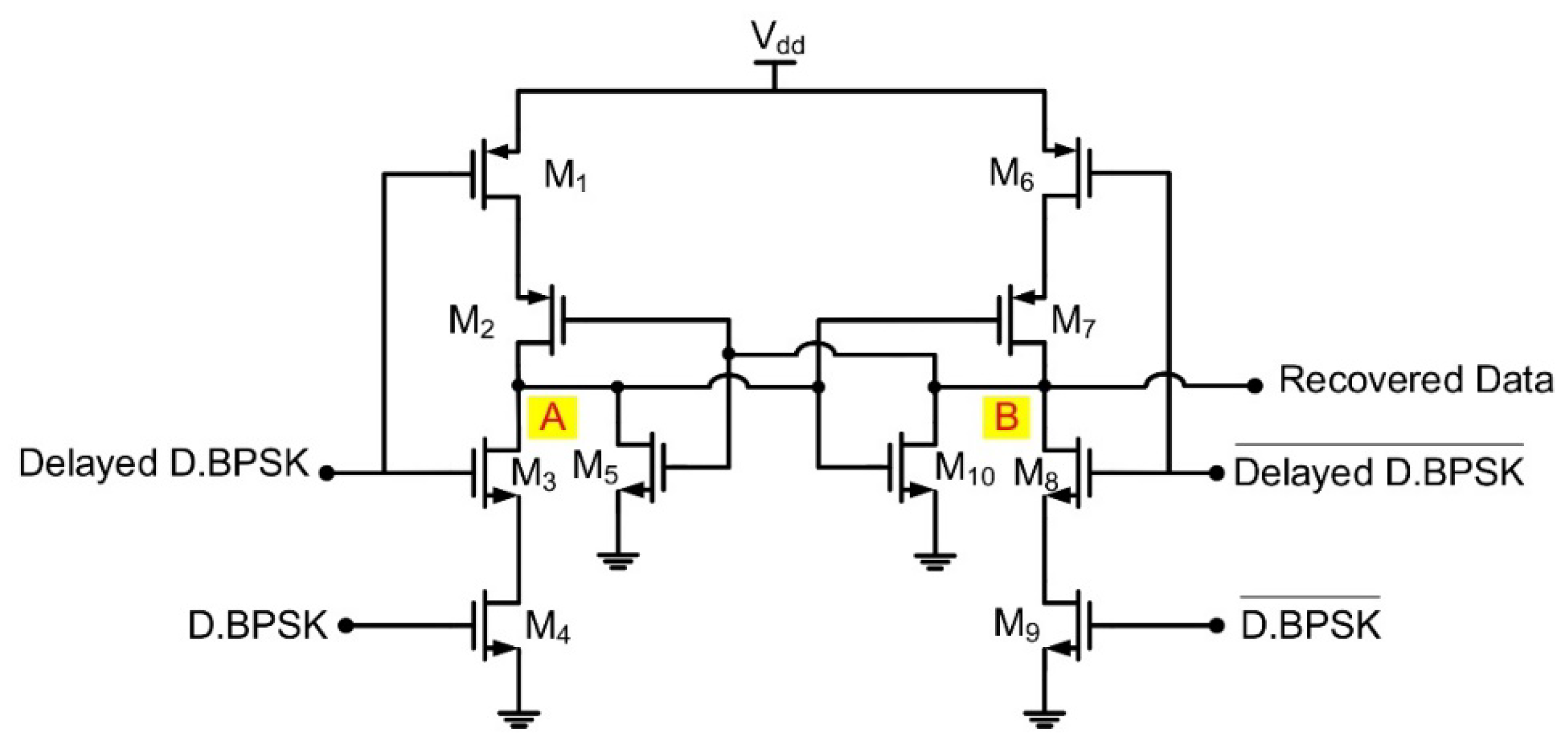

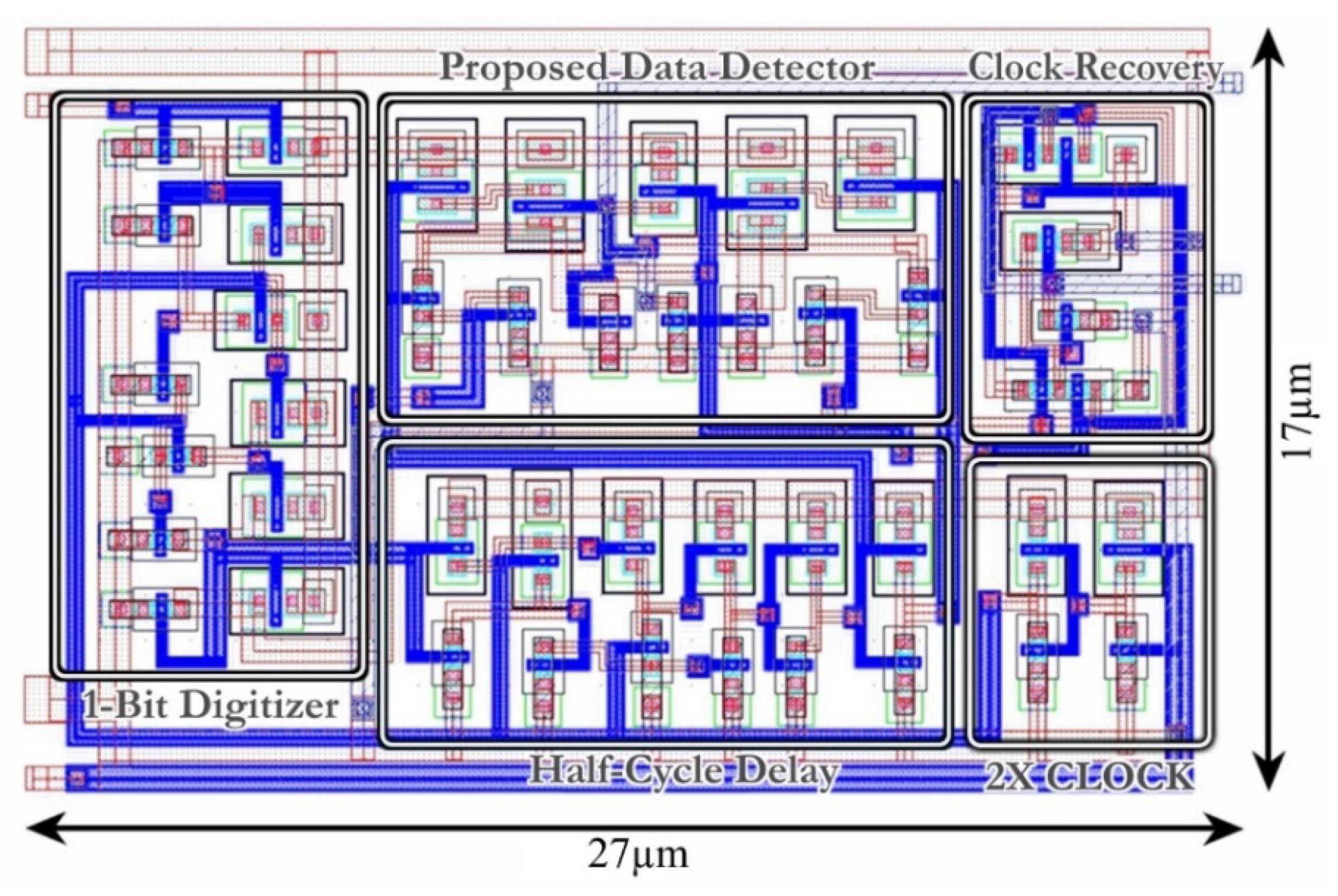

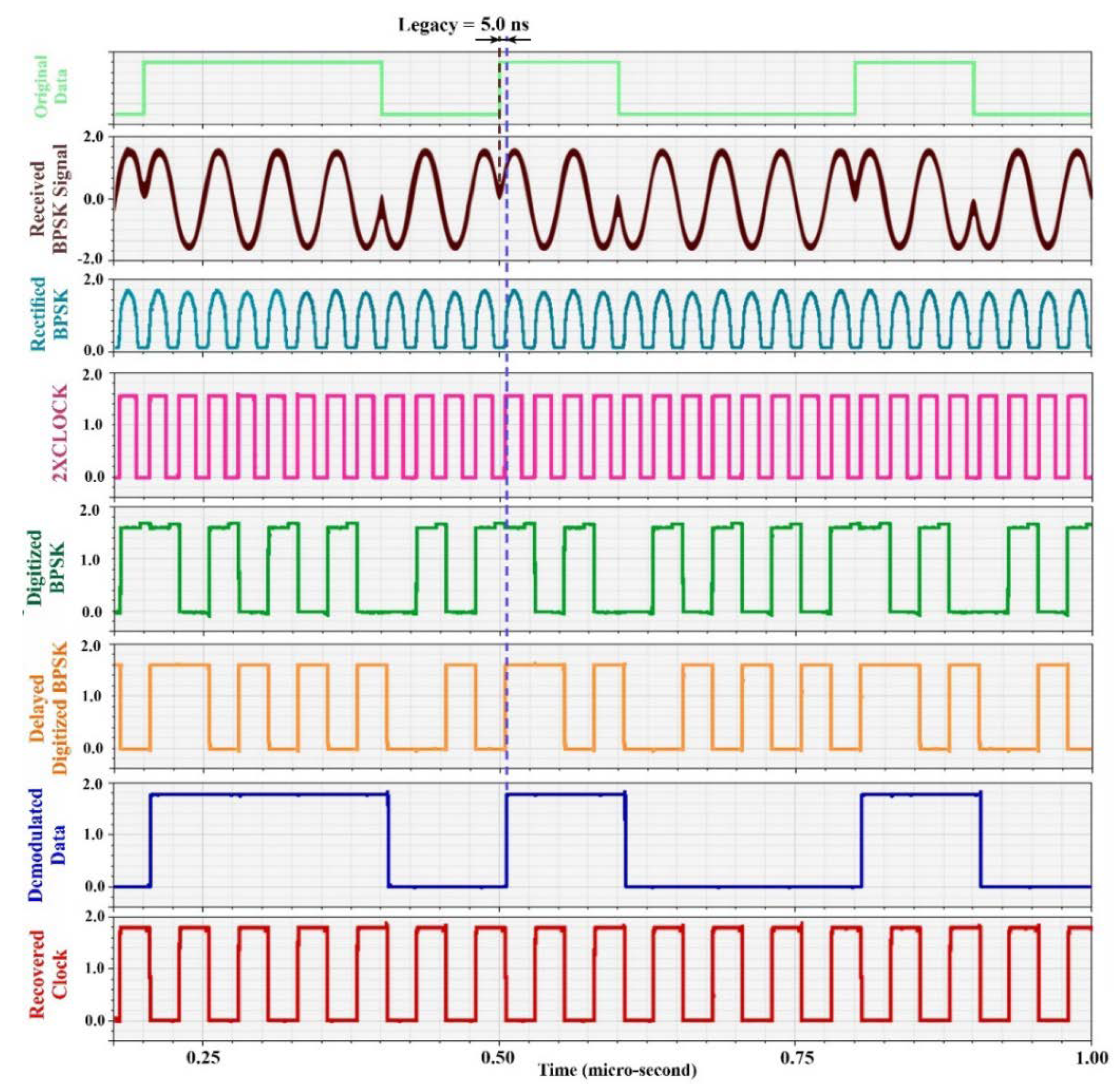

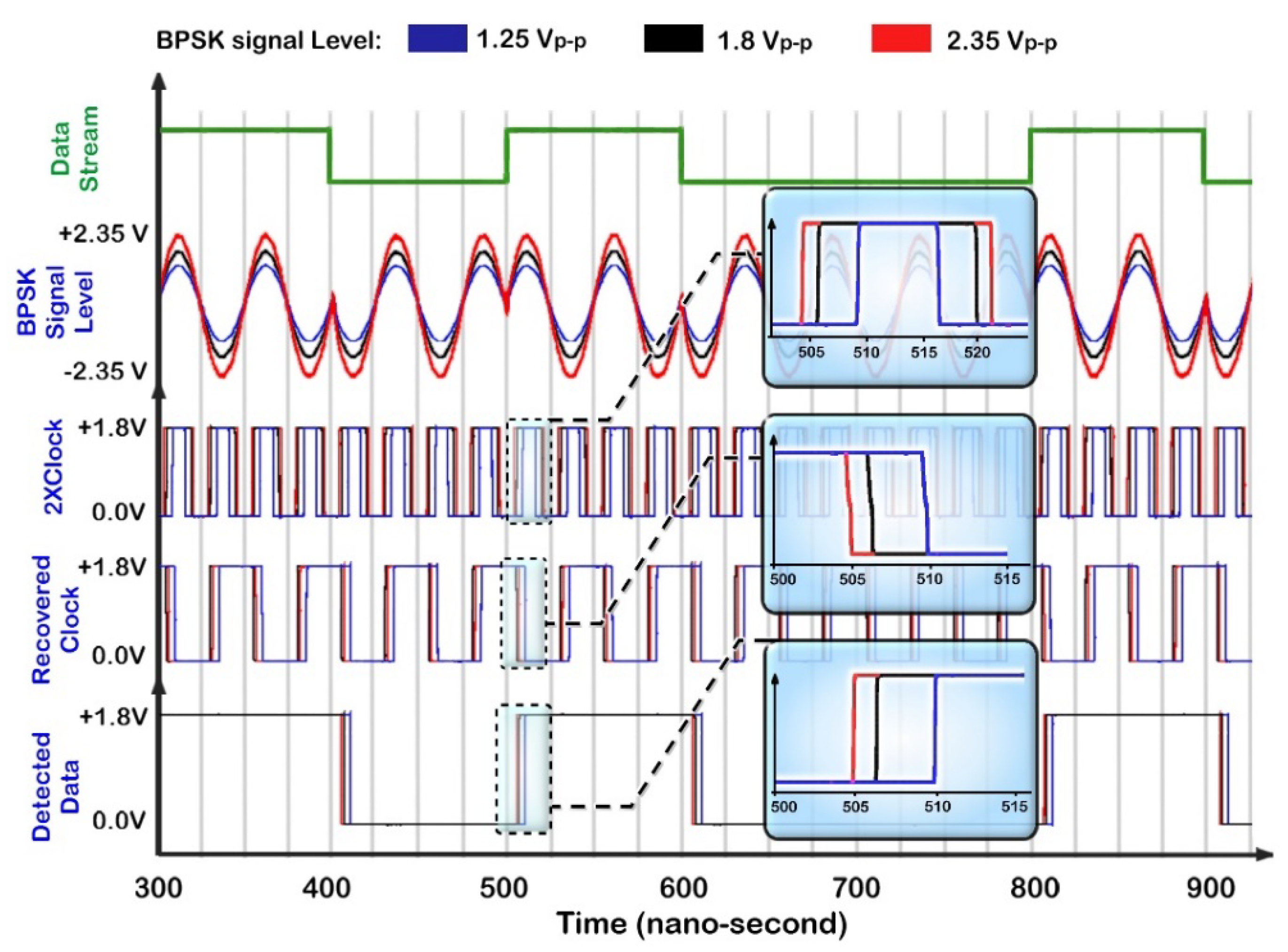

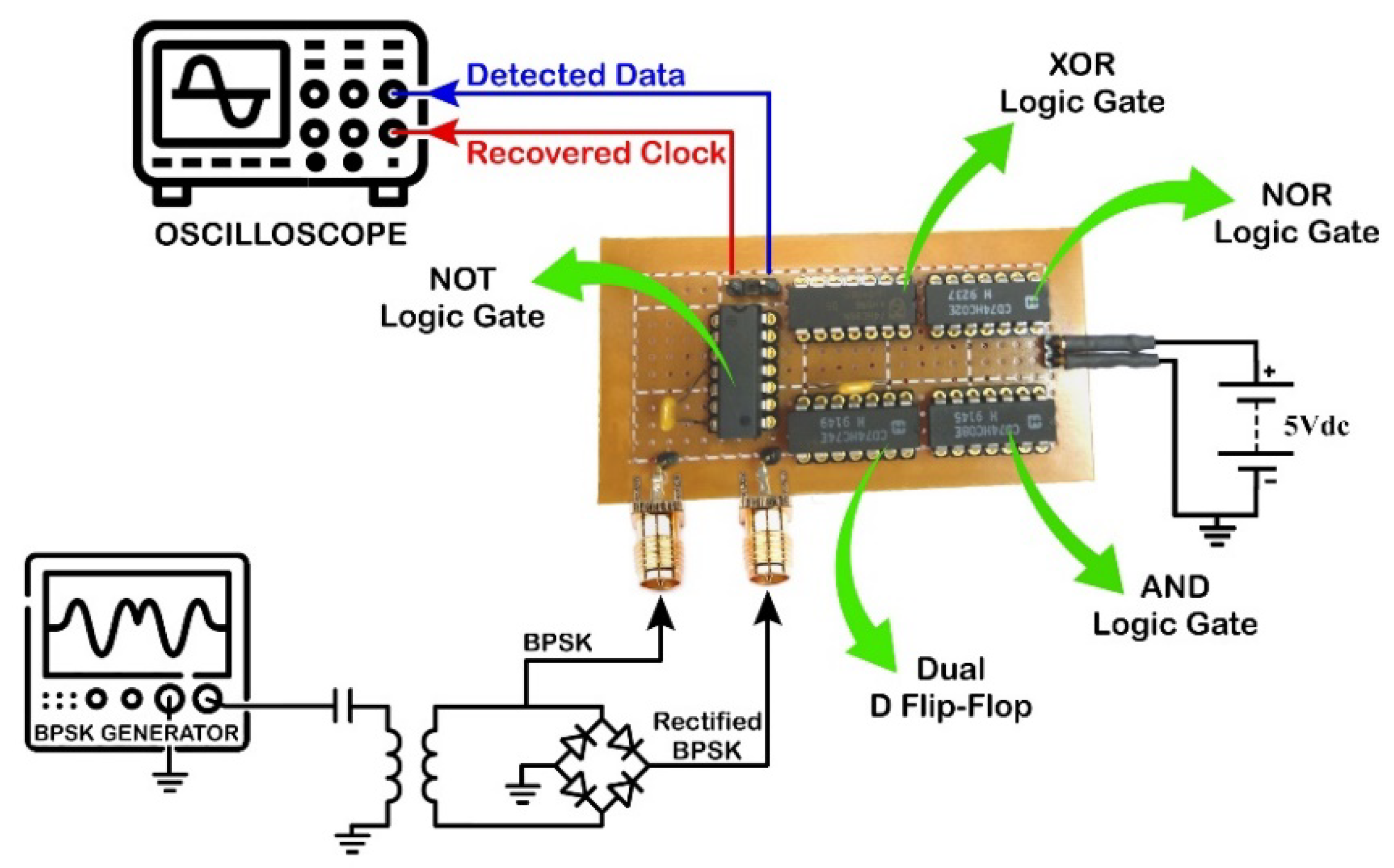

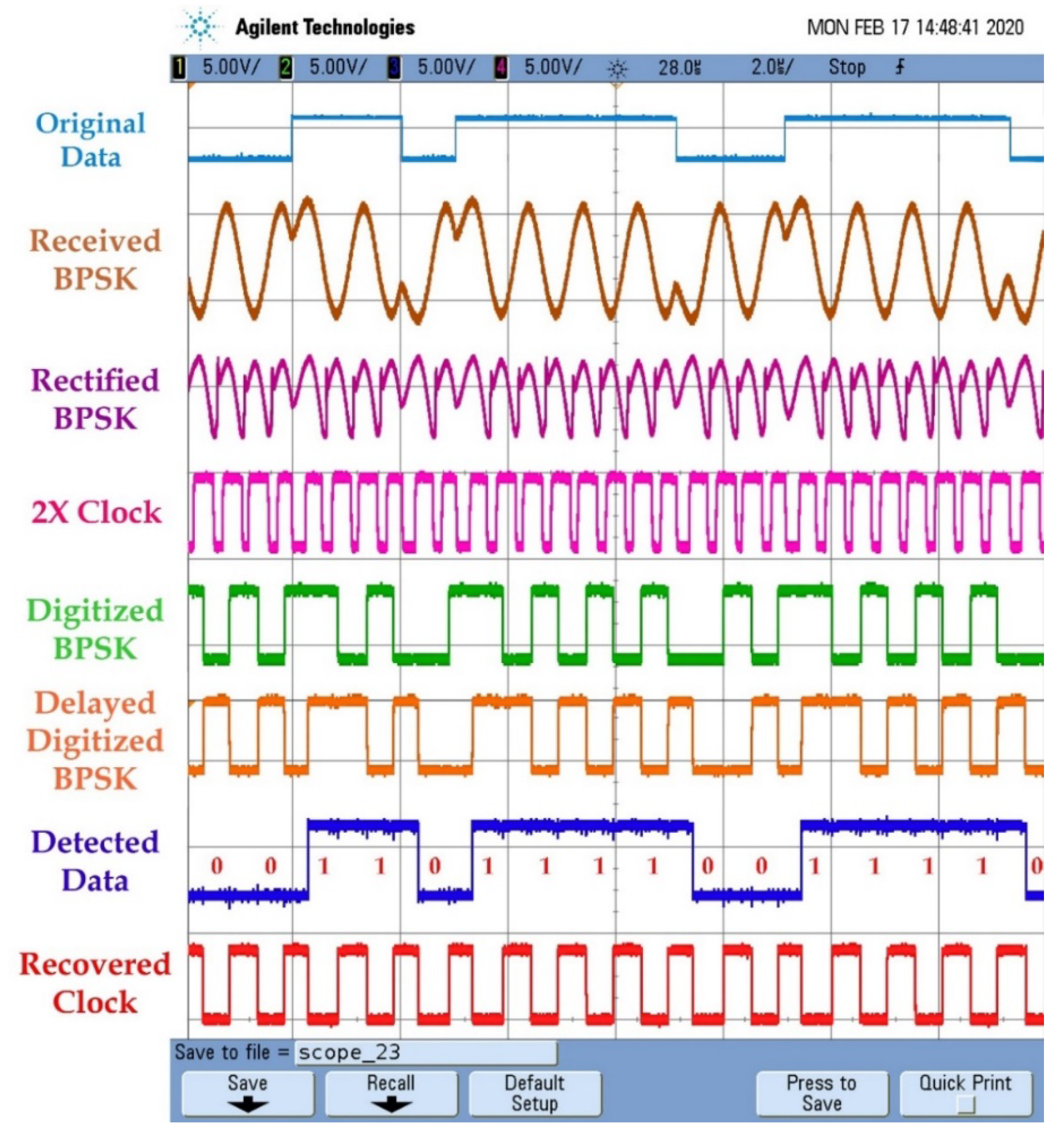

2. Proposed BPSK Demodulator and Clock Recovery Circuit

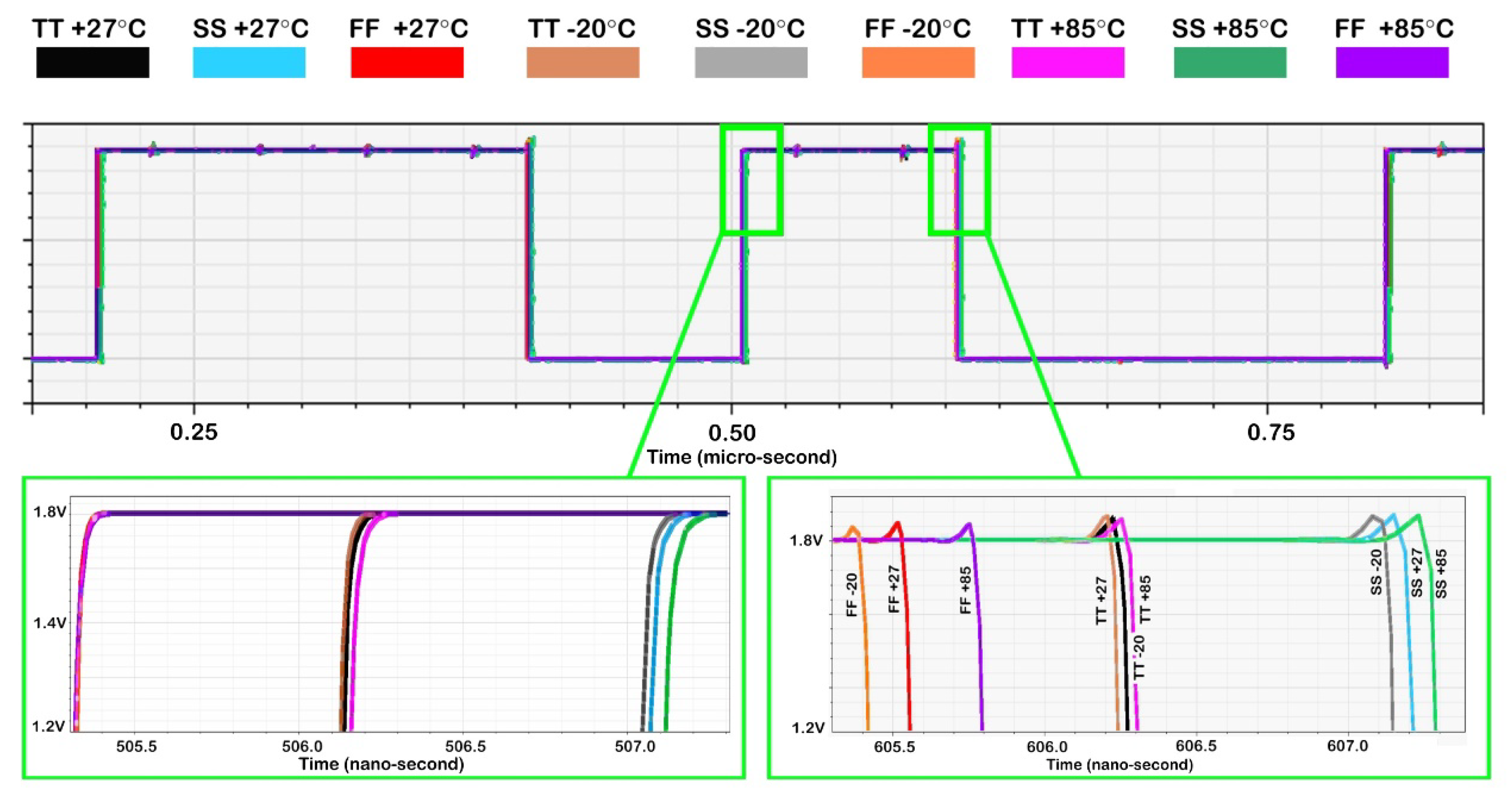

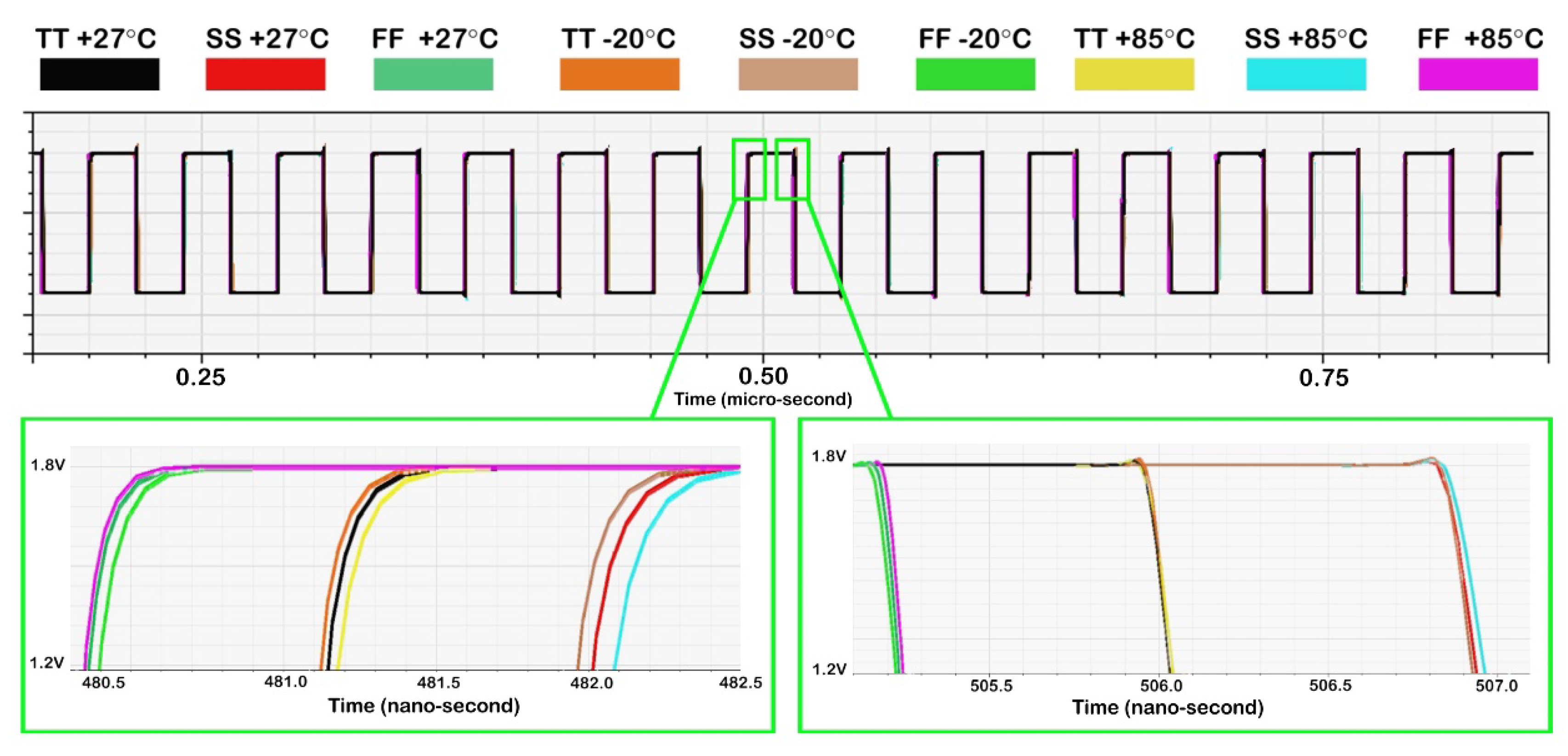

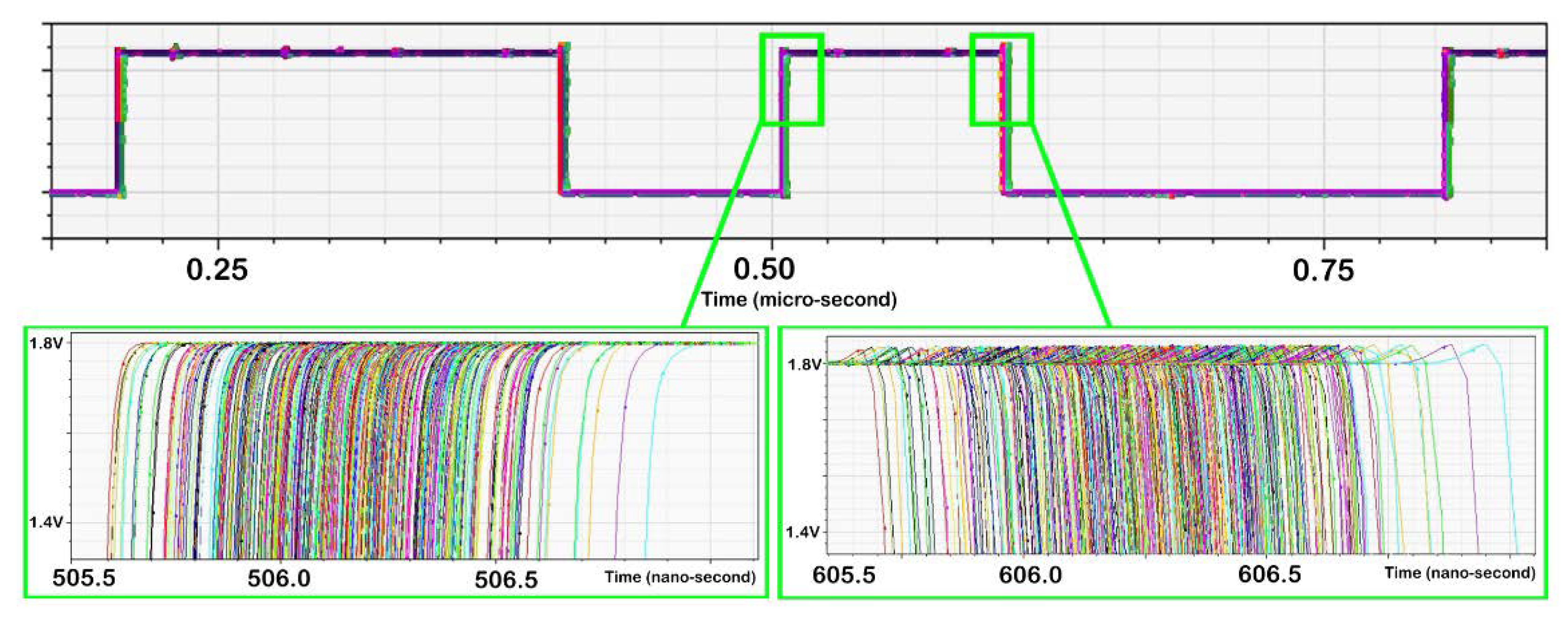

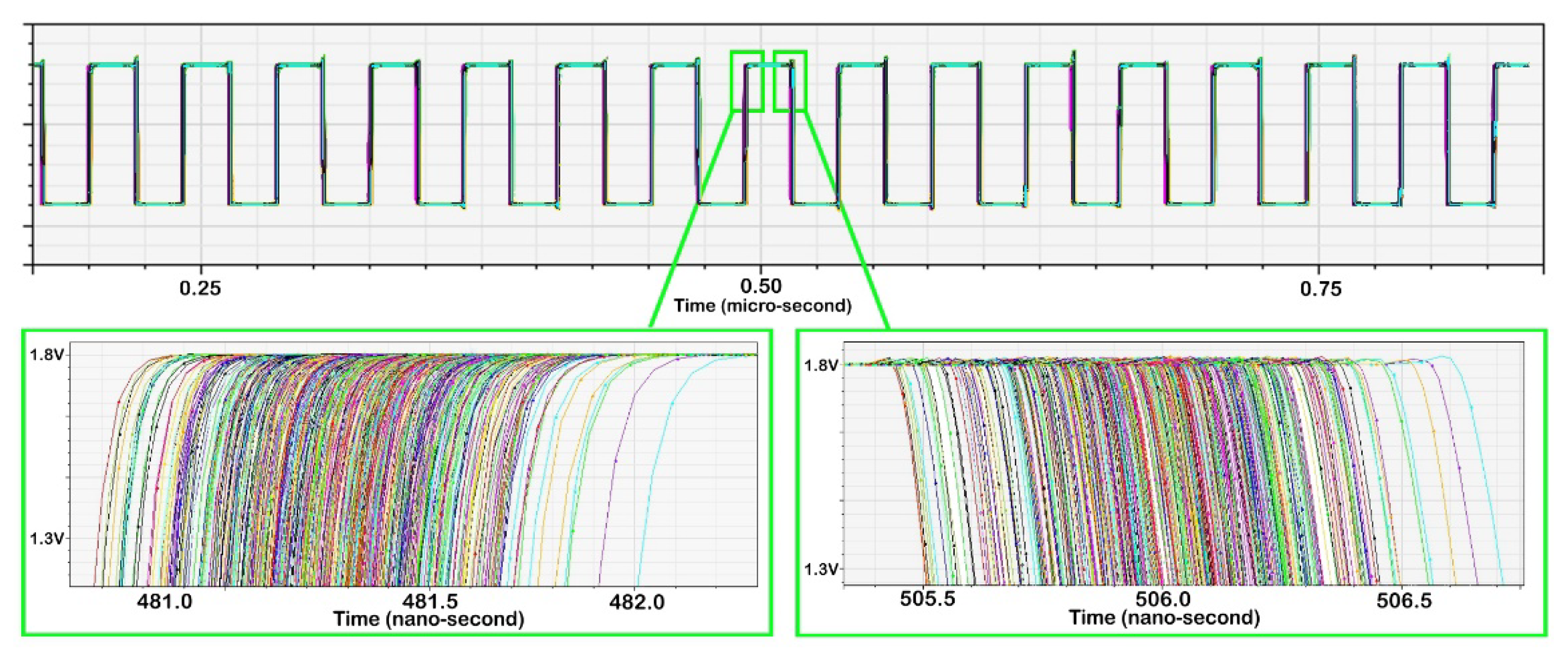

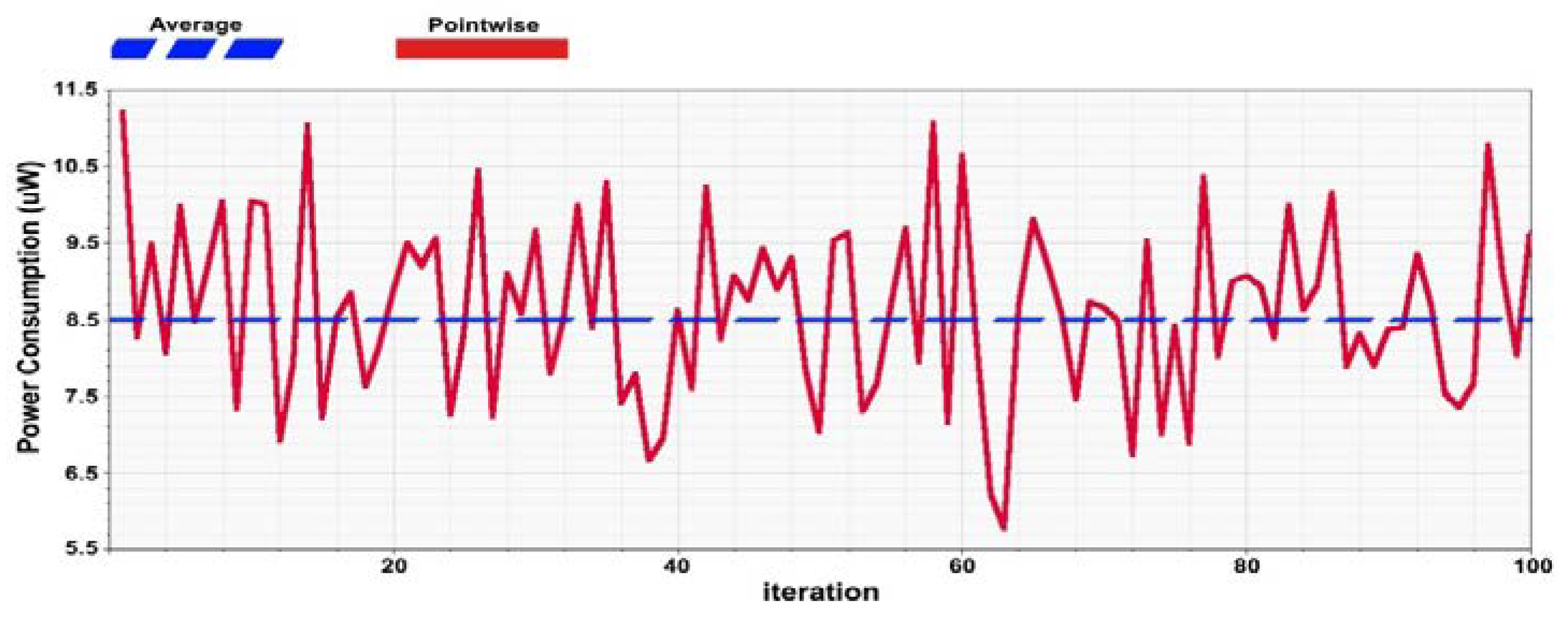

3. Post-Layout Simulation and Experimental Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Asgarian, F.; Sodagar, A.M. Wireless Telemetry for Implantable Biomedical Microsystems. In Biomedical Engineering, Trends in Electronics, Communications and Software; Laskovski, A.N., Ed.; InTech Press: Rijeka, Croatia, 2011; pp. 21–44. [Google Scholar]

- Gati, E.; Kokosis, S.; Patsourakis, N.; Manias, S. Comparison of Series Compensation Topologies for Inductive Chargers of Biomedical Implantable Devices. Electronics 2020, 9, 8. [Google Scholar] [CrossRef]

- Bazaka, K.; Jacob, M.V. Implantable Devices: Issues and Challenges. Electronics 2013, 2, 1–34. [Google Scholar] [CrossRef]

- Zabihian, A.R.; Maghami, M.H.; Sodagar, A.M. Implantable Biomedical Devices. In Biomedical Engineering, Technical Applications in Medicine; Hudak, R., Penhaker, M., Majernik, J., Eds.; InTech Press: Rijeka, Croatia, 2012; pp. 157–190. [Google Scholar]

- Ghovanloo, M.; Najafi, K. A wideband frequency-shift keying wireless link for inductively powered biomedical implants. IEEE Trans. Circuit Syst. I 2004, 51, 2374–2383. [Google Scholar] [CrossRef]

- Lee, B.; Ghovanloo, M. An overview of data telemetry in inductively powered implantable biomedical devices. IEEE Commun. Mag. 2019, 57, 74–80. [Google Scholar] [CrossRef]

- Asgarian, F.; Sodagar, A.M. A Carrier-Frequency-Independent BPSK Demodulator with 100% Data-Rate-To-Carrier-Frequency Ratio. In Proceedings of the 2010 IEEE Biomedical Circuits and Systems Conference, Paphos, Cyprus, 3–5 November 2010; pp. 29–32. [Google Scholar]

- Hu, Y.; Sawan, M. A fully-integrated low power BPSK demodulator for implantable medical devices. IEEE Trans. Circuit Syst. I 2005, 52, 2552–2562. [Google Scholar]

- Luo, Z.; Sonkusale, S. A novel BPSK demodulator for biological implants. IEEE Trans. Circuit Syst. I 2008, 55, 1478–1484. [Google Scholar]

- Asgarian, F.; Sodagar, A.M. A low-power noncoherent BPSK demodulator and clock recovery circuit for high-data-rate biomedical applications. In Proceedings of the 31st International Conference of the IEEE/EMBS, Minneapolis, MN, USA, 3–6 September 2009; pp. 4840–4843. [Google Scholar]

- Nabovati, G.; Ghafar-Zadeh, E.; Awwad, F.; Sawan, M. Fully digital low-power self-calibrating BPSK demodulator for implantable biosensors. In Proceedings of the IEEE 55th International Midwest Symposium on Circuits and Systems, Boise, ID, USA, 5–8 August 2012; pp. 354–357. [Google Scholar]

- Wilkerson, B.P.; Jang, J.-K. A low power BPSK demodulator for wirelessly implantable biomedical devices. In Proceedings of the International Symposium on Circuits and Systems, Beijing, China, 19–23 May 2013; pp. 626–629. [Google Scholar]

- Liu, H.-H.; Wu, Z.-H.; Li, B.; Zhao, M.-J. A fully digital low-power wide-speed-range BPSK demodulator. Int. J. Electron. Lett. 2014, 2, 158–165. [Google Scholar] [CrossRef]

- Gong, C.-S.A.; Shiue, M.-T.; Yao, K.-W.; Chen, T.-Y. Low-power and area-efficient PSK demodulator for wirelessly powered implantable command receivers. Electron. Lett. 2008, 44, 841–842. [Google Scholar]

- Karimi, M.; Maghami, M.H.; Faizollah, M.; Sodagar, A.M. A noncoherent low-power high-data-rate BPSK demodulator and clock recovery circuit for implantable biomedical devices. In Proceedings of the IEEE Biomedical Circuits and Systems Conference (BioCAS), Lausanne, Switzerland, 22–24 October 2014; pp. 372–375. [Google Scholar]

- Beheshti, B.; Jalali, M. A low-power noncoherent BPSK demodulator for implantable medical devices. In Proceedings of the IEEE International Conference on Electronics Design, Systems and Applications (ICEDSA), Kuala Lumpur, Malaysia, 5–6 November 2012; pp. 203–206. [Google Scholar]

- Eslampanah Sendi, M.S.; Nasiri, S.; Mousavi, N.; Sharifkhani, M.; Sodagar, A.M. A 3-d inductive powering approach dedicated to implantable/wearable biomedical microsystems. In Proceedings of the IEEE Biomedical Circuits and Systems Conference (BioCAS), Lausanne, Switzerland, 22–24 October 2014. [Google Scholar]

- Sonkusale, S.; Luo, Z. A complete data and power telemetry system utilizing BPSK and LSK signaling for biomedical implants. In Proceedings of the International Conference of the IEEE Engineering in Medicine and Biology Society, Vancouver, BC, Canada, 20–25 August 2008; pp. 3216–3219. [Google Scholar]

- Cheng, C.-H.; Tsai, P.-Y.; Yang, T.-Y.; Cheng, W.-H.; Yen, T.-Y.; Luo, Z.; Qian, X.-H.; Chen, Z.-X.; Lin, T.-H.; Chen, W.-H.; et al. A fully integrated 16-channel closed-loop neural-prosthetic CMOS SoC with wireless power and bidirectional data telemetry for real-time efficient human epileptic seizure control. IEEE J. Solid-State Circuit 2018, 53, 3314–3326. [Google Scholar] [CrossRef]

- Prabhu Deva Kumar, S.V.S.; Nayini, L.; Ronald, E. Implementation of low power D-Flip Flop using 45nm Technology. Int. J. Recent Sci. Res. 2017, 8, 17729–17732. [Google Scholar]

- Radhakrishnan, D. Low-voltage low-power CMOS full adder. IEE Proc. Circuits Devices Syst. 2001, 148, 19–24. [Google Scholar] [CrossRef]

- Asgarian, F.; Sodagar, A.M. A high-data-rate low-power BPSK demodulator and clock recovery circuit for implantable biomedical devices. In Proceedings of the 4th International IEEE/EMBS Conference on Neural Engineering, Antalya, Turkey, 29 April–2 May 2009; pp. 407–410. [Google Scholar]

- Javid, A.; Vahedian, H.; Sodagar, A.M.; Mofrad, M.E. Low-power, high data-rate, BPSK demodulator for implantable biomedical applications. In Proceedings of the IEEE ICECS, Marseille, France, 7–10 December 2014; pp. 415–418. [Google Scholar]

- Hosseinnejad, M.; Erfanian, A. A VCO-free low-power fully digital BPSK demodulator for implantable biomedical microsystems. In Proceedings of the 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Batumi, GA, USA, 5–8 December 2017; pp. 474–477. [Google Scholar]

| Device Name | W/L |

|---|---|

| M1,2,6,7 | 0.88 µm/0.18 µm |

| M3,4,8,9 | 0.22 µm/0.18 µm |

| M5,10 | 0.44 µm/0.18 µm |

| Process Corner/Temperature | TT/27 °C | SS/85 °C | FF/−40 °C |

| Power Consumption * (1.8 V Vdd) | 8.7 µW | 5.9 µW | 13.2 µW |

| [7] | [8] | [10] | [11] | [14] | [15] | [16] * | [22] | [23] | [24] | This Work | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Frequency (MHz) | 10 | 13.56 | 10 | 16 | 4 | 10 | 1 | 8 | 10 | 10 | 2 | 10 | 20 |

| Data rate (Mbps) | 10 | 1.12 | 10 | 16 | 0.8 | 10 | 1 | 8 | 10 | 10 | 2 | 10 | 20 |

| DRCF (%) | 100 | 8.25 | 100 | 100 | 20 | 100 | 100 | 100 | 100 | 100 | 100 | 100 | 100 |

| Chip Area (µm2) | - | 19 × 104 | - | - | 4300 | 3500 | - | - | - | 1120 | 459 | 459 | 459 |

| Power Consumption (µW) | 119 | 610 | 232 | 27 | 59 | 77.9 | 88.2 | 148 | 27.2 | 14 | 5.6 | 6.7 | 8.5 |

| FOM × 10 −3) | 8.4 | 0.14 | 4.3 | 37 | 3.4 | 12.8 | 11.3 | 6.7 | 36.7 | 71.4 | 160 | 144 | 113 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ghazi, M.; Maghami, M.H.; Amiri, P.; Hamedi-Hagh, S. An Ultra-Low-Power Area-Efficient Non-Coherent Binary Phase-Shift Keying Demodulator for Implantable Biomedical Microsystems. Electronics 2020, 9, 1123. https://doi.org/10.3390/electronics9071123

Ghazi M, Maghami MH, Amiri P, Hamedi-Hagh S. An Ultra-Low-Power Area-Efficient Non-Coherent Binary Phase-Shift Keying Demodulator for Implantable Biomedical Microsystems. Electronics. 2020; 9(7):1123. https://doi.org/10.3390/electronics9071123

Chicago/Turabian StyleGhazi, Milad, Mohammad Hossein Maghami, Parviz Amiri, and Sotoudeh Hamedi-Hagh. 2020. "An Ultra-Low-Power Area-Efficient Non-Coherent Binary Phase-Shift Keying Demodulator for Implantable Biomedical Microsystems" Electronics 9, no. 7: 1123. https://doi.org/10.3390/electronics9071123

APA StyleGhazi, M., Maghami, M. H., Amiri, P., & Hamedi-Hagh, S. (2020). An Ultra-Low-Power Area-Efficient Non-Coherent Binary Phase-Shift Keying Demodulator for Implantable Biomedical Microsystems. Electronics, 9(7), 1123. https://doi.org/10.3390/electronics9071123