Area-Efficient Differential Fault Tolerance Encoding for Finite State Machines

Abstract

1. Introduction

2. Background

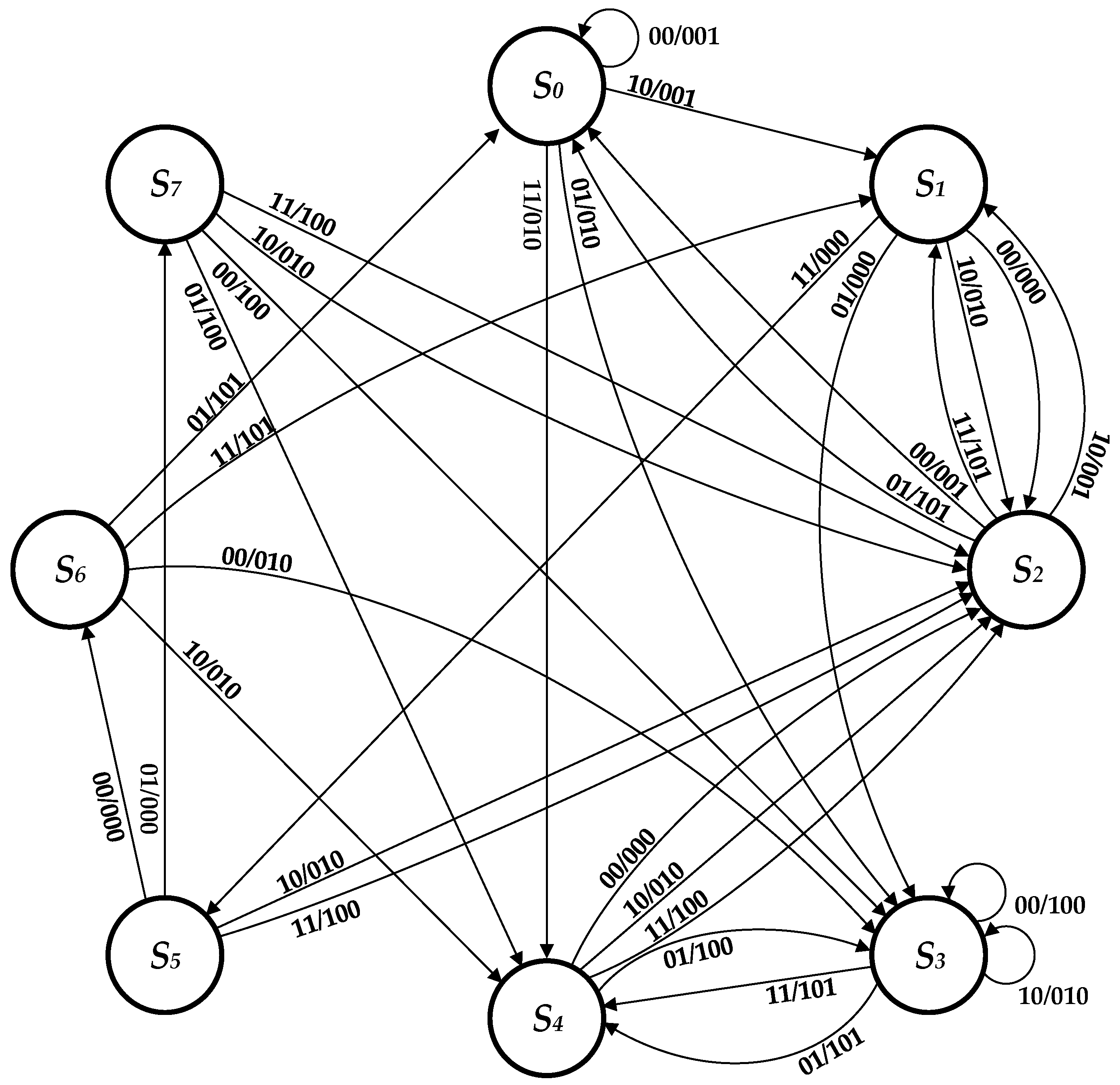

2.1. Finite State Machine

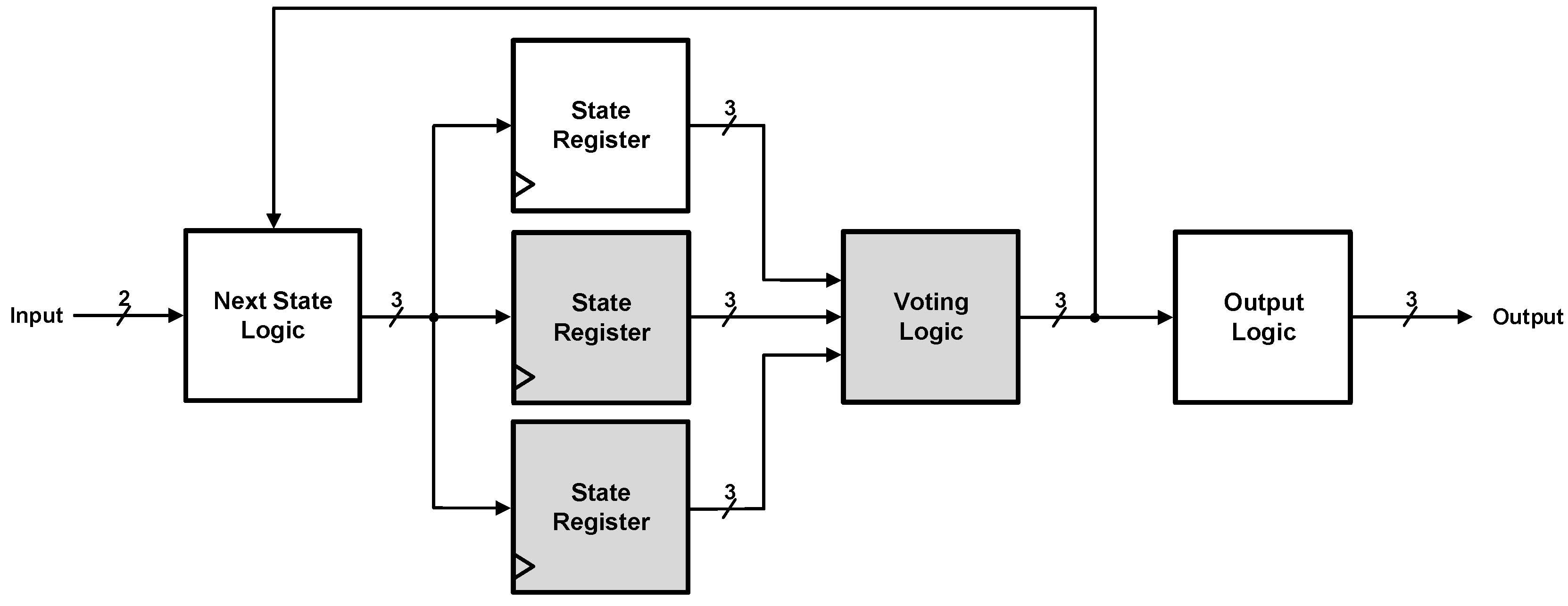

2.2. Fault-Tolerant Techniques

3. Proposed Method

3.1. State Classification

- Count the frequency of each state using an ordinary FSM with random inputs;

- List the states based on their descending order of frequency;

- Extract a state from the top of the frequency list and include it in the critical state Sc;

- Repeat step (3) until the accumulation of frequency exceeds the coverage C;

- Include the remaining states in the non-critical state SNC.

3.2. State Encoding

3.3. FSM Construction

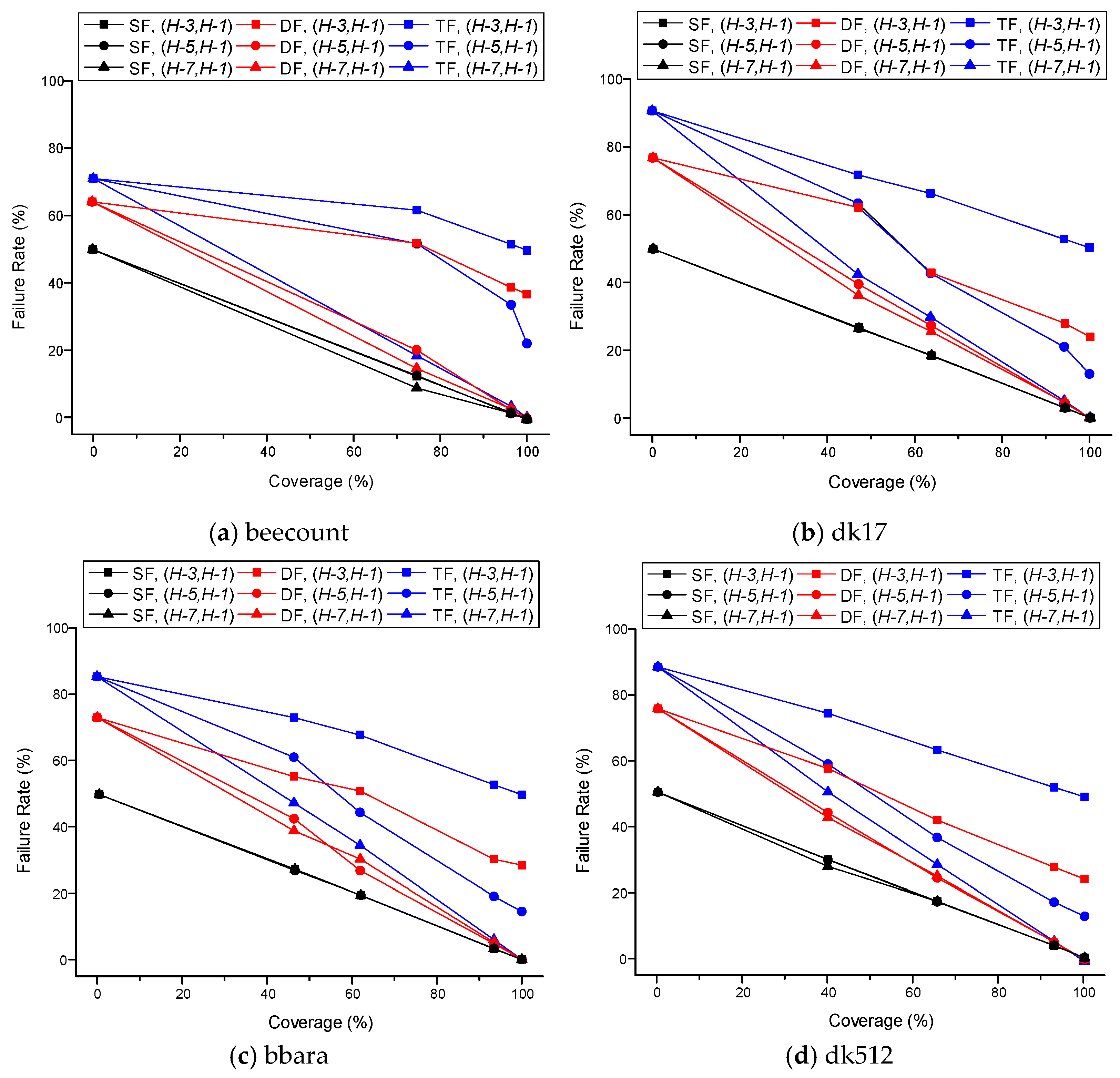

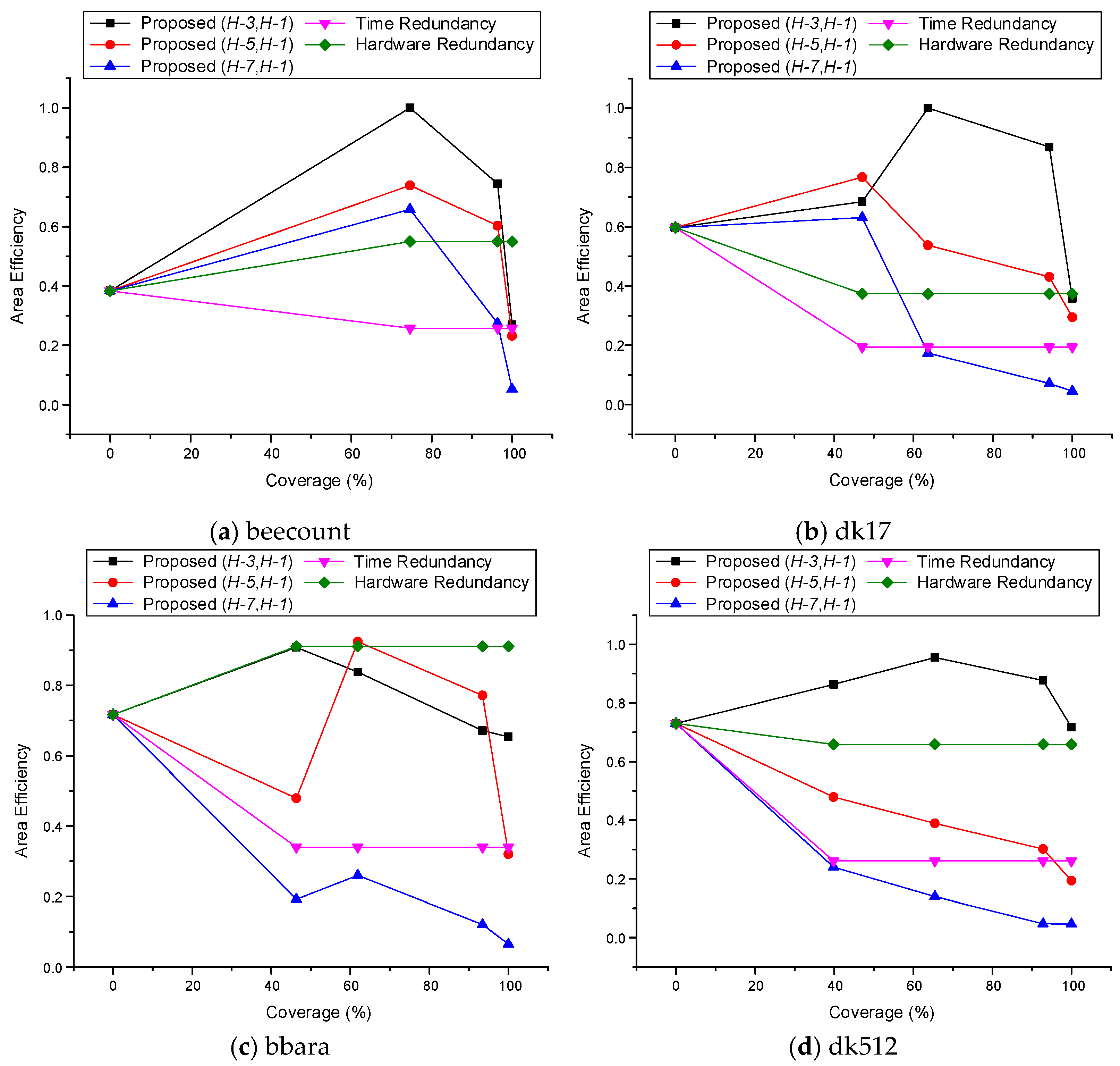

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Mealy, G.H. A method for synthesizing sequential circuits. Bell Syst. Tech. J. 1955, 34, 1045–1079. [Google Scholar] [CrossRef]

- Moore, E.F. Gedanken-experiments on sequential machines. Autom. Stud. 1956, 34, 129–153. [Google Scholar]

- Xu, J.; Dong, F.; Tian, P.; Tang, F.; Yang, Q. Design and implementation of HL-2A host centralized control system FSM model based on EPICS. IEEE Trans. Plasma Sci. 2018, 46, 1234–1238. [Google Scholar] [CrossRef]

- Sharma, C.; Chauhan, D.K. High performance low power AHB DMA controller with FSM decomposition technique. In Proceedings of the 2017 IEEE International Conference on Power, Control, Signals and Instrumentation Engineering (ICPCSI), Chennai, India, 21–22 September 2017. [Google Scholar]

- Chu, S.I.; Hsieh, C.E.; Huang, Y.J. Design of FSM-based function with reduced number of states in integral stochastic computing. IEEE Trans. Very Large Scale Integr. (Vlsi) Syst. 2019, 27, 1475–1479. [Google Scholar] [CrossRef]

- Rathor, V.S.; Garg, B.; Sharma, G.K. An energy-efficient trusted fsm design technique to thwart fault injection and trojan attacks. In Proceedings of the 2018 31st International Conference on VLSI Design and 2018 17th International Conference on Embedded Systems (VLSID), Maharashtra, India, 6–10 January 2018. [Google Scholar]

- Nahiyan, A.; Farahmandi, F.; Mishra, P.; Forte, D.; Tehranipoor, M. Security-aware FSM design flow for identifying and mitigating vulnerabilities to fault attacks. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2018, 38, 1003–1016. [Google Scholar] [CrossRef]

- Hashimoto, M.; Liao, W. Soft Error and Its Countermeasures in Terrestrial Environment. In Proceedings of the 2020 25th Asia and South Pacific Design Automation Conference (ASP-DAC), Beijing, China, 13–16 January 2020. [Google Scholar]

- Raji, M.; Sabet, M.A.; Ghavami, B. Soft error reliability improvement of digital circuits by exploiting a fast gate sizing scheme. IEEE Access 2019, 7, 66485–66495. [Google Scholar] [CrossRef]

- Gaillard, R. Single event effects: Mechanisms and classification. In Soft Errors in Modern Electronic Systems; Springer: Berlin/Heidelberg, Germany, 2011; pp. 27–54. [Google Scholar]

- Lei, L.; Yinghui, L.; Hongwei, Z.; Xuesong, Z.; Qingkui, Y.; Min, T. Single Event Effect Detection and Simulation Analysis for an ASIC. In Proceedings of the 2019 2nd International Conference on Information Systems and Computer Aided Education (ICISCAE), Dalian, China, 6–8 July 2019. [Google Scholar]

- Hiemstra, D.M.; Kirischian, V.; Brelski, J. Single event upset characterization of the Kintex UltraScale field programmable gate array using proton irradiation. In Proceedings of the 2016 IEEE Radiation Effects Data Workshop (REDW), Portland, OR, USA, 11–15 July 2016. [Google Scholar]

- Ciani, L.; Catelani, M. A fault tolerant architecture to avoid the effects of Single Event Upset (SEU) in avionics applications. Measurement 2014, 54, 256–263. [Google Scholar] [CrossRef]

- Evans, A.; Glorieux, M.; Alexandrescu, D.; Polo, C.B.; Ferlet-Cavrois, V. Single event multiple transient (SEMT) measurements in 65 nm bulk technology. In Proceedings of the 2016 16th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Bremen, Germany, 19–23 September 2016. [Google Scholar]

- Hao, P.; Chen, S.; Wu, Z.; Chi, Y. On-chip relative single-event transient/single-event upset susceptibility test circuit for integrated circuits working in real time. IEEE Trans. Nucl. Sci. 2017, 65, 376–381. [Google Scholar] [CrossRef]

- Nahiyan, A.; Xiao, K.; Yang, K.; Jin, Y.; Forte, D.; Tehranipoor, M. AVFSM: A framework for identifying and mitigating vulnerabilities in FSMs. In Proceedings of the the 53rd Annual Design Automation Conference, Austin, TX, USA, 5–9 June 2016. [Google Scholar]

- Li, S.; Choi, K. A high performance low power implementation scheme for FSM. In Proceedings of the 2014 International SoC Design Conference (ISOCC), Jeju, Korea, 3–6 November 2014. [Google Scholar]

- El-Maleh, A.H.; Al-Qahtani, A.S. A finite state machine based fault tolerance technique for sequential circuits. Microelectron. Reliab. 2014, 54, 654–661. [Google Scholar] [CrossRef]

- Madhumithaa, S.P.; Aravind, S.; Ch, R.P. A Diagnosis Pattern Generation Procedure to Distinguish Between Stuck-at and Bridging Faults in Digital Circuits. In Proceedings of the 2019 International Conference on Intelligent Computing and Control Systems (ICCS), Madurai, India, 15–17 May 2019. [Google Scholar]

- Zhang, J.; Li, Y.; Han, T.; Li, J. Radiation Hardened Design Based on TMR_5DFF for ASIC. In Proceedings of the 2019 IEEE 5th International Conference on Computer and Communications (ICCC), Chengdu, China, 6–9 December 2019. [Google Scholar]

- Mallavarapu, P.; Upadhyay, H.N.; Rajkumar, G.; Elamaran, V. Fault-tolerant digital filters on FPGA using hardware redundancy techniques. In Proceedings of the 2017 International conference of Electronics, Communication and Aerospace Technology (ICECA), Coimbatore, India, 20–22 April 2017. [Google Scholar]

- Hamilton, N.; Graham, S.; Carbino, T.; Petrosky, J.; Betances, A. Adaptive-Hybrid Redundancy with Error Injection. Electronics 2019, 8, 1266. [Google Scholar] [CrossRef]

- Alvarez, I.; Proenza, J.; Barranco, M.; Knezic, M. Towards a time redundancy mechanism for critical frames in Time-Sensitive Networking. In Proceedings of the 2017 22nd IEEE International Conference on Emerging Technologies and Factory Automation (ETFA), Limassol, Cyprus, 12–15 September 2017. [Google Scholar]

- Sooraj, S.; Bhakthavatchalu, R. Hamming 3 algorithm for improving the reliability of SRAM based FPGAs. In Proceedings of the 2017 International Conference on Communication and Signal Processing (ICCSP), Tamilnadu, India, 6–8 April 2017. [Google Scholar]

- Eslami, M.; Ghavami, B.; Raji, M.; Mahani, A. A survey on fault injection methods of digital integrated circuits. Integration 2020, 71, 154–163. [Google Scholar] [CrossRef]

- Choi, S.; Park, J.; Yoo, H. Area-Efficient Fault Tolerant Design for Finite State Machines. In Proceedings of the 2020 International Conference on Electronics, Information, and Communication (ICEIC), Barcelona, Spain, 19–22 January 2020. [Google Scholar]

- Fabero, J.C.; Mecha, H.; Franco, F.J.; Clemente, J.A.; Korkian, G.; Rey, S.; Velazco, R. Single Event Upsets under 14-MeV Neutrons in a 28-nm SRAM-based FPGA in Static Mode. IEEE Trans. Nucl. Sci. 2020. [Google Scholar] [CrossRef]

- Wu, K.; Pahlevanzadeh, H.; Liu, P.; Yu, Q. A new fault injection method for evaluation of combining SEU and SET effects on circuit reliability. In Proceedings of the 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, Australia, 1–5 June 2014. [Google Scholar]

| State | Next State | Outputs | |||||||

|---|---|---|---|---|---|---|---|---|---|

| I = 00 | I = 01 | I = 10 | I = 11 | I = 00 | I = 01 | I = 10 | I = 11 | ||

| S0 | (000) | S0 | S3 | S1 | S4 | 001 | 010 | 001 | 010 |

| S1 | (001) | S2 | S3 | S2 | S5 | 000 | 000 | 010 | 000 |

| S2 | (010) | S0 | S0 | S1 | S1 | 001 | 101 | 001 | 101 |

| S3 | (011) | S3 | S4 | S3 | S4 | 100 | 101 | 010 | 101 |

| S4 | (100) | S4 | S3 | S4 | S4 | 000 | 100 | 010 | 100 |

| S5 | (101) | S6 | S7 | S2 | S2 | 000 | 000 | 010 | 100 |

| S6 | (110) | S3 | S0 | S4 | S1 | 010 | 101 | 010 | 101 |

| S7 | (111) | S3 | S4 | S2 | S2 | 100 | 100 | 010 | 100 |

| State | H-1 | H-2 | H-3 | |

|---|---|---|---|---|

| S0 | (000) | 000 | 0000 | 000000 |

| S1 | (001) | 001 | 1001 | 001011 |

| S2 | (010) | 010 | 1010 | 010110 |

| S3 | (011) | 011 | 0011 | 011101 |

| S4 | (100) | 100 | 1100 | 100111 |

| S5 | (101) | 101 | 0101 | 101100 |

| S6 | (110) | 110 | 0110 | 110001 |

| S7 | (111) | 111 | 1111 | 111010 |

| State | Frequency | Accumulation | C = 0% | C = 30% | C = 60% | C = 90% | C = 100% |

|---|---|---|---|---|---|---|---|

| S3 | 24.58% | 24.58% | SNC | SC | SC | SC | SC |

| S2 | 22.48% | 47.06% | SNC | SC | SC | SC | SC |

| S4 | 16.59% | 63.65% | SNC | SNC | SC | SC | SC |

| S0 | 15.30% | 78.95% | SNC | SNC | SNC | SC | SC |

| S1 | 15.30% | 94.25% | SNC | SNC | SNC | SC | SC |

| S5 | 3.83% | 98.08% | SNC | SNC | SNC | SNC | SC |

| S7 | 0.96% | 99.04% | SNC | SNC | SNC | SNC | SC |

| S6 | 0.96% | 100.00% | SNC | SNC | SNC | SNC | SC |

| State | Type | (H-1, H-1) | (H-3, H-1) | (H-5, H-1) | (H-7, H-1) |

|---|---|---|---|---|---|

| S0 | SNC | 000 | 00101 | 0000000111 | 000000001111 |

| S1 | SNC | 001 | 00111 | 0000001011 | 000000011011 |

| S2 | SC | 010 | 00000 | 0000000000 | 000000000000 |

| S3 | SC | 011 | 01011 | 0111010001 | 010100110111 |

| S4 | SC | 100 | 10110 | 1001110011 | 101001101110 |

| S5 | SNC | 101 | 01100 | 0000001101 | 000000011101 |

| S6 | SNC | 110 | 01101 | 0000001110 | 000000011110 |

| S7 | SNC | 111 | 01110 | 0000001111 | 000000011111 |

| State | C = 0% | C = 30% | C = 60% | C = 90% | C = 100% |

|---|---|---|---|---|---|

| S0 | 000 (SNC) | 1001 (SNC) | 00101 (SNC) | 000000 (SC) | 000000 (SC) |

| S1 | 001 (SNC) | 1010 (SNC) | 00111 (SNC) | 001011 (SC) | 001011 (SC) |

| S2 | 010 (SNC) | 0000 (SC) | 00000 (SC) | 010110 (SC) | 010110 (SC) |

| S3 | 011 (SNC) | 0111 (SC) | 01011 (SC) | 011101 (SC) | 011101 (SC) |

| S4 | 100 (SNC) | 1011 (SNC) | 10110 (SC) | 100111 (SC) | 100111 (SC) |

| S5 | 101 (SNC) | 1100 (SNC) | 01100 (SNC) | 000101 (SNC) | 101100 (SC) |

| S6 | 110 (SNC) | 1101 (SNC) | 01101 (SNC) | 001100 (SNC) | 110001 (SC) |

| S7 | 111 (SNC) | 1110 (SNC) | 01110 (SNC) | 001110 (SNC) | 111010 (SC) |

| State | Type | Next State | Outputs | ||||||

|---|---|---|---|---|---|---|---|---|---|

| I = 00 | I = 01 | I = 10 | I = 11 | I = 00 | I = 01 | I = 10 | I = 11 | ||

| S0 (00101) | SNC | S0 | S3 | S1 | S4 | 001 | 010 | 001 | 010 |

| S1 (00111) | SNC | S2 | S3 | S2 | S5 | 000 | 000 | 010 | 000 |

| S2 (00000) | SC | S0 | S0 | S1 | S1 | 001 | 101 | 001 | 101 |

| S2,0 (00001) | SR | S0 | S0 | S1 | S1 | 001 | 101 | 001 | 101 |

| S2,1 (00010) | SR | S0 | S0 | S1 | S1 | 001 | 101 | 001 | 101 |

| S2,2 (00100) | SR | S0 | S0 | S1 | S1 | 001 | 101 | 001 | 101 |

| S2,3 (01000) | SR | S0 | S0 | S1 | S1 | 001 | 101 | 001 | 101 |

| S2,4 (10000) | SR | S0 | S0 | S1 | S1 | 001 | 101 | 001 | 101 |

| S3 (01011) | SC | S3 | S4 | S3 | S4 | 100 | 101 | 010 | 101 |

| S3,0 (01010) | SR | S3 | S4 | S3 | S4 | 100 | 101 | 010 | 101 |

| S3,1 (01001) | SR | S3 | S4 | S3 | S4 | 100 | 101 | 010 | 101 |

| S3,2 (01111) | SR | S3 | S4 | S3 | S4 | 100 | 101 | 010 | 101 |

| S3,3 (00011) | SR | S3 | S4 | S3 | S4 | 100 | 101 | 010 | 101 |

| S3,4 (11011) | SR | S3 | S4 | S3 | S4 | 100 | 101 | 010 | 101 |

| S4 (10110) | SC | S4 | S3 | S4 | S4 | 000 | 100 | 010 | 100 |

| S4,0 (10111) | SR | S4 | S3 | S4 | S4 | 000 | 100 | 010 | 100 |

| S4,1 (10100) | SR | S4 | S3 | S4 | S4 | 000 | 100 | 010 | 100 |

| S4,2 (10010) | SR | S4 | S3 | S4 | S4 | 000 | 100 | 010 | 100 |

| S4,3 (11110) | SR | S4 | S3 | S4 | S4 | 000 | 100 | 010 | 100 |

| S4,4 (00110) | SR | S4 | S3 | S4 | S4 | 000 | 100 | 010 | 100 |

| S5 (01100) | SNC | S6 | S7 | S2 | S2 | 000 | 000 | 010 | 100 |

| S6 (01101) | SNC | S3 | S0 | S4 | S1 | 010 | 101 | 010 | 101 |

| S7 (01110) | SNC | S3 | S4 | S2 | S2 | 100 | 100 | 010 | 100 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, J.; Yoo, H. Area-Efficient Differential Fault Tolerance Encoding for Finite State Machines. Electronics 2020, 9, 1110. https://doi.org/10.3390/electronics9071110

Park J, Yoo H. Area-Efficient Differential Fault Tolerance Encoding for Finite State Machines. Electronics. 2020; 9(7):1110. https://doi.org/10.3390/electronics9071110

Chicago/Turabian StylePark, Jiwoon, and Hoyoung Yoo. 2020. "Area-Efficient Differential Fault Tolerance Encoding for Finite State Machines" Electronics 9, no. 7: 1110. https://doi.org/10.3390/electronics9071110

APA StylePark, J., & Yoo, H. (2020). Area-Efficient Differential Fault Tolerance Encoding for Finite State Machines. Electronics, 9(7), 1110. https://doi.org/10.3390/electronics9071110