A Network Adaptive Fault-Tolerant Routing Algorithm for Demanding Latency and Throughput Applications of Network-on-a-Chip Designs

Abstract

1. Introduction

- The proposed NAFTR algorithm decreased the latency in fault-free scenarios by avoiding the congested regions in the network.

- When there was a tie between two outports in terms of having a similar hop count toward a destination, the NAFTR algorithm ensured load balancing regarding route selection.

- Moreover, the NAFTR algorithm increased the flit delivery ratio by selecting alternate outports to avoid livelocks in the network.

2. Related Research

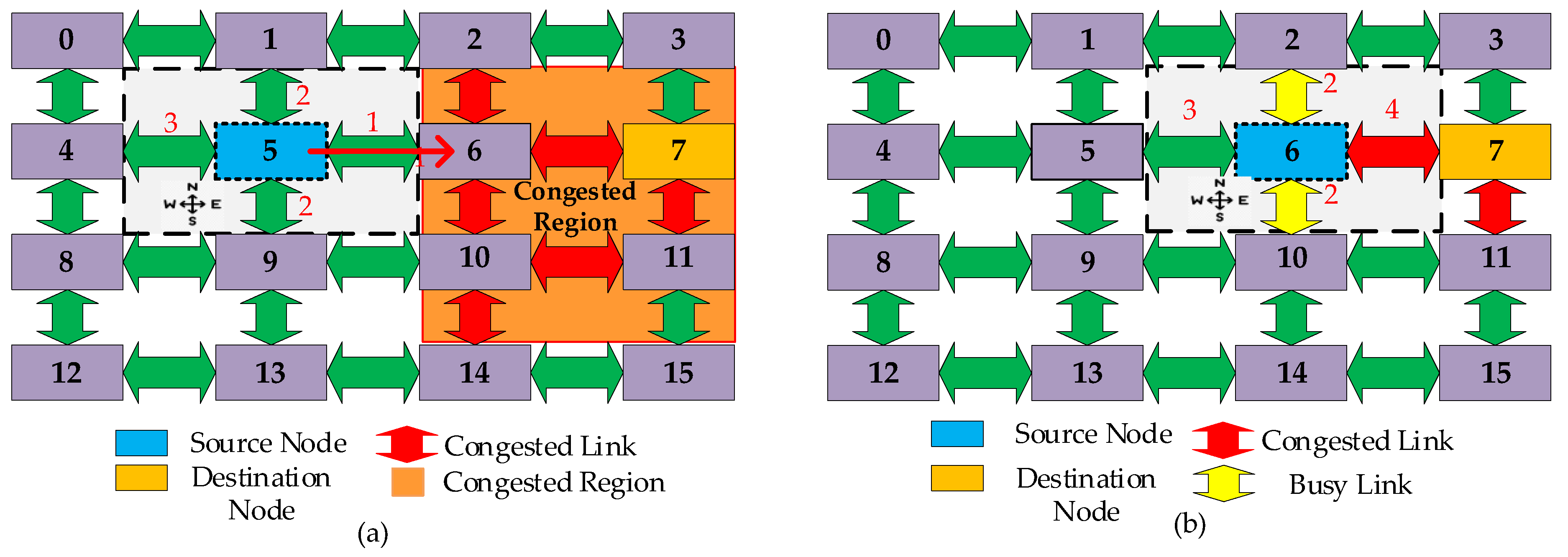

3. Problem Statement

4. Proposed Solution

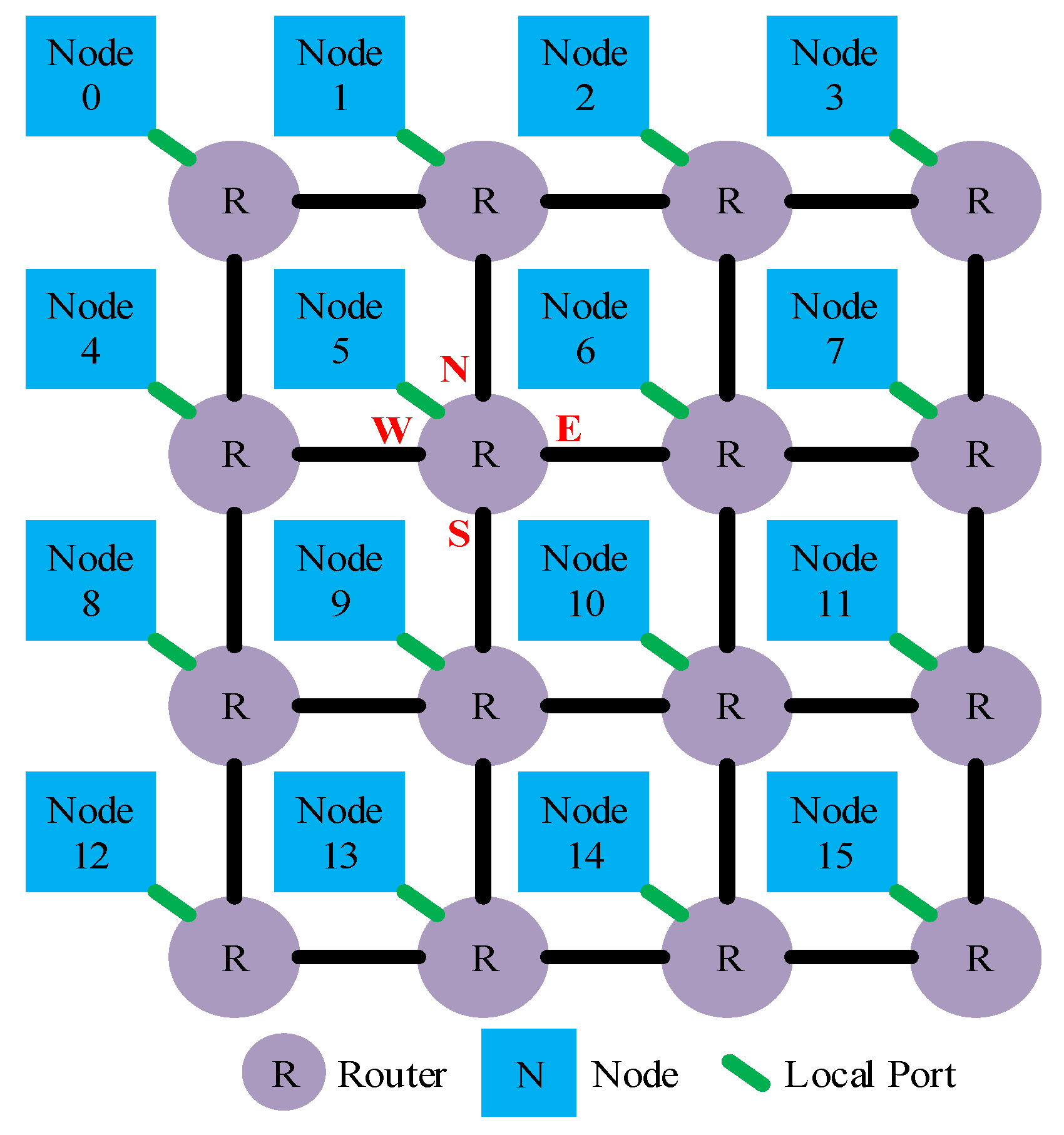

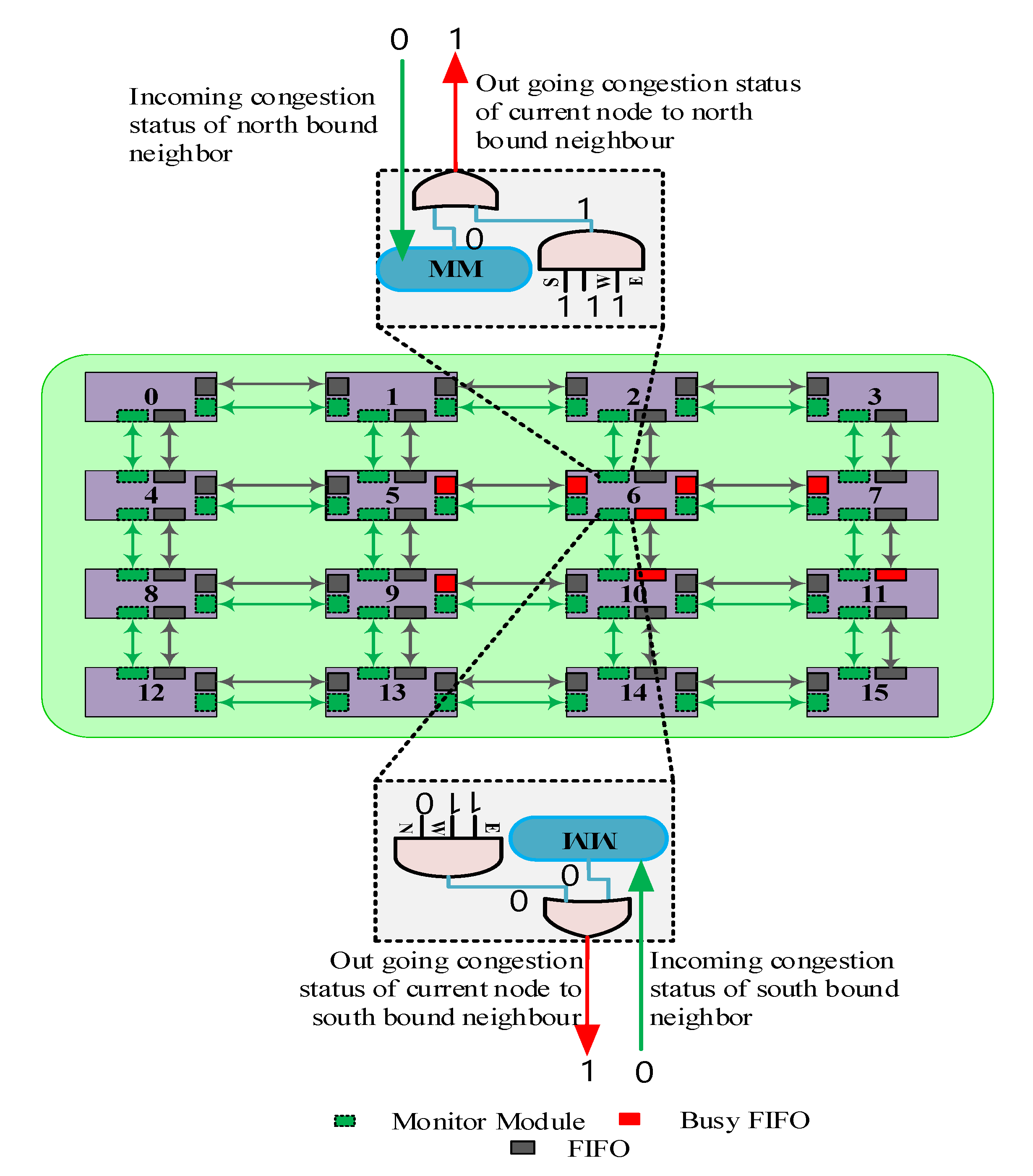

4.1. Modified EMBRACE Router Architecture

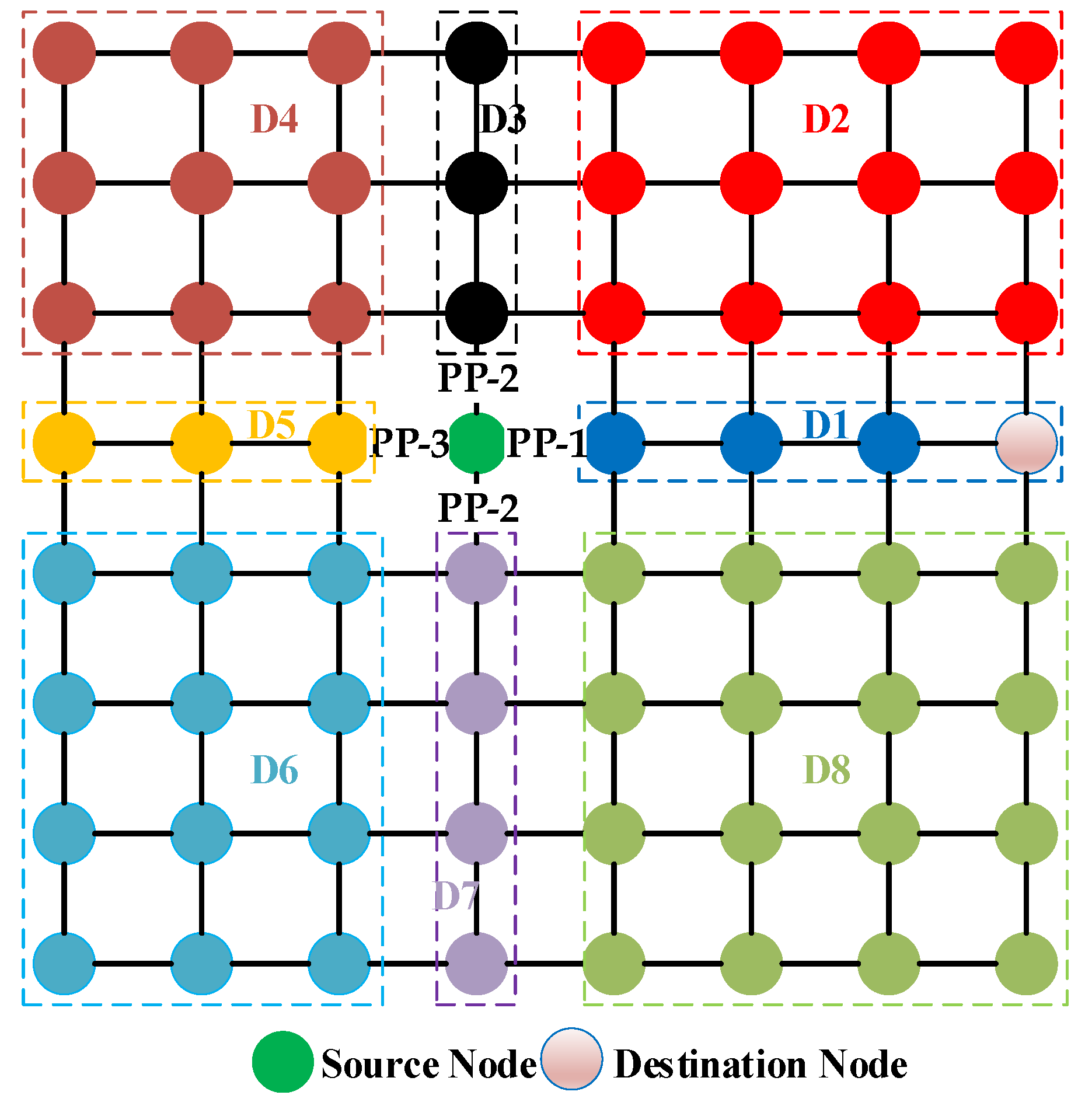

4.2. NAFTR Algorithm

4.2.1. Latency Improvement Achieved Using NAFTR in Fault-Free Scenarios

4.2.2. Load Balancing

| Algorithm 1: Network-Adaptive Fault-Tolerant Routing (NAFTR) Algorithm | |

| Input:, DestinationID, CurrentID, , In-port | |

| Output: Chosen Out-portOutput | |

| 01 | procedure Determine_Next_Hop |

| 02 | Xcur= CurrentID / numcols, Ycur = CurrentID % numcols |

| 03 | Xdest= DestinationID / , Ydest = DestinationID % |

| 04 | if ( == && == ) then |

| 05 | return local port; |

| 06 | end if |

| 07 | [4]=DPWC(x) |

| 08 | for i=E to W do |

| 09 | if equals 1 then |

| 10 | =3/2/10 |

| 11 | end if |

| 12 | + |

| 13 | end for |

| 14 | Selected-port=Min-weigh-port-in |

| 15 | if Selected-port equals In-port then |

| 16 | Out-port=Second_Min_Weigh_Port_in |

| 17 | else |

| 18 | return Selected-port |

| 19 | end if |

| 20 | end procedure |

| 01 | procedure DPWC(x) |

| 02 | if (x==0) then |

| 03 | z1=0,z2=0.5 |

| 04 | else z1=0.5,z2=0 |

| 05 | if () then //D1 |

| 06 | ={2+z1,1,2+z2,3} end if |

| 07 | else if () then //D2 |

| 08 | ={2,1,3+z1,3+z2} end if |

| 09 | else if () then //D3 |

| 10 | ={1,2+z1,3,2+z2} end if |

| 11 | else if () then //D4 |

| 12 | ={2,3+z1,3+z2,1} end if |

| 13 | else if () then //D5 |

| 14 | ={2+z1,3,2+z2,1} end if |

| 15 | else if () then //D6 |

| 16 | ={3+z1,3+z2,2,1} end if |

| 17 | else if () then //D7 |

| 18 | ={3,2+z1,1,2+z2} end if |

| 19 | else if () then //D8 |

| 20 | ={3+z1,1,2,3+z2} end if |

| 21 | end procedure |

4.2.3. Livelock/Deadlock Avoidance

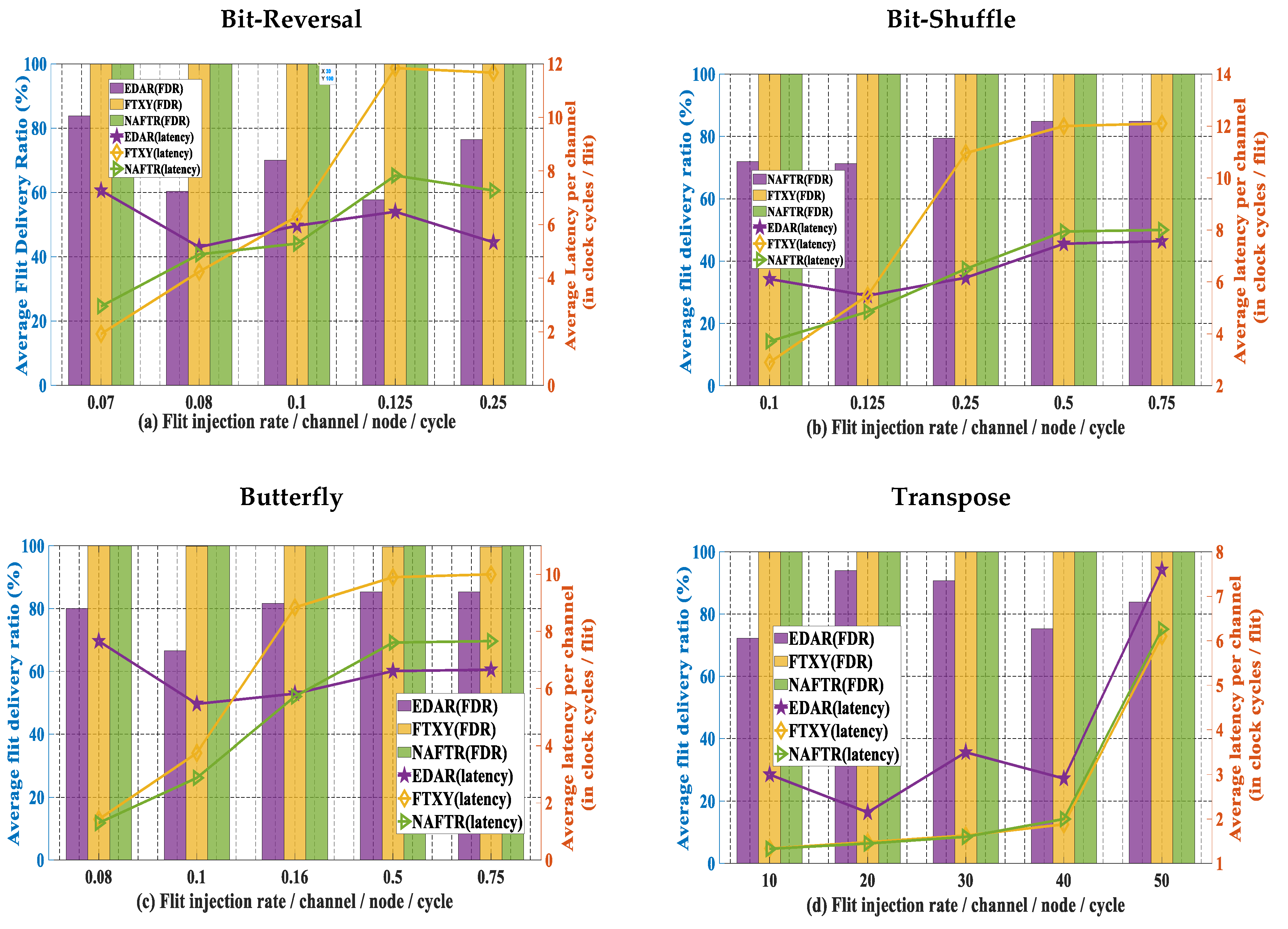

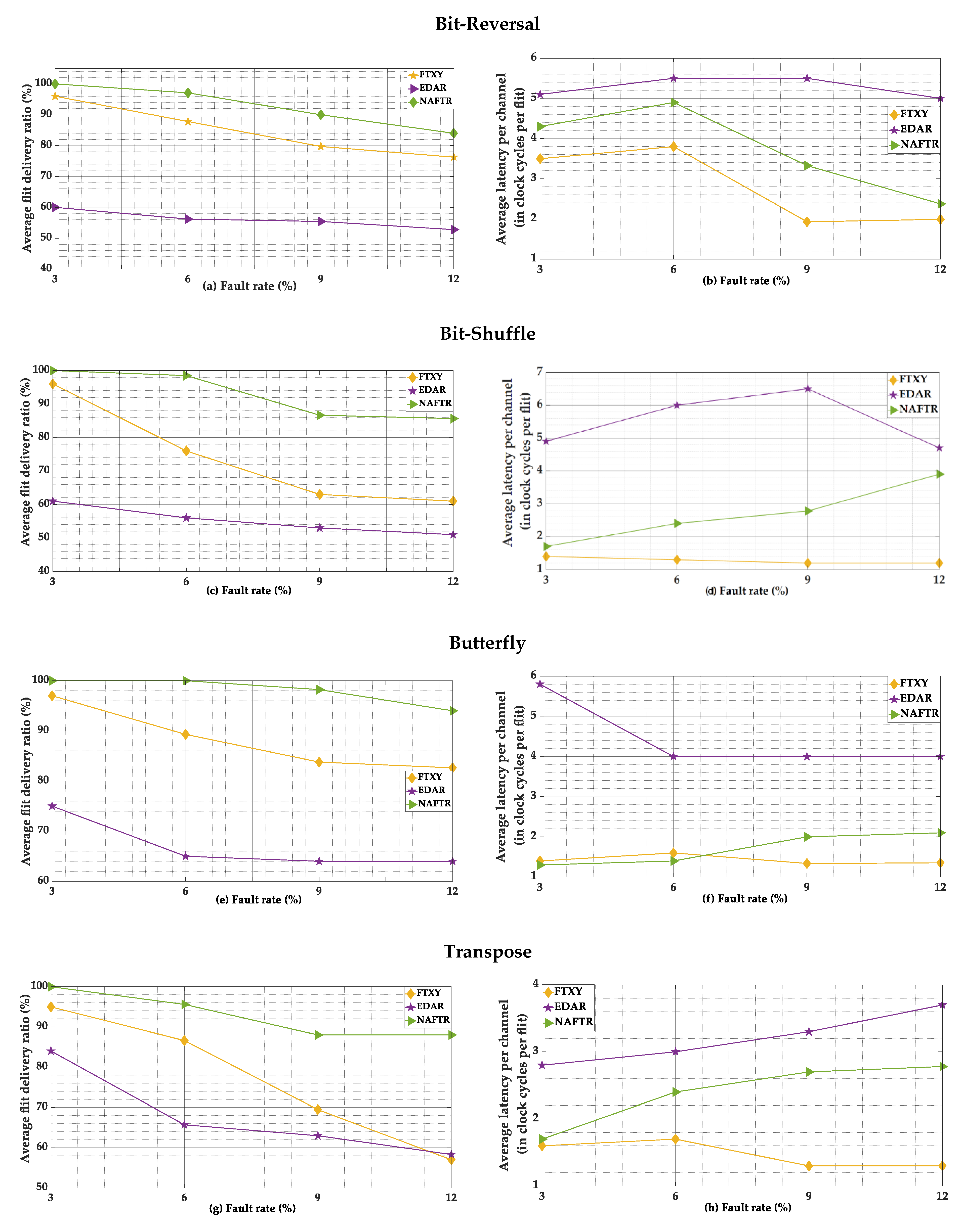

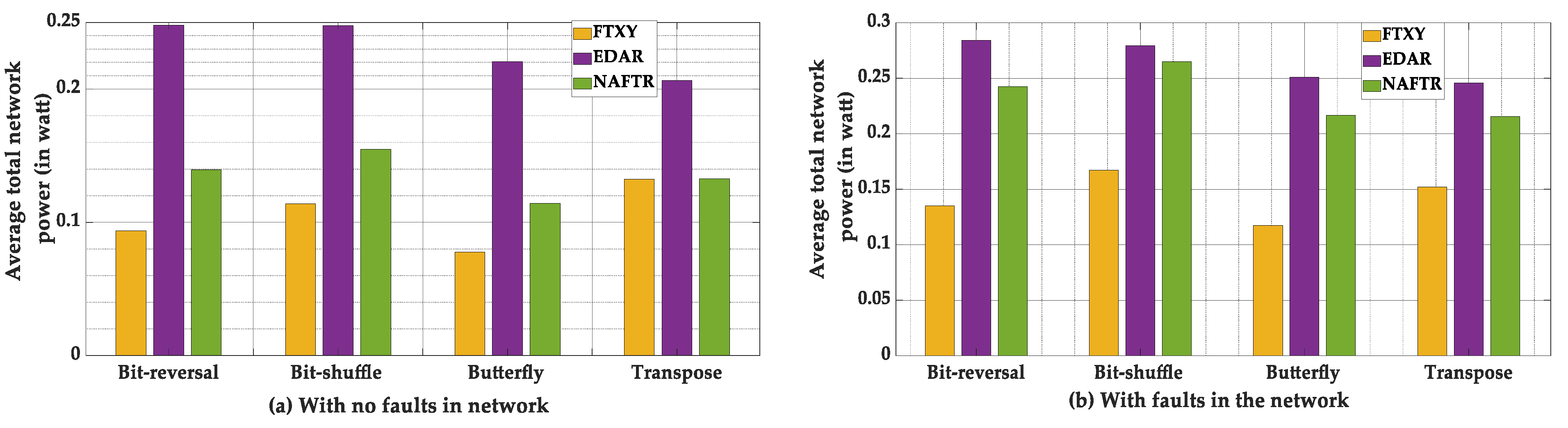

5. Experimental Results

Hardware Requirement Analysis

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hassan, A.S.; Morgan, A.A.; El-Kharashi, M.W. An Enhanced Network-on-chip Simulation for Cluster-based Routing. Procedia Comput. Sci. 2016, 94, 410–417. [Google Scholar] [CrossRef]

- Fathi, M.; Ebrahimi, S.; Pedram, H. A fault-tolerant routing algorithm in 3D topology manycore processors. In Proceedings of the 2015 2nd International Conference on Knowledge-Based Engineering and Innovation (KBEI), Tehran, Iran, 5–6 November 2015; pp. 217–222. [Google Scholar]

- Yang, P.; Wang, Q. Heterogeneous Honeycomb-like NoC Topology and Routing based on Communication Division. Int. J. Futur. Gener. Commun. Netw. 2015, 8, 19–26. [Google Scholar] [CrossRef]

- Anuradha, K.S.; Mahendra, A.G. Review of Odd-Even Routing Algorithm for 2D Mesh Topology of Network-on-Chip Architecture for Bursty Traffic. IJCA Spec. Issue Recent Trends Eng. Technol. 2013, RETRET, 9–12. [Google Scholar]

- Gulzari, U.A.; Anjum, S.; Aghaa, S.; Khan, S.; Torres, F.S. Efficient and scalable cross-by-pass-mesh topology for networks-on-chip. IET Comput. Digit. Tech. 2017, 11, 140–148. [Google Scholar] [CrossRef]

- Gulzari, U.A.; Sajid, M.; Anjum, S.; Agha, S.; Torres, F.S. A New Cross-By-Pass-Torus Architecture Based on CBP-Mesh and Torus Interconnection for On-Chip Communication. PLoS ONE 2016, 11, 0167590. [Google Scholar] [CrossRef]

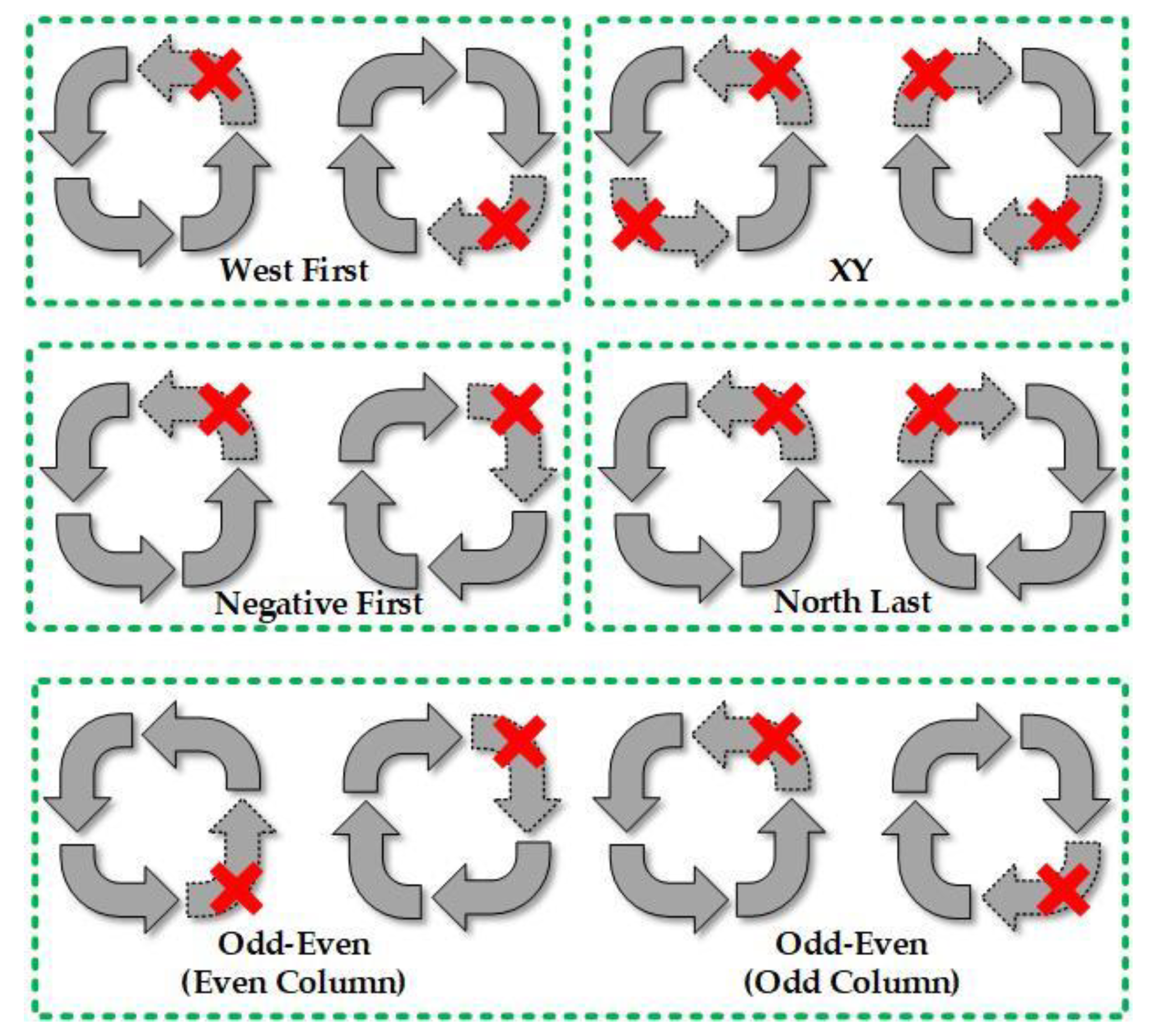

- Glass, C.J.; Ni, L.M. The Turn Model for Adaptive Routing. In Proceedings of the 19th Annual International Symposium on Computer Architecture, Queensland, Australia, 19–21 May 1992; pp. 278–287. [Google Scholar]

- Jiang, S.; Jiang, S.; Liu, P.; Liu, Y.; Cheng, H. Network on Chip-based Fault-Tolerant Routing Algorithm and Its Implementation. Trans. Comput. Sci. Technol. 2013, 2, 55–61. [Google Scholar]

- Chand, M.S.; Naveen, C.; Dharm, J. An Efficient Routing Implementation for Irregular Networks. Glob. J. Comput. Sci. Technol. 2014, 14, 65284796. [Google Scholar]

- Liu, J.; Harkin, J.; Li, Y.; Maguire, L. Low-cost fault-tolerant routing algorithm for Networks-on-Chip. Microprocess. Microsyst. 2015, 39, 358–372. [Google Scholar] [CrossRef]

- Du, G.; He, J.; Song, Y.; Zhang, D.; Wu, H. Comparison of NoC routing algorithms based on packet-circuit switching. In Proceedings of the 2013 IEEE Third International Conference on Information Science and Technology (ICIST), Yangzhou, China, 23–25 March 2013; pp. 707–710. [Google Scholar]

- Chiu, G.-M. The Odd-Even Turn Model for Adaptive Routing. IEEE Trans. Parallel Distrib. Syst. 2000, 11, 729–738. [Google Scholar] [CrossRef]

- Boura, Y.M.; Das, C.R. Efficient fully adaptive wormhole routing in n-dimensional meshes. In Proceedings of the 14th International Conference on Distributed Computing Systems, Poznan, Poland, 21–24 June 1994; pp. 589–596. [Google Scholar]

- Chien, A.A.; Jae, H.K. Planar-Adaptive Routing: Low-cost Adaptive Networks for Multiprocessors. In Proceedings of the 19th Annual International Symposium on Computer Architecture, Queensland, Australia, 19–21 May 1992; pp. 268–277. [Google Scholar]

- Reza, A.; Ali, A.E.; Farshad, S. An efficient fault-tolerant routing algorithm in NoCs to tolerate permanent faults. J. Supercomput. 2016. [Google Scholar] [CrossRef]

- Glass, C.J.; Ni, L.M. Fault-tolerant wormhole routing in meshes. In Proceedings of the FTCS-23 The Twenty-Third International Symposium on Fault-Tolerant Computing, Toulouse, France, 22–24 June 1993; pp. 240–249. [Google Scholar]

- Wu, J. A Fault-Tolerant and Deadlock-Free Routing Protocol in 2D Meshes Based on Odd-Even Turn Model. IEEE Trans. Comput. 2003, 52, 1154–1169. [Google Scholar]

- Chalasani, S.; Boppana, R.V. Fault-Tolerant Wormhole Routing Algorithms for Mesh Networks. IEEE Trans. Comput. 1995, 44, 848–864. [Google Scholar]

- Chiu, K.-H.C.A.G.-M. Fault-Tolerant Routing Algorithm for Meshes Without Using Virtual Channels. J. Inf. Sci. Eng. 1998, 14, 765–783. [Google Scholar]

- Su, C.-C.; Shin, K.G. Adaptive Fault-Tolerant Deadlock-Free Routing in Meshes and Hypercubes. IEEE Trans. Comput. 1996, 45, 666–683. [Google Scholar]

- Park, D.; Nicopoulos, C.; Kim, J.; Vijaykrishnan, N.; Das, C.R. Exploring Fault-Tolerant Network-on-Chip Architectures. In Proceedings of the International Conference on Dependable Systems and Networks, Philadelphia, PA, USA, 25–28 June 2006; pp. 93–104. [Google Scholar]

- Schonwald, T.; Zimmermann, J.; Bringmann, O.; Rosenstiel, W. Fully Adaptive Fault-Tolerant Routing Algorithm for Network-on-Chip Architectures. In Proceedings of the 10th Euromicro Conference on Digital System Design Architectures, Methods and Tools, Lubeck, Germany, 29–31 August 2007; pp. 527–534. [Google Scholar]

- Singh, S.K.; Mondal, A.J.; Majumder, A. Generation and Performance Evaluation of Reconfigurable Fault-Tolerant Routing Algorithm for 2D-Mesh NoC. Procedia Comput. Sci. 2015, 57, 232–240. [Google Scholar] [CrossRef]

- Tse, S.S.H.; Zhou, J.; Lau, F.C.M. Fault-tolerant Routing for Irregular Faulty Patterns in 2D-Mesh Without Virtual Channel. In Proceedings of the 2012 12th International Symposium on Pervasive Systems, Algorithms and Networks, San Marcos, TX, USA, 13–15 December 2012; pp. 96–103. [Google Scholar]

- Bishnoi, R. Hybrid fault-tolerant routing algorithm in NoC. Perspect. Sci. 2016, 8, 586–588. [Google Scholar] [CrossRef]

- Yang, P.; Wang, Q.; Li, W.; Yu, Z.; Ye, H. A Fault Tolerance NoC Topology and Adaptive Routing Algorithm. In Proceedings of the 2016 13th International Conference on Embedded Software and Systems (ICESS), Chengdu, China, 13–14 August 2016; pp. 42–47. [Google Scholar]

- Moriam, S.; Fettweis, G.P. Reliability assessment of fault-tolerant routing algorithms in networks-on-chip: an analytic approach. In Proceedings of the Conference on Design, Automation & Test in Europe, Lausanne, Switzerland, 27–31 March 2017; pp. 61–66. [Google Scholar]

- Melo, D.R.; Zeferino, C.A.; Dilillo, L.; Bezerra, E.A. Maximizing the Inner Resilience of a Network-on-Chip through Router Controllers Design. Sensors 2019, 19, 5416. [Google Scholar] [CrossRef]

- Zhang, Z.; Serwe, W.; Wu, J.; Yoneda, T.; Zheng, H.; Myers, C. An improved fault-tolerant routing algorithm for a Network-on-Chip derived with formal analysis. Sci. Comput. Program. 2016, 118, 61–66. [Google Scholar] [CrossRef]

- Xiang, D.; Pan, Q. Low-power and high-performance adaptive routing in on-chip networks. CCF Trans. HPC 2019, 1, 92–110. [Google Scholar] [CrossRef]

- Deb, D.; Jose, J.; Das, S.; KKapoor, H. Cost effective routing techniques in 2D mesh NoC using on-chip transmission lines. J. Parallel Distrib. Comput. 2019, 123, 118–129. [Google Scholar] [CrossRef]

- Song, Y.; Lin, B. Uniform Minimal First: Latency Reduction in Throughput-Optimal Oblivious Routing for Mesh-Based Networks-on-Chip. IEEE Embed. Syst. Lett. 2019, 11, 81–84. [Google Scholar] [CrossRef]

- Lin, L.; Sun, Y.; Zhu, Z.; Yang, Y. A congestion-aware OE router employing fair arbitration for network-on-chip. J. Semicond. 2018, 39, 125006. [Google Scholar] [CrossRef]

- Kang, J.; Cunlu, L.; Dezun, D.; Binzhang, F. HARE: History-Aware Adaptive Routing Algorithm for Endpoint congestion in Networks-on-Chip. Int. J. Parallel Program. 2018, 47, 433–450. [Google Scholar]

- Carrillo, S.; Harkin, J.; McDaid, L.; Pande, S.; Cawley, S.; McGinley, B.; Morgan, F. Advancing interconnect density for spiking neural network hardware implementations using traffic-aware adaptive network-on-chip routers. Neural Networks 2012, 33, 42–57. [Google Scholar] [CrossRef] [PubMed]

- Liu, J.; Harkin, J.; Li, Y.; Maguire, L. Online traffic-aware fault detection for networks-on-chip. J. Parallel Distrib. Comput. 2014, 74, 1984–1993. [Google Scholar] [CrossRef]

- Pande, S.; Morgan, F.; Smit, G.; Bruintjes, T.; Rutgers, J.; McGinley, B.; Cawley, S.; Harkin, J.; McDaid, L. Fixed latency on-chip interconnect for hardware spiking neural network architectures. Parallel Comput. 2013, 39, 357–371. [Google Scholar] [CrossRef]

- Carrillo, S.; Harkin, J.; McDaid, L.J.; Pande, S.; Cawley, S.; McGinley, B.; Morgan, F. Hierarchical Network-on-Chip and Traffic Compression for Spiking Neural Network Implementations. In Proceedings of the 2012 IEEE/ACM Sixth International Symposium on Networks-on-Chip, Lyngby, Denmark, 9–11 May 2012; pp. 83–90. [Google Scholar]

- Jerger, N.E. On-Chip Networks; Morgan & Claypool: San Rafael, CA, USA, 2009; Volume 4. [Google Scholar]

- Alhussien, A.; Wang, C.; Bagherzadeh, N. Design and evaluation of a high throughput robust router for network-on-chip. IET Comput. Digit. Tech. 2012, 6, 173–179. [Google Scholar] [CrossRef]

- School of Electronics and Computer Science, University of Southampton. Available online: http://nirgam.ecs.soton.ac.uk/ (accessed on 10 February 2020).

| Ref. | Primary Focus of the Study is to Propose | Supported Network Topology | Analysis Performed on | Virtual Channel Utilization to Avoid Faults | Fault Tolerance | Congestion Awareness | Business Awareness | Proposed Algorithm Compared with |

|---|---|---|---|---|---|---|---|---|

| Glass et al. [16] | Negative-first-based adaptive fault-tolerant routing | 2D mesh | In-house built simulator | × | √ | × | × | Negative first |

| Jie Wu [17] | Adaptive fault-tolerant routing | 2D mesh | × | √ | × | × | - | |

| Boppana et al. [18] | Adaptive fault-tolerant routing | 2D mesh and torus | √ | √ | × | × | e-cube | |

| Chen et al. [19] | Adaptive fault-tolerant routing | 2D mesh | × | √ | × | × | Boura’s algorithm | |

| Su et al. [20] | Adaptive fault-tolerant routing | 2D mesh and hypercube | √ | √ | × | × | e-cube | |

| Park et al. [21] | Adaptive fault-tolerant routing | 2D mesh | √ | √ | × | × | - | |

| Schonwald et al. [22] | Adaptive fault-tolerant routing | 2D mesh and torus | × | √ | × | × | XY | |

| Singh et al. [23] | Adaptive fault-tolerant routing | 2D mesh | × | √ | √ | × | XY, west first, north last, negative first | |

| Tse et al. [24] | Adaptive fault-tolerant routing | 2D mesh | - | × | √ | × | × | - |

| Bishnoi [25] | Adaptive fault-tolerant routing | 2D mesh | - | √ | √ | × | × | - |

| Yang et al. [26] | Adaptive fault-tolerant routing | Honeycomb | Nirgam Simulator | × | √ | √ | × | Dimensional order routing |

| Moriam et al. [27] | Analytical model to assess fault-tolerant routing algorithms | 2D mesh and hexagonal | In-house built simulator | - | - | - | - | - |

| Douglas et al. [28] | Router controller design | 2D mesh | - | √ | × | × | - | |

| Zhang et al. [29] | Fault-tolerant routing | 2D mesh | In-house built simulator | - | √ | × | × | - |

| Xiang et al. [30] | Fully adaptive routing | 2D mesh | × | × | × | × | DyXY, DP, SU, EVC | |

| Deb et al. [31] | Routing technique using on-chip transmission lines | 2D mesh | Booksim simulator | × | × | √ | × | - |

| Song et al. [32] | Latency reduction in oblivious routing | 2D mesh | PopNet simulator | × | × | × | × | Valiant, dimension order routing |

| Liu et al. [33] | Congestion-aware odd-even (OE) router employing fair arbitration | 2D mesh | Noxim simulator | × | × | √ | × | OE, CAOE-random |

| Jin et al. [34] | History-aware adaptive Routing for end-point congestion | 2D mesh | Booksim simulator | × | × | √ | × | Footprint, Dimensional order routing |

| Liu et al. [10] | Low-cost fault-tolerant routing | 2D mesh | Noxim simulator | × | √ | √ | √ | DyAD, OE, XY, Negative first, FoN, Cost, FTDR, FTDR-H, LAFT, HLAFT, |

| This work | Fault-tolerant routing for throughput and latency-critical NoC architectures | 2D mesh | Nirgam simulator | × | √ | √ | √ | EDAR, FTXY |

| Variable | Description |

|---|---|

| ID of the current node | |

| ID of the destination node | |

| x coordinate of the current node | |

| y coordinate of the current node | |

| x coordinate of the destination node | |

| y coordinate of the destination node | |

| Number of columns in the network | |

| Inport of incoming flit | |

| Selected outgoing port for a flit | |

| Busy status of neighboring channels | |

| Congestion status of neighboring channels | |

| Fault status of neighboring channels | |

| Direction priority of each outport, which depends on the location of the destination node | |

| Weight for busy neighboring channels either have a value of 0 or 2 | |

| Weight for congested neighboring channels either have a value of 0 or 3 | |

| Weight for faulty neighboring channels either have a value of 0 or 10 | |

| Total weight of each outport, which is calculated by adding and |

| Name | Description |

|---|---|

| Simulator | Nirgam 2.1 |

| Routing algorithms | EDAR, FTXY, NAFTR |

| Topology | 2D mesh |

| Traffic pattern | Bit-shuffle, bit-reversal, butterfly, transpose |

| Size of the network | 5 × 5 |

| Warm-up time | 5 cycles |

| Simulation time | 5000 cycles |

| Fault percentage | 3%, 6%, 9%, 12% |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nain, Z.; Ali, R.; Anjum, S.; Afzal, M.K.; Kim, S.W. A Network Adaptive Fault-Tolerant Routing Algorithm for Demanding Latency and Throughput Applications of Network-on-a-Chip Designs. Electronics 2020, 9, 1076. https://doi.org/10.3390/electronics9071076

Nain Z, Ali R, Anjum S, Afzal MK, Kim SW. A Network Adaptive Fault-Tolerant Routing Algorithm for Demanding Latency and Throughput Applications of Network-on-a-Chip Designs. Electronics. 2020; 9(7):1076. https://doi.org/10.3390/electronics9071076

Chicago/Turabian StyleNain, Zulqar, Rashid Ali, Sheraz Anjum, Muhammad Khalil Afzal, and Sung Won Kim. 2020. "A Network Adaptive Fault-Tolerant Routing Algorithm for Demanding Latency and Throughput Applications of Network-on-a-Chip Designs" Electronics 9, no. 7: 1076. https://doi.org/10.3390/electronics9071076

APA StyleNain, Z., Ali, R., Anjum, S., Afzal, M. K., & Kim, S. W. (2020). A Network Adaptive Fault-Tolerant Routing Algorithm for Demanding Latency and Throughput Applications of Network-on-a-Chip Designs. Electronics, 9(7), 1076. https://doi.org/10.3390/electronics9071076