Abstract

Thin film transistors (TFTs) fabricated on flexible and large area substrates have been studied with great interest due to their future applications. Recent studies have developed new semiconductors such as a-SiGe:H for fabrication of high performance TFTs. These films have important advantages, including deposition at low temperatures and low pressures, and higher carrier mobilities. Due to these advantages, the a-SiGe:H films can be used in the fabrication of TFTs. In this work, we present an analytical drain current model for a-SiGe:H TFTs considering density of states and free charges, which describes the current behavior at sub-and above- threshold region. In addition, 2D numerical simulations of a-SiGe:H TFTs are developed. The results of the analytical drain current model agree well with those of the 2D numerical simulations. For all characteristics of the drain current curves, the average absolute error of the analytical model is close to 5.3%. This analytical drain current model can be useful to estimate the performance of a-SiGe:H TFTs for applications in large area electronics.

1. Introduction

Thin film transistors (TFTs) are key devices to develop large area electronics applications such as active matrix liquid crystal displays (AMLCD) [1,2,3], wearable sensors [4,5] and passive tags RFID (radio frequency identification) [6,7,8]. Nowadays, TFT technology is based on amorphous silicon (a-Si), polysilicon (poly-Si) and IGZO (indium-gallium-zinc oxide) semiconductors. The a-Si TFTs offer small electron mobilities (<1 cm2/Vs), and thus low switching speed [9]. The other hand, poly-Si TFTs are devices with high performance, but they are fabricated at higher temperatures (500–600 °C) [10,11,12], while IGZO TFTs have moderate mobilities (>10 cm2/Vs) and low temperature of fabrication [13]. However, this semiconductor is only used for the fabrication of n-type devices, for p-type is used a different semiconductor, such as SnO [14]. To overcome these limitations, hydrogenated amorphous silicon-germanium (a-SiGe:H) films can be used to fabricate TFTs at low temperature of deposition (<300 °C) by PECVD technique. This allows carrier mobilities higher than 1 cm2/Vs caused by the incorporation of germanium and hydrogen atoms. In addition, a-SiGe:H TFTs can have an ambipolar behavior, allowing their operation into either as n- or p-type [15]. In order to design a-SiGe:H TFTs for specific applications, it is necessary to predict the behavior of their drain currents. Shur et al. [16] reported a physical drain current model for n- and p-channels hydrogenated amorphous silicon and polysilicon staggered bottom-gate top-contact TFTs. This model was implemented into an AIM-SPICE circuit simulator. However, it is adapted from MOSFET model and it does not include semiconductor density of states. Chen et al. [17] reported an analytical drain current model for both triode and saturation region of operation for a-Si:H TFTs considering semiconductor density of states and an effective temperature approach. However, this model registered a high error between measurements and modeled results. Liu et al. [18] presented an analytical drain current model for a-Si:H TFTs based on surface potential, which was compared with numerical simulations considering free and localized carrier densities into the semiconductor. Colalongo et al. [19] designed an analytical drain current model for a-Si:H TFTs based on deep and tail states in both semiconductors, which describe the behavior at sub-threshold and above-threshold mode of operation.

In this paper, we develop an analytical drain current model for a-SiGe:H TFTs that considers free and localized charges into semiconductor and its characteristic temperatures, which can represent the behavior at sub-threshold and above-threshold regions of operation without using fitting parameters. In addition, 2D numerical simulations using finite element method of the output and transfer characteristics of bottom-gate top-contact coplanar a-SiGe:H TFTs are reported. The results of our analytical drain current model agree well with respect to those of the numerical simulations. In Section 2, electrostatic analysis and derivation of expressions for electric field and drain current are explained. In Section 3, comparison of our model and simulation results are presented. Finally, the conclusions are discussed in Section 4.

2. Analytical Drain Current Model for a-SiGe:H TFTs

2.1. Density of Estates of Amorphous Semiconductors

The density of states, g(E), of an amorphous semiconductor thin film consists of four energy bands over the bandgap: two tail bands and two deep bands. Tail bands consist of a donor-like valence band, gTA(E), and an acceptor-like conduction band, . On the other hand, deep bands are composed of a donor-like valence band, , and an acceptor-like conduction band, , which are represented as follow, [20]:

where E is the trap energy, EC and Ev are the conduction and valence band energy, respectively; WTA (kTtail) and WTD (kTtail) are acceptor and donor characteristic decay energy for the tail band, respectively; WGA (kTdeep) and WGD (kTdeep) are acceptor and donor characteristic decay energy for the deep band, respectively; NTA, NTD, NDA and NDD are the conduction and valence band edge intercept densities for the tail and deep band, respectively.

2.2. Analytical Drain Current Model

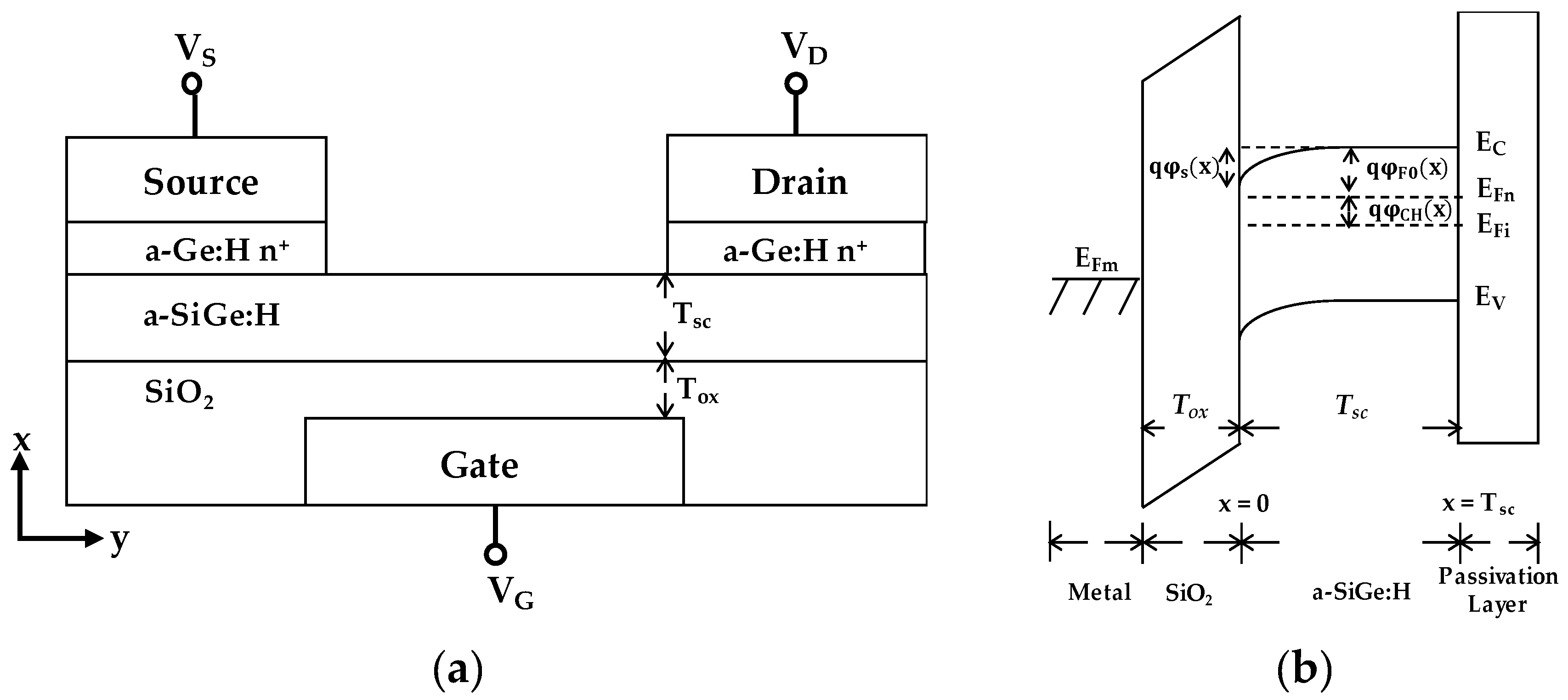

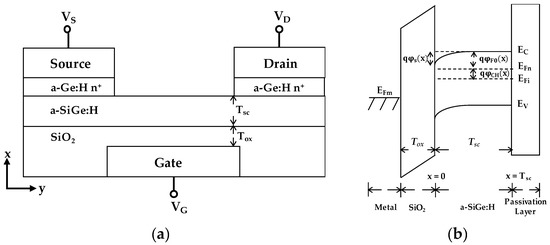

Figure 1a shows a schematic cross section of a n-type coplanar bottom-gate top-contact a-SiGe:H TFT with SiO2 as gate insulator and a-Ge:H n+ layers for drain and source extensions. In this Figure, Tox and Tsc are the gate oxide and semiconductor thickness, respectively. Figure 1b depicts the diagram of energy band for MIS (metal-insulator-semiconductor) region for this device working under accumulation regimen, when a positive gate potential (VG) is applied. For this Figure, EC and EV are energy levels of conduction and valence bands, respectively; EFm, and EFn are the Fermi energy levels for metal, intrinsic and n-type semiconductor, respectively; φS and φCH(x) are surface and channel potential; and φF0(x) is the potential between Ec and EFn.

Figure 1.

(a) Cross-section of a coplanar bottom-gate top-contact a-SiGe:H TFT; (b) equivalent energy band diagram of the MIS region of this device.

2.2.1. Derivation of Electric Field

Taking into account the free and localized electron concentration for an n-type amorphous semiconductor, the Poisson’s equation in one dimension, along the x direction, can be expressed as:

where q is the electron charge, ϕ(x) is the potential across the active layer, ρ(x) is the total charge density, ɛsc is the permittivity constant of the semiconductor layer, nfree(x), ndeep(x) and ntail(x) are the free, deep and tail electron concentrations, respectively. These concentrations for a-SiGe:H layer can be expressed as:

where NC is the free electron concentration, VCH is the potential along the channel, q is the electron charge, k is Boltzmann constant, T is a reference temperature and g is the degeneration factor which depends of the temperature ratio (T/Teff) as exponential expression.

In order to simplify the analysis, an effective carrier concentration (Neff) instead of free, deep or tail carrier concentrations (Nfree, Ndeep or Ntail), which are computed with Equations (8), (10) or (12) equations, respectively, is proposed. In the same way, an effective characteristic temperature (Teff) instead of free, deep or tail temperature (Tfree, Tdeep or Ttail), respectively, is used.

To derivate the electric filed as function of electrostatic potential, it is necessary to solve the following Poisson´s equation:

By employing the next expression to change the integration variable, from x to ϕ(x):

By integrating both sides in Equation (14) and applying the square root, we have:

By substituting Equation (13) into Equation (15) and applying the boundary conditions from x = 0 (ϕS (x)) to x = TSC (ϕB(x)), the electric field as a function of ϕ(x) is expressed as:

where neff is the effective electron density, Teff is the effective characteristic temperature, is the semiconductor permittivity, ϕS(x) is the electrostatic potential in the gate insulator/semiconductor interface, ϕB(x) is the electrostatic potential in the semiconductor/passivation layer interface, which is neglected because is close to zero. Thus, the transversal electric field through an amorphous semiconductor, at x direction, is given by:

2.2.2. Derivation of Drain to Source Current in Subthreshold Region, IDS_sub

In the subthreshold region operation of a-SiGe:H TFT, that is gate to source voltage, VGS, is less than threshold voltage, VTH, but larger than the flat band voltage, VFB, (VFB < VGS < VTH), most of the carriers are free electrons, because of deep and tail localized carriers are trapped into semiconductor defects. Therefore, it is necessary to apply a larger VGS in order to generate a higher transversal electric field to the active layer to set free those charges. In addition, for this semiconductor (see Table 1) the localized energy characteristics (kTtail and kTdeep) are higher than the free energy characteristic (kTfree). Thus, for an a-SiGe:H TFT at subthreshold operation can be obtained by:

Table 1.

Electrical parameters for a-SiGe:H and SiO2 layers [20].

In order to derive the drain to source current in subthreshold regimen, IDS_sub, is employed the gradual channel approximation expression, which is given by:

where W is the channel width of TFT, σn(x) is the n-type channel conductivity of a-SiGe:H, E(φ(x)) is the electric field dependent of potential at x direction, and μ0 is the carrier mobility of semiconductor.

The final expression for drain to source current at region of subthreshold for an a-SiGe:H TFT is computing solving Equation (19), step-by-step at Appendix A, considering Neff = Nfree and Teff = Tfree, as follows:

with:

2.2.3. Derivation of Drain Current at Above Threshold Region, IDS_abv

Above threshold region of a-SiGe:H TFT operation, that is when VGS > VTH, free and localized charges are taken in to account due to the applied gate to source voltage generates a strong transversal electric field to the active layer which produces an accumulation of both carriers in the semiconductor/gate-insulator interface. However, in this semiconductor ndeep(x) << ntail(x). Thus, we obtained the following equation:

Poisson’s equation is applied as follows:

By using the gradual channel approximation Equation (19) and the procedure in Appendix A, taking into account free and tail localized charges along the semiconductor, we can derive the drain to source current for the above threshold region, IDS_abv, as follows:

with

2.2.4. Total Analytical Drain Current Model

The final unified analytical drain current model for a-SiGe:H TFTs takies into account the sub-threshold and above-threshold regions, which it considers the density of states of such amorphous semiconductor and free electrons, is estimated by adding IDS_sub and IDS_abv with the following expression:

3. Results and Discussion

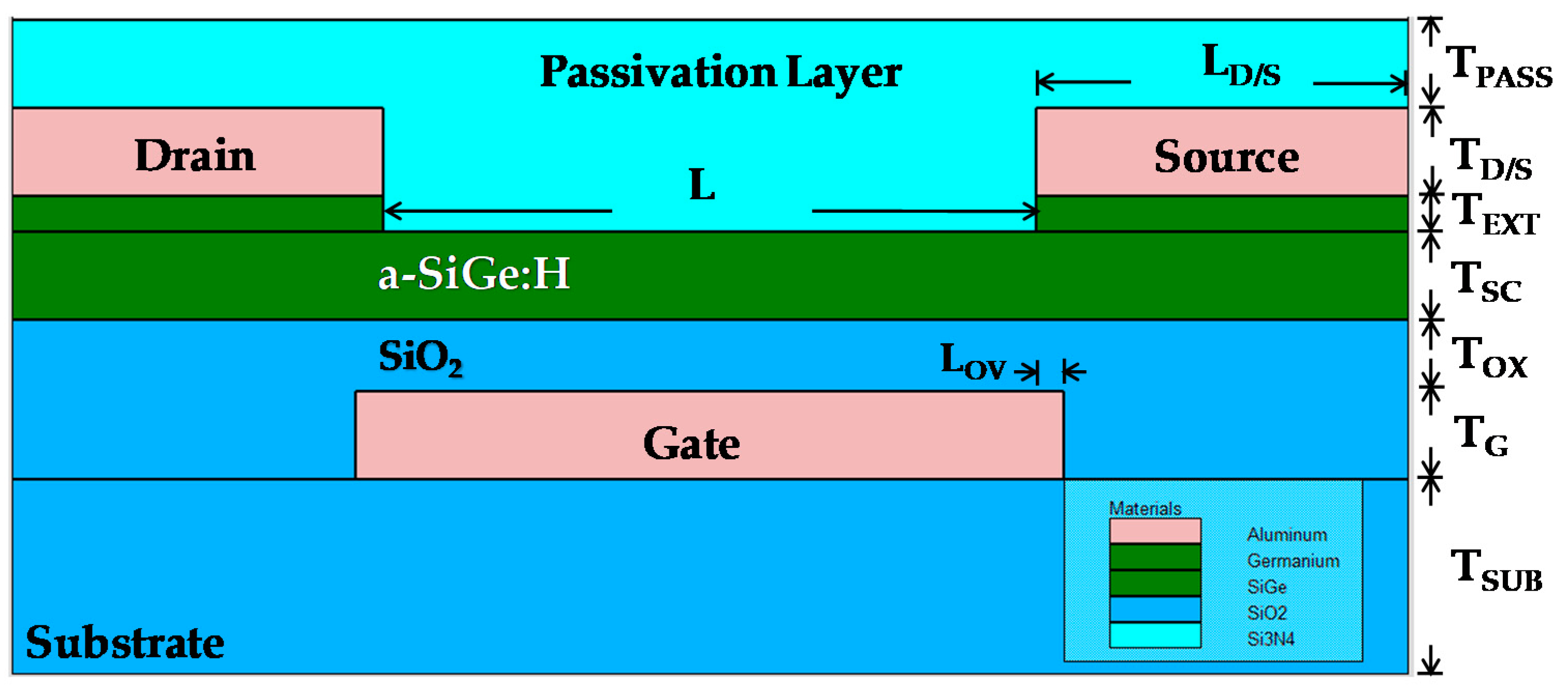

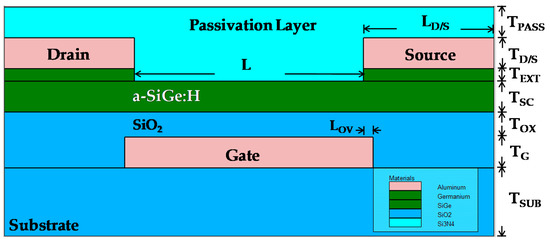

In order to compare the results of our analytical drain current model, we develop 2D numerical simulations for bottom-gate top-contact coplanar a-SiGe:H TFTs using Silvaco TCAD software through Atlas and Devedit tools (Santa Clara, CA, USA) [21]. These simulation tools use finite element method to perform the electrostatic analysis. Figure 2 shows a schematic view of the cross-section of the proposed device and its main geometrical parameters. The substrate is silicon oxide with a thickness TSUB = 200 nm. The gate and drain/source electrodes are aluminum with thickness TG and TD/S of 100 nm, respectively. SiO2 is used as gate insulator with a thickness TOX = 80 nm. An overlap length between gate and drain/source electrodes of LOV = 10 nm is used. Then, a thin film of a-SiGe:H as active layer or semiconductor with a thickness TSC = 100 nm and a length channel L = 75 µm is used. The width of the active layer W = 30 µm is used for calculation. A layer of high doped germanium as drain/source extension region with thickness TEXT = 40 nm and length LD/S = 2 µm are employed to get a good ohmic contact with the semiconductor. Finally, SiN4 as passivating dielectric layer with TPASS = 200 nm is used in order to reduce broken bonds of the a-SiGe:H surface and carriers recombination.

Figure 2.

Bottom-gate top-contact coplanar TFT structure and its geometrical parameters used for 2D numerical simulations.

The parameters for semiconductor and gate insulator layers considered in the numerical simulations and analytical drain current model are listed in Table 1. Furthermore, defects parameters that define the density of states of a-SiGe:H layer used for simulations and modeling are shown in Table 2. Some of those values were taken from [20].

Table 2.

Defects parameters of a-SiGe:H layer employed in analytical model and numerical simulations [20].

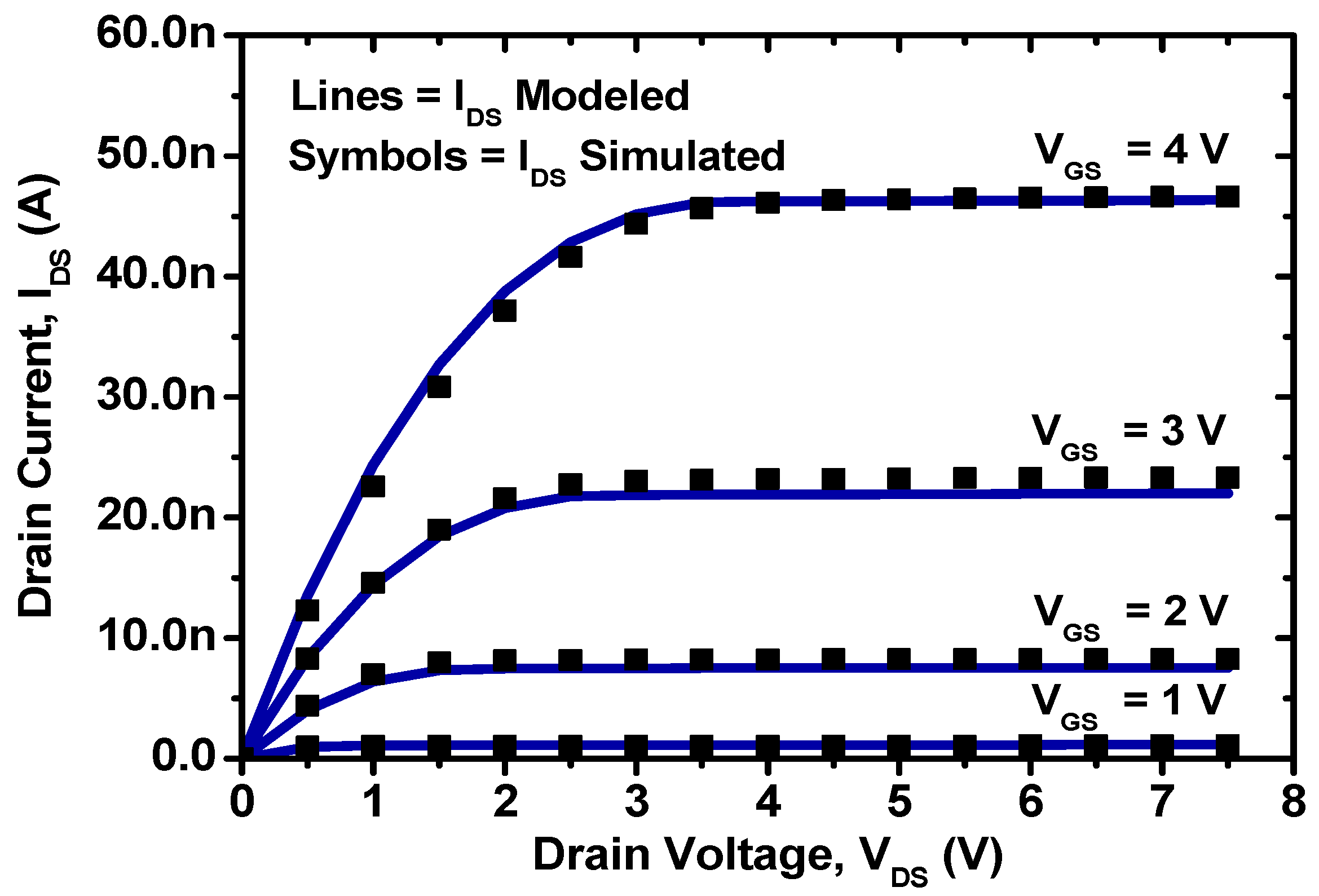

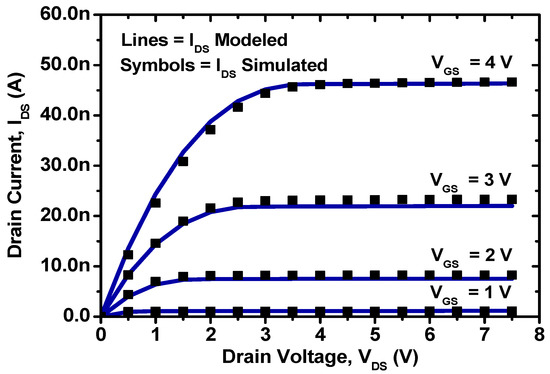

Figure 3 shows the comparison of modeled (lines) and simulated (symbols) characteristics IDS vs VDS for VGS = 1, 2, 3 and 4 Volts. It can be seen that the model is able to represent the behavior of the drain current at the sub-threshold and above-threshold regions for each curve corresponding to different VGS values with a small error for the whole VDS range.

Figure 3.

Comparison of modeled and simulated characteristic IDS vs VDS for various values of VGS = 1, 2, 3 and 4 Volts.

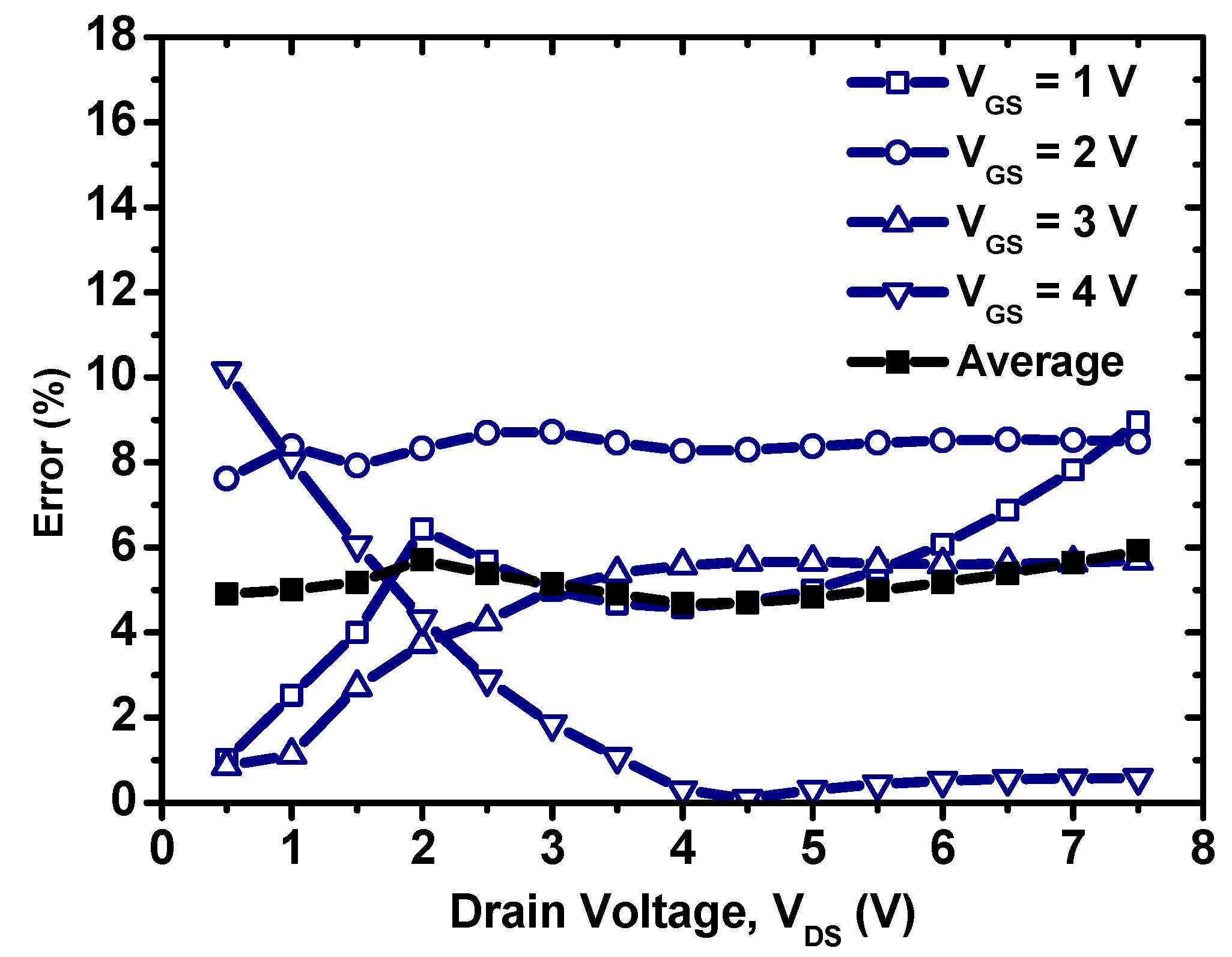

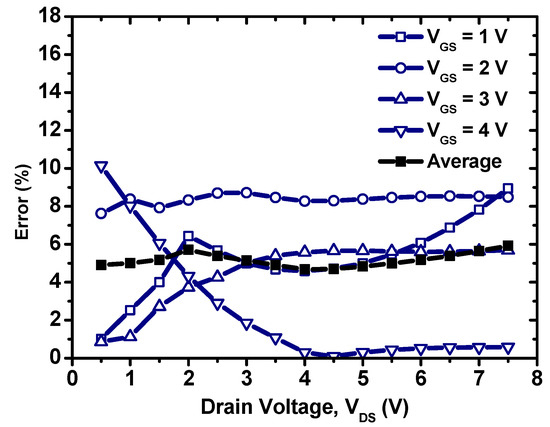

Figure 4 shows the absolute and average error between IDS characteristics modeled and simulated presented, which is computed with Equation (33). It can be seen; the maximum absolute error occurs for the IDS curve when VDS = 0.5 V and VGS = 4 V which is 9.8%. In addition, the average absolute error for all values of VGS is 5%, approximately.

Figure 4.

Absolute error computed for each simulated and modeled IDS curve showed in Figure 3 and the average absolute error for all curves.

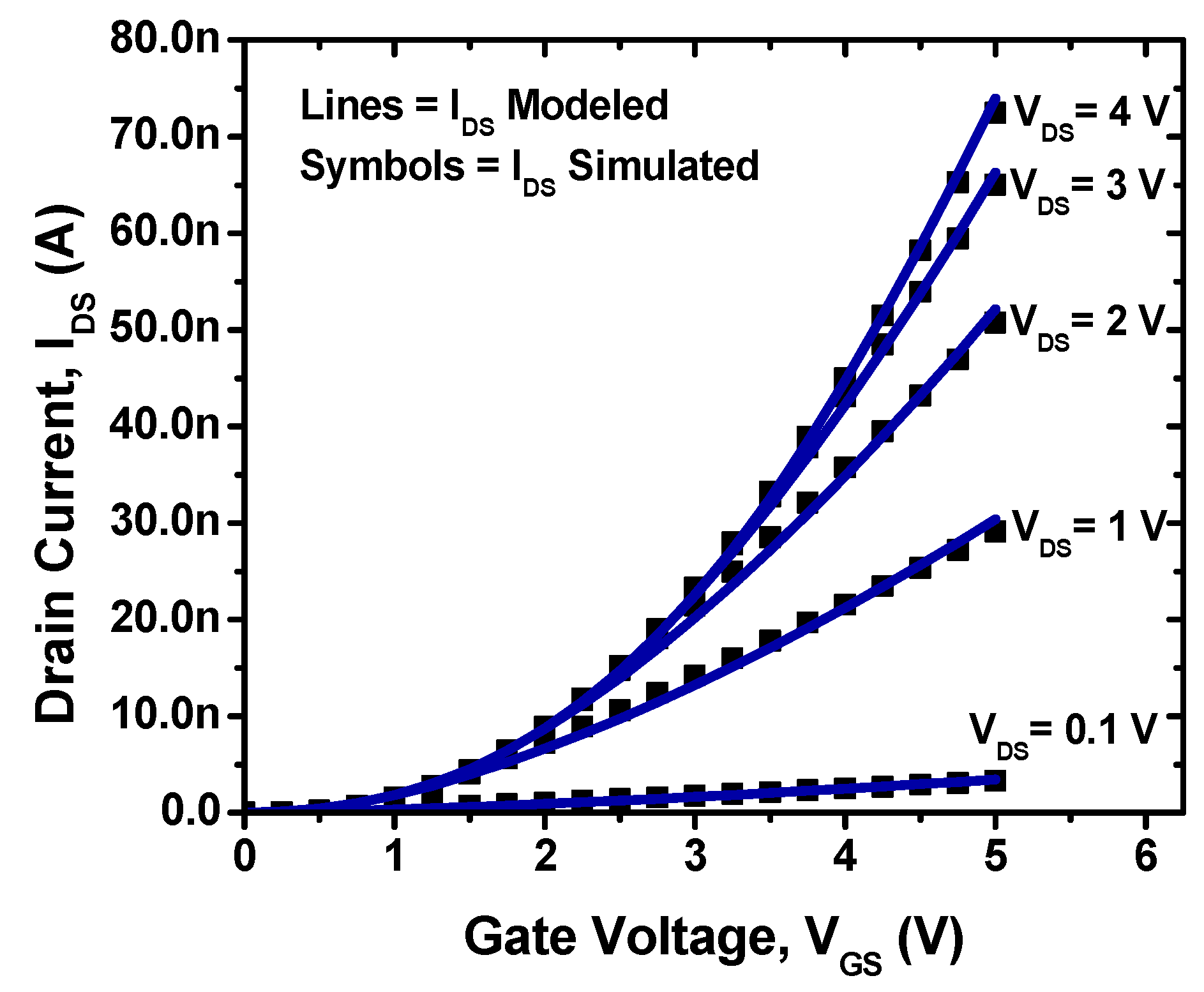

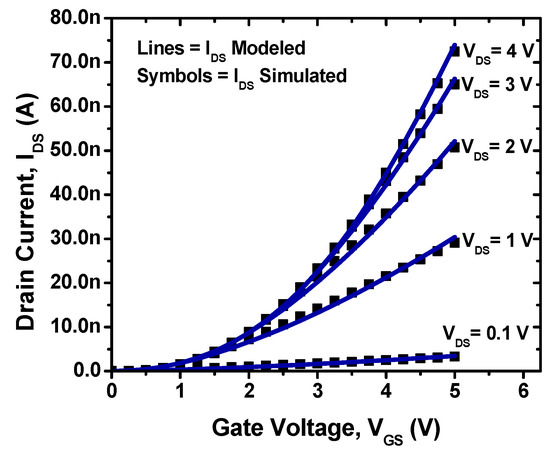

Figure 5 shows the comparison of the modeled (lines) and simulated (symbols) output characteristics IDS vs VGS for VDS = 0.1, 1, 2, 3 and 4 Volts. It can be seen that there exist a good fit between modeled and simulated IDS curves for both linear (VDS = 0.1 Volts, VGS > VTH) and saturation (VDS > VGS – VTH, VGS > VTH) regions of operation for a-SiGe:H TFT.

Figure 5.

Comparison of modeled and simulated output characteristics IDS vs VGS at VDS = 0.1, 1, 2, 3, and 4 Volts.

4. Conclusions

In this paper, was developed an analytical drain current model for a-SiGe:H TFTs that shows very good agreement with 2D numerical simulations which were used to validate it. The model considers free and localized charges into a-SiGe:H layer, characteristic temperature dependence and is able to work for sub- and above- threshold region of operation with a small absolute average error. In this sense, the proposed model has implication for development and prediction of electrical performance of TFTs at low frequencies based on amorphous semiconductors, such as a-SiGe:H, which is requested for analysis and design of circuits for large area and flexible electronic systems. Future work will include the fabrication and characterization of a-SiGe:H thin films transistors devices.

Author Contributions

S.S.-R., F.L.-H., and J.M.-C. develop the analytic drain current model. S.S.-R. and J.M.-R. made the simulation of thin film transistors using the INAOE fabrication process. S.S.-R., A.L.H.-M., F.L.-H., J.M.-R., and J.M.-C. wrote all the sections of the paper. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by project PRODEP “Modelado y Desarrollo de Microsensores CMOS-MEMS para la detección de diabetes”.

Acknowledgments

This work was supported by National Council of Science and Technology (CONACYT), México, through scholarship 386526, and by Program of Doctorate in Materials and Nanoscience of the Research Center in Micro and Nanotechnology of University of Veracruz (MICRONA-UV), México.

Conflicts of Interest

The authors declare no conflict of interest.

Appendix A

By substituting Equations (7) and (17) in Equation (19), we obtain:

Then, by integrating for ϕ(x) and evaluating from ϕ(x = 0) = ΦS to ϕ(x = TSC) = ΦB, we obtain:

where:

However, the second term inside of Equation (A2) is neglected (ϕB = 0). Thus, Equation (A2) can be rearranged as follows:

By integrating Equation (A5) with respect to y at both sides, and by evaluating the boundary conditions from y = 0 (source voltage, VS) to y = L (drain voltage, VD) in order to solve VCH(y), we obtain:

Then, by applying the Gauss’s Law along the Metal-Oxide-Semiconductor structure, and by substituting the electric field expression, we obtain:

where COX is the capacitance due to gate oxide per area unit, ϕs is surface potential at the oxide/semiconductor interface and VFB is flat band voltage.

By rewriting Equation (A8) as function of VCH(y), we obtain:

By differentiating VCH(y) for from Equation (A7), we obtain:

Substituting Equations (A10) and (A11) in Equation (A6), we get:

By rewriting Equation (A13), we obtain:

Finally, solving Equation (A14), we derive , which is given by:

where:

References

- Gao, X.; Lin, L.; Liu, Y.; Huang, X. LTPS TFT Process on Polyimide Substrate for Flexible AMOLED. IEEE J. Disp. Tech. 2015, 11, 666–669. [Google Scholar] [CrossRef]

- Xu, X.; Huang, B.; Fan, J.; Zhao, J.; Guo, X. Employing Drain-Bias Dependent Electrical Characteristics of Poly-Si TFTs to Improve Gray Level Control in Low Power AMOLED Displays. IEEE J. Elec. Devices Soc. 2019, 7, 489–494. [Google Scholar] [CrossRef]

- Lin, C.L.; Lai, P.C.; Lee, P.T.; Chen, B.S.; Chang, J.H.; Lin, Y.S. Highly Reliable a-Si: H TFT Gate Driver With Precharging Structure for In-Cell Touch AMLCD Applications. IEEE Trans. Elect. Devices 2019, 66, 1789–1796. [Google Scholar] [CrossRef]

- Wang, X.; Liu, Z.; Zhang, T. Flexible Sensing Electronics for Wearable/Attachable Health Monitoring. Small 2017, 13, 1602790. [Google Scholar] [CrossRef] [PubMed]

- Han, S.T.; Peng, H.; Sun, Q.; Venkatesh, S.; Chung, K.S.; Lau, S.C.; Zhou, Y.; Roy, V.A.L. An Overview of the Development of Flexible Sensors. Adv. Mat. 2017, 33, 1700375. [Google Scholar] [CrossRef] [PubMed]

- Fiore, V.; Battiato, P.; Abdinia, S.; Jacobs, S.; Chartier, I.; Coppard, R.; Klink, G.; Cantatore, E.; Ragonese, E.; Palmisano, G. An Integrated 13.56-MHz RFID Tag in a Printed Organic Complementary TFT Technology on Flexible Substrate. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1668–1677. [Google Scholar] [CrossRef]

- Mehlman, Y.; Kumar, P.; Ozatay, M.; Wagner, S.; Sturm, J.C.; Verma, N. Large-Area Electronics HF RFID Reader Array for Object-Detecting Smart Surfaces. IEEE Solid-State Circuits Lett. 2018, 1, 182–185. [Google Scholar] [CrossRef]

- Qin, Y.; Li, G.; Xu, Y.; Chen, R.; Deng, S.; Zhong, W.; Kwok, H.S. Low-Power Design for Unipolar ITO-Stabilized ZnO TFT RFID Code Generator Using Differential Logic Decoder. IEEE Trans. Electron Devices 2019, 66, 4768–4773. [Google Scholar] [CrossRef]

- Huang, Y.; Hekmatshoar, B.; Wagner, S.; Sturm, J.C. Top-Gate Amorphous Silicon TFT With Self-Aligned Silicide Source/Drain and High Mobility. IEEE Electron Device Lett. 2008, 29, 737–739. [Google Scholar] [CrossRef]

- Hu, H.H.; Huang, H.P. High-Frequency Performance of Trigate Poly Si Thin-Film Transistors by Microwave Annealing. IEEE Electron Device Lett. 2015, 36, 345–347. [Google Scholar] [CrossRef]

- Park, J.H.; Jang, G.S.; Kim, H.Y.; Lee, S.K.; Joo, S.K. High-Performance Poly-Si Thin-Film Transistor With High-k ZrTiO4 Gate Dielectric. IEEE Electron Device Lett. 2015, 36, 920–922. [Google Scholar] [CrossRef]

- Chen, Y.-J.E.; Lee, Y.-J.; Yu, Y.-H. Investigation of Polysilicon Thin-Film Transistor Technology for RF Applications. IEEE Trans. Microw. Theory Tech. 2010, 58, 3444–3451. [Google Scholar] [CrossRef]

- Wang, Y.; Yang, J.; Wang, H.; Zhang, J.; Li, H.; Zhu, G.; Song, A. Amorphous-InGaZnO Thin-Film Transistors Operating Beyond 1 GHz Achieved by Optimizing the Channel and Gate Dimensions. IEEE Trans. Electron. Devices 2018, 65, 1377–1382. [Google Scholar] [CrossRef]

- Hsu, S.-M.; He, J.-C.; Li, Y.-S.; Su, D.-Y.; Tsai, F.-Y.; Cheng, I.-C. Effect of Mechanical Strain on Electrical Performance of Flexible P-Type SnO Thin-Film Transistors. IEEE Trans. Electron Devices 2019, 66, 5183–5186. [Google Scholar] [CrossRef]

- Dominguez, M.; Rosales, P.; Torres, A.; Moreno, M.; Molina, J.; de la Hidalga, F.; Calleja, W. Ambipolar a-SiGe:H thin-film transistors fabricated at 200 °C. J. Non-Cryst. Solids 2012, 358, 2340–2343. [Google Scholar] [CrossRef]

- Shur, M.S. SPICE Models for Amorphous Silicon and Polysilicon Thin Film Transistors. J. Electrochem. Soc. 1997, 144, 2833. [Google Scholar] [CrossRef]

- Chen, S.S.; Kuo, J.B. An analytical a-Si:H TFT DC/capacitance model using an effective temperature approach for deriving a switching time model for an inverter circuit considering deep and tail states. IEEE Trans. Electron. Devices 1994, 41, 1169–1178. [Google Scholar] [CrossRef]

- Liu, Y.; Yao, R.H.; Li, B.; Deng, W.L. An Analytical Model Based on Surface Potential for a-Si:H Thin-Film Transistors. J. Disp. Technol. 2008, 4, 180–187. [Google Scholar] [CrossRef]

- Colalongo, L. A new analytical model for amorphous-silicon thin film transistor including tail and deep states. Solid State Electron. 2001, 45, 1525–1530. [Google Scholar] [CrossRef]

- Rosales-Quintero, P.; Torres-Jacome, A.; Murphy-Arteaga, R.; Landa-Vázquez, M. Electrical characterization of n-type a-SiGe:H/p-type crystalline-silicon heterojunctions. Semicond. Sci. Techn. 2003, 19, 366–372. [Google Scholar] [CrossRef]

- Silvaco International. Atlas User’s Manual. Available online: www.silvaco.com (accessed on 18 September 2019).

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).