Programming Pulse Width Assessment for Reliable and Low-Energy Endurance Performance in Al:HfO2-Based RRAM Arrays †

Abstract

1. Introduction

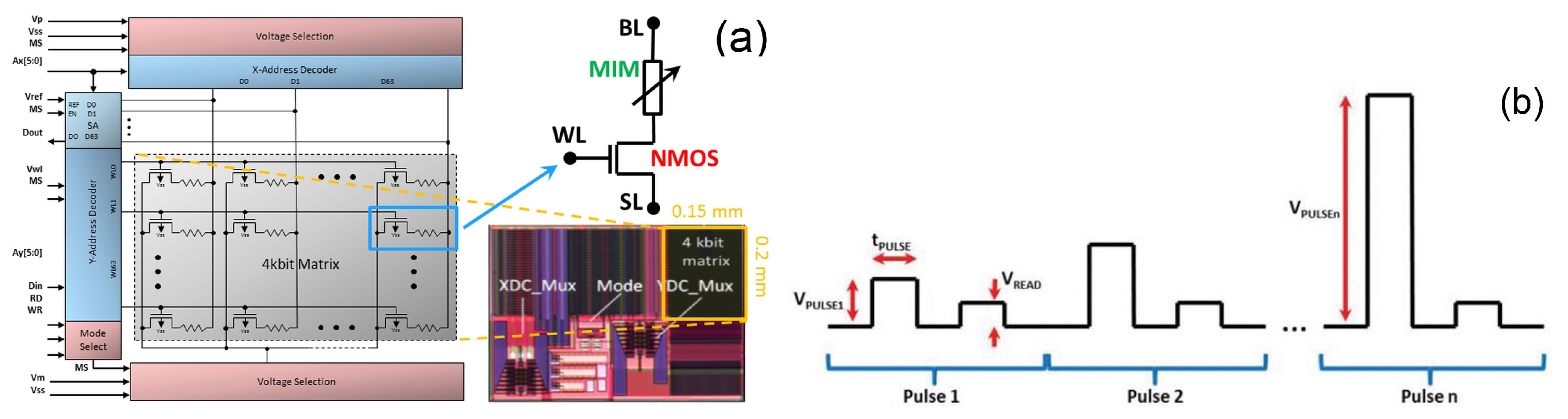

2. Experimental Description

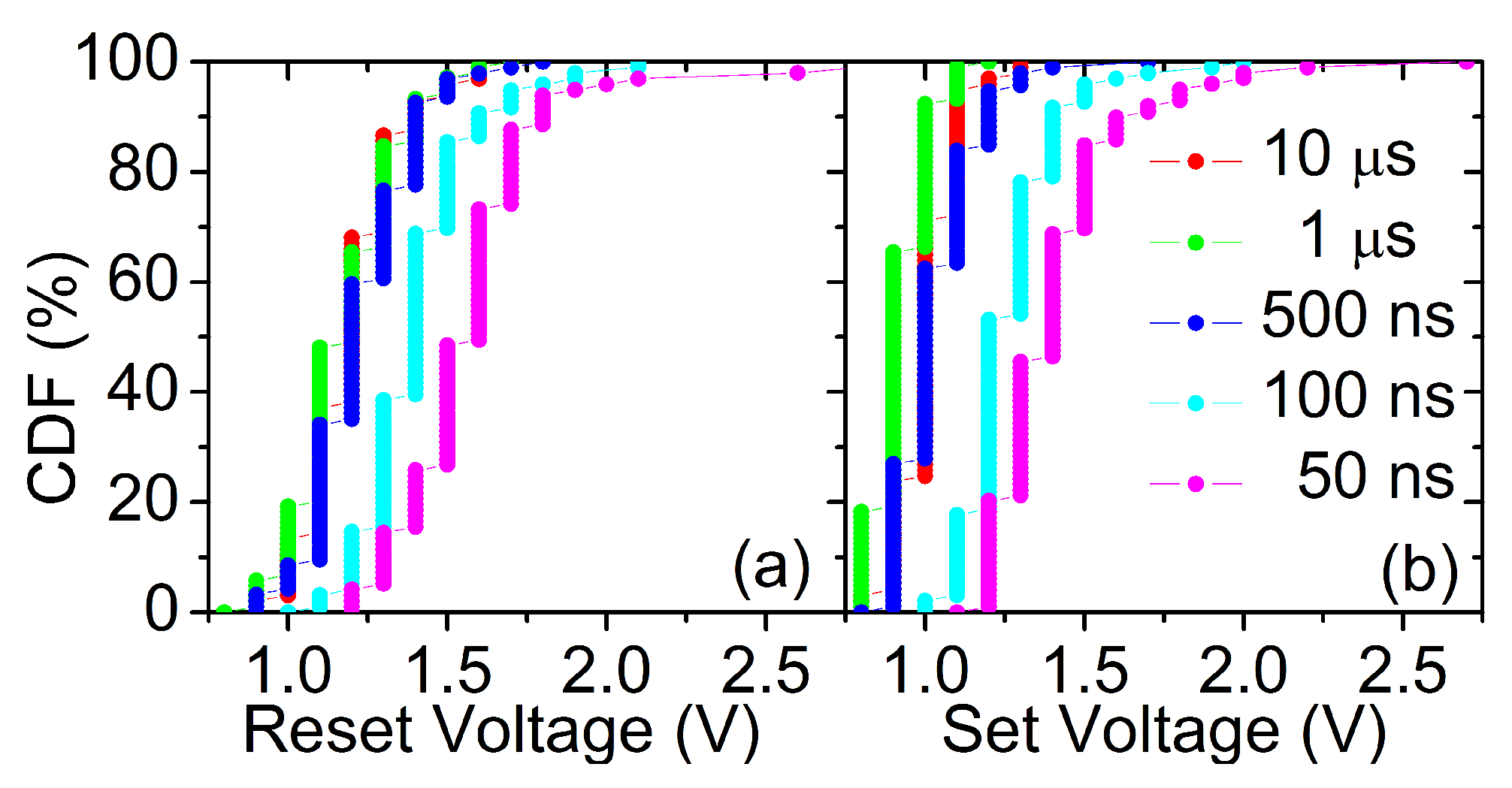

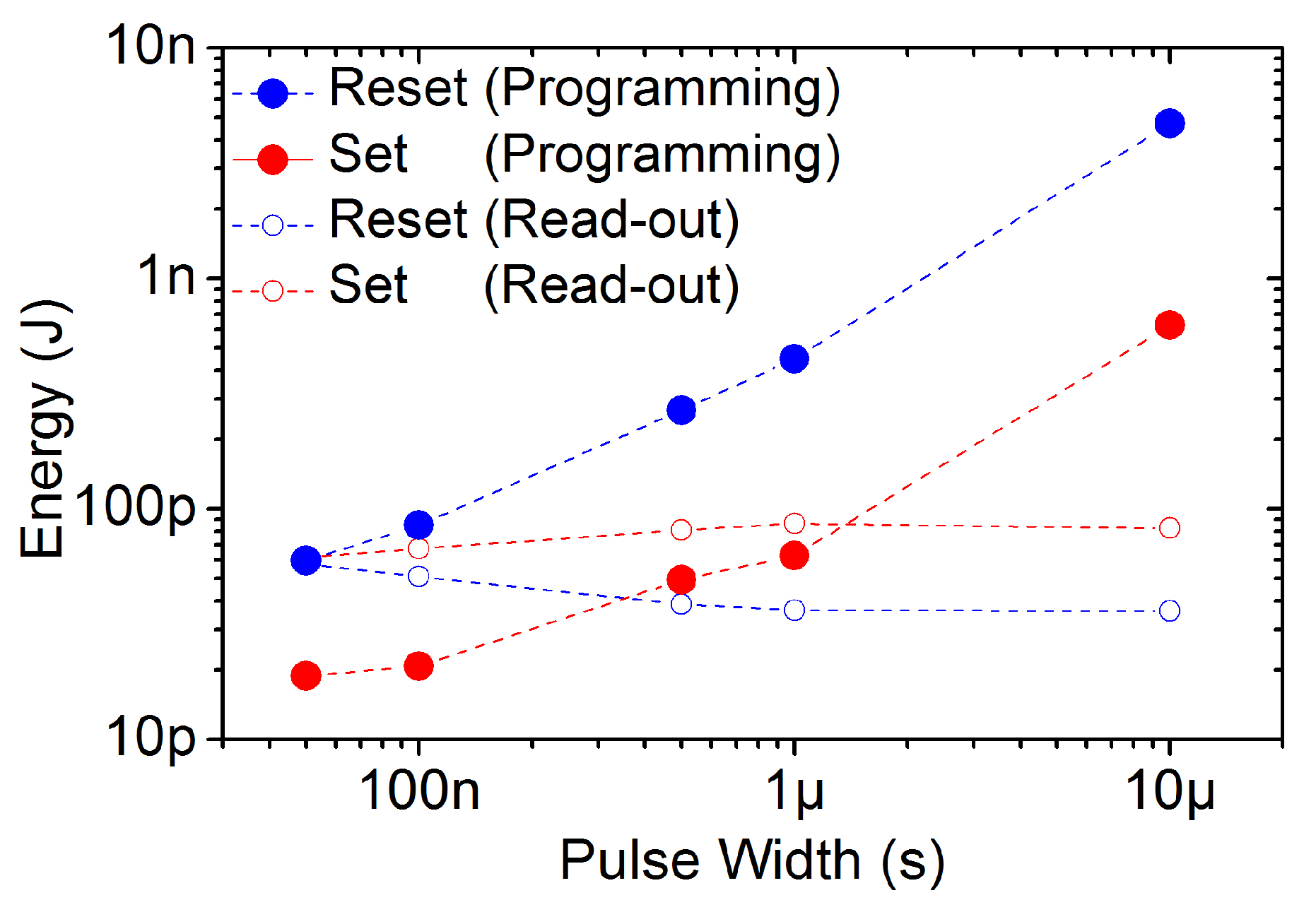

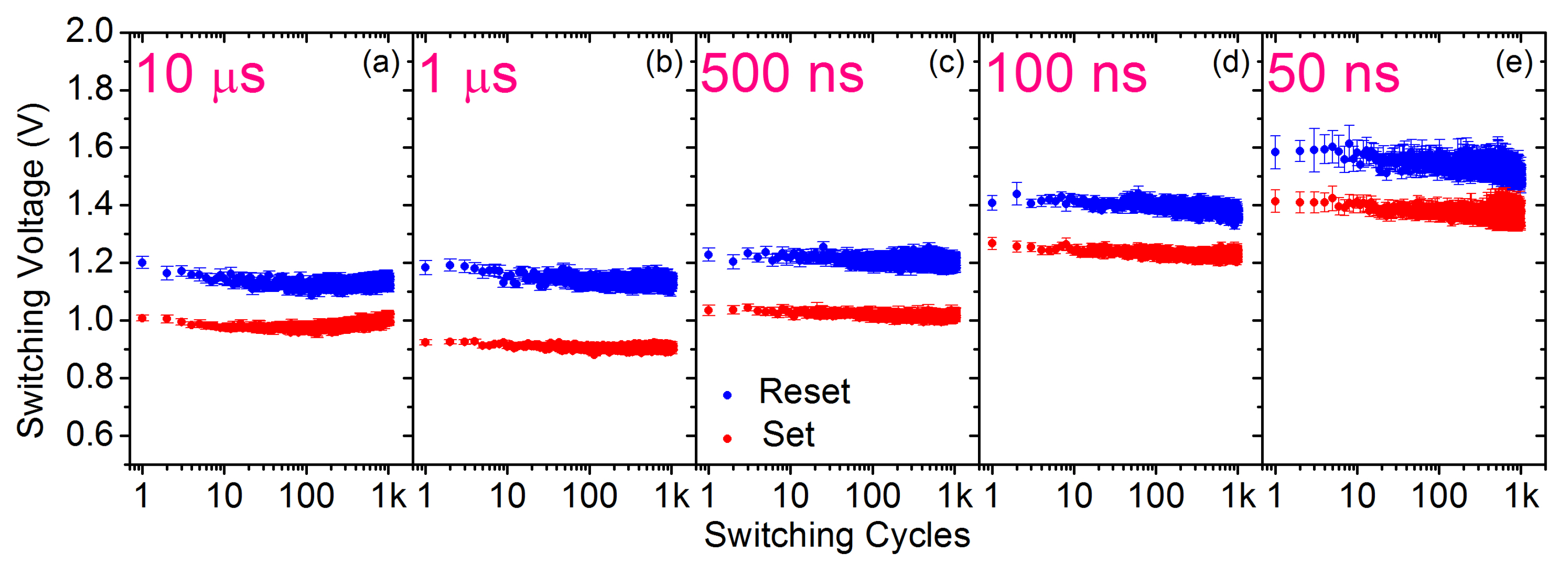

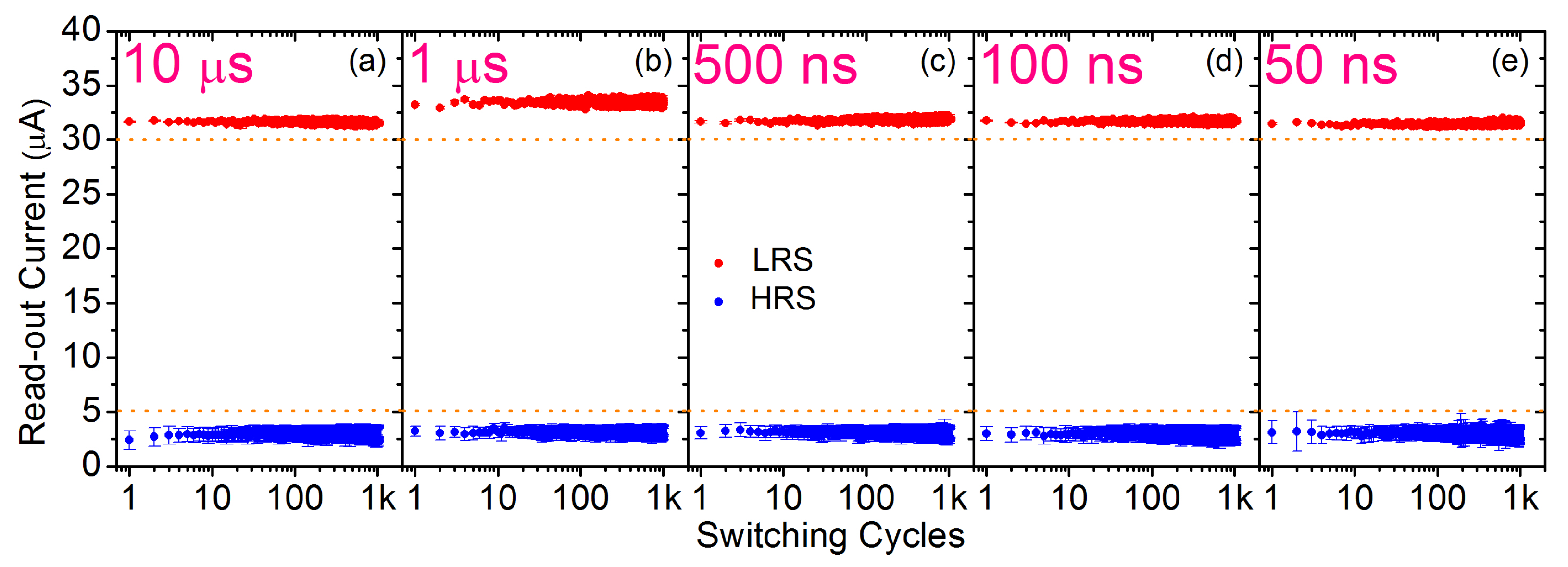

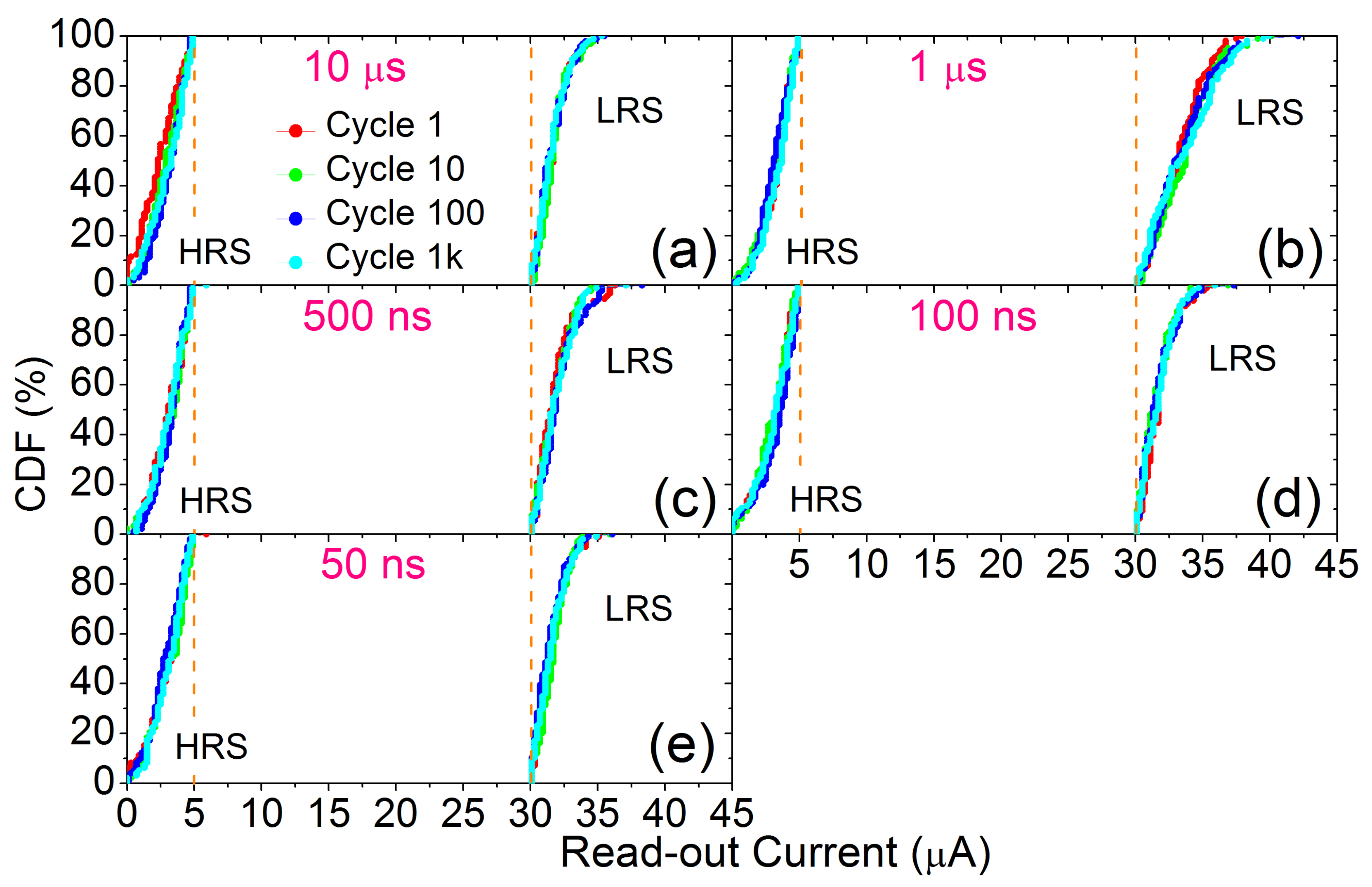

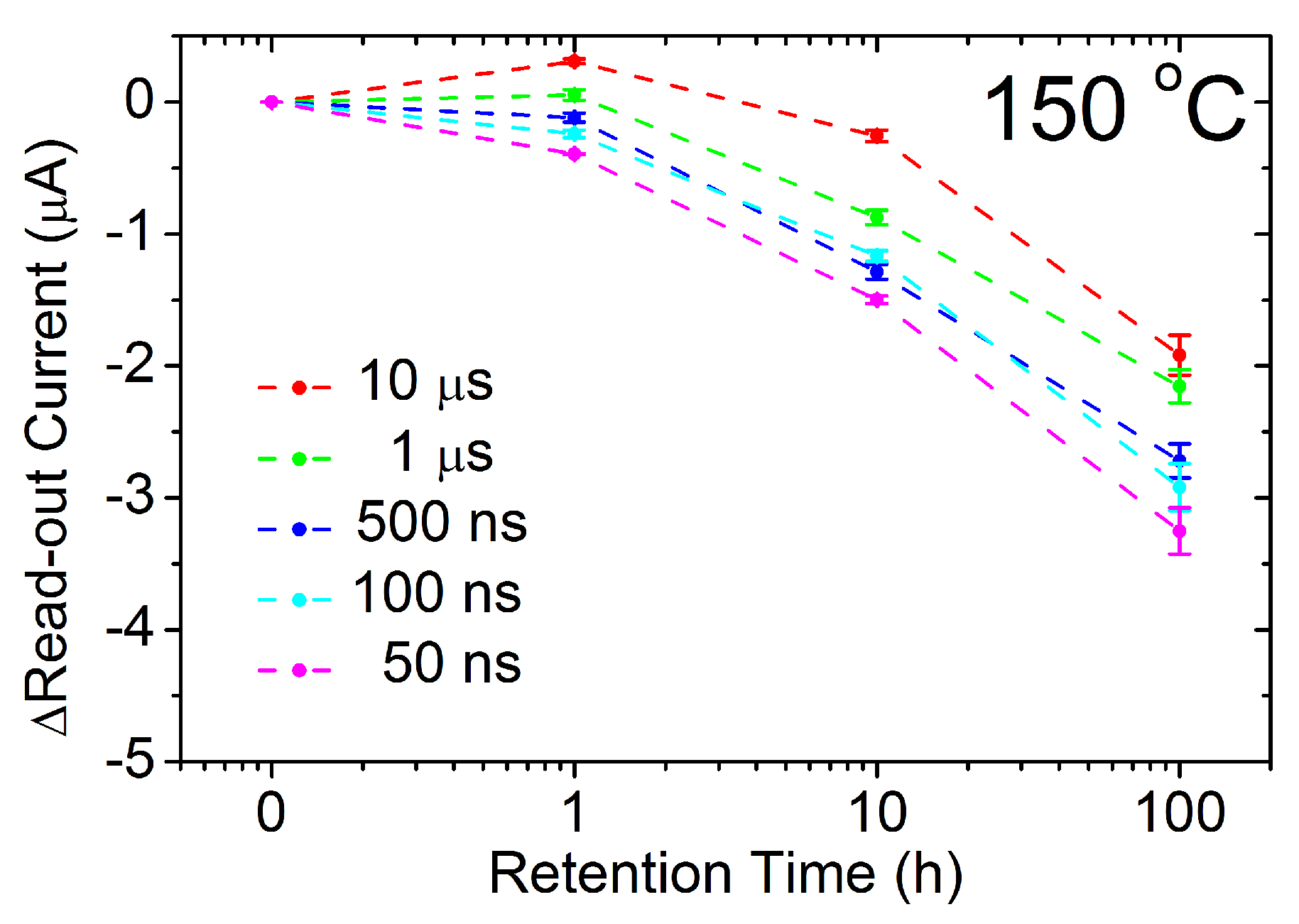

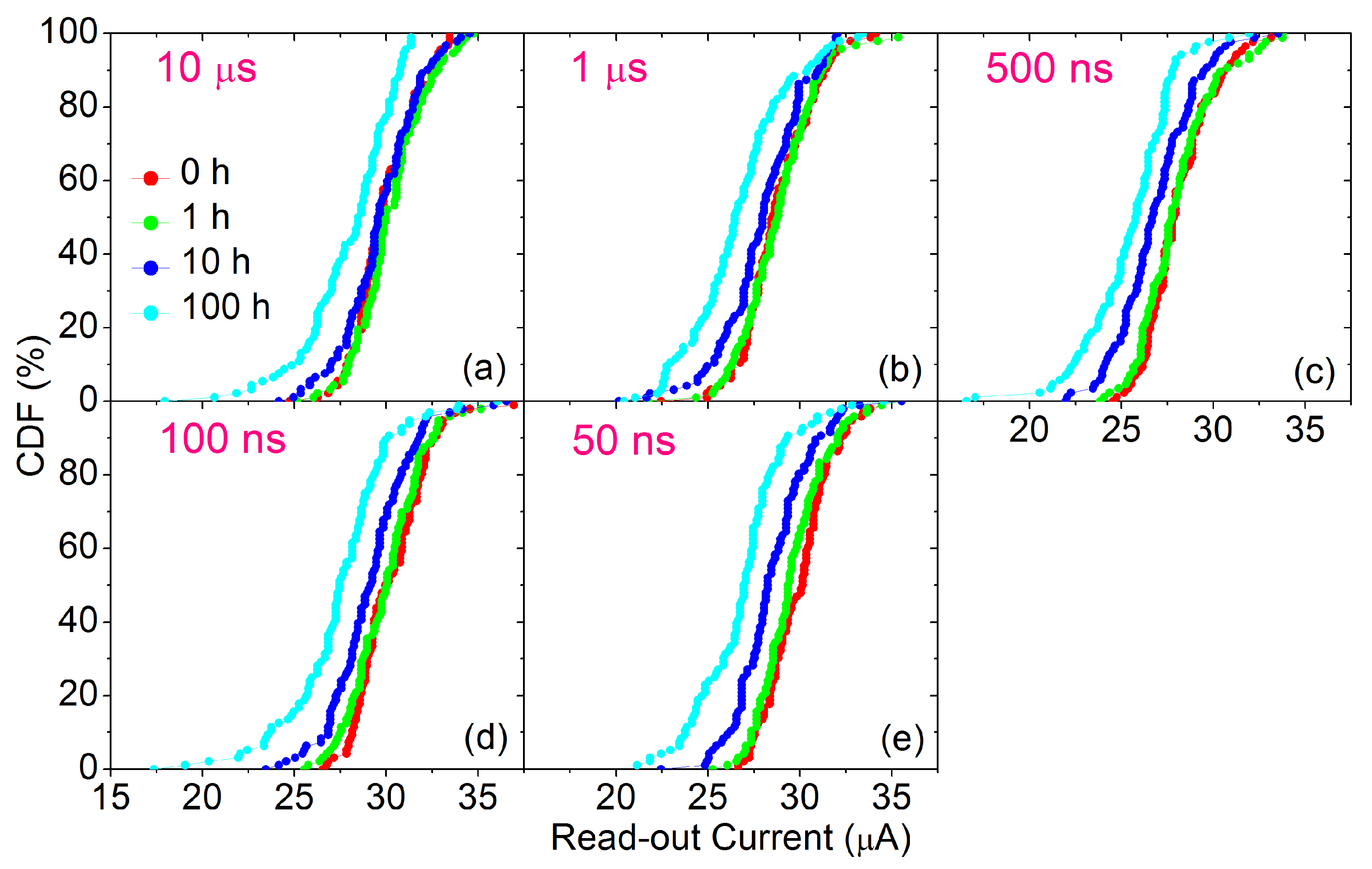

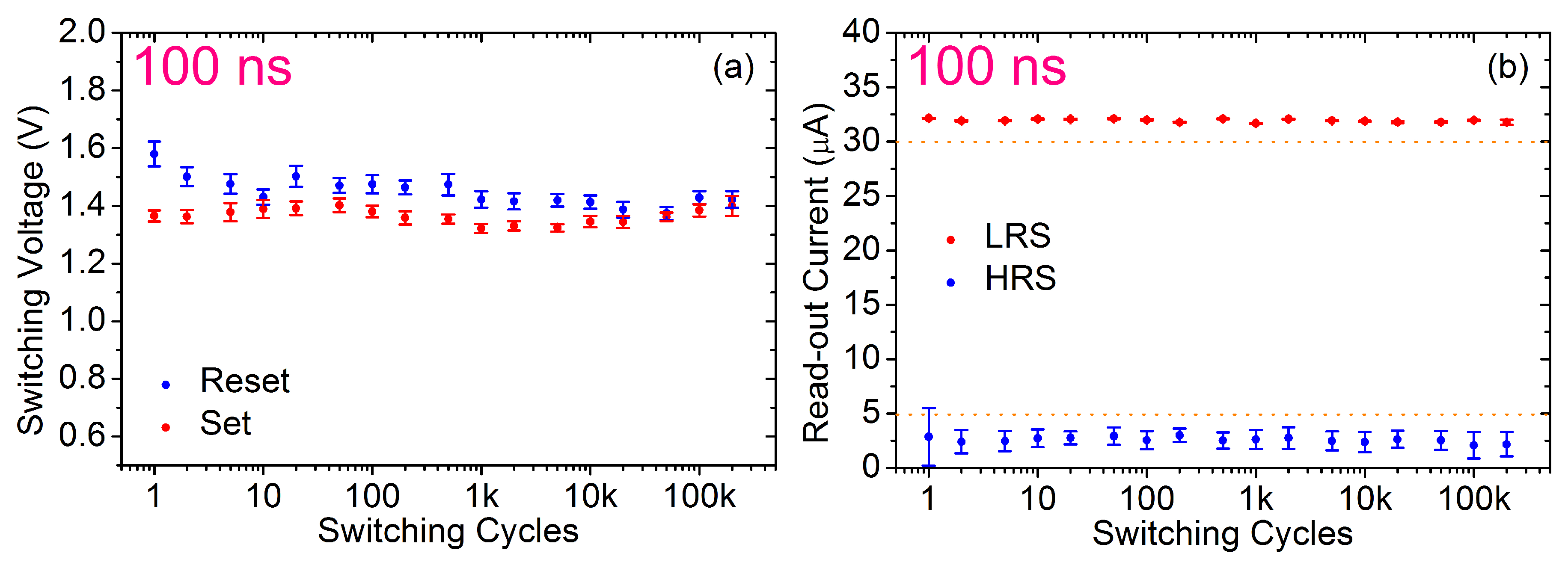

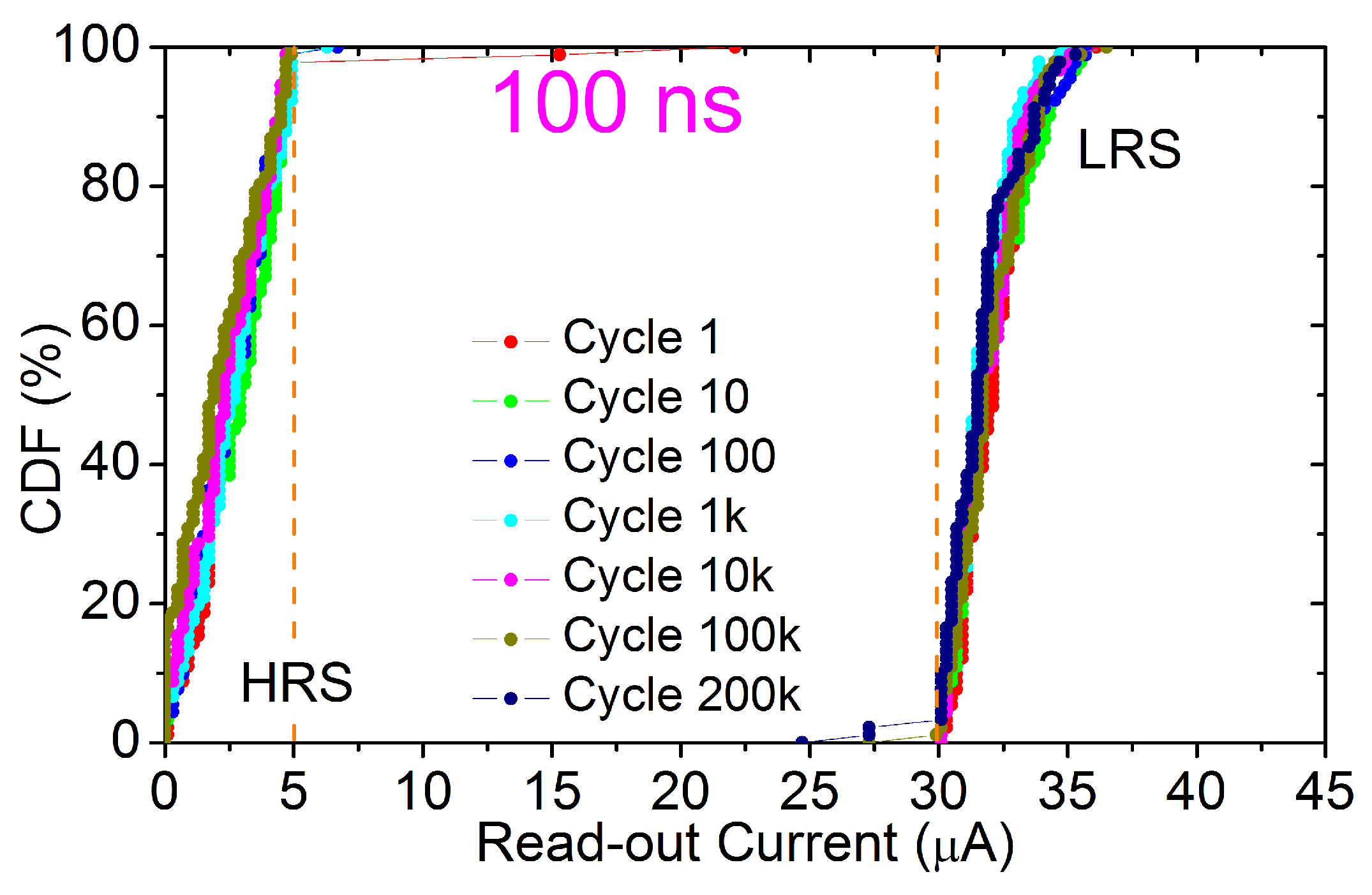

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Ielmini, D. Resistive switching memories based on metal oxides: Mechanisms, reliability and scaling. Semicond. Sci. Technol. 2016, 31, 063002. [Google Scholar] [CrossRef]

- Lee, H.Y.; Chen, P.S.; Wu, T.Y.; Chen, Y.S.; Wang, C.C.; Tzeng, P.J.; Lin, C.H.; Chen, F.; Lien, C.H.; Tsai, M.-J. Low power and high speed bipolar switching with a thin reactive Ti buffer layer in robust HfO2 based RRAM. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008. [Google Scholar]

- Chen, Y.Y.; Goux, L.; Pantisano, L.; Swerts, J.; Adelmann, C.; Mertens, S.; Afanasiev, V.V.; Wang, X.P.; Govoreanu, B.; Degraeve, R.; et al. Fully CMOS BEOL compatible HfO2 RRAM cell, with low (μA) program current, strong retention and high scalability, using an optimized Plasma Enhanced Atomic Layer Deposition (PEALD) process for TiN electrode. In Proceedings of the 2011 IEEE International Interconnect Technology Conference, Dresden, Germany, 8–12 May 2011. [Google Scholar]

- Jeong, D.S.; Thomas, R.; Katiyar, R.S.; Scott, J.F.; Kohlstedt, H.; Petraru, A.; Hwang, C.S. Emerging memories: Resistive switching mechanisms and current status. Rep. Prog. Phys. 2012, 75, 076502. [Google Scholar] [CrossRef] [PubMed]

- Lin, Y.S.; Zeng, F.; Tang, S.G.; Liu, H.Y.; Chen, C.; Gao, S.; Wang, Y.G.; Pan, F. Resistive switching mechanisms relating to oxygen vacancies migration in both interfaces in Ti/HfOx/Pt memory devices. J. Appl. Phys. 2013, 113, 064510. [Google Scholar] [CrossRef]

- Traore, B.; Blaise, P.; Vianello, E.; Perminola, L.; De Salvo, B.; Nishi, Y. HfO2-based RRAM: Electrode effects, Ti/HfO2 interface, charge injection, and oxygen defects diffusion through experiment and ab initio calculations. IEEE Trans. Electron Devices 2016, 63, 360–368. [Google Scholar] [CrossRef]

- Lee, H.Y.; Chen, Y.S.; Chen, P.S.; Gu, P.Y.; Hsu, Y.Y.; Wang, S.M.; Liu, W.H.; Tsai, C.H.; Sheu, S.S.; Chiang, P.C.; et al. Evidence and solution of over-RESET problem for HfOx based resistive memory with sub-ns switching speed and high endurance. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 19.7.1–19.7.4. [Google Scholar]

- Chien, W.-C.; Lee, M.-H.; Lee, F.-M.; Lin, Y.-Y.; Lung, H.-L.; Hsieh, K.-Y.; Lu, C.-Y. A multi-level 40nm WOX resistive memory with excellent reliability. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 31.5.1–31.5.4. [Google Scholar]

- Kim, H.; Sah, M.P.d.; Yang, C.; Roska, T.; Chua, L.O. Neural synaptic weighting with a pulse-based memristor circuit. IEEE Trans. Circuits Syst. I 2012, 59, 148–158. [Google Scholar] [CrossRef]

- Eshraghian, J.K.; Kang, S.-M.; Baek, S.; Orchard, G.; Iu, H.H.-C.; Lei, W. Analog weights in ReRAM DNN accelerators. In Proceedings of the 2019 IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), Hsinchu, Taiwan, 19–20 March 2019; pp. 267–271. [Google Scholar]

- Azghadi, M.R.; Chen, Y.-C.; Eshraghian, J.K.; Chen, J.; Lin, C.-Y.; Amirsoleimani, A.; Mehonic, A.; Kenyon, A.J.; Fowler, B.; Lee, J.C.; et al. Complementary metal-oxide semiconductor and memristive hardware for neuromorphic computing. Adv. Intell. Syst. 2020, 2, 1900189. [Google Scholar] [CrossRef]

- Fantini, A.; Goux, L.; Clima, S.; Degraeve, R.; Redolfi, A.; Adelmann, C.; Polimeni, G.; Chen, Y.Y.; Komura, M.; Belmonte, A.; et al. Engineering of Hf1-xAlxOy amorphous dielectrics for high-performance RRAM applications. In Proceedings of the 2014 IEEE 6th International Memory Workshop (IMW), Taipei, Taiwan, 18–21 May 2014. [Google Scholar]

- Wang, C.; Wu, H.; Gao, B.; Dai, L.; Deng, N.; Sekar, D.C.; Lu, Z.; Kellam, M.; Bronner, G.; Qian, H. Relaxation effect in RRAM arrays: Demonstration and characteristics. IEEE Electron Device Lett. 2016, 37, 182–185. [Google Scholar] [CrossRef]

- Perez, E.; Grossi, A.; Zambelli, C.; Olivo, P.; Roelofs, R.; Wenger, C. Reduction of the cell-to-cell variability in Hf1-xAlxOy based RRAM arrays by using program algorithms. IEEE Electron Device Lett. 2017, 38, 175–178. [Google Scholar] [CrossRef]

- Perez, E.; Mahadevaiah, M.K.; Zambelli, C.; Olivo, P.; Wenger, C. Data retention investigation in Al:HfO2-based resistive random access memory arrays by using high-temperature accelerated tests. J. Vac. Sci. Technol. B 2019, 37, 012202. [Google Scholar] [CrossRef]

- Ossorio, O.G.; Perez, E.; Dueñas, S.; Castan, H.; Garcia, H.; Wenger, C. Effective Reduction of the Programing Pulse Width in Al:HfO2-based RRAM Arrays. In Proceedings of the Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon, Grenoble, France, 1–3 April 2019. [Google Scholar]

- Perez, E.; Maldonado, D.; Acal, C.; Ruiz-Castro, J.E.; Alonso, F.J.; Aguilera, A.M.; Jimenez-Molinos, F.; Wenger, C.; Roldan, J.B. Analysis of the statistics of device-to-device and cycle-to-cycle variability in TiN/Ti/Al:HfO2/TiN RRAMs. Microelectron. Eng. 2019, 214, 104–109. [Google Scholar] [CrossRef]

- Perez, E.; Grossi, A.; Zambelli, C.; Olivo, P.; Wenger, C. Impact of the incremental programming algorithm on the filament conduction in HfO2-based 1T-1R RRAM arrays. J. Electron Device Soc. 2017, 5, 64–68. [Google Scholar] [CrossRef]

- Grossi, A.; Zambelli, C.; Olivo, P.; Miranda, E.; Stikanov, V.; Walczyk, C.; Wenger, C. Electrical characterization and modeling of pulse-based forming techniques in RRAM arrays. Solid State Electron. 2016, 115, 17–25. [Google Scholar] [CrossRef]

- Perez, E.; Mahadevaiah, M.K.; Zambelli, C.; Olivo, P.; Wenger, C. Characterization of the interface-driven 1st Reset operation in HfO2-based 1T1R RRAM devices. Solid State Electron. 2019, 159, 51–56. [Google Scholar] [CrossRef]

- Balatti, S.; Ambrogio, S.; Wang, Z.-Q.; Sills, S.; Calderoni, A.; Ramaswamy, N.; Ielmini, D. Understanding pulsed-cycling variability and endurance in HfOx RRAM. In Proceedings of the 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 19–23 April 2015; pp. 5B.3.1–5B.3.6. [Google Scholar]

- Chen, C.Y.; Fantini, A.; Degraeve, R.; Redolfi, A.; Groeseneken, G.; Goux, L.; Kar, G.S. Statistical investigation of the impact of program history and oxide-metal interface on OxRRAM retention. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 4.6.1–4.6.4. [Google Scholar]

- Grossi, A.; Zambelli, C.; Olivo, P.; Crespo-Yepes, A.; Martin-Martinez, J.; Rodriguez, R.; Nafria, M.; Perez, E.; Wenger, C. Electrical characterization and modeling of 1T-1R RRAM arrays with amorphous and poly-crystalline HfO2. Solid State Electron. 2017, 128, 187–193. [Google Scholar] [CrossRef]

- Miranda, E.A.; Walczyk, C.; Wenger, C.; Schroeder, T. Model for the resistive switching effect in HfO2 MIM structures based on the transmission properties of narrow constrictions. IEEE Electron Device Lett. 2010, 31, 609–611. [Google Scholar] [CrossRef]

- Ambrogio, S.; Balatti, S.; Gilmer, D.C.; Ielmini, D. Analytical Modeling of oxide-based bipolar resistive memories and complementary resistive switches. IEEE Trans. Electron Devices 2014, 61, 2378–2386. [Google Scholar] [CrossRef]

- Chen, C.Y.; Fantini, A.; Goux, L.; Degraeve, R.; Clima, S.; Redolfi, A.; Groeseneken, G.; Jurczak, M. Programming-conditions solutions towards suppression of retention tails of scaled oxide-based RRAM. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 10.6.1–10.6.4. [Google Scholar]

- Gu, P.-Y.; Chen, Y.-S.; Lee, H.-Y.; Chen, P.-S.; Liu, W.-H.; Chen, W.-S.; Hsu, Y.-Y.; Chen, F.; Tsai, M.-J. Scalability with silicon nitride encapsulation layer for Ti/HfOx pillar RRAM. In Proceedings of the 2010 International Symposium on VLSI Technology, System and Application, Hsinchu, Taiwan, 26–28 April 2010; pp. 146–147. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pérez, E.; González Ossorio, Ó.; Dueñas, S.; Castán, H.; García, H.; Wenger, C. Programming Pulse Width Assessment for Reliable and Low-Energy Endurance Performance in Al:HfO2-Based RRAM Arrays. Electronics 2020, 9, 864. https://doi.org/10.3390/electronics9050864

Pérez E, González Ossorio Ó, Dueñas S, Castán H, García H, Wenger C. Programming Pulse Width Assessment for Reliable and Low-Energy Endurance Performance in Al:HfO2-Based RRAM Arrays. Electronics. 2020; 9(5):864. https://doi.org/10.3390/electronics9050864

Chicago/Turabian StylePérez, Eduardo, Óscar González Ossorio, Salvador Dueñas, Helena Castán, Héctor García, and Christian Wenger. 2020. "Programming Pulse Width Assessment for Reliable and Low-Energy Endurance Performance in Al:HfO2-Based RRAM Arrays" Electronics 9, no. 5: 864. https://doi.org/10.3390/electronics9050864

APA StylePérez, E., González Ossorio, Ó., Dueñas, S., Castán, H., García, H., & Wenger, C. (2020). Programming Pulse Width Assessment for Reliable and Low-Energy Endurance Performance in Al:HfO2-Based RRAM Arrays. Electronics, 9(5), 864. https://doi.org/10.3390/electronics9050864