2.1. Low-Parasitic, High Speed Gate Driver

Driving WBG devices requires a fast and capable gate driver circuit. The function of the gate driver in power electronic circuits is to isolate the logic and control portions of the circuit from the power path, in addition to providing the device with the proper turn-on and turn-off voltages or currents. For example, a control logic level of 1, or an analog voltage level of 5 V used to turn on a SiC MOSFET, must produce a 15 V differential voltage between the gate and the source terminals of the MOSFET; while a turn-off signal will require a −3 V differential between the same terminals. It is important to note that in many power electronic circuits the source terminal of the switch is most likely floating, which requires a floating differential gate drive output.

At the same time, the gate driver circuit should not affect or slow down the device’s operation. This requires special attention to the parasitic gate loop inductance, which may cause delayed switching, ringing, and even cause the switch to unintentionally turn-on, which may result in the destruction of the switch.

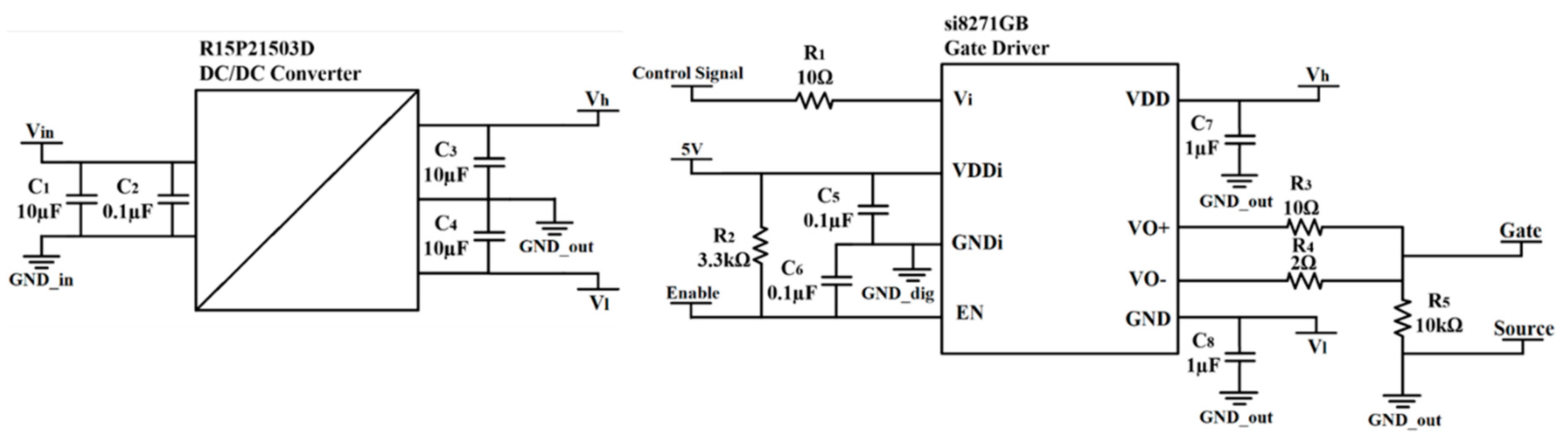

To minimize the gate loop area, and maximize the flexibly of the testing bed, a modular design approach was followed. The gate driver circuit board was separated from the main test board, which allowed changing the gate driver board easily to perform tests at different gate voltages. A schematic of the gate driver circuit is shown in

Figure 1.

The gate driver circuit consisted of two main components, the gate driver IC, and the DC/DC converter. The gate driver IC’s main job was to receive the switching logic signal from the controller and output a similar shaped signal, while providing isolation between the logic side and the power side. The most important characteristics of a gate driver IC are its switching capabilities and its common mode transient immunity (CMTI) [

6]. The Silicon Labs si8271 GB gate driver IC was selected for this design, as it provided sufficient current, high switching speed, and very high CMTI of over 200 kV/μs. Another reason for selecting this IC was its separate pull-up/down outputs, which allowed controlling of the turn-on and turn-off slew rates with minimal external components, thus minimizing the gate loop parasitics and achieving a sharper gate driving signal. The slew rate could be controlled by changing the output resistors, which is a thin-film of low ESL resistors with the smallest possible package footprint to minimize the gate loop inductance.

The DC/DC converter provides two main functions. It supplies the appropriate high and low voltages to the gate driver IC, and provides galvanic isolation between the power side of the gate driver circuit and any external circuitry. The RECOM R15P21503D 2 W isolated DC/DC converter was selected for this research. This converter outputs +15 V and −3 V, and provides 6.4 kVDC of voltage isolation. Four decoupling capacitors were used to filter noise and voltage ripple.

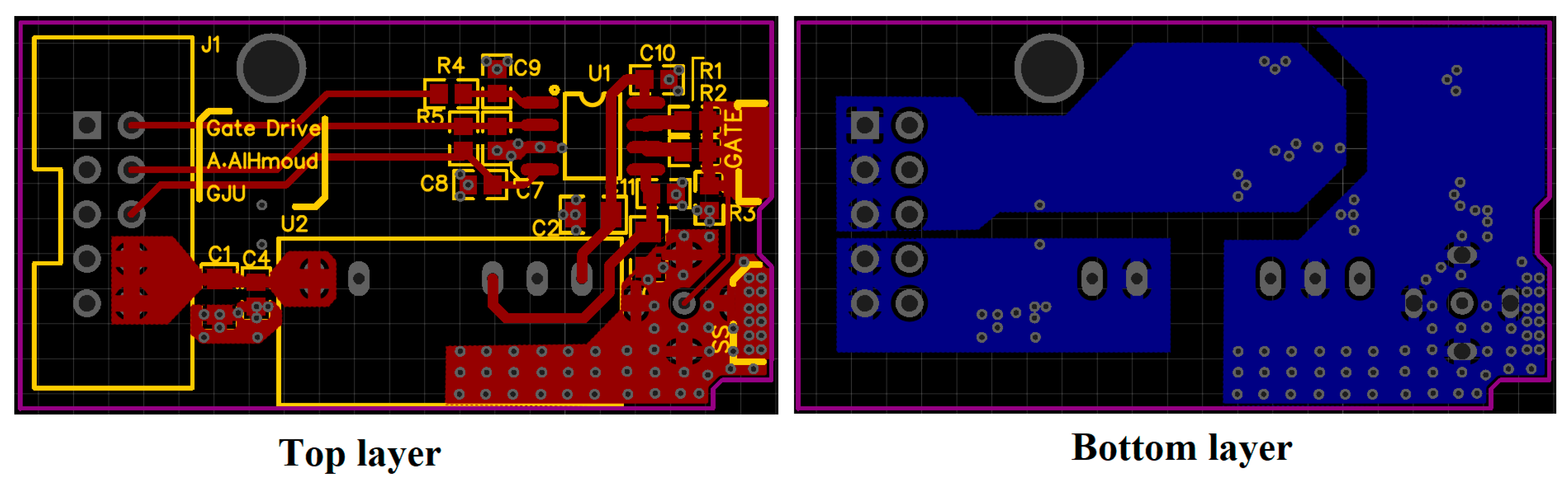

The gate drives were designed on a separate PCB. The gate driver board can be directly soldered to the DUT’s gate and source pins, as close to the package as possible, forming a Kelvin connection with the source pin. This approach minimized the loop area by bypassing the long leads of the DUT, and sharing the least length with the power loop. A 0.8 mm 2-layer board was used, reducing the gate loop area at a reasonable price. The gate driver PCB layout can be seen in

Figure 2 and the populated board soldered to the DUT in

Figure 3.

2.2. Double Pulse Test Circuit

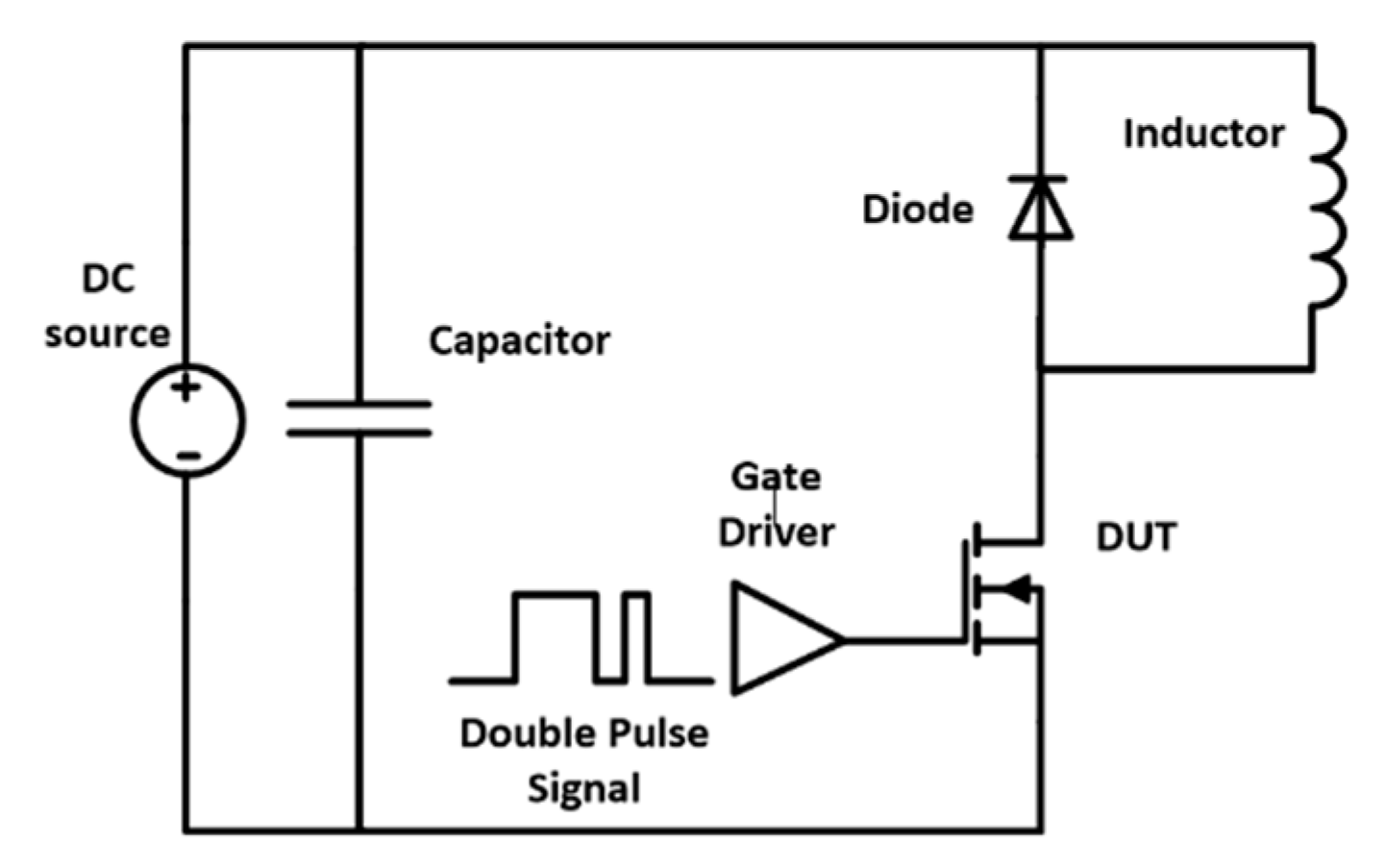

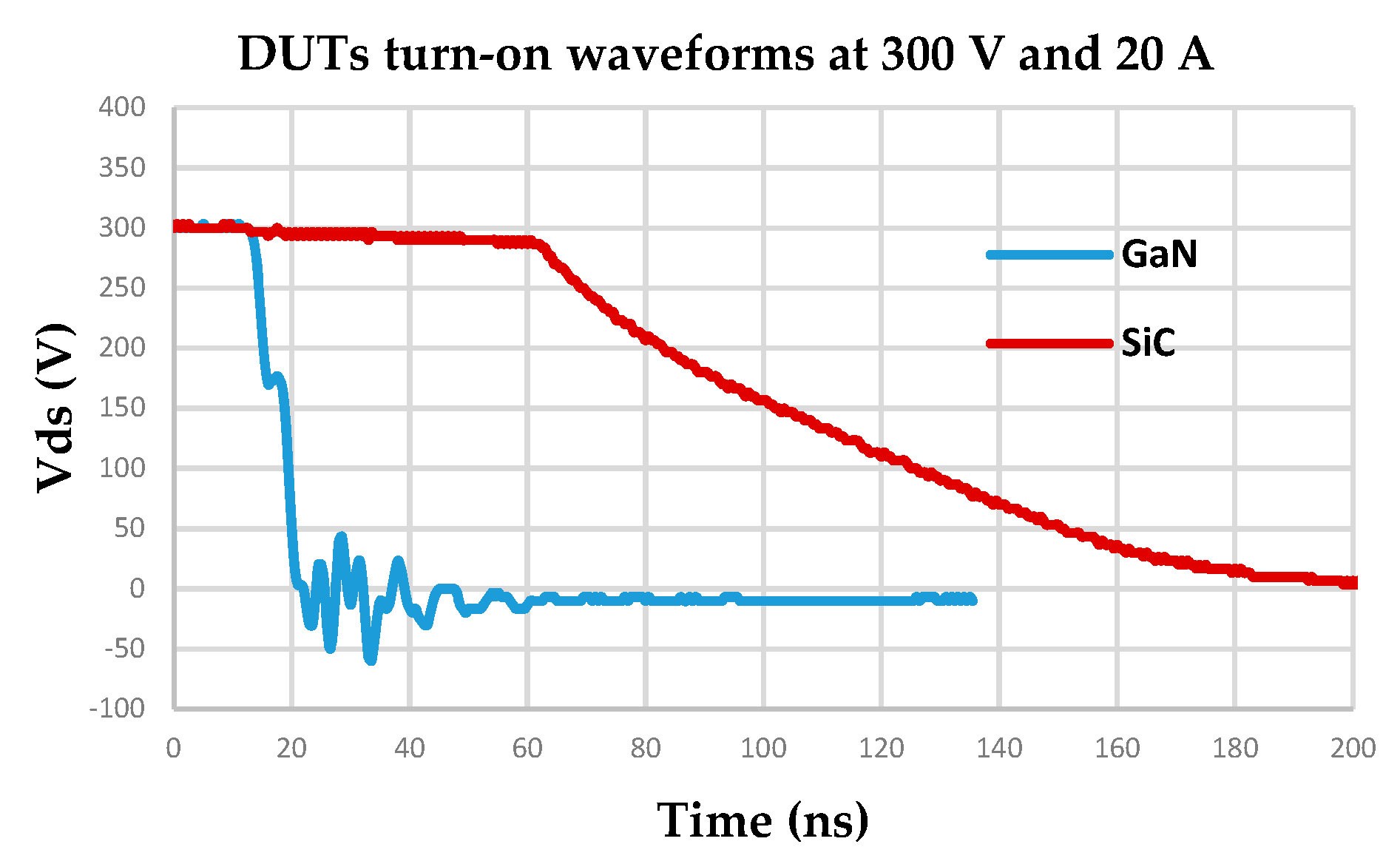

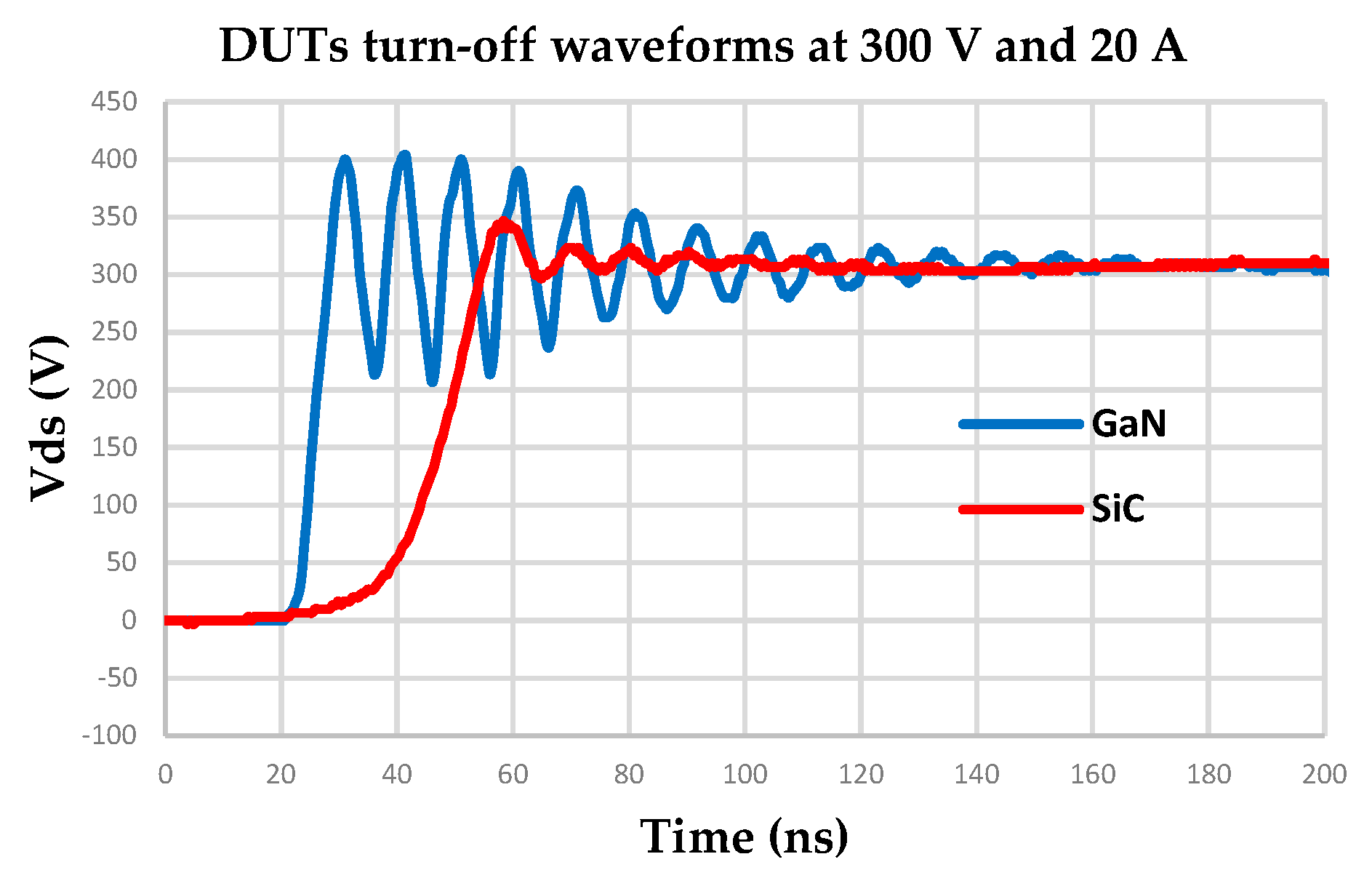

The double pulse method is widely used in industry to test power semiconductor devices, and to evaluate their dynamic performance. As the name suggests, two pulses are sent to the device under test (DUT). By regulating the DC bus voltage and the first pulse’s duration, the DUT’s dynamic characteristics can be evaluated under any desired I-V condition. A typical double pulse tester circuit is shown in

Figure 4.

A pulse is first applied to the DUT, closing the circuit, and charging the inductor. Since the inductor will gradually allow more current to flow, the longer the duration of the pulse, the higher the current flowing through the circuit. When the desired testing current is reached the pulse ends, and the switch turns off. This will capture the turn-off characteristics of the switch at the applied voltage and current.

The gate signal is kept low for a long enough duration for all the transients to reach steady state. Next, a second pulse is applied and the DUT is turned on. This captures the turn-on characteristics under the same voltage and current. The pulse is kept high long enough to reach a steady state, then the signal goes low to turn off the DUT and to allow the inductor to discharge through the freewheeling diode. Using a high inductive load, the current magnitude change between the two pulses would be small, and may be neglected, and since the two pulses happen in a short amount of time, the DUT temperature is not affected [

9,

15]. A typical DPT waveform is shown in

Figure 5.

Although the main principle of the DPT is not complicated, designing a DPT to characterize WBG devices is a challenging task. The main challenge was to build a test bed that would allow the capture of the actual device performance, and not the effects of the test bed parasitics. As WBG devices operate at both higher frequency and higher power than conventional devices, the influence of parasitics may entirely conceal the actual performance of the DUT.

An equivalent circuit showing the parasitic elements existing in a DPT is illustrated in

Figure 6. There are mainly seven parasitic elements in the DPT: Lds, Cds, and Cd in the power loop, Lgs and Cgs in the gate loop, and Lcm and Cgd shared by both loops. The main issues caused by these parasitic elements are power loop ringing and overshoot voltages, which cause electromagnetic interference and reliability issues. The biggest contributors to these issues are the power loop inductance Lds and the diode capacitance Cd [

6,

16].

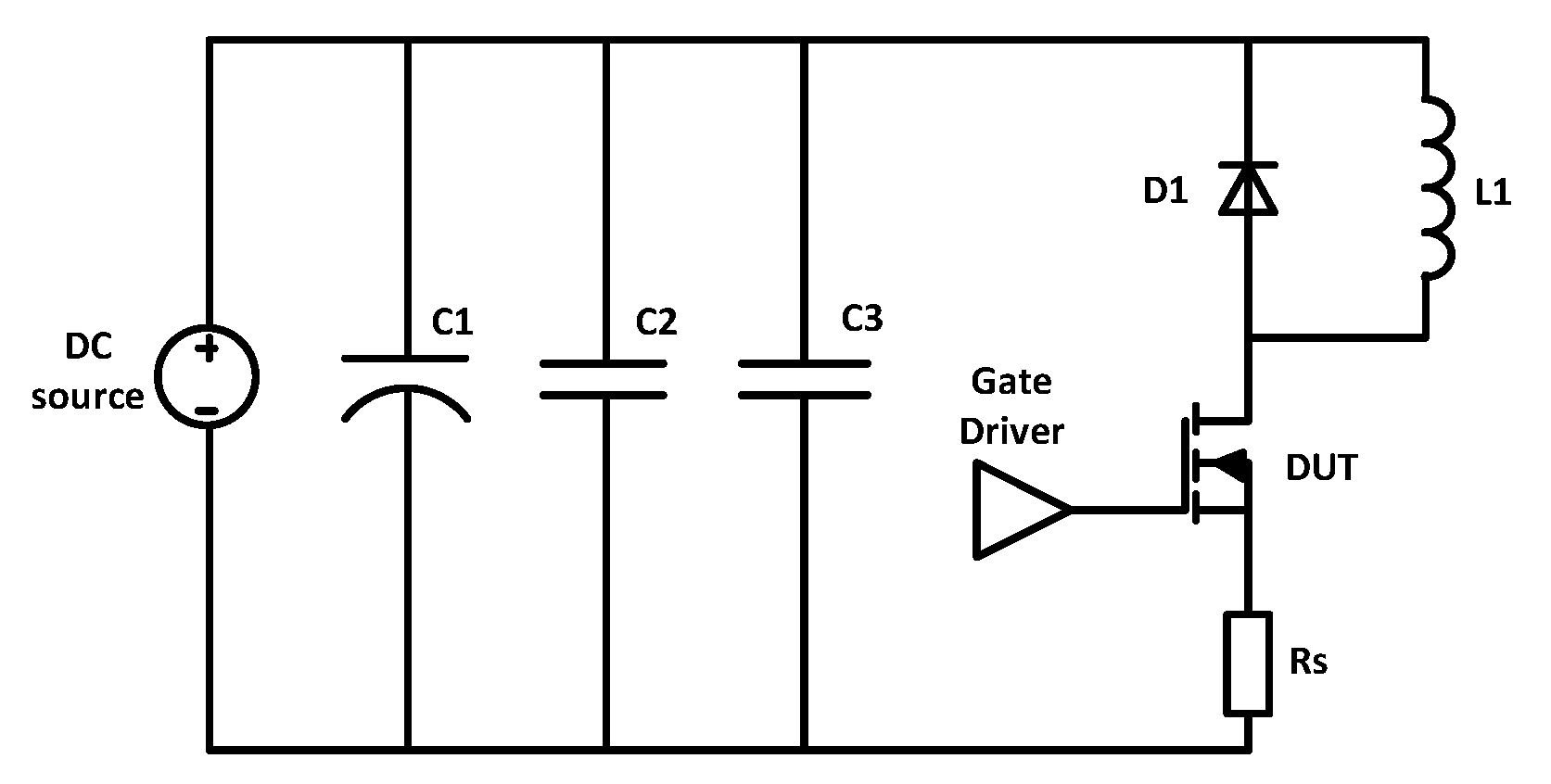

Components’ size, type, and packaging should be carefully selected for the DPT to work properly, while achieving minimal parasitics. The DPT schematic used is shown in

Figure 7.

The load inductor is not only responsible for establishing the current during the test, but also to maintain near constant current between the two pulses. Thus, it should be large enough to maintain the current for the desired off-time. The load inductor value is determined under worst case conditions, which occur under maximum voltage and minimum current.

Another critical property of the inductor is its core saturation point. If the core saturates before reaching the testing current the inductance will collapse, resulting in a very rapid current increase and could potentially destroy the DUT. To reach the target inductance while achieving a high saturation current level, Kool Mµ toroidal cores were used to build a custom inductor core.

To minimize the equivalent series resistance (ESR) of the inductor, 6 mm2 Litz wire was used. To minimize the equivalent parallel capacitance (EPC), the inductor was constructed using one layer of winding. The inductor was evaluated using a GW Instek 817 LCR meter to measure the inductance, and a saturation current tester to test the core’s saturation point. The final inductor had an inductance of 810 μH, and saturated at 80 A.

A DC capacitor bank (C1) was used to supply the inductor current, and it is designed to limit the voltage variation during the charging of the inductor. The capacitor should be designed to handle the maximum operating voltage, and the value should be determined under worst conditions, which occurs under minimum voltage and maximum current. It is preferred they are either electrolytic or film capacitors [

6]. A capacitor bank was formed using four 560 μF 400 V electrolytic capacitors, with two connected in series, and then the two sets connected in parallel to form a 1060 μF 800 V capacitor bank.

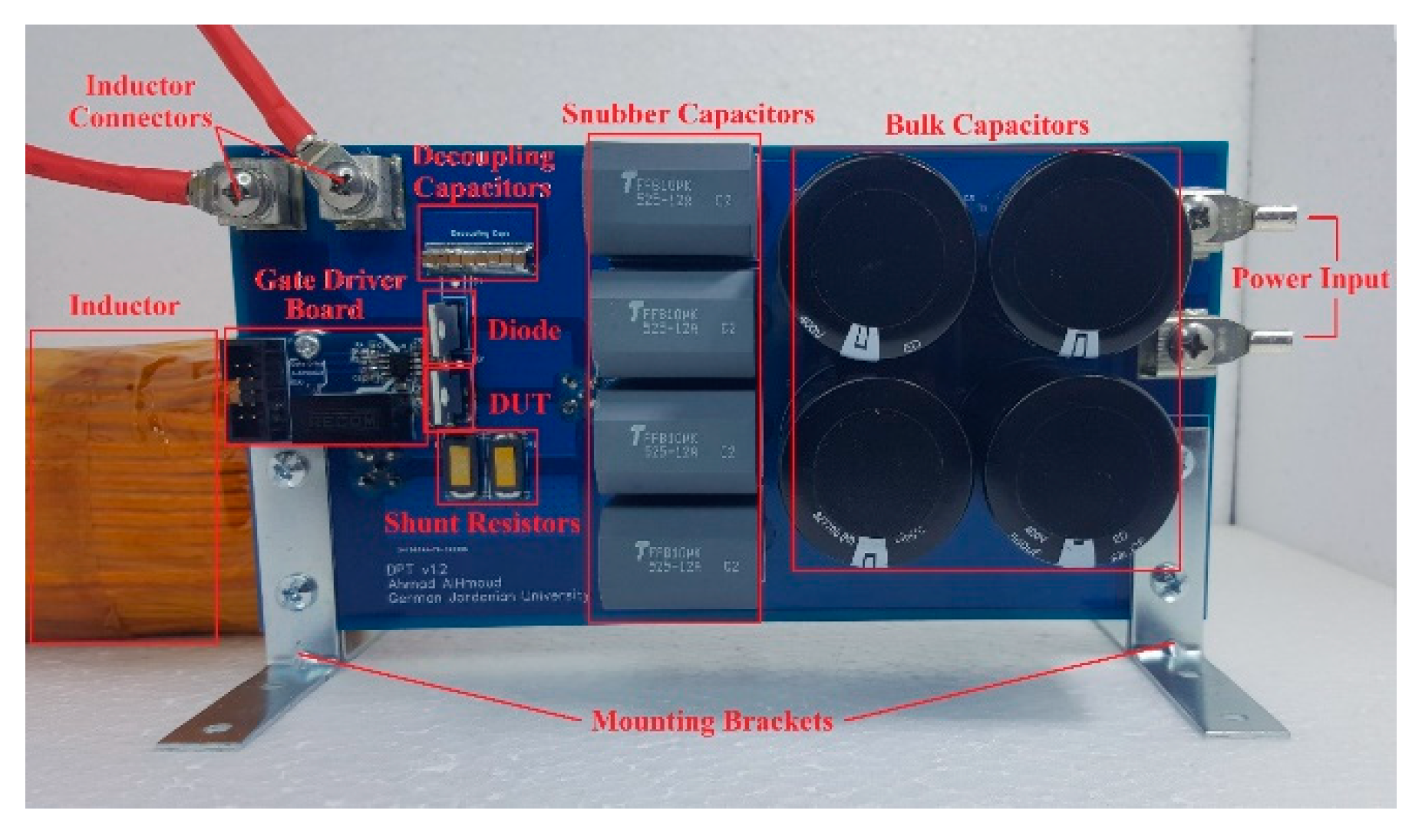

A second stage made of film capacitors (C2) was added between the bulk capacitor bank and the decoupling capacitors to absorb or supply any high voltage or current spikes that are too fast for the electrolytic capacitors, and too demanding for the decoupling capacitors. Four 525 V 10 μF (FFB46J0106K) film capacitors arranged in parallel were empirically found to achieve high decoupling from the DC source, and enable the testing board to achieve much higher testing currents, with no noticeable voltage ripple.

Ceramic decoupling capacitors (C3) were used to supply transient current and mitigate overvoltage during the switching transient. To ensure good decoupling, seven 22 nF 1.5 kV (C1210 × 223KFRACTU) ceramic capacitors where used. The high voltage ratings ensure that the capacitors can withstand any possible voltage spikes during testing. To minimize the power loop parasitic inductance, the capacitors were chosen to have very low ESL ratings, and a wider 1210 footprint.

The freewheeling diode should be able to withstand the maximum testing current, be able to handle the testing voltage and voltage overshoots. Furthermore, it should have the fastest recovery time possible to minimize interference with the DUT’s performance evaluation. A diode with a low capacitance will reduce the overshoots caused by the parasitic second order oscillation. The diode chosen is a CREE C4D08120A SiC Schottky diode. SiC Schottky diodes have no reverse recovery time, and thus will insure no interference with DUT performance.

A shunt resistor (Rs) is used to measure the DUT’s current. As a shunt resistor, it must have very tight tolerance and low temperature coefficient. To minimize the power loop inductance, the resistors material must have low ESL. Two 100 mΩ (WSR5R1000FEA) power metal resistors were connected in parallel to form a 50 mΩ current sense resistor. These resistors have a low TRC, and a very low ESL. Using two parallel resistors instead of one further reduces the ESL and reduces the effect on the power loop inductance.

When designing test circuits, it is very important to place test points throughout the design, to ease data acquisition. With the DPT, waveforms give the most insight, and therefore a 500 MHz Teledyne LeCroy Wavesurfer oscilloscope and 500 MHz passive probes were used.

The instruments used are only the first step in acquiring good measurements. The probe setup and connection method has a major role in acquiring clean waveforms. Low inductance connection termination to the board is absolutely necessary. Probing a circuit always introduces some parasitics, which could potentially affect both the circuit and the measurement acquired, particularly when dealing with WBG devices.

Using a probe with a long ground lead such as in

Figure 8a will introduce very high parasitic inductance, causing ringing in the measured waveform [

6]. A better option is to use a short ground lead, as in the spring ground lead of

Figure 8b, which introduces much less parasitic inductance and less background noise. However, it still picks up noise, and it does not provide a secure way to connect the probe to the circuit.

The best termination method is to use a PCB mounted shielded connecter as can be seen in

Figure 9. This method provides the lowest measurement loop area, thus minimizing parasitic inductance and provides shielding all the way to the PCB board. Using this termination method provides the best probing results. In our design, the probes are perpendicular to the PCB board, and connected on the backside. This will shielded the probes behind the ground plane of the PCB, which will minimize any noise from the high current pulses during testing.

The PCB layout is a major contributor in minimizing parasitics, and achieving accurate test results [

6]. The most critical aspect of the PCB layout is to minimize the power loop area. Conventional lateral power loop routing is based on placing all the components and traces on one side of the PCB as tightly as possible. It provides the ability to use single sided PCBs, but does not provide the minimal loop area, and lacks good field self-cancelation. The better approach is to use a vertical power loop routing scheme, where the top layer is used for the positive power path, and the bottom layer is used as a ground return path. This approach results in smaller power loop area and provides field self-cancelation because the current returns in a parallel trace to the positive flow [

17,

18].

However, conventional 1.6 mm double-sided PCBs are too thick to achieve substantially better results than the lateral approach, since the PCB thickness heavily affects the loop area and the field self-cancelation [

17,

18]. Using thinner PCBs is impractical as the board becomes too flexible and could potentially cause damage to solder joints, especially to surface mounted devices (SMD) components.

To minimize the distance between the positive plane and the ground plane while maintaining board strength, a 4-layer design approach is used. Four-layer PCBs can be built to have the top and first inner layer close to each other (typically 0.1 to 0.2 mm apart), which reduces the inductance dramatically, not only due to the reduced loop area, but also due to field self-canceling [

17,

18], as can be seen in

Figure 10. A 4-layer PCB can be made thick enough to maintain the board’s structural integrity, while the additional two layers can be used to route shielded Kelvin connections for optimal signal integrity and measurement accuracy.

The top side of the populated DPT test board is shown in

Figure 11, and the backside showing the probe connections in

Figure 12.

2.3. Leakage Current Testing Fixtures

Forward blocking voltage or drain-source breakdown voltage is defined as the maximum voltage that the device is guaranteed to block between drain and source [

19], and is usually linked to reaching a certain level of drain-source leakage current. Drain-source leakage current or drain cut-off current is defined as the leakage current that occurs when a voltage is applied across the drain and source with the gate and source short-circuited [

19].

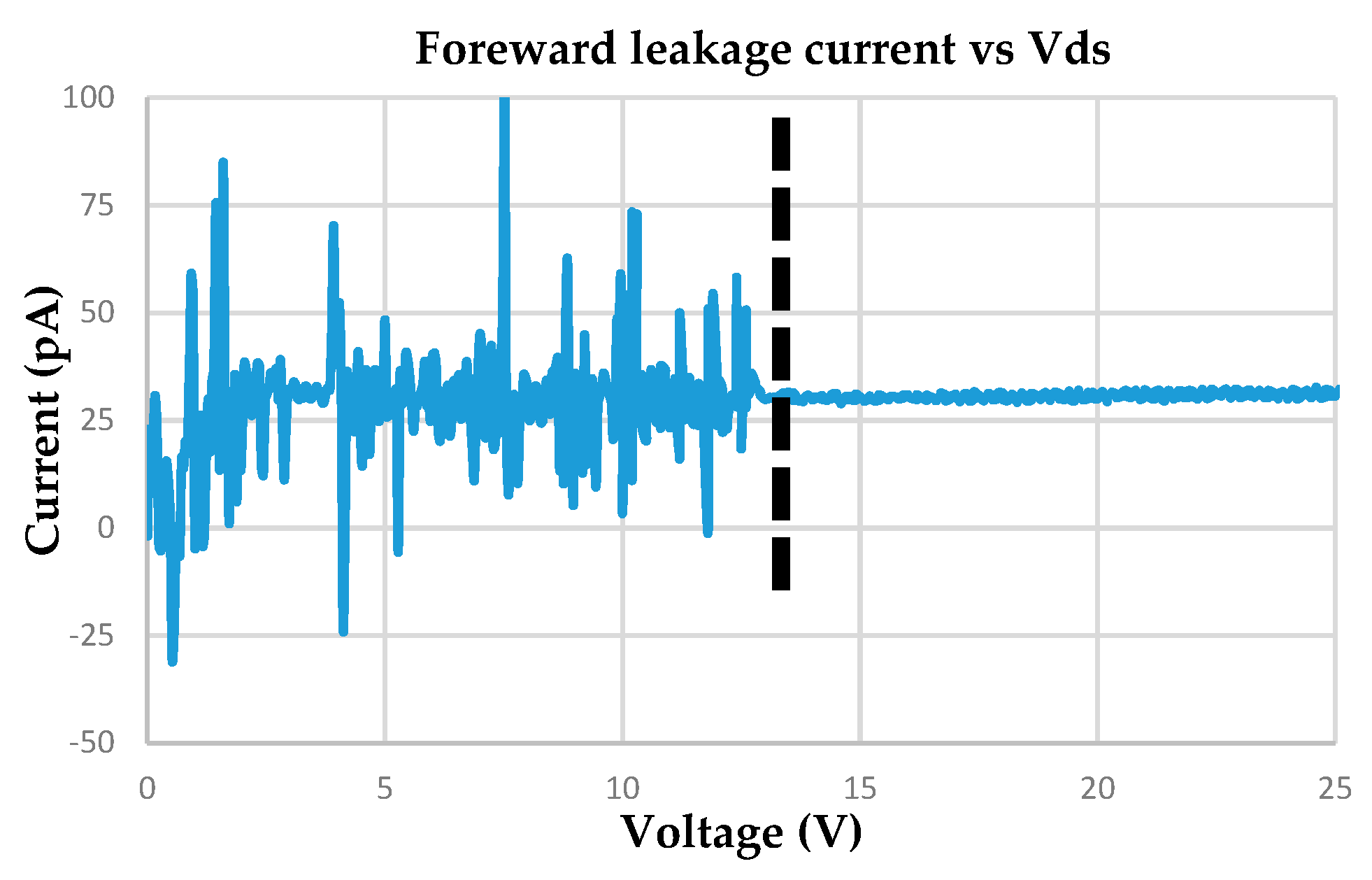

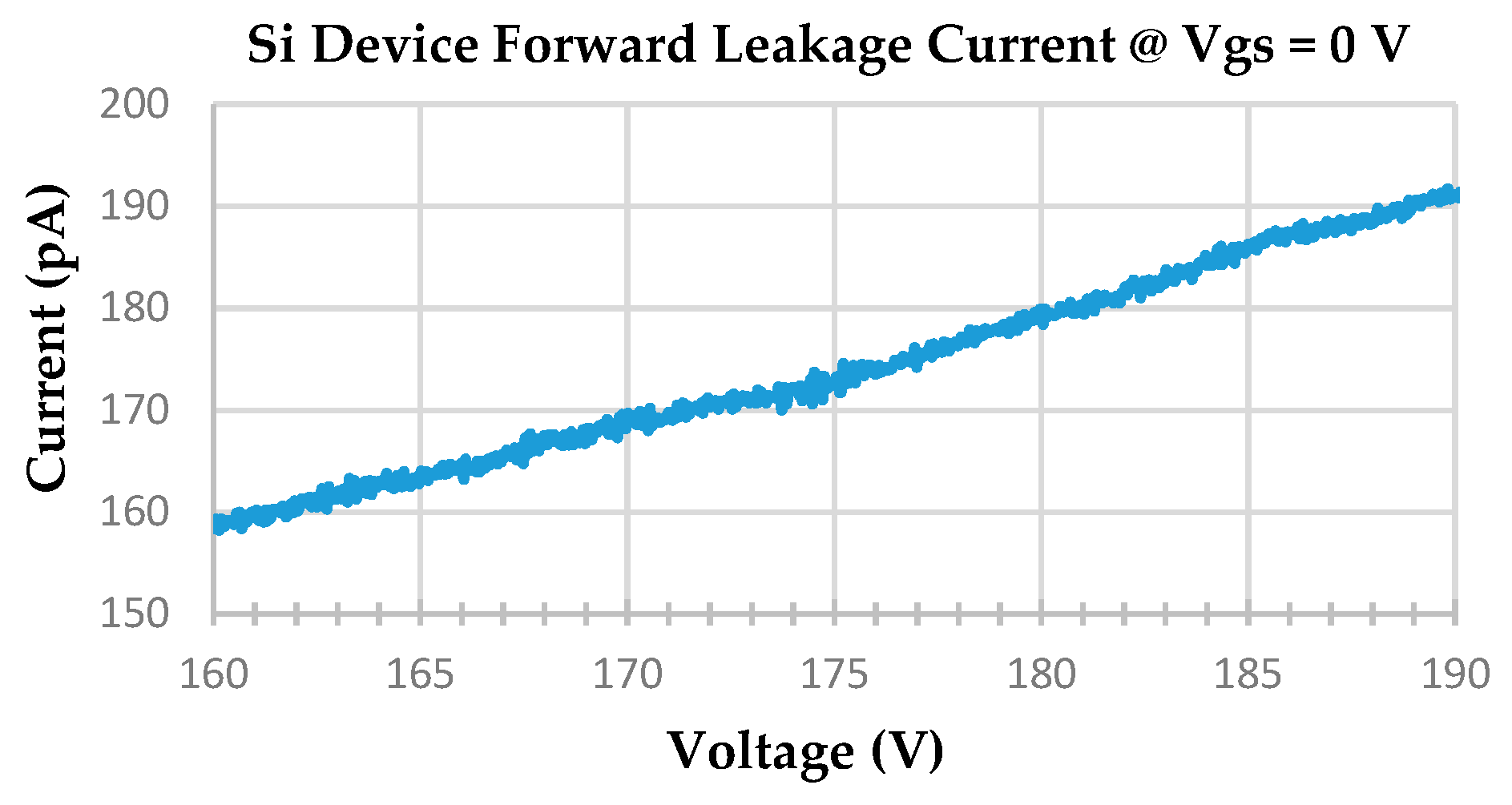

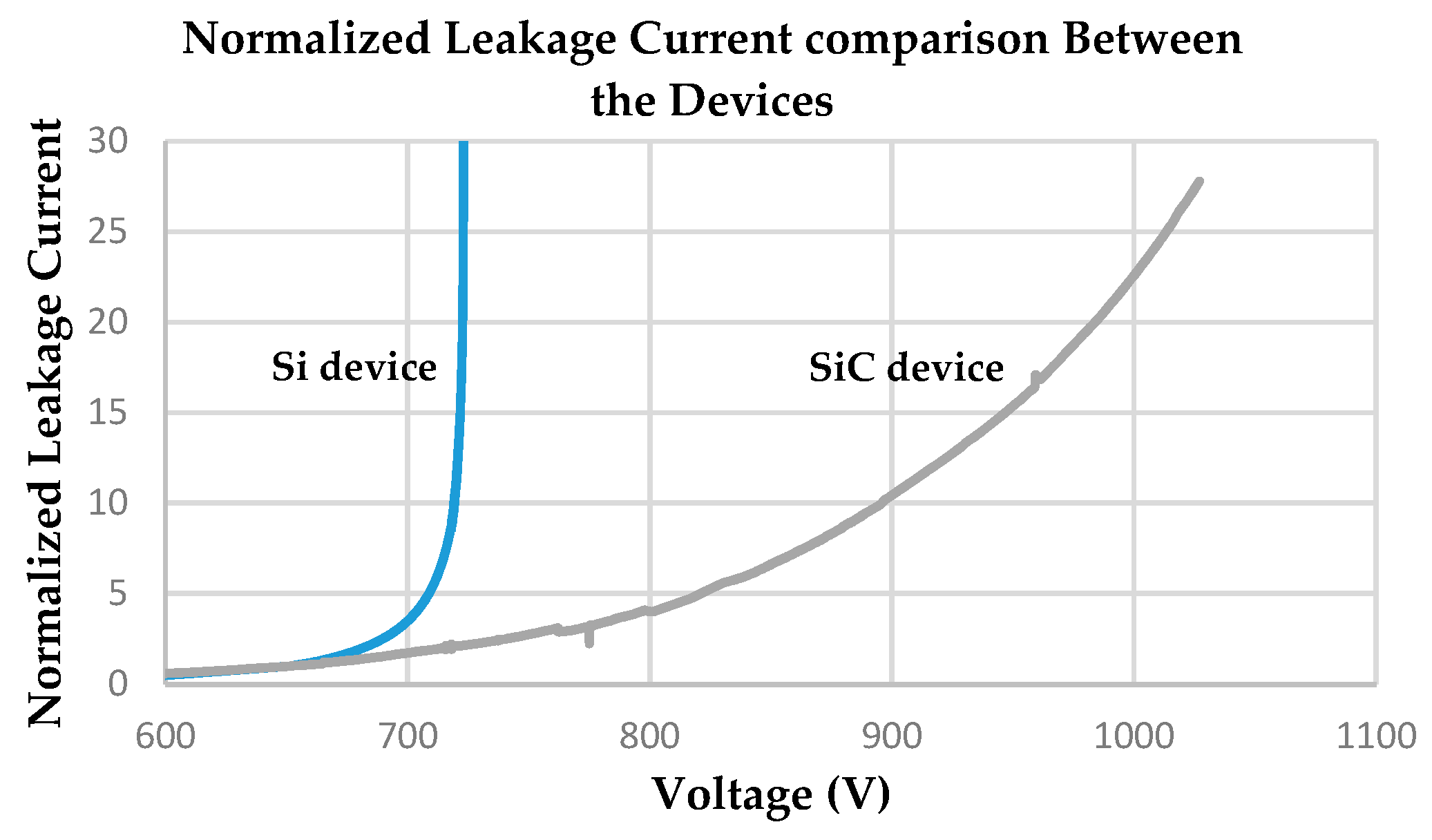

Datasheets usually use the rated voltage of the switch as the blocking voltage value, without including the upper limits of the switch, or the way it approaches the breakdown point, and often, they do not specify the basis on which the breakdown voltage value is chosen. Measuring forward leakage current enables extraction of the forward blocking voltage of a switch, since the blocking voltage is characterized by a certain level of increase in forward leakage current.

Drain-source leakage current values are often specified to be below a certain maximum level, but without including the exact value or profile of the leakage current change with the applied voltage. This makes it often very hard to compare devices based on their leakage current or provide accurate estimation of energy loss. The required test bed must perform two main functions: to be able to measure low currents down to the pA range, and to be able to test devices with voltages up to 1000 V.

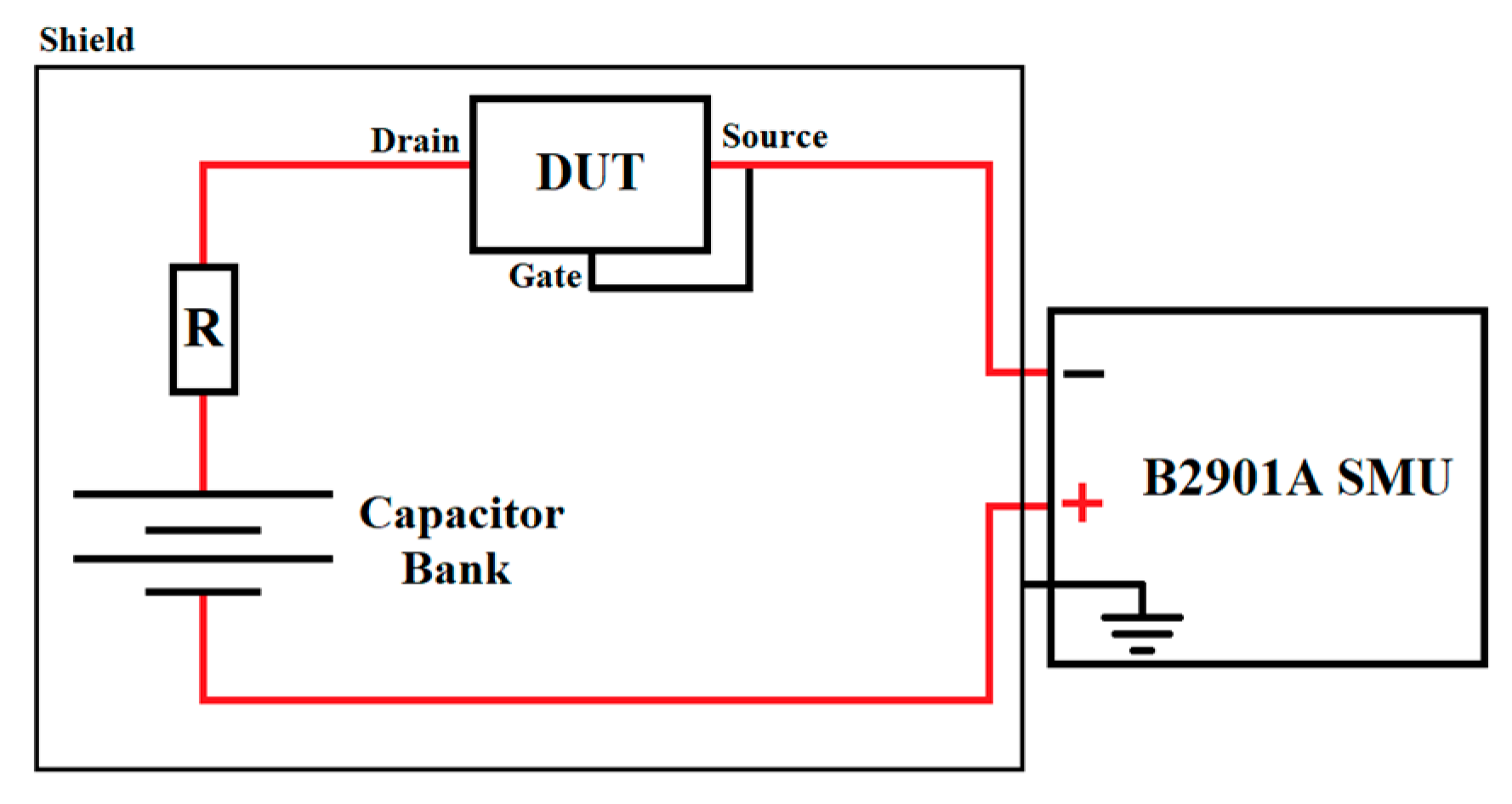

A Keysight B2901A source/meter unit (SMU) is selected as the current measurement unit. This SMU is capable of measuring current as low as 100 fA, is able to perform voltage sweeps up to 42 V, and log measured data.

A major limitation of using SMUs is their relatively limited voltage range for this particular application. The SMU used in this work can only deliver up to 42 V, which is far below the sought range. This requires the use of an external voltage source in order to measure the leakage current at voltages up to 1000 V.

Ideally, adding a power source in series with the DUT, should solve the problem. Using a bench power supply causes too much noise in the voltage path, rendering the readings unusable. Any common mode noise may affect the readings as well. To overcome this issue, a capacitor bank was used as a non-switching, floating power supply, which provided a pure DC voltage with zero ripple, and no common mode issues with the SMU. This also enabled placing the entire capacitor bank inside a shield casing for complete noise shielding.

Since the leakage current is very small, the test will result in minor capacitor discharge. Six 800 µF 450 V electrolytic capacitors were used. Connecting three capacitors in series and two in parallel resulted in a 1600 µF 1350 V capacitor bank, which provided a large enough capacitance.

When using the sweep function of the SMU to generate a graph of the voltage–current relationship, the test may take some time. In this case, to increase the accuracy of the test, the capacitor voltage was measured before and after the test, and the voltage sweep values were compensated for the capacitor voltage decrease during the test by a linear approximation of the voltage drop, which was justified because of the very small voltage drop in comparison to the operating voltage.

If the DUT fails as a short, the SMU will see the full voltage of the capacitor bank. This is an issue as only 210 V is allowed at the inputs of the SMU. To protect the SMU from potential damage, a current limiting protection resistor was connected in series, therefore any catastrophic voltage drop would be across the resistor and not the SMU, if the DUT failed as a short. The resistor should not introduce measurement errors due to its relatively low value in comparison to the DUT.

Figure 13 shows a schematic of the test setup, while

Figure 14 shows the actual test circuit.

Dealing with very low currents, even probe insulation will leak enough current to potentially affect measurement that may overwhelm the actual DUT leakage current [

20].

In order to prevent current leakage through the probe’s insulation, a special fixture was required. The fixture used a triaxial probe for the positive output, and a coaxial probe for the negative output. The probe used a guarding technique to eliminate leakage current from the measurement path. The guarding technique was based on surrounding the main conductor with a guarding shield that had the same potential of the main conductor, this would guarantee that no current would flow between them.

The guarding shield was further shielded with a grounding shield to block background noise. The negative probe was shielded with only one shield, which acted both as a guarding and a grounding shield [

20], as illustrated in

Figure 15.

The triaxial cable was built by wrapping a coaxial cable with a layer of aluminum foil, then covering it with a heat-shrink tube. The core of the coaxial cable would act as the main conductor, while the shield of the coaxial cable was terminated at the guard terminal of the SMU. The newly added layer would be used as the shield, and were terminated to the ground of the SMU. The probes were kept as short as possible to minimize parasitic capacitance, as shown in

Figure 14.