A 1 GS/s 12-Bit Pipelined/SAR Hybrid ADC in 40 nm CMOS Technology

Abstract

1. Introduction

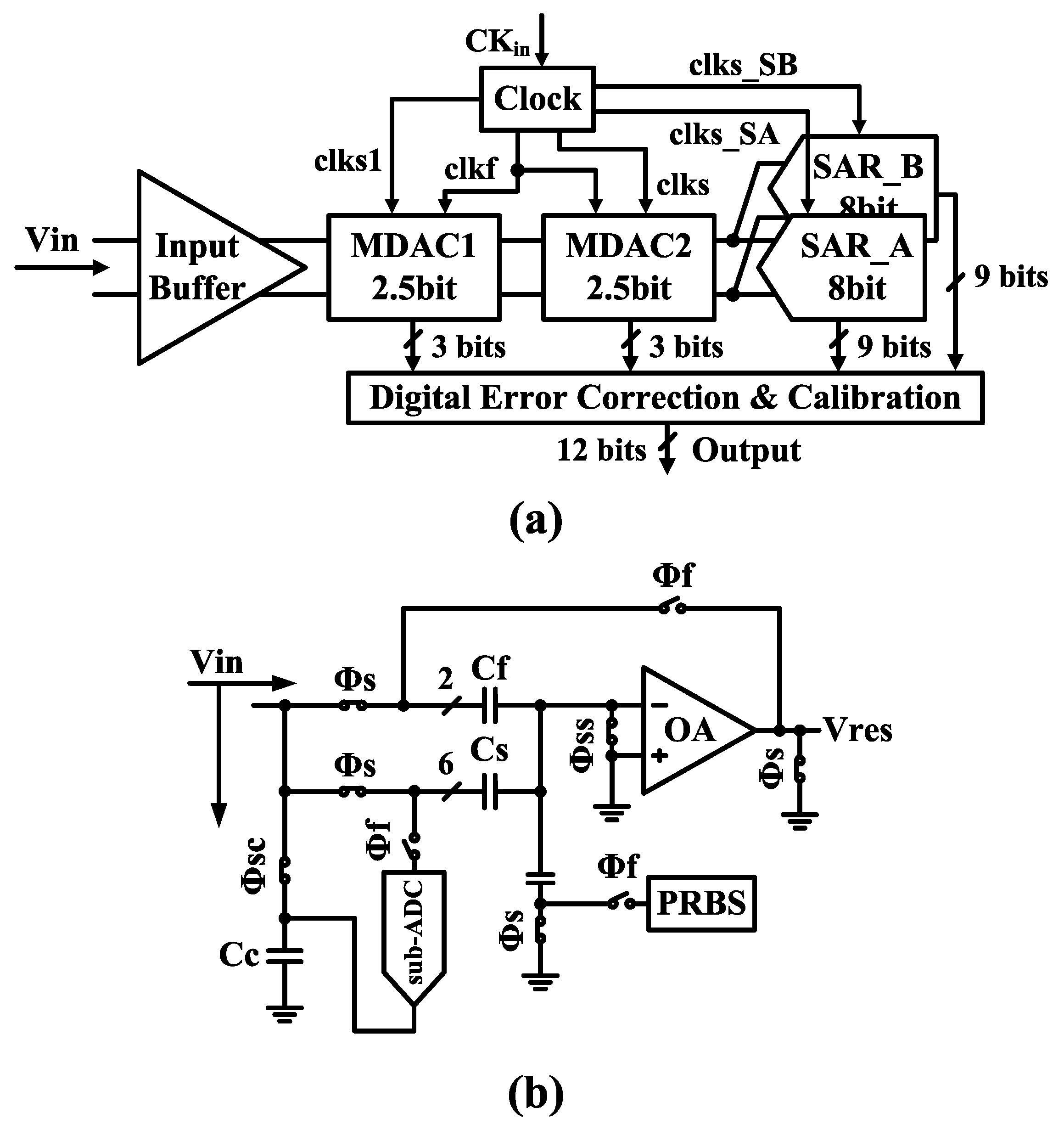

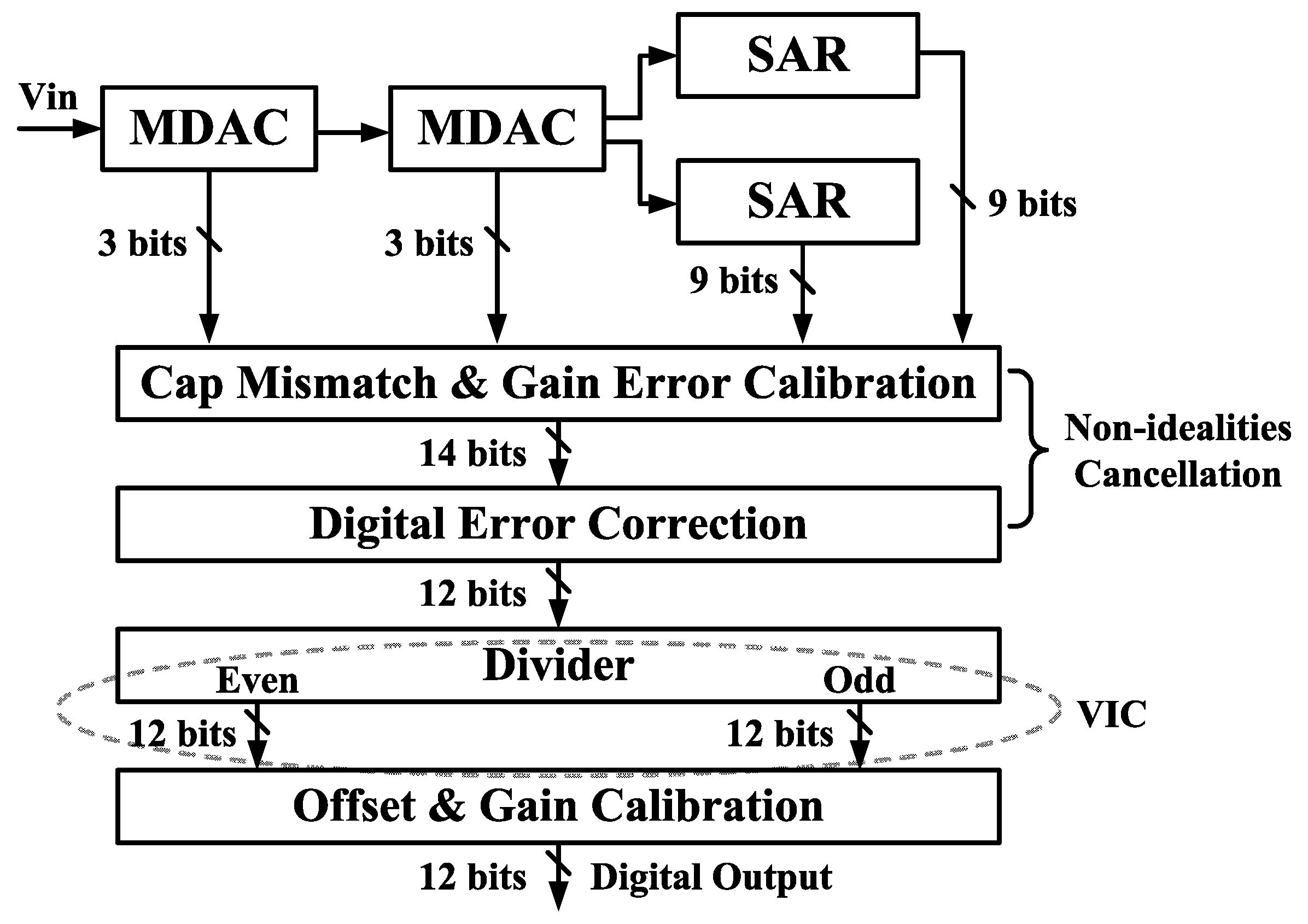

2. Proposed ADC Architecture

3. Circuits Implementation and Calibration

3.1. Input Buffer

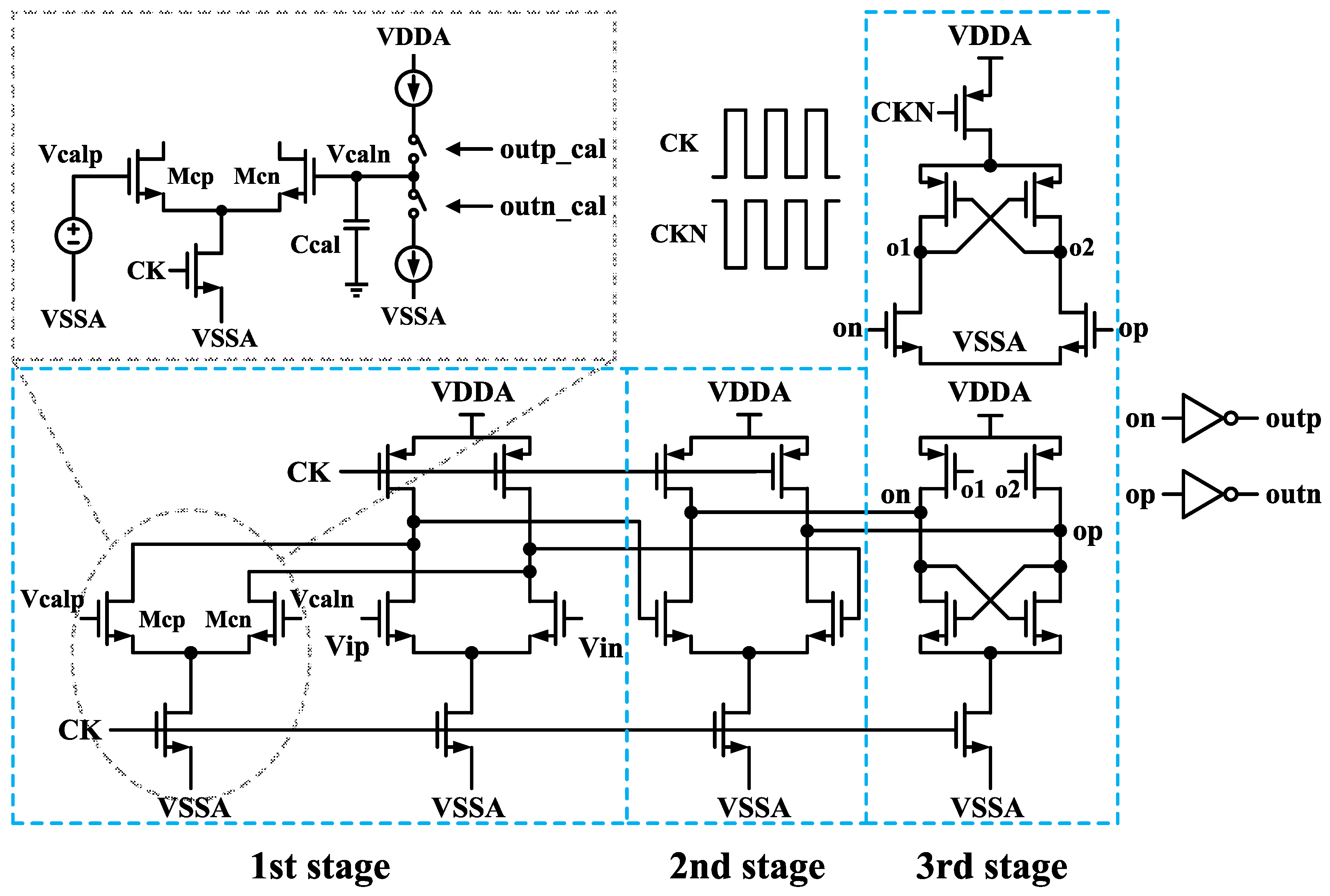

3.2. Operational Amplifier

3.3. Asynchronous SAR Quantizer

3.3.1. Architecture

3.3.2. CDAC and Comparator

3.4. Adaptive Power/Ground

3.5. Offset and Gain Calibration

4. Measured Results and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| ADC | analog-to-digital converter |

| CMOS | complementary metal-oxide-semiconductor |

| SAR | successive-approximation-register |

| TI-SAR | time-interleaved SAR |

| MDAC | multiplying digital-to-analog converter |

| MSB | most significant bit |

| Vpp | peak-to-peak voltage |

| LSB | least significant bit |

| FOM | figure of merit |

| MOS | metal-oxide-semiconductor |

| VIC | virtually-interleaved channels |

| CDAC | capacitive digital-to-analog converter |

| FFT | fast Fourier transform |

| GBW | gain-bandwidth product |

| LDO | low dropout regulator |

| DCV | direct current value |

| MAV | mean absolute value |

| DNL | differential nonlinearity |

| INL | integral nonlinearity |

| SNDR | signal-to-noise-and-distortion ratio |

| SFDR | spurious free dynamic range |

References

- Le Dortz, N.; Blanc, J.; Simon, T.; Verhaeren, S.; Rouat, E.; Urard, P.; Le Tual, S.; Goguet, D.; Lelandais-Perrault, C.; Benabes, P. A 1.62GS/s time-interleaved SAR ADC with digital background mismatch calibration achieving interleaving spurs below 70dBFS. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 9–13 February 2014; pp. 386–388. [Google Scholar]

- Zhu, Y.; Chan, C.; Seng-Pan, U.; Martins, R.P. An 11b 900 MS/s time-interleaved sub-ranging pipelined-SAR ADC. In Proceedings of the 2014—40th European Solid State Circuits Conference, Venice Lido, Italy, 22–26 September 2014; pp. 211–214. [Google Scholar]

- Louwsma, S.M.; van Tuijl, A.J.M.; Vertregt, M.; Nauta, B. A 1.35 GS/s, 10 b, 175 mW Time-Interleaved AD Converter in 0.13 μm CMOS. IEEE J. Solid-State Circuit 2008, 43, 778–786. [Google Scholar] [CrossRef]

- Wei, H.; Chan, C.; Chio, U.; Sin, S.; Seng-Pan, U.; Martins, R.P.; Maloberti, F. An 8-b 400-MS/s 2-b-Per-Cycle SAR ADC with Resistive DAC. IEEE J. Solid-State Circuit 2012, 47, 2763–2772. [Google Scholar]

- Zhu, Y.; Chan, C.; Sin, S.; Seng-Pan, U.; Martins, R.P.; Maloberti, F. A 50-fJ 10-b 160-MS/s Pipelined-SAR ADC Decoupled Flip-Around MDAC and Self-Embedded Offset Cancellation. IEEE J. Solid-State Circuit 2012, 47, 2614–2626. [Google Scholar] [CrossRef]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y. A 10-bit 50-MS/s SAR ADC with a Monotonic Capacitor Switching Procedure. IEEE J. Solid-State Circuit 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Liu, W.; Huang, P.; Chiu, Y. A 12-bit, 45-MS/s, 3-mW Redundant Successive-Approximation-Register Analog-to-Digital Converter with Digital Calibration. IEEE J. Solid-State Circuit 2011, 46, 2661–2672. [Google Scholar] [CrossRef]

- Zhou, Y.; Xu, B.; Chiu, Y. A 12 bit 160 MS/s Two-Step SAR ADC with Background Bit-Weight Calibration Using a Time-Domain Proximity Detector. IEEE J. Solid-State Circuit 2015, 50, 920–931. [Google Scholar] [CrossRef]

- Jae-Won, N.; Hassanpourghadi, M.; Aoyang, Z.; Mike Shuo-Wei, C. A 12-bit 1.6 GS/s interleaved SAR ADC with dual reference shifting and interpolation achieving 17.8 fJ/conv-step in 65nm CMOS. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar]

- Nam, J.; Hassanpourghadi, M.; Zhang, A.; Chen, M.S. A 12-Bit 1.6, 3.2, and 6.4 GS/s 4-b/Cycle Time-Interleaved SAR ADC With Dual Reference Shifting and Interpolation. IEEE J. Solid-State Circuit 2018, 53, 1765–1779. [Google Scholar] [CrossRef]

- Doris, K.; Janssen, E.; Nani, C.; Zanikopoulos, A.; Weide, G.V.D. A 480 mW 2.6 GS/s 10b Time-Interleaved ADC with 48.5 dB SNDR up to Nyquist in 65 nm CMOS. IEEE J. Solid-State Circuit 2011, 46, 2821–2833. [Google Scholar] [CrossRef]

- Janssen, E.; Doris, K.; Zanikopoulos, A.; Murroni, A.; Weide, G.V.D.; Lin, Y.; Alvado, L.; Darthenay, F.; Fregeais, Y. An 11b 3.6GS/s time-interleaved SAR ADC in 65nm CMOS. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2013; pp. 464–465. [Google Scholar]

- Young-Deuk, J.; Young-Kyun, C.; Jae-Won, N.; Kwi-Dong, K.; Woo-Yol, L.; Kuk-Tae, H.; Jong-Kee, K. A 9.15 mW 0.22 mm2 10b 204 MS/s pipelined SAR ADC in 65nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar]

- Zhong, J.; Zhu, Y.; Sin, S.; Seng-Pan, U.; Martins, R.P. Thermal and Reference Noise Analysis of Time-Interleaving SAR and Partial-Interleaving Pipelined-SAR ADCs. IEEE Trans. Circuits Syst. I-Regul. Pap. 2015, 62, 2196–2206. [Google Scholar] [CrossRef]

- Ali, A.M.A.; Dinc, H.; Bhoraskar, P.; Dillon, C.; Puckett, S.; Gray, B.; Speir, C.; Lanford, J.; Brunsilius, J.; Derounian, P.R.; et al. A 14 Bit 1 GS/s RF Sampling Pipelined ADC with Background Calibration. IEEE J. Solid-State Circuit 2014, 49, 2857–2867. [Google Scholar] [CrossRef]

- Hershberg, B.; Dermit, D.; Liempd, B.V.; Martens, E.; Markulic, N.; Lagos, J.; Craninckx, J. A 3.2GS/s 10 ENOB 61mW Ringamp ADC in 16nm with Background Monitoring of Distortion. In Proceedings of the 2019 IEEE International Solid- State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019; pp. 58–60. [Google Scholar]

- Lagos, J.; Hershberg, B.P.; Martens, E.; Wambacq, P.; Craninckx, J. A 1-GS/s, 12-b, Single-Channel Pipelined ADC with Dead-Zone-Degenerated Ring Amplifiers. IEEE J. Solid-State Circuit 2019, 54, 646–658. [Google Scholar] [CrossRef]

- Dongsheng, M.; Wing-Hung, K.; Chi-Ying, T. An integrated one-cycle control buck converter with adaptive output and dual loops for output error correction. IEEE J. Solid-State Circuit 2004, 39, 140–149. [Google Scholar]

- Huang, H.; Xu, H.; Elies, B.; Chiu, Y. A Non-Interleaved 12-b 330-MS/s Pipelined-SAR ADC with PVT-Stabilized Dynamic Amplifier Achieving Sub-1-dB SNDR Variation. IEEE J. Solid-State Circuit 2017, 52, 3235–3247. [Google Scholar] [CrossRef]

- Lim, Y.; Flynn, M.P. A 100 MS/s, 10.5 Bit, 2.46 mW Comparator-Less Pipeline ADC Using Self-Biased Ring Amplifiers. IEEE J. Solid-State Circuit 2015, 50, 2331–2341. [Google Scholar] [CrossRef]

- Hsu, C.; Huang, F.; Shih, C.; Huang, C.; Lin, Y.; Lee, C.; Razavi, B. An 11b 800 MS/s Time-Interleaved ADC with Digital Background Calibration. In Proceedings of the 2007 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 11–15 February 2007; pp. 464–615. [Google Scholar]

- Guerber, J.; Gande, M.; Moon, U. The Analysis and Application of Redundant Multistage ADC Resolution Improvements Through PDF Residue Shaping. IEEE Trans. Circuits Syst. I-Regul. Pap. 2012, 59, 1733–1742. [Google Scholar] [CrossRef]

- Chen, C.; Wu, J.; Hung, J.; Li, T.; Liu, W.; Shih, W. A 12-Bit 3 GS/s Pipeline ADC With 0.4 mm2 and 500 mW in 40 nm Digital CMOS. IEEE J. Solid-State Circuit 2012, 47, 1013–1021. [Google Scholar] [CrossRef]

- Byung-Moo, M.; Kim, P.; Bowman, F.W.; Boisvert, D.M.; Aude, A.J. A 69-mW 10-bit 80-MSample/s Pipelined CMOS ADC. IEEE J. Solid-State Circuit 2003, 38, 2031–2039. [Google Scholar] [CrossRef]

- Razavi, B. Basic MOS Device Physics. In Design of Analog CMOS Integrated Circuits, 2nd ed.; McGraw-Hill Education: New York, NY, USA, 2017; pp. 7–44. [Google Scholar]

- Gentinne, B.; Colinge, J.P.; Jespers, P.G.A.; Eggermont, J.P. Improvement of the performances of SOI CMOS operational amplifiers by means of a gain-boosting stage. In Proceedings of the 1993 IEEE International SOI Conference, Palm Springs, CA, USA, 5–7 October 1993; pp. 184–185. [Google Scholar]

- Bult, K.; Geelen, G.J.G.M. A fast-settling CMOS op amp for SC circuits with 90-dB DC gain. IEEE J. Solid-State Circuit 1990, 25, 1379–1384. [Google Scholar] [CrossRef]

- Kull, L.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Brändli, M.; Kossel, M.; Morf, T.; Andersen, T.M.; Leblebici, Y. A 3.1 mW 8b 1.2 GS/s Single-Channel Asynchronous SAR ADC with Alternate Comparators for Enhanced Speed in 32 nm Digital SOI CMOS. IEEE J. Solid-State Circuit 2013, 48, 3049–3058. [Google Scholar] [CrossRef]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y.; Huang, C. A 1V 11fJ/conversion-step 10bit 10 MS/s asynchronous SAR ADC in 0.18 μm CMOS. In Proceedings of the 2010 Symposium on VLSI Circuits, Honolulu, HI, USA, 16–18 June 2010; pp. 241–242. [Google Scholar]

- Allen, P.E.; Holberg, D.R. Comparators. In CMOS Analog Circuit Design, 3rd ed.; Oxford University Press, Inc.: New York, NY, USA, 2012; pp. 444–497. [Google Scholar]

- Kuo, B.; Chen, B.; Tsai, C. A 0.6V, 1.3GHz dynamic comparator with cross-coupled latches. In Proceedings of the VLSI Design, Automation and Test, Hsinchu, Taiwan, 27–29 April 2015; pp. 1–4. [Google Scholar]

- Charania, T.; Opal, A.; Sachdev, M. Analysis and Design of On-Chip Decoupling Capacitors. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2013, 21, 648–658. [Google Scholar] [CrossRef]

- Zheng, X.; Wang, Z.; Li, F.; Zhao, F.; Yue, S.; Zhang, C.; Wang, Z. A 14-bit 250 MS/s IF Sampling Pipelined ADC in 180 nm CMOS Process. IEEE Trans. Circuits Syst. I-Regul. Pap. 2016, 63, 1381–1392. [Google Scholar] [CrossRef]

- Vecchi, D.; Mulder, J.; van der Goes, F.M.L.; Westra, J.R.; Ayranci, E.; Ward, C.M.; Wan, J.; Bult, K. An 800 MS/s Dual-Residue Pipeline ADC in 40 nm CMOS. IEEE J. Solid-State Circuit 2011, 46, 2834–2844. [Google Scholar] [CrossRef]

- Wu, J.; Chen, C.; Li, T.; He, L.; Liu, W.; Shih, W.; Tsai, S.S.; Chen, B.; Huang, C.; Hung, B.J.; et al. A 240-mW 2.1-GS/s 52-dB SNDR Pipeline ADC Using MDAC Equalization. IEEE J. Solid-State Circuit 2013, 48, 1818–1828. [Google Scholar]

| Reference | [11] | [12] | [34] | [35] | This Work |

|---|---|---|---|---|---|

| Architecture | TI-SAR | TI-SAR | TI-Pipeline | TI-Pipeline | Pipelined/SAR |

| Technology | CMOS 65 nm | CMOS 65 nm | CMOS 40 nm | CMOS 40 nm | CMOS 40 nm |

| Sampling rate (GS/s) | 2.6 | 3.6 | 0.8 | 2.1 | 1 |

| Resolution (bits) | 10 | 11 | 12 | 12 | 12 |

| Supply (V) | 1.2/1.3/1.6 | 1.2/2.5 | 1/2.5 | 2.5 | 1.8 |

| SNDR@Nyquist (dB) | 48.5 | 42 | 59 | 52 | 58 |

| SFDR@Nyquist (dB) | 53.8 | 50 | 70 | 62 | 68 |

| Power (mW) | 480 | 795 | 105 | 240 | 94 |

| FOM@Nyquist (pJ/step) | 0.85 | 2.15 | 0.18 | 0.43 | 0.14 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, J.; Guo, X.; Luan, J.; Wu, D.; Zhou, L.; Wu, N.; Huang, Y.; Jia, H.; Zheng, X.; Wu, J.; et al. A 1 GS/s 12-Bit Pipelined/SAR Hybrid ADC in 40 nm CMOS Technology. Electronics 2020, 9, 375. https://doi.org/10.3390/electronics9020375

Li J, Guo X, Luan J, Wu D, Zhou L, Wu N, Huang Y, Jia H, Zheng X, Wu J, et al. A 1 GS/s 12-Bit Pipelined/SAR Hybrid ADC in 40 nm CMOS Technology. Electronics. 2020; 9(2):375. https://doi.org/10.3390/electronics9020375

Chicago/Turabian StyleLi, Jianwen, Xuan Guo, Jian Luan, Danyu Wu, Lei Zhou, Nanxun Wu, Yinkun Huang, Hanbo Jia, Xuqiang Zheng, Jin Wu, and et al. 2020. "A 1 GS/s 12-Bit Pipelined/SAR Hybrid ADC in 40 nm CMOS Technology" Electronics 9, no. 2: 375. https://doi.org/10.3390/electronics9020375

APA StyleLi, J., Guo, X., Luan, J., Wu, D., Zhou, L., Wu, N., Huang, Y., Jia, H., Zheng, X., Wu, J., & Liu, X. (2020). A 1 GS/s 12-Bit Pipelined/SAR Hybrid ADC in 40 nm CMOS Technology. Electronics, 9(2), 375. https://doi.org/10.3390/electronics9020375