EMI Susceptibility of the Output Pin in CMOS Amplifiers

Abstract

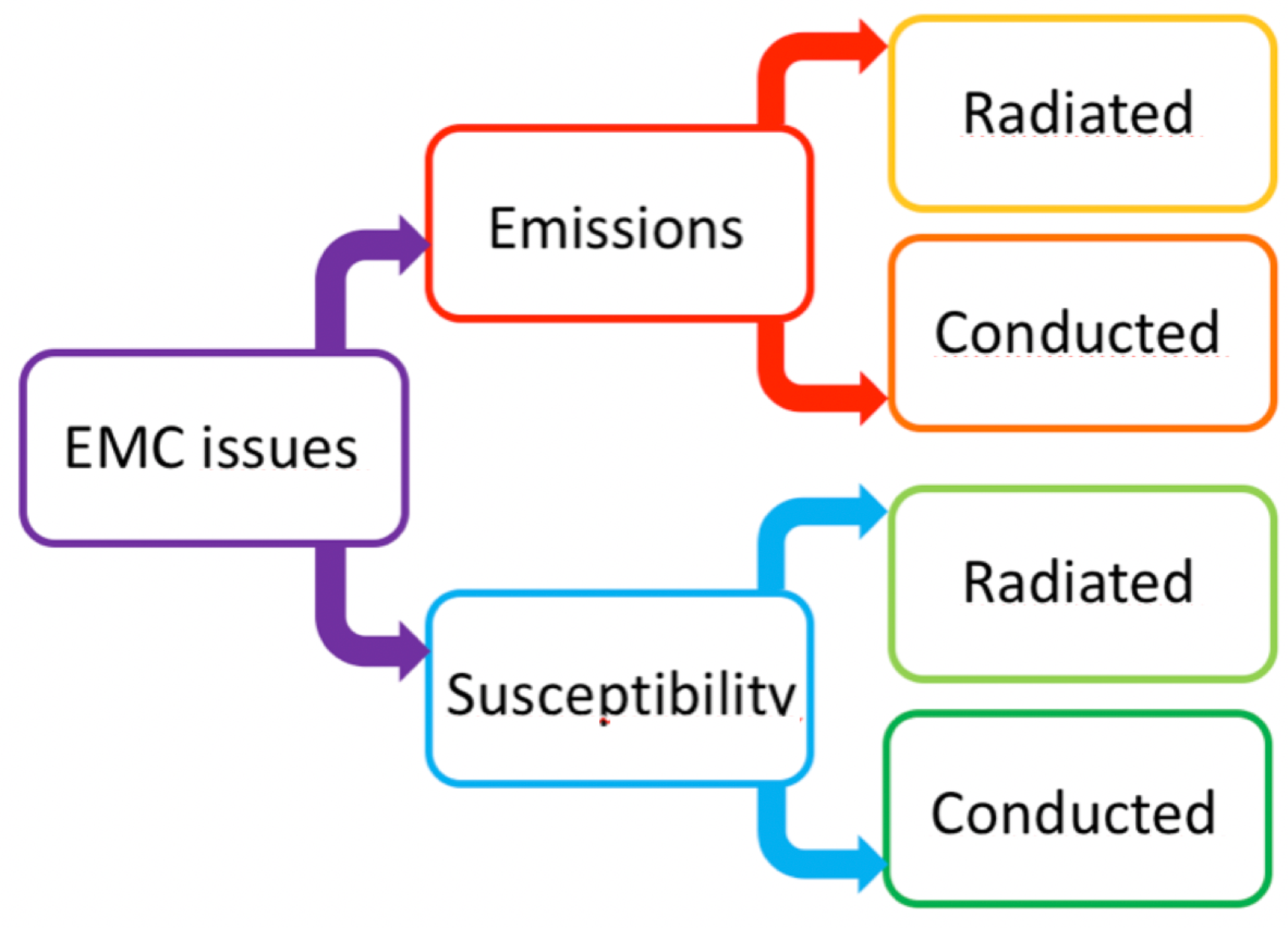

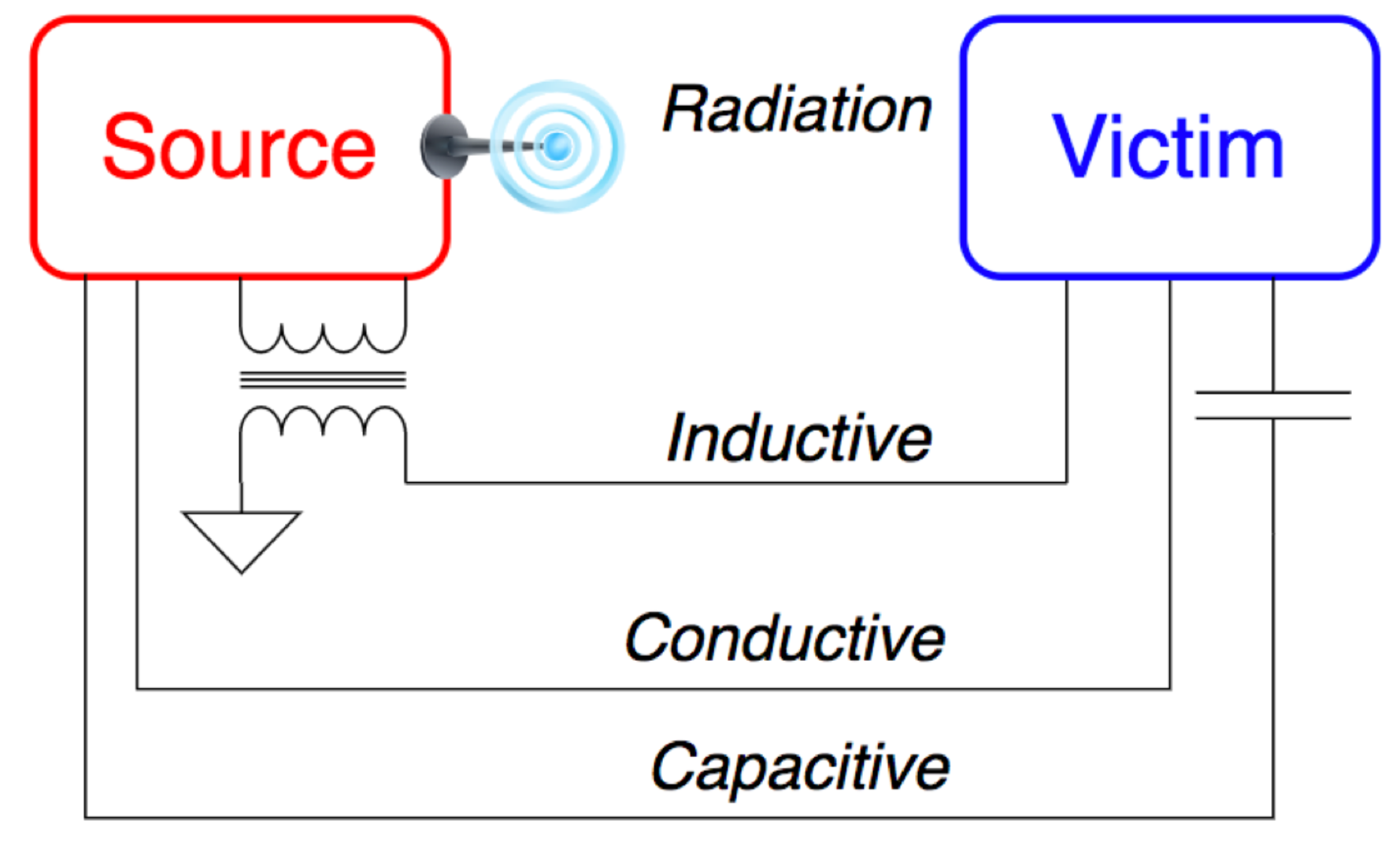

1. Introduction

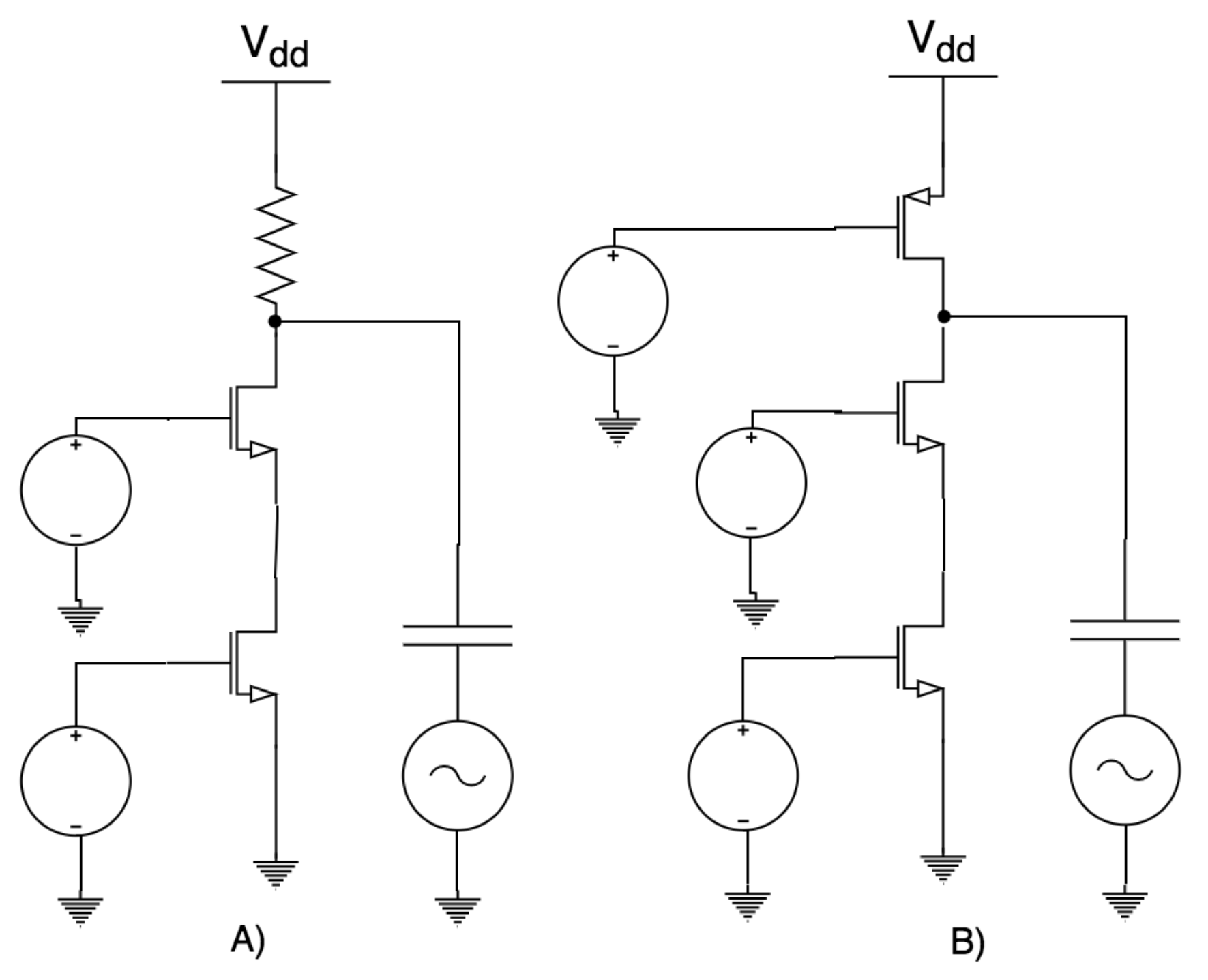

2. Definition of the Simulation Settings

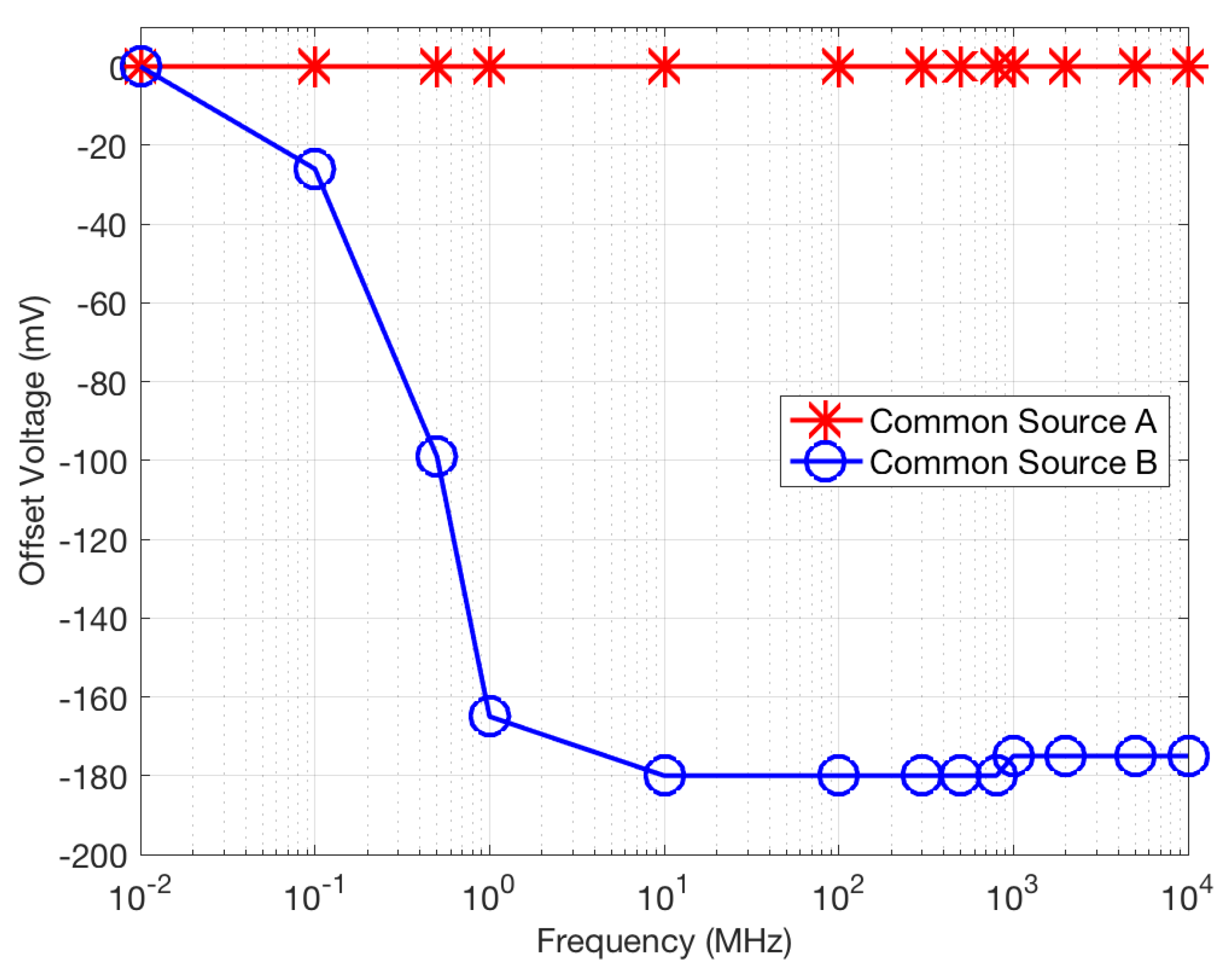

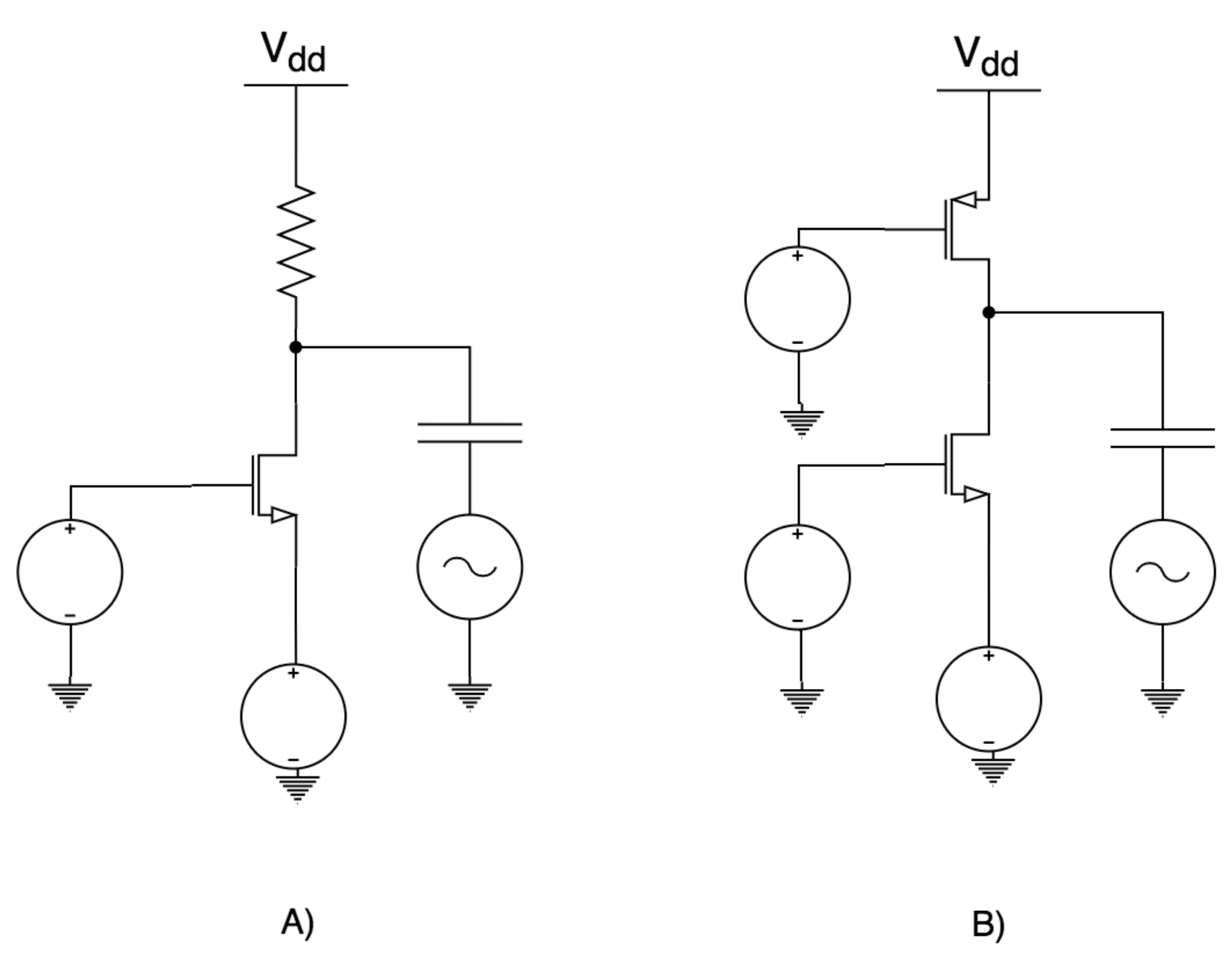

3. Susceptibility of the Common Source Stage

4. Susceptibility of the Common Gate Stage

5. Susceptibility of the Common Drain Stage

6. Susceptibility of the Cascode Stage

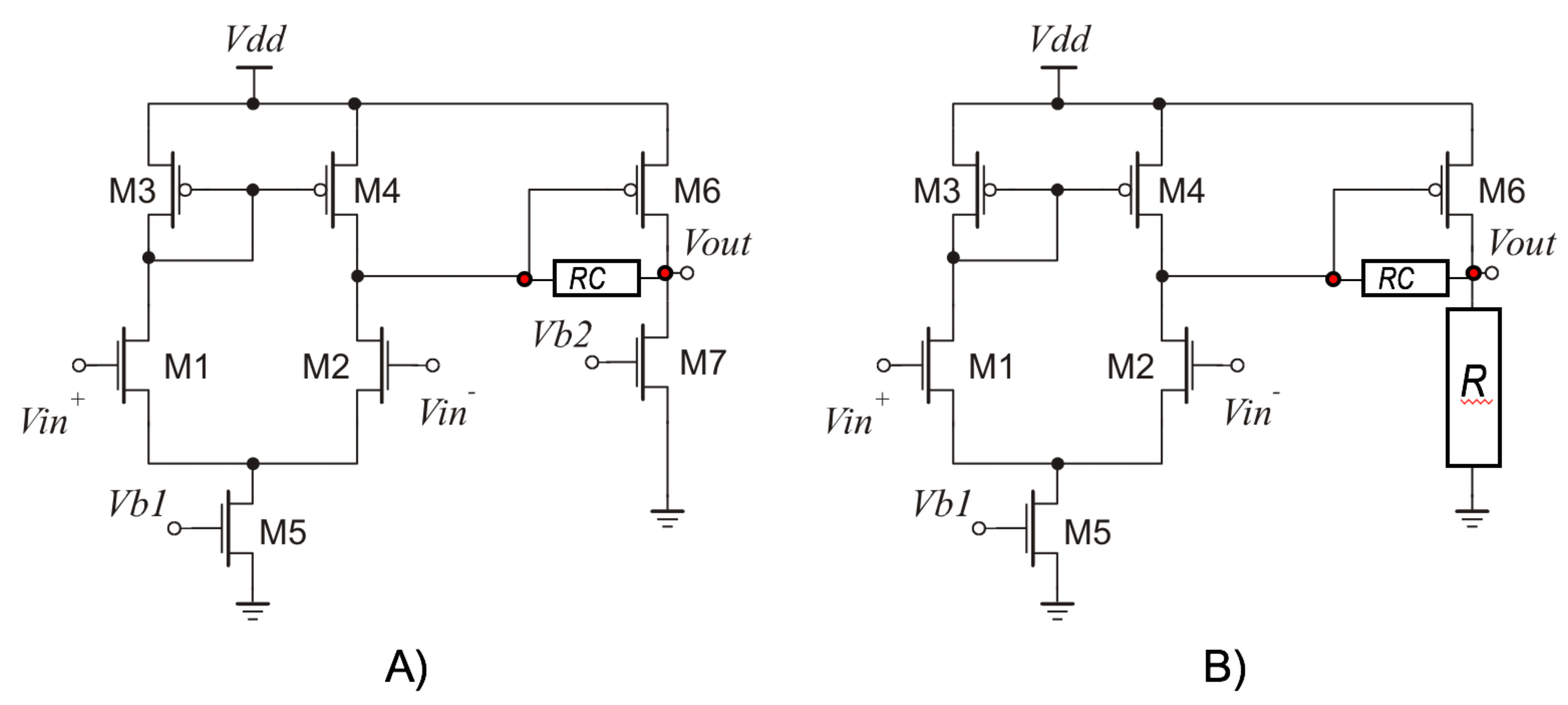

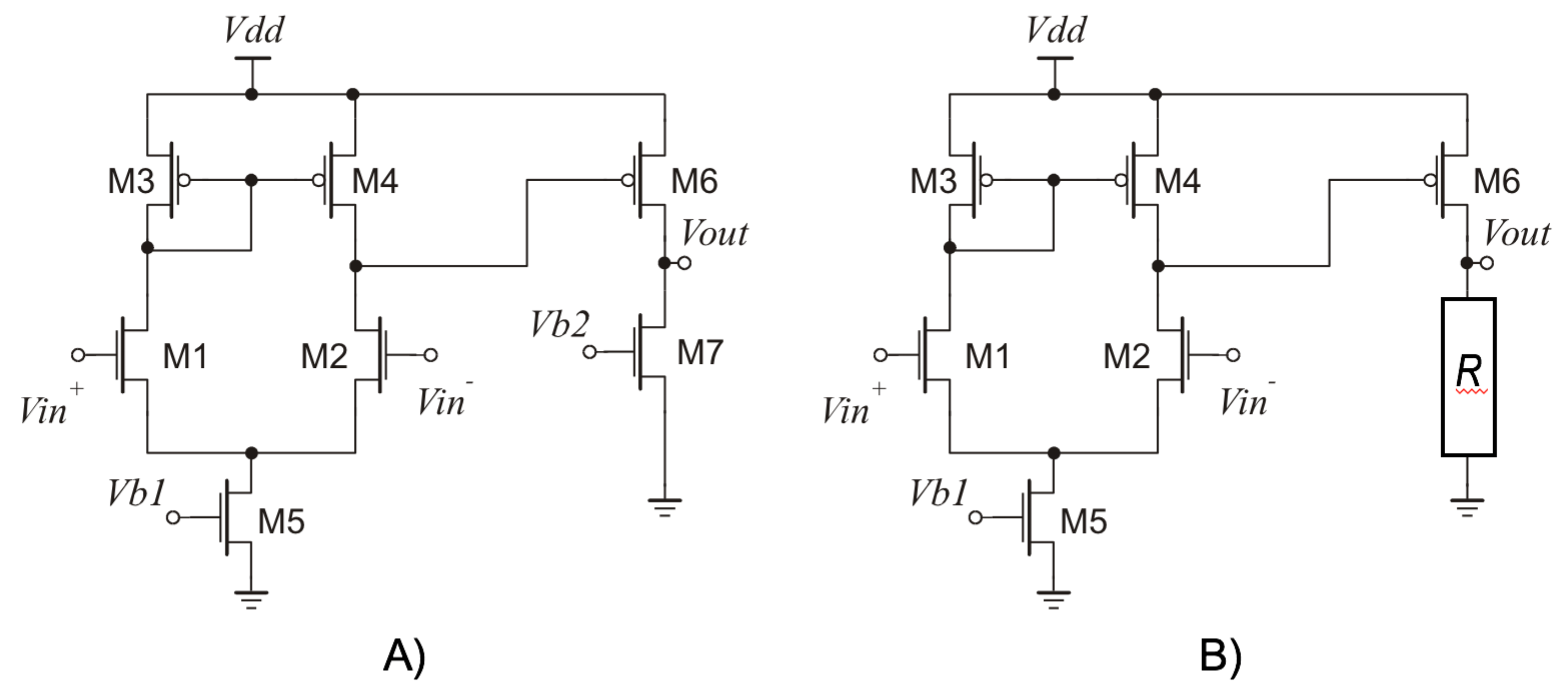

7. Susceptibility of a Two Stages Amplifier

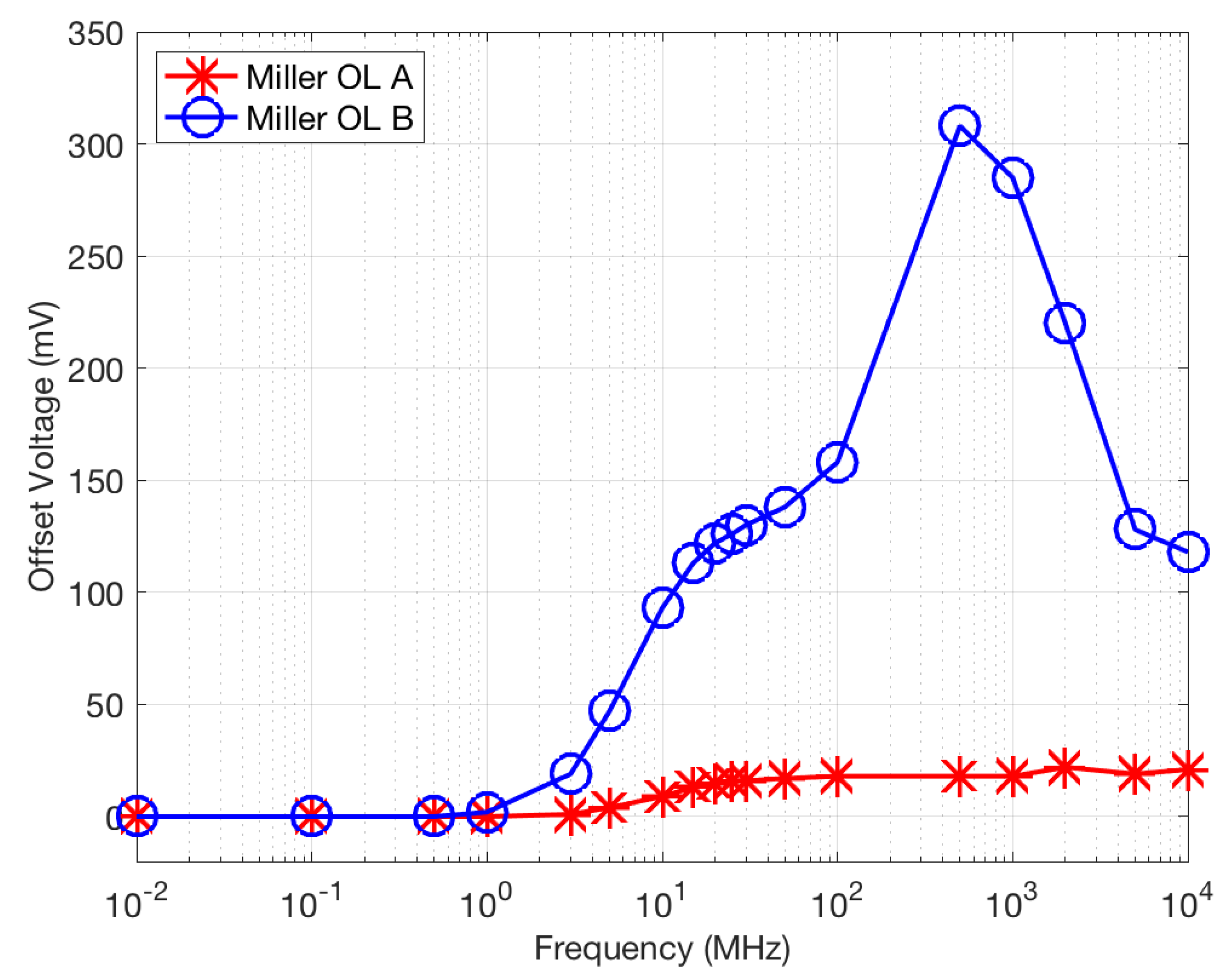

7.1. Susceptibility of a Two Stages Amplifier in Open Loop Configuration

7.2. Susceptibility of a Two Stages Amplifier in Closed Loop Configuration

8. Overview of the Obtained Results

9. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Van De Beek, S.; Leferink, F. Robustness of a TETRA Base Station Receiver Against Intentional EMI. IEEE Trans. Electromag. Compat. 2015, 57, 461–469. [Google Scholar] [CrossRef]

- Dawson, J.F.; Flintoft, I.D.; Kortoci, P.; Dawson, L.; Marvin, A.C.; Robinson, M.P.; Stojilovic, M.; Rubinstein, M.; Menssen, B.; Garbe, H.; et al. A Cost-Efficient System for Detecting an Intentional Electromagnetic Interference (IEMI) attack. In Proceedings of the IEEE International Symposium on Electromagnetic Compatibility, Gothenburg, Sweden, 1–4 September 2014; pp. 1252–1256. [Google Scholar]

- IEEE Draft Recommended. Practice for Protecting Public Accessible Computer Systems from Intentional EMI. In Practice for Protecting Public Accessible Computer Systems from Intentional EMI; IEEE P1642/D10; IEEE: Piscataway, NJ, USA, 2014; pp. 1–31. [Google Scholar]

- Kune, D.F.; Backes, J.; Clark, S.S.; Kramer, D.; Reynolds, M.; Fu, K.; Kim, Y.; Xu, W. Ghost Talk: Mitigating EMI Signal Injection Attacks against Analog Sensors. In Proceedings of the 2013 IEEE Symposium on Security and Privacy, Berkeley, CA, USA, 19–22 May 2013; pp. 145–159. [Google Scholar]

- Van De Beek, S.; Leferink, F. Current intentional EMI studies in Europe with a focus on STRUCTURES. In Proceedings of the IEEE International Symposium on Electromagnetic Compatibility Tokyo 2014, Tokyo, Japan, 12–16 May 2014; pp. 402–405. [Google Scholar]

- Fiori, F.; Crovetti, P. Prediction of high-power EMI effects in CMOS operational amplifiers. IEEE Trans. Electromagn. Compat. 2006, 48, 153–160. [Google Scholar] [CrossRef]

- Ramdani, M.; Sicard, E.; Boyer, A.; Ben Dhia, S.; Whalen, J.J.; Hubing, T.H.; Coenen, M.; Wada, O. The Electromagnetic Compatibility of Integrated Circuits-Past, Present and Future. IEEE Trans. Electromagn. Compat. 2009, 51, 78–100. [Google Scholar] [CrossRef]

- Crovetti, P.S. Operational amplifier immune to EMI with no baseband performance degradation. Electr. Lett. 2010, 46, 209–210. [Google Scholar] [CrossRef]

- Walravens, C.; Van Winckel, S.; Redoute, J.M.; Steyaert, M. Efficient reduction of electromagnetic interference effects in operational amplifiers. Electr. Lett. 2007, 43, 84–85. [Google Scholar] [CrossRef]

- Richelli, A. CMOS OpAmp resisting to large electromagnetic interferences. IEEE Trans. Electromagn. Compat. 2010, 52, 1062–1065. [Google Scholar] [CrossRef]

- Fiori, F. EMI susceptibility: The achilles’ heel of smart power ICs. IEEE EMC Mag. 2015, 4, 101–105. [Google Scholar] [CrossRef]

- Crovetti, P.; Musolino, F. Interference of Spread-Spectrum EMI and Digital Data Links under Narrowband Resonant Coupling. Electronics 2020, 9, 60. [Google Scholar] [CrossRef]

- Richelli, A.; Matig-a, G.; Redoute, J.M. Design of a folded cascode opamp with increased immunity to conducted electromagnetic interference in 0.18 μm CMOS. Microelectr. Reliab. 2015, 55, 654–661. [Google Scholar] [CrossRef]

- Redoute, J.M.; Steyaert, M. EMI-Resistant CMOS Differential Input Stages. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 323–331. [Google Scholar] [CrossRef]

- Richelli, A. Increasing EMI immunity in novel low-voltage CMOS OpAmps. IEEE Trans. Electromagn. Compat. 2010, 54, 947–950. [Google Scholar] [CrossRef]

- Sbaraini, S.; Richelli, A.; Kovács-Vajna, Z.M. EMI susceptibility in bulk-driven Miller opamp. Electr. Lett. 2010, 46, 1111–1113. [Google Scholar] [CrossRef]

- Redouté, J.-M.; Steyaert, M. An EMI Resisting LIN Driver in 0.35-micron High-Voltage CMOS. IEEE J. Solid State Circuits 2007, 42, 1574–1582. [Google Scholar] [CrossRef]

- Richelli, A.; Delaini, G.; Grassi, M.; Redouté, J.-M. Susceptibility of Operational Amplifiers to Conducted EMI Injected Through the Ground Plane into Their Output Terminal. IEEE Trans. Reliab. 2016, 65, 1369–1379. [Google Scholar] [CrossRef]

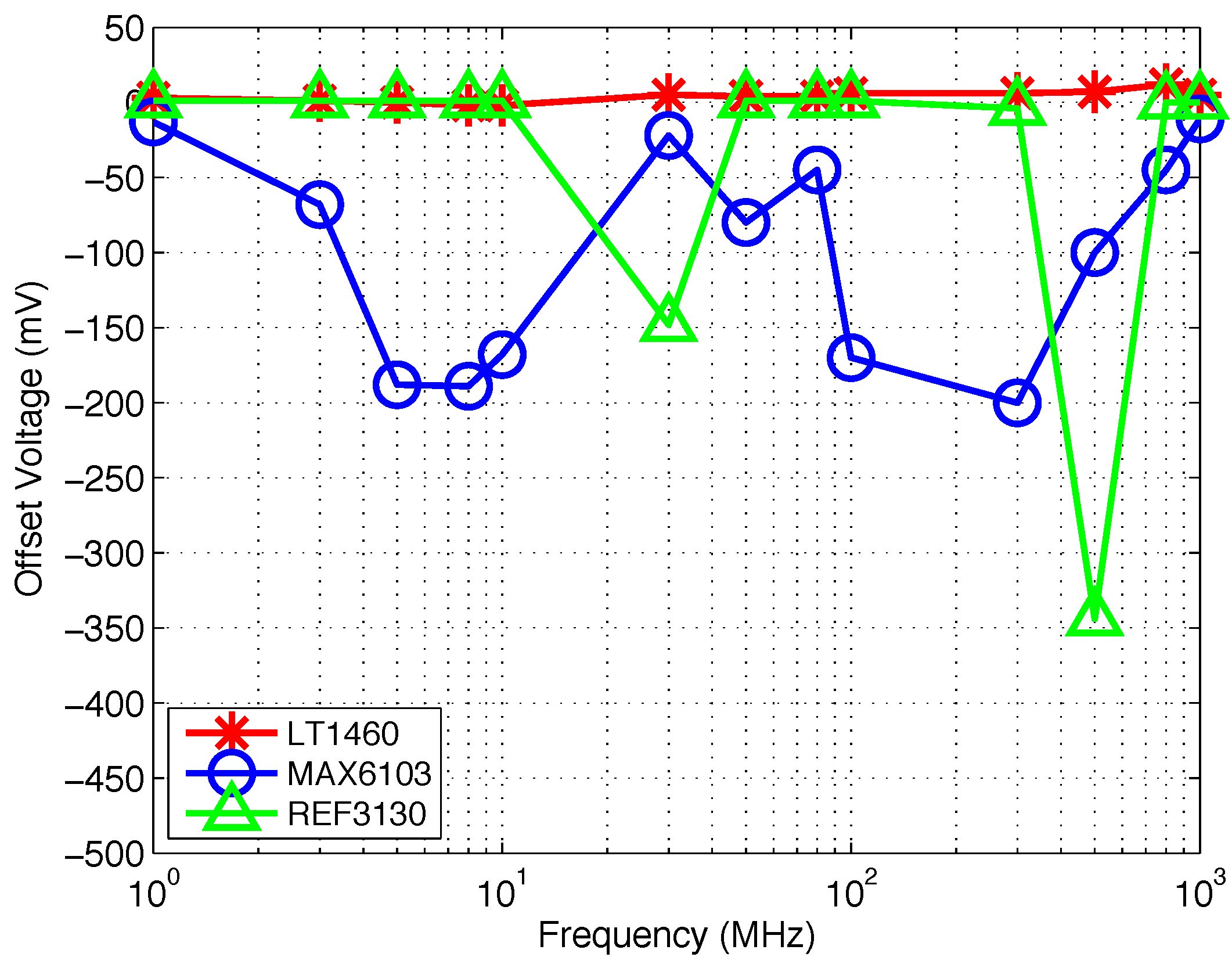

- Richelli, A.; Colalongo, L.; Toninelli, L.; Rusu, I.; Redouté, J.-M. Measurements of EMI susceptibility of precision voltage references. In Proceedings of the EMCCompo 2017, St. Petersburg, Russia, 4–8 July 2017. [Google Scholar]

- Becchetti, S.; Richelli, A.; Colalongo, L.; Kovács-Vajna, Z.M. A Comprehensive Comparison of EMI Immunity in CMOS Amplifier Topologies. Electronics 2019, 8, 1181. [Google Scholar] [CrossRef]

- Preibisch, J.B.; Duan, X.; Schuster, C. An Efficient Analysis of Power/Ground Planes With Inhomogeneous Substrates Using the Contour Integral Method. IEEE Trans. Electromagn. Compatib. 2014, 56, 980–989. [Google Scholar] [CrossRef]

- Kachout, M.; Bel Hadj Tahar, J.; Choubani, F. Modeling of Microstrip and PCB Traces to Enhance Crosstalk Reduction. In Proceedings of the IEEE SIBIRCON-2010, Listvyanka, Russia, 11–15 July 2010; pp. 594–597. [Google Scholar]

- Ricchiuti, V. Evaluation of the Effective Electrical Parameters of a PCB Trace for Accurate Signal Integrity Simulations. In Proceedings of the PIERS 2004, Pisa, Italy, 28–31 March 2004; pp. 77–80. [Google Scholar]

- Richelli, A.; Kennedy, S.; Redouté, J.M. An EMI-Resistant Common-Mode Cancelation Differential Input Stage in UMC 180 nm CMOS. IEEE Trans. Electromagn. Compatib. 2017, 59, 2049–2051. [Google Scholar] [CrossRef]

- Redouté, J.-M.; Steyaert, M. EMC of Analog Integrated Circuits; Springer: Dordrecht, The Netherlands, 2010. [Google Scholar]

- Richelli, A.; Redouté, J.-M. A Methodological Approach to EMI Resistant Analog Integrated Circuit Design. IEEE EMC Mag. 2015, 4, 92–100. [Google Scholar]

- Redouté, J.-M.; Steyaert, M. Current mirror structure insensitive to conducted EMI. IET Electr. Lett. 2005, 41, 1145–1146. [Google Scholar] [CrossRef]

| DC Biasing and AC Parameters | Components Sizing | |

|---|---|---|

| Common Source with R | VbiasN = 500 mV, 16 dB gain | W = 20 m, L = 1 m |

| (passive load) | 1.5 MHz cut-off freq., 11 MHz GBW | R = 10 k |

| Common Source with PMOS | VbiasN = 500 mV, VbiasP = 1 V, 35 dB gain | Wn = 20 m, Ln = 1 m |

| (active load) | 180 kHz cut-off freq., 10 MHz GBW | Wp = 20 m, Lp = 1 m |

| DC Biasing and AC Parameters | Components Sizing | |

|---|---|---|

| Common Drain with R | VbiasN = 1.2 V, −1dB gain | W = 20 m, L = 1 m |

| (passive load) | 13 MHz cut-off freq. | R = 10 k |

| Common Drain with NMOS | VbiasN = 1.2 and VbiasN2 = 500 mV, 0 dB gain | Wn = 20 m, Ln = 1 m |

| (active load) | 9.6 MHz cut-off freq. | Wn2 = 20 m, Ln2 = 1 m |

| DC Biasing and AC Parameters | Components Sizing | |

|---|---|---|

| Cascode with R | VbiasN1 = 0.5 V, VbiasN2 = 1 V, 16 dB gain | Wn1,2 = 20 m, Ln1,2 = 1 m |

| (passive load) | 1.5 MHz cut-off freq., 10 MHz GBW | R = 10 k |

| Common Drain with NMOS | VbiasN1 = 0.5 V, VbiasN2 = 1 V, VbiasP = 1.015 V | Wn1,2 = 20 m, Ln1,2 = 1 m |

| (active load) | 45 dB gain, 0.6 MHz cut-off freq., 10 MHz GBW | Wp = 20 m, Lp = 1 m |

| DC Biasing and AC Parameters | Components Sizing | |

|---|---|---|

| Miller with R (passive load) | Vb1 = 1.16 V, 55 dB gain | Wn1,2 = 20 m, Ln1,2 = 1 m; Wp3,4,6 = 25 m, Lp3,4,6 = 0.5 m |

| 22 kHz cut-off freq., 12 MHz GBW | Wn5 = 20 m, Ln5 = 1 m; R = 10 k | |

| Miller with NMOS (active load) | Vb1 = Vb2 = 1.16 V, | Wn1,2 = 20 m, Ln1,2 = 1 m; Wp3,4,6 = 25 m, Lp3,4,6 = 0.5 m |

| 72 dB gain, 2.8 kHz cut-off freq., 12 MHz GBW | Wn5 = 20 m, Ln5 = 1 m; Wn7 = 8.5 m, Ln7 = 0.5 m |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Richelli, A.; Colalongo, L.; Kovacs-Vajna, Z. EMI Susceptibility of the Output Pin in CMOS Amplifiers. Electronics 2020, 9, 304. https://doi.org/10.3390/electronics9020304

Richelli A, Colalongo L, Kovacs-Vajna Z. EMI Susceptibility of the Output Pin in CMOS Amplifiers. Electronics. 2020; 9(2):304. https://doi.org/10.3390/electronics9020304

Chicago/Turabian StyleRichelli, Anna, Luigi Colalongo, and Zsolt Kovacs-Vajna. 2020. "EMI Susceptibility of the Output Pin in CMOS Amplifiers" Electronics 9, no. 2: 304. https://doi.org/10.3390/electronics9020304

APA StyleRichelli, A., Colalongo, L., & Kovacs-Vajna, Z. (2020). EMI Susceptibility of the Output Pin in CMOS Amplifiers. Electronics, 9(2), 304. https://doi.org/10.3390/electronics9020304