Influence of Flexibility of the Interconnects on the Dynamic Bending Reliability of Flexible Hybrid Electronics

Abstract

1. Introduction

2. Sample Fabrication Process

2.1. Fabrication of Interconnects on the Foil Substrate

2.2. Fabrication and Thinning of Silicon Chips

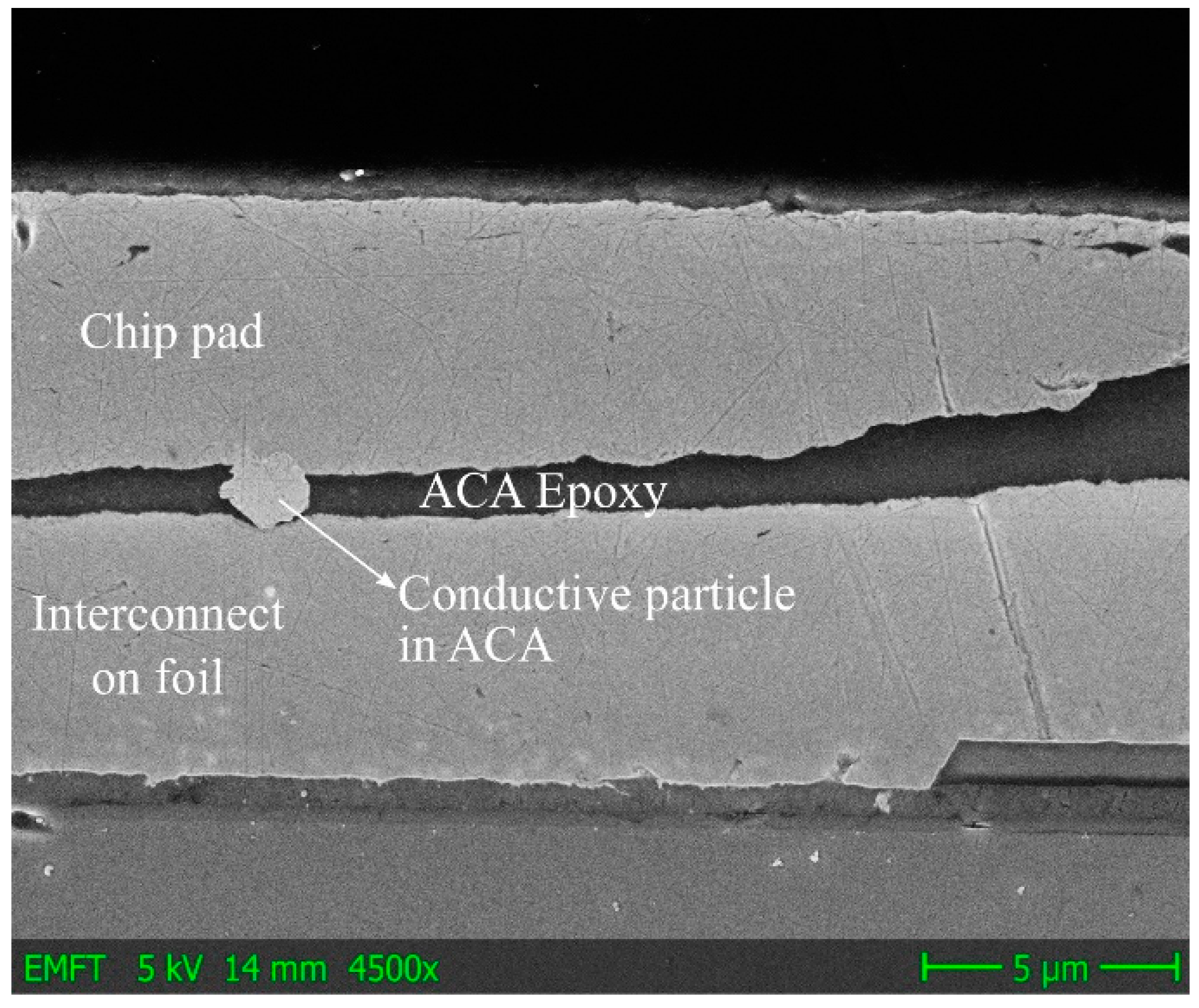

2.3. Integration of Ultra-Thin Silicon Chips on Foil Substrates

3. Experimental Setup and Procedure

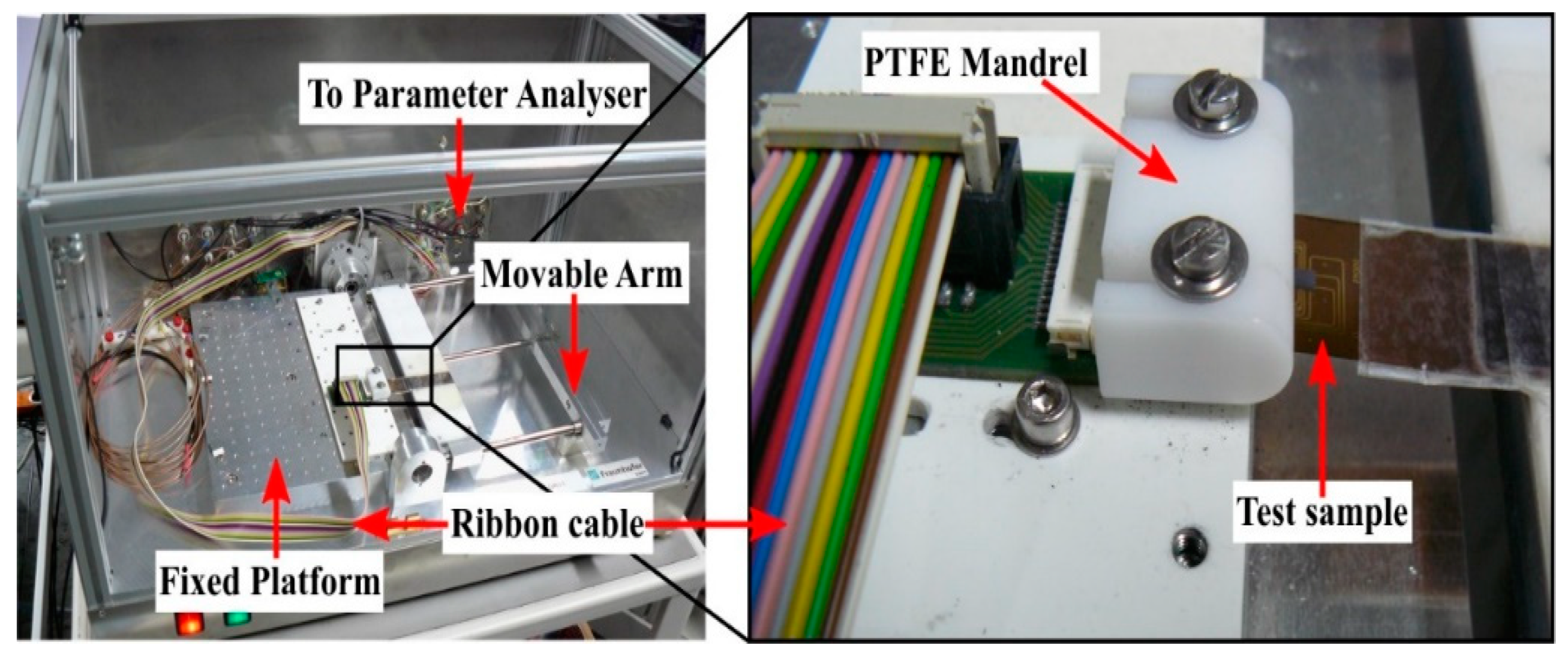

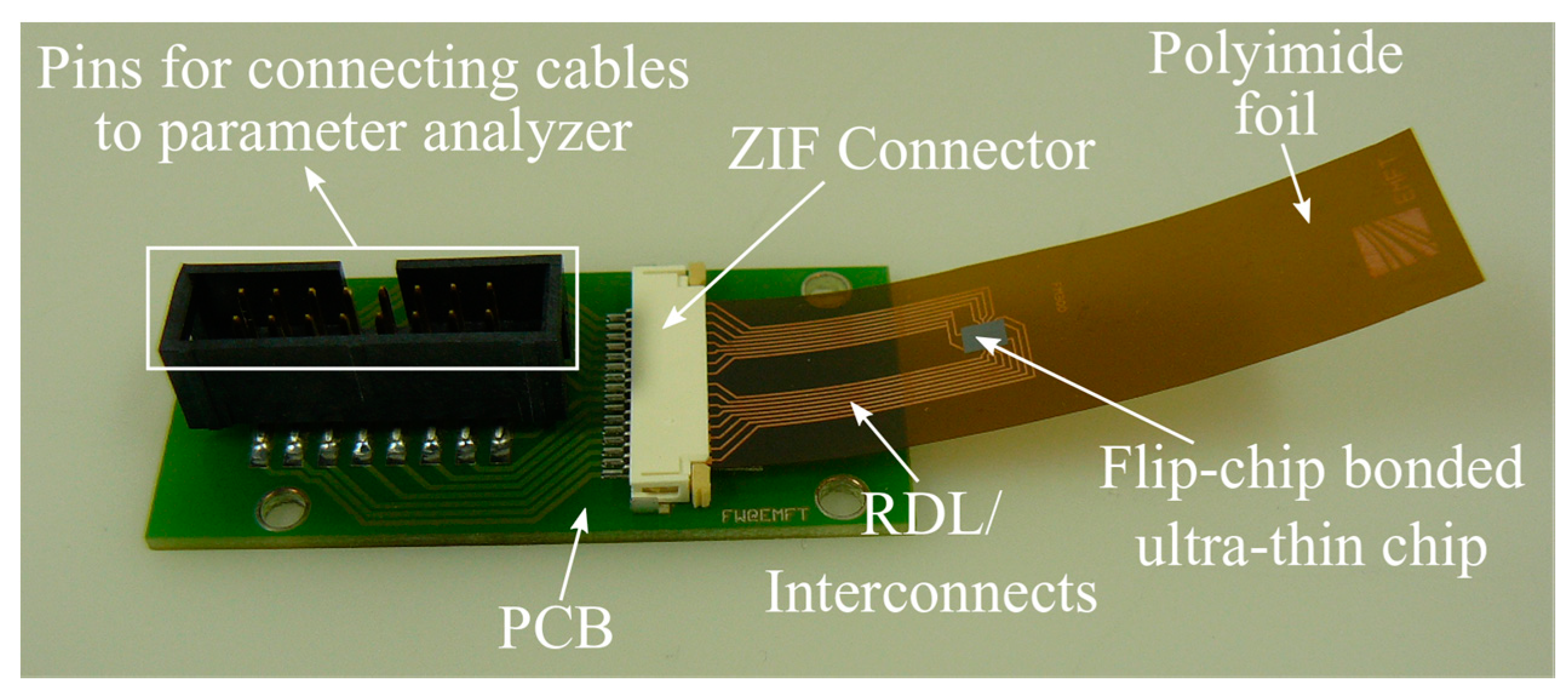

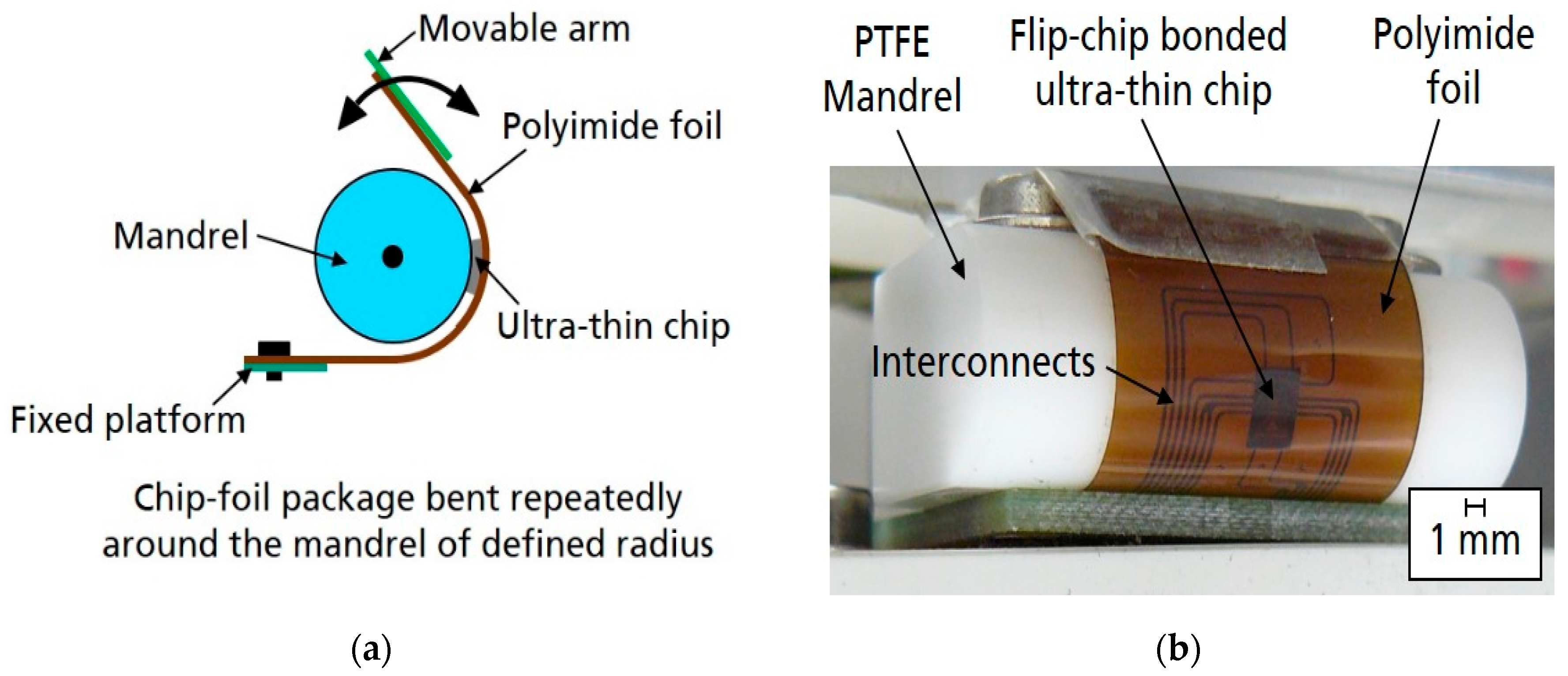

3.1. Test Equipment

3.2. Experimental Procedure

4. Results and Discussion

4.1. Optical Analysis

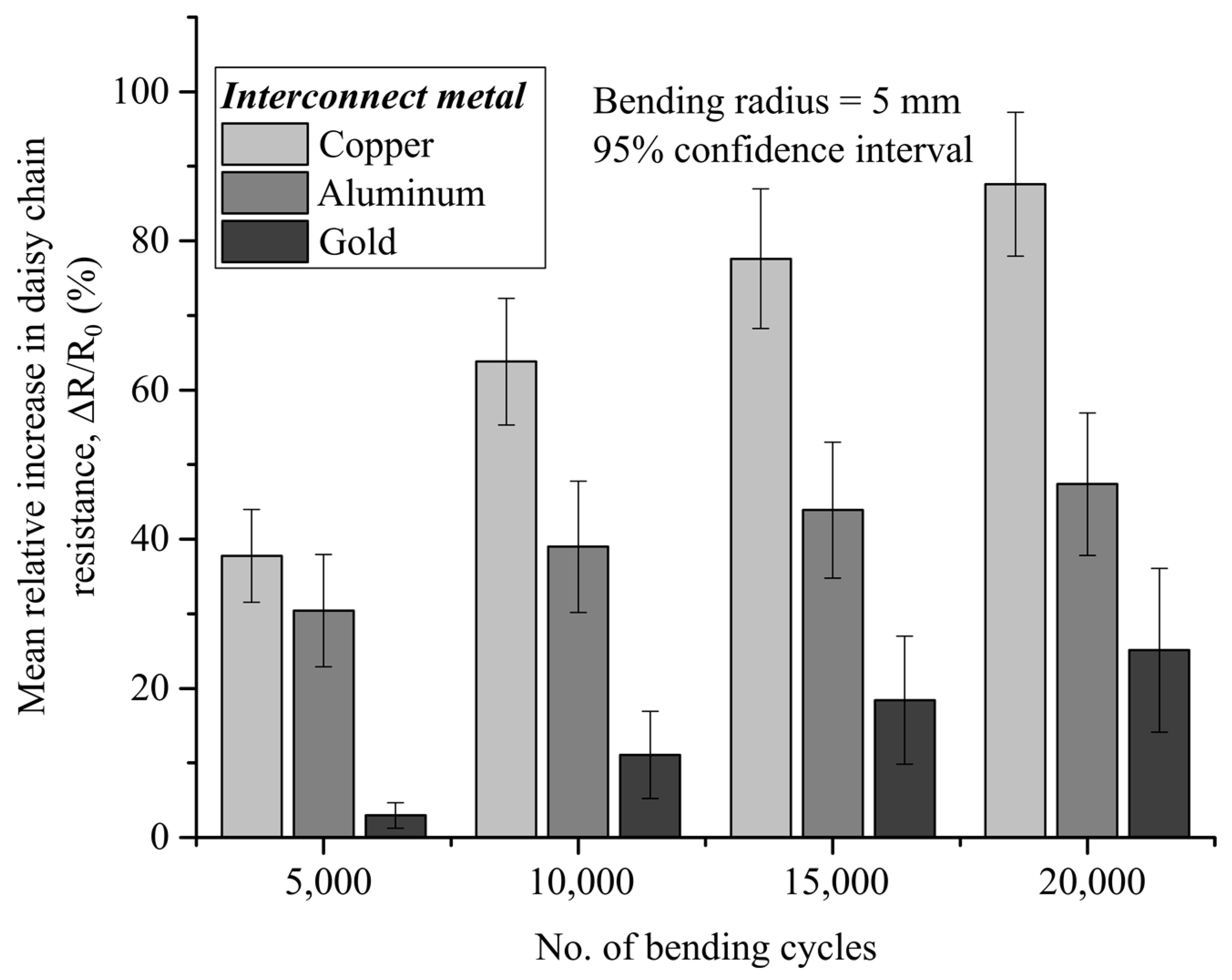

4.2. Choice of Metal for Fabrication of Interconnects

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Landesberger, C.; Palavesam, N.; Hell, W.; Drost, A.; Faul, R.; Gieser, H.; Bonfert, D.; Bock, K.; Kutter, C. Novel processing scheme for embedding and interconnection of ultra-thin IC devices in flexible chip foil packages and recurrent bending reliability analysis. In Proceedings of the 2016 International Conference on Electronics Packaging (ICEP), Sapporo, Japan, 20–22 April 2016; IEEE: Sapporo, Japan. [Google Scholar]

- Mahsereci, Y.; Saller, S.; Richter, H.; Burghartz, J.N. An ultra-thin flexible CMOS stress sensor demonstrated on an adaptive robotic gripper. IEEE J. Solid State Circuits 2015, 51, 273–280. [Google Scholar]

- Bose, I.; Palavesam, N.; Hochreiter, C.; Landesberger, C.; Kutter, C. Low Profile Open MEMS and ASIC Packages Manufactured by Flexible Hybrid Integration in a Roll-to-Roll Compatible Process. In Proceedings of the 2018 48th European Solid-State Device Research Conference (ESSDERC), Dresden, Germany, 3–6 September 2018; IEEE: Dresden, Germany. [Google Scholar]

- Gao, W.; Emaminejad, S.; Nyein, H.Y.Y.; Challa, S.; Chen, K.; Peck, A.; Fahad, H.M.; Ota, H.; Shiraki, H.; Kiriya, D.; et al. Fully integrated wearable sensor arrays for multiplexed in situ perspiration analysis. Nature 2016, 529, 509–514. [Google Scholar] [CrossRef] [PubMed]

- Kim, J.; Sempionatto, J.R.; Imani, S.; Hartel, M.C.; Barfidokht, A.; Tang, G.; Campbell, A.S.; Mercier, P.P.; Wang, J. Simultaneous monitoring of sweat and interstitial fluid using a single wearable biosensor platform. Adv. Sci. 2018, 5, 1800880. [Google Scholar] [CrossRef] [PubMed]

- Oh, S.Y.; Hong, S.Y.; Jeong, Y.R.; Yun, J.; Park, H.; Jin, S.W.; Lee, G.; Oh, J.H.; Lee, H.; Lee, S.-S.; et al. Skin-attachable, stretchable electrochemical sweat sensor for glucose and pH detection. ACS Appl. Mater. Interfaces 2018, 10, 13729–13740. [Google Scholar] [CrossRef]

- Sekine, T.; Sugano, R.; Tashiro, T.; Sato, J.; Takeda, Y.; Matsui, H.; Kumaki, D.; Dos Santos, F.D.; Miyabo, A.; Tokito, S. Fully printed wearable vital sensor for human pulse rate monitoring using ferroelectric polymer. Sci. Rep. 2018, 8, 4442. [Google Scholar] [CrossRef]

- Khan, Y.; Garg, M.; Gui, Q.; Schadt, M.; Gaikwad, A.; Han, D.; Yamamoto, N.A.D.; Hart, P.; Welte, R.; Wilson, W.; et al. Flexible hybrid electronics: Direct interfacing of soft and hard electronics for wearable health monitoring. Adv. Funct. Mater. 2016, 26, 8764–8775. [Google Scholar] [CrossRef]

- Jeong, G.S.; Baek, D.-H.; Jung, H.C.; Song, J.H.; Moon, J.H.; Hong, S.W.; Kim, I.Y.; Lee, S.-H. Solderable and electroplatable flexible electronic circuit on a porous stretchable elastomer. Nat. Commun. 2012, 3, 977. [Google Scholar] [CrossRef]

- Strohmeier, P.; Burstyn, J.; Carrascal, J.B.P.; Levesque, V.; Vertegaal, R. ReFlex: A Flexible Smartphone with Active Haptic Feedback for Bend Input. In Proceedings of the TEI’16: Tenth International Conference on Tangible, Embedded, and Embodied Interaction, Eindhoven, The Netherlands, 14–17 February 2016; ACM: Eindhoven, The Netherlands. [Google Scholar]

- Loughran, J. Foldable screens and 5G compatibility steal the show at MWC. Eng. Technol. 2019, 14, 9. [Google Scholar] [CrossRef]

- Chortos, A.; Liu, J.; Bao, Z. Pursuing prosthetic electronic skin. Nat. Mater. 2016, 15, 937–950. [Google Scholar] [CrossRef]

- Gerratt, A.P.; Michaud, H.O.; Lacour, S.P. Elastomeric electronic skin for prosthetic tactile sensation. Adv. Funct. Mater. 2015, 25, 2287–2295. [Google Scholar] [CrossRef]

- Wang, C.; Hwang, D.; Yu, Z.; Takei, K.; Park, J.; Chen, T.; Ma, B.; Javey, A. User-interactive electronic skin for instantaneous pressure visualization. Nat. Mater. 2013, 12, 899–904. [Google Scholar] [CrossRef] [PubMed]

- Hammock, M.L.; Chortos, A.; Tee, B.C.-K.; Tok, J.B.-H.; Bao, Z. 25th anniversary article: The evolution of electronic skin (e-skin): A brief history, design considerations, and recent progress. Adv. Mater. 2013, 25, 5997–6038. [Google Scholar] [CrossRef] [PubMed]

- Yacoub-George, E.; Palavesam, N.; Hell, W.; Koenig, M.; Faul, R.; Landesberger, C. Ultra-thin flexible interposer-a flexible hybrid integration approach to replace wire bonds. In Proceedings of the Smart Systems Integration; 13th International Conference and Exhibition on Integration Issues of Miniaturized Systems, Barcelona, Spain, 10–11 April 2019; VDE: Barcelona, Spain. [Google Scholar]

- Christiaens, W.; Bosman, E.; Vanfleteren, J. UTCP: A novel polyimide-based ultra-thin chip packaging technology. IEEE Trans. Components Packag. Technol. 2010, 33, 754–760. [Google Scholar] [CrossRef]

- Braun, T.; Becker, K.-F.; Raatz, S.; Minkus, M.; Bader, V.; Bauer, J.; Aschenbrenner, R.; Kahle, R.; Georgi, L.; Voges, S.; et al. Foldable fan-out wafer level packaging. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; IEEE: Las Vegas, NV, USA. [Google Scholar]

- Fang, H.; Yu, K.J.; Gloschat, C.; Yang, Z.; Song, E.; Chiang, C.-H.; Zhao, J.; Won, S.M.; Xu, S.; Trumpis, M.; et al. Capacitively coupled arrays of multiplexed flexible silicon transistors for long-term cardiac electrophysiology. Nat. Biomed. Eng. 2017, 1, 0038. [Google Scholar] [CrossRef]

- Burghartz, J.N.; Alavi, G.; Albrecht, B.; Deuble, T.; Elsobky, M.; Ferwana, S.; Harendt, C.; Mahsereci, Y.; Richter, H.; Yu, Z. Hybrid Systems-in-Foil—Combining the Merits of Thin Chips and of Large-Area Electronics. IEEE J. Electron Devices Soc. 2019, 7, 776–783. [Google Scholar] [CrossRef]

- Kobayashi, T.; Takeshita, T.; Takei, Y.; Takei, R. Flexible substrate with movable device island supported by serpentine interconnect for mounting ultra-thin silicon chips. In Proceedings of the 2018 International Conference on Electronics Packaging and iMAPS All Asia Conference (ICEP-IAAC), Mie, Japan, 17–21 April 2018; IEEE: Mie, Japan, 2018. [Google Scholar]

- Kim, H.; Yoo, H.G.; Hong, S.M.; Jang, B.; Park, D.Y.; Joe, D.J.; Kim, J.-H.; Lee, K.J. Simultaneous roll transfer and interconnection of flexible silicon NAND flash memory. Adv. Mater. 2016, 28, 8371–8378. [Google Scholar] [CrossRef]

- Takei, Y.; Nomura, K.-I.; Horii, Y.; Zymelka, D.; Ushijima, H.; Kobayashi, T. Fabrication of Simultaneously Implementing “Wired Face-Up and Face-Down Ultrathin Piezoresistive Si Chips” on a Film Substrate by Screen-Offset Printing. Micromachines 2019, 10, 563. [Google Scholar] [CrossRef]

- Gao, H.; Bhat, G.; Ogras, U.Y.; Ozev, S. Optimized Stress Testing for Flexible Hybrid Electronics Designs. In Proceedings of the 2019 IEEE 37th VLSI Test Symposium (VTS), Monterey, CA, USA, 23–25 April 2019; IEEE: Monterey, CA, USA, 2019. [Google Scholar]

- Kim, Y.-S.; Lu, J.; Shih, B.; Gharibans, A.; Zou, Z.; Matsuno, K.; Aguilera, R.; Han, Y.; Meek, A.; Xiao, J.; et al. Scalable manufacturing of solderable and stretchable physiologic sensing systems. Adv. Mater. 2017, 29, 1701312. [Google Scholar] [CrossRef]

- Palavesam, N.; Marín, S.; Hemmetzberger, D.; Landesberger, C.; Bock, K.; Kutter, C. Roll-to-roll processing of film substrates for hybrid integrated flexible electronics. Flex. Print. Electron. 2018, 3, 014002. [Google Scholar] [CrossRef]

- Palavesam, N.; Landesberger, C.; Kutter, C.; Bock, K. A novel test method for robustness assessment of very small, functional ultra-thin chips embedded in flexible foils. In Proceedings of the 10th Smart Systems Integration Conference (SSI 2016), Munich, Germany, 9–10 March 2016. [Google Scholar]

- Palavesam, N.; Landesberger, C.; Kutter, C.; Bock, K. Finite element analysis of uniaxial bending of ultra-thin silicon dies embedded in flexible foil substrates. In Proceedings of the 2015 11th Conference on Ph. D. Research in Microelectronics and Electronics (PRIME), Glasgow, UK, 29 June–2 July 2015; IEEE: Glasgow, UK, 2015. [Google Scholar]

- Palavesam, N.; Landesberger, C.; Bock, K. Investigations of the fracture strength of thin silicon dies embedded in flexible foil substrates. In Proceedings of the 2014 IEEE 20th International Symposium for Design and Technology in Electronic Packaging (SIITME), Bucharest, Romania, 23–26 October 2014; IEEE: Bucharest, Romania, 2014. [Google Scholar]

- Palavesam, N.; Hell, W.; Drost, A.; Landesberger, C.; Kutter, C.; Bock, K. A novel low cost roll-to-roll manufacturing compatible ultra-thin chip integration and direct metal interconnection process for flexible hybrid electronics. In Proceedings of the Additional Conferences (Device Packaging, HiTEC, HiTEN, & CICMT), Copenhagen, Denmark, 11–13 June 2019; No. NOR. International Microelectronics Assembly and Packaging Society: Copenhagen, Denmark; Vol. 2019. [Google Scholar]

- Ende, D.V.D.; Van De Wiel, H.; Kusters, R.; Sridhar, A.; Schram, J.; Cauwe, M.; Brand, J.V.D. Mechanical and electrical properties of ultra-thin chips and flexible electronics assemblies during bending. Microelectron. Reliab. 2014, 54, 2860–2870. [Google Scholar] [CrossRef]

- Wacker, N.; Richter, H.; Hoang, T.; Gazdzicki, P.; Schulze, M.; A Angelopoulos, E.; Hassan, M.-U.; Burghartz, J.N. Stress analysis of ultra-thin silicon chip-on-foil electronic assembly under bending. Semicond. Sci. Technol. 2014, 29, 095007. [Google Scholar] [CrossRef]

- Kim, J.-H.; Lee, T.-I.; Shin, J.-W.; Kim, T.-S.; Paik, K.-W. Bending properties of anisotropic conductive films assembled chip-in-flex packages for wearable electronics applications. IEEE Trans. Components, Packag. Manuf. Technol. 2016, 6, 208–215. [Google Scholar] [CrossRef]

- Leber, D.E.; Meek, B.N.; Leija, S.D.; Wilson, D.G.; Chaney, R.L.; Hackler, D.R. Electromechanical reliability testing of flexible hybrid electronics incorporating FleX silicon-on-polymer ICs. In Proceedings of the 2016 IEEE Workshop on Microelectronics and Electron Devices (WMED), Boise, ID, USA, 15 April 2016; IEEE: Boise, ID, USA, 2016. [Google Scholar]

- Palavesam, N.; Bonfert, D.; Hell, W.; Landesberger, C.; Gieser, H.; Kutter, C.; Bock, K. Mechanical Reliability Analysis of Ultra-thin Chip-on-Foil Assemblies under different types of recurrent bending. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; IEEE: Las Vegas, NV, USA, 2016. [Google Scholar]

- Palavesam, N.; Yacoub-George, E.; Hell, W.; Landesberger, C.; Kutter, C.; Bock, K. Dynamic Bending Reliability Analysis of Flexible Hybrid Integrated Chip-Foil Packages. In Proceedings of the 2018 IEEE 20th Electronics Packaging Technology Conference (EPTC), Singapore, 4–7 December 2018; IEEE: Singapore, 2018. [Google Scholar]

- Liss, K.D.; Qu, D.; Yan, K.; Reid, M. Variability of Poisson’s ratio and enhanced ductility in amorphous metal. Adv. Eng. Mater. 2013, 15, 347–351. [Google Scholar] [CrossRef]

- Greaves, G.N.; Greer, A.L.; Lakes, R.S.; Rouxel, T. Poisson’s ratio and modern materials. Nat. Mater. 2011, 10, 823–837. [Google Scholar] [CrossRef] [PubMed]

- Gu, X.; Poon, S.J.; Shiflet, G.J.; Widom, M. Ductility improvement of amorphous steels: Roles of shear modulus and electronic structure. Acta Mater. 2008, 56, 88–94. [Google Scholar] [CrossRef]

- Oehlers, D.; Seracino, R. Design of FRP and Steel Plated RC Structures: Retrofitting Beams and Slabs for Strength, Stiffness and Ductility; Elsevier: Amsterdam, The Netherlands, 2004; pp. 46–99. [Google Scholar]

- Yang, S.-Y.; Yuan, L.-L. Advanced Polyimide Films. In Advanced Polyimide Materials; Elsevier: Amsterdam, The Netherlands, 2018; pp. 1–66. [Google Scholar]

- Znajdek, K.; Sibinski, M.; Strąkowska, A.; Lisik, Z. Polymer substrates for flexible photovoltaic cells application in personal electronic system. Opto Electron. Rev. 2016, 24, 20–24. [Google Scholar] [CrossRef]

- Sroog, C.E. Films, Mouldings and other Applications. In Polyimides; Springer: Dordrecht, The Netherlands, 1990; pp. 252–284. [Google Scholar]

- Landesberger, C.; Scherbaum, S.; Karlheinz, B. Ultra-thin wafer fabrication through dicing-by-thinning. In Ultra-Thin Chip Technology and Applications; Springer: New York, NY, USA, 2011; pp. 33–43. [Google Scholar]

- Landesberger, C.; Paschke, C.; Bock, K. Influence of wafer grinding and etching techniques on the fracture strength of thin silicon substrates. In Advanced Materials Research; Trans Tech Publications: Stafa-Zurich, Switzerland, 2011; Volume 325. [Google Scholar]

- Delo® Monopox AC245 Technical Information. Available online: https://www.delo-adhesives.com/fileadmin/datasheet/DELO%20MONOPOX_AC245_%28TIDB-GB%29.pdf (accessed on 11 January 2020).

- Gouldstone, A.; Koh, H.-J.; Zeng, K.-Y.; Giannakopoulos, A.; Suresh, S. Discrete and continuous deformation during nanoindentation of thin films. Acta Mater. 2000, 48, 2277–2295. [Google Scholar] [CrossRef]

- Baek, C.W.; Kim, J.M.; Kim, Y.K.; Kim, J.H.; Lee, H.J.; Han, S.W. Mechanical characterization of gold thin films based on strip bending and nanoindentation test for MEMS/NEMS applications. Sens. Mater. 2005, 17, 277–288. [Google Scholar]

- Baek, C.-W.; Kim, Y.-K.; Ahn, Y.; Kim, Y.-H. Measurement of the mechanical properties of electroplated gold thin films using micromachined beam structures. Sens. Actuators A Phys. 2005, 117, 17–27. [Google Scholar] [CrossRef]

- Frolov, T.; Boettinger, W.; Mishin, Y. Atomistic simulation of hillock growth. Acta Mater. 2010, 58, 5471–5480. [Google Scholar] [CrossRef]

- Wang, D. Fatigue Behavior of Thin Cu Films: Film Thickness and Interface Effects. Ph.D. Thesis, University of Stuttgart, Stuttgart, Germany, 2007. [Google Scholar]

- Mönig, R. Thermal Fatigue of Cu Thin Films. Ph.D. Thesis, University of Stuttgart, Stuttgart, Germany, 2005. [Google Scholar]

- Eberl, C. Fatigue of Al Thin Films at Ultra High Frequencies. Ph.D. Thesis, University of Stuttgart, Stuttgart, Germany, 2005. [Google Scholar]

- Kim, D.-K.; Nix, W.D.; Deal, M.D.; Plummer, J.D. Creep-controlled diffusional hillock formation in blanket aluminum thin films as a mechanism of stress relaxation. J. Mater. Res. 2000, 15, 1709–1718. [Google Scholar] [CrossRef]

- Eve, S.; Huber, N.; Last, A.; Kraft, O. Fatigue behavior of thin Au and Al films on polycarbonate and polymethylmethacrylate for micro-optical components. Thin Solid Films 2009, 517, 2702–2707. [Google Scholar] [CrossRef]

- Lee, H.-Y.; Yi, S.-M.; Lee, J.-H.; Lee, H.-S.; Hyun, S.; Joo, Y.-C. Effects of bending fatigue on the electrical resistance in metallic films on flexible substrates. Met. Mater. Int. 2010, 16, 947–951. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Palavesam, N.; Hell, W.; Drost, A.; Landesberger, C.; Kutter, C.; Bock, K. Influence of Flexibility of the Interconnects on the Dynamic Bending Reliability of Flexible Hybrid Electronics. Electronics 2020, 9, 238. https://doi.org/10.3390/electronics9020238

Palavesam N, Hell W, Drost A, Landesberger C, Kutter C, Bock K. Influence of Flexibility of the Interconnects on the Dynamic Bending Reliability of Flexible Hybrid Electronics. Electronics. 2020; 9(2):238. https://doi.org/10.3390/electronics9020238

Chicago/Turabian StylePalavesam, Nagarajan, Waltraud Hell, Andreas Drost, Christof Landesberger, Christoph Kutter, and Karlheinz Bock. 2020. "Influence of Flexibility of the Interconnects on the Dynamic Bending Reliability of Flexible Hybrid Electronics" Electronics 9, no. 2: 238. https://doi.org/10.3390/electronics9020238

APA StylePalavesam, N., Hell, W., Drost, A., Landesberger, C., Kutter, C., & Bock, K. (2020). Influence of Flexibility of the Interconnects on the Dynamic Bending Reliability of Flexible Hybrid Electronics. Electronics, 9(2), 238. https://doi.org/10.3390/electronics9020238