A New High Voltage Gain DC to DC Converter with Low Voltage Stress for Energy Storage System Application

Abstract

1. Introduction

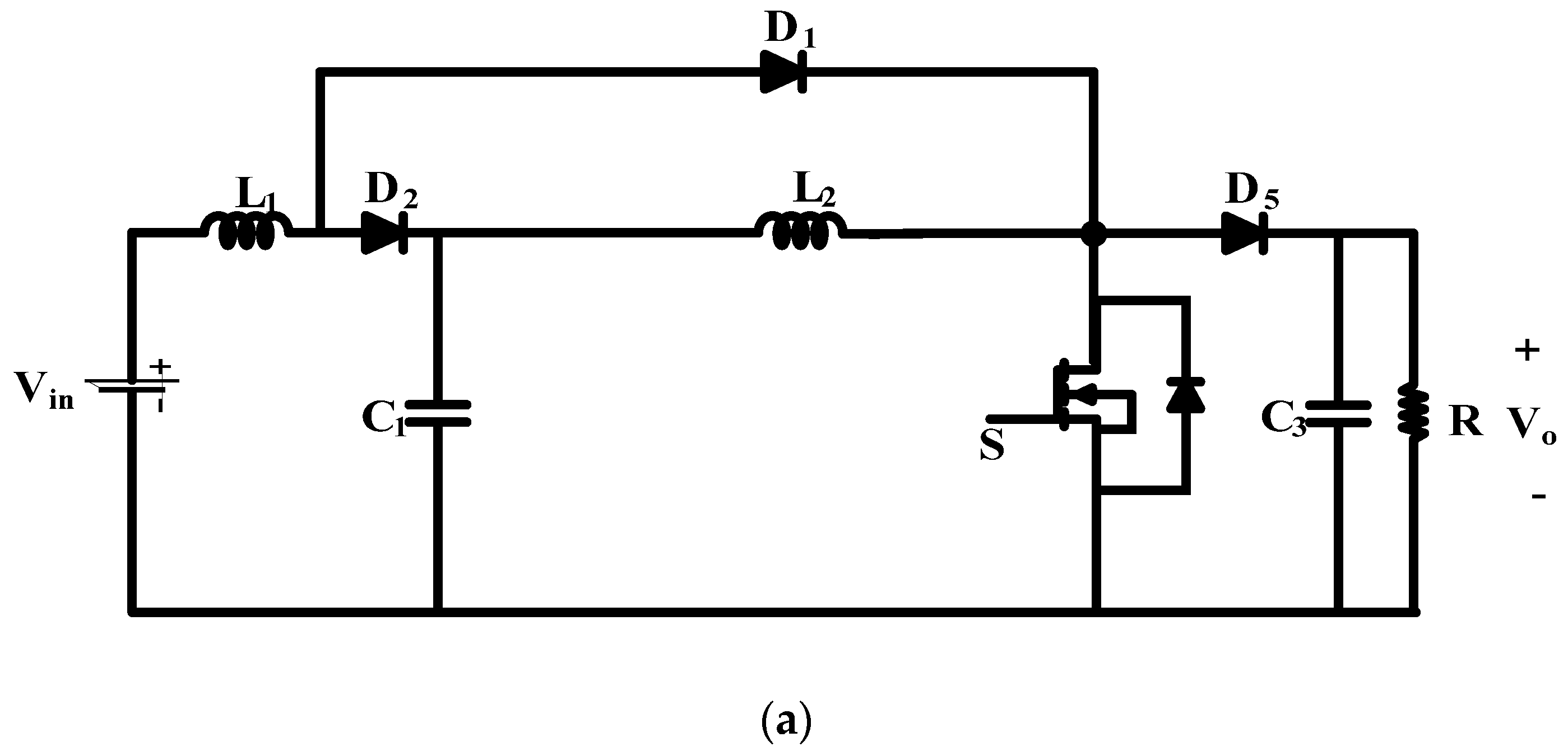

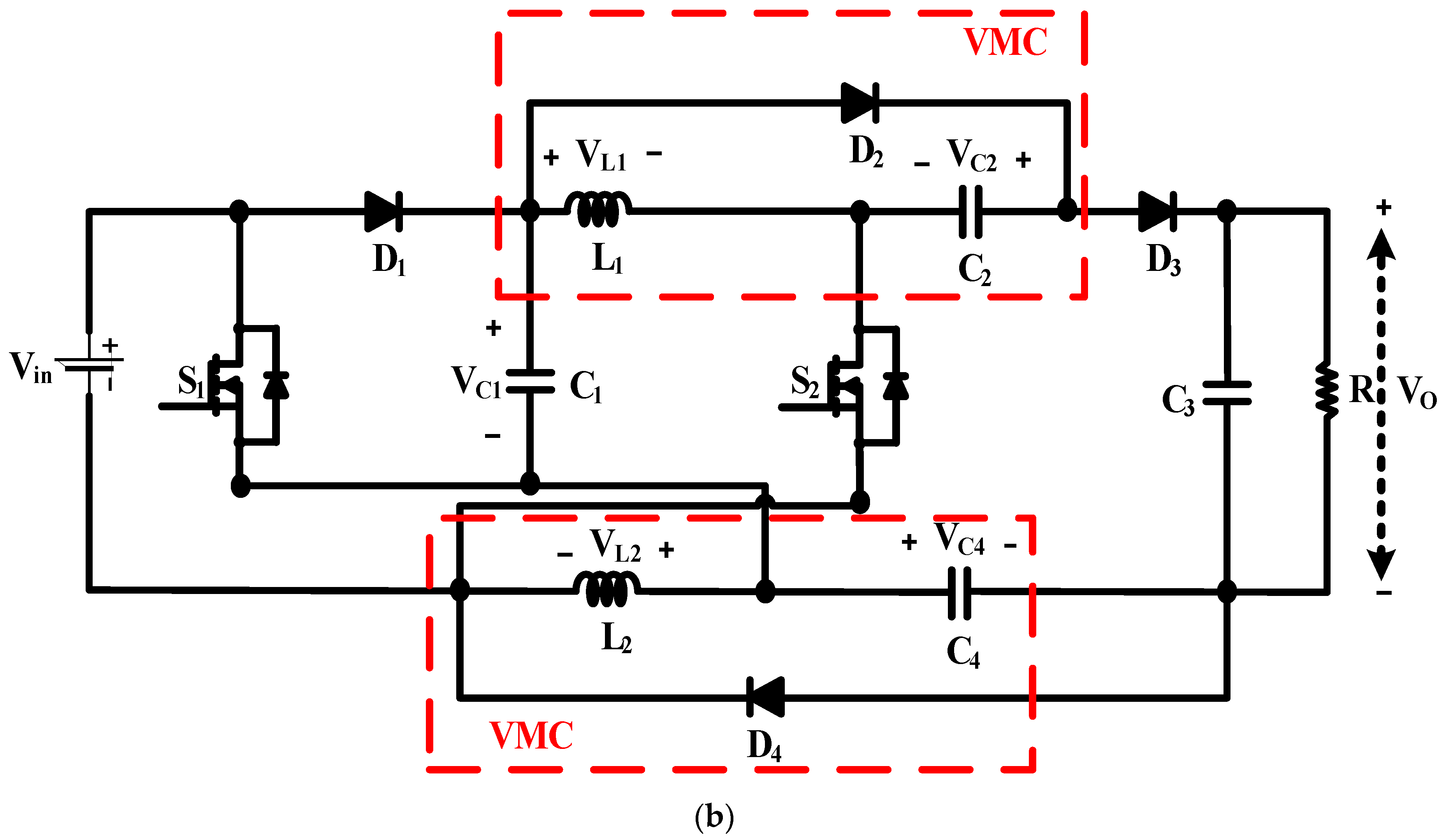

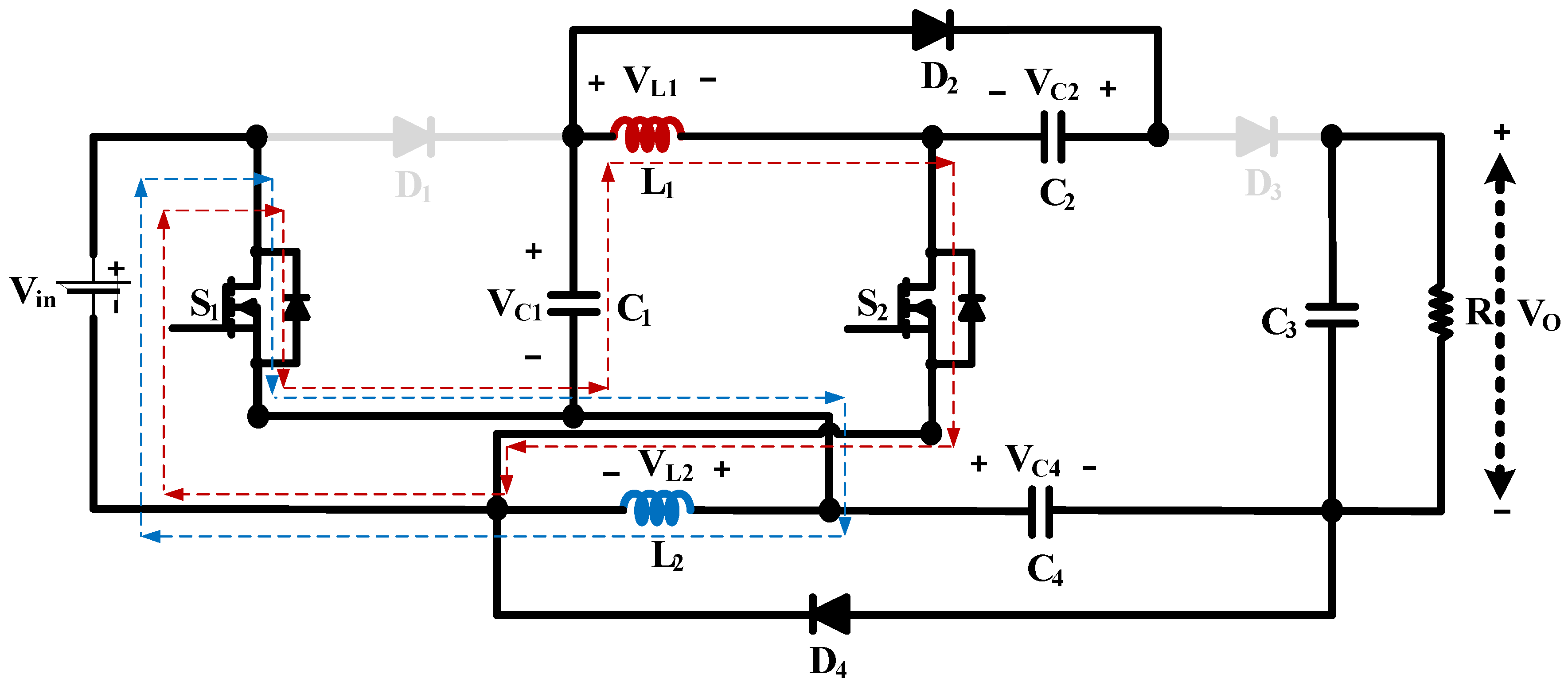

2. Proposed Topology

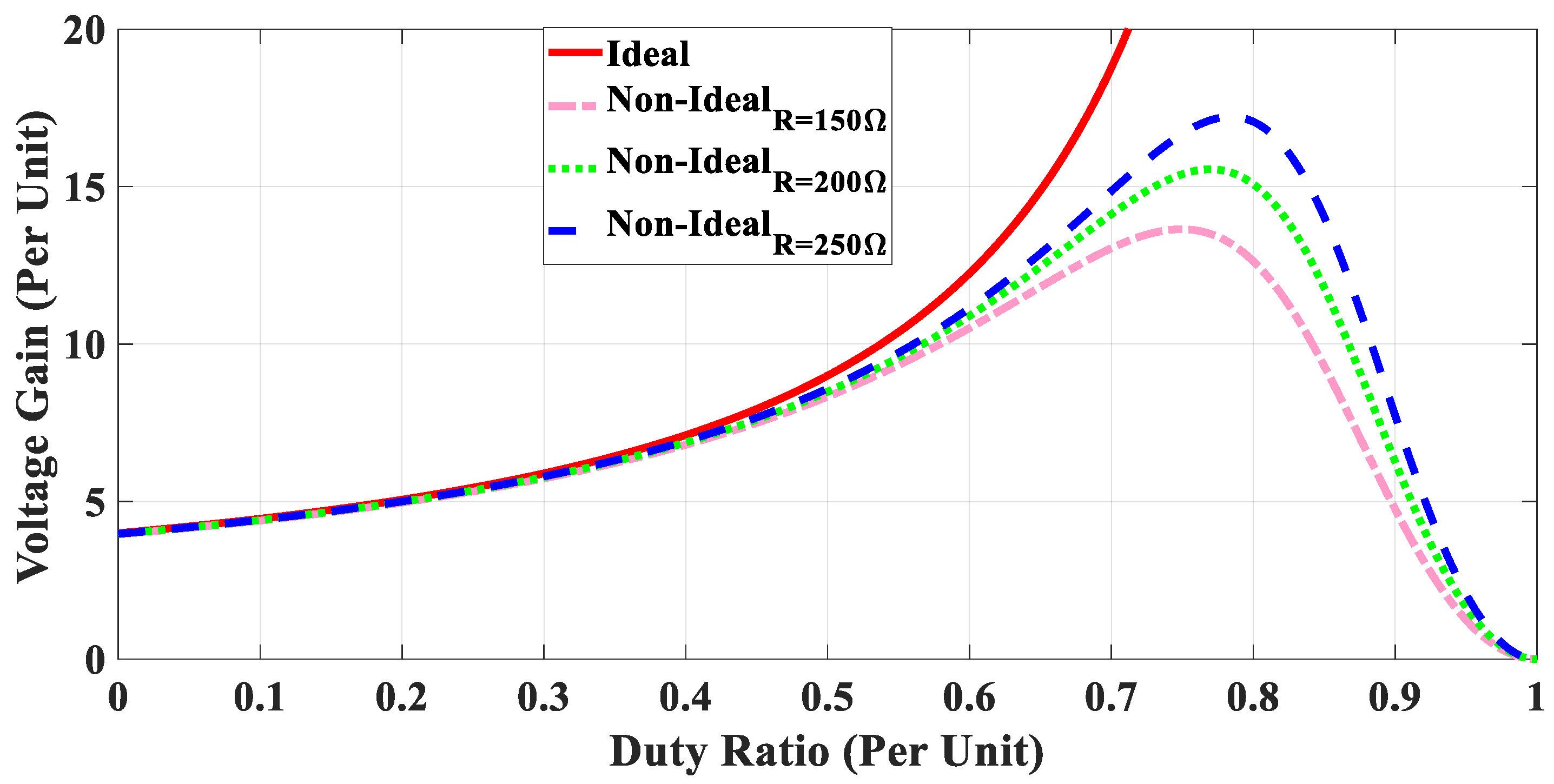

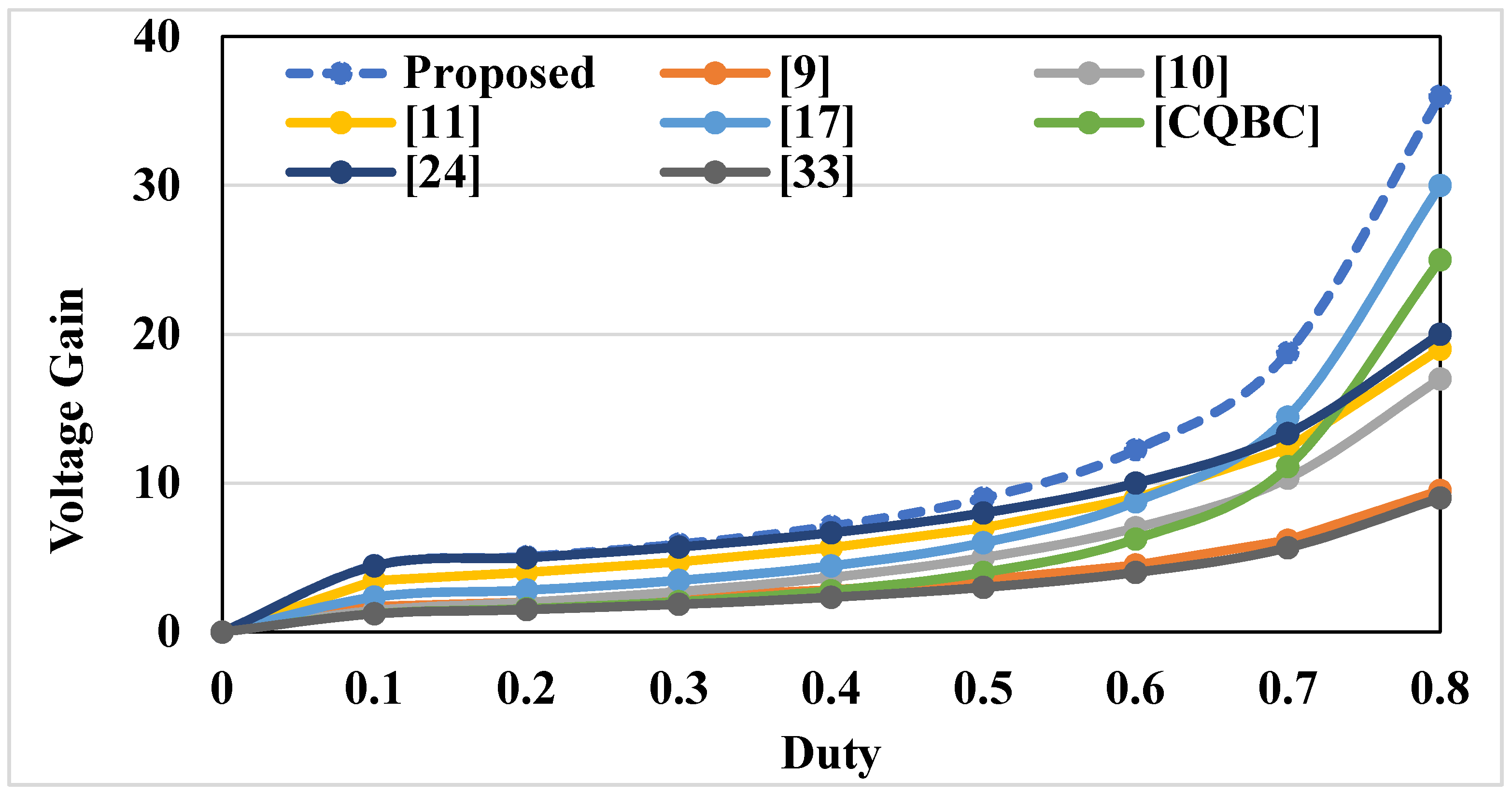

Effect of Inductor’s Parasitic Resistance on Voltage Gain

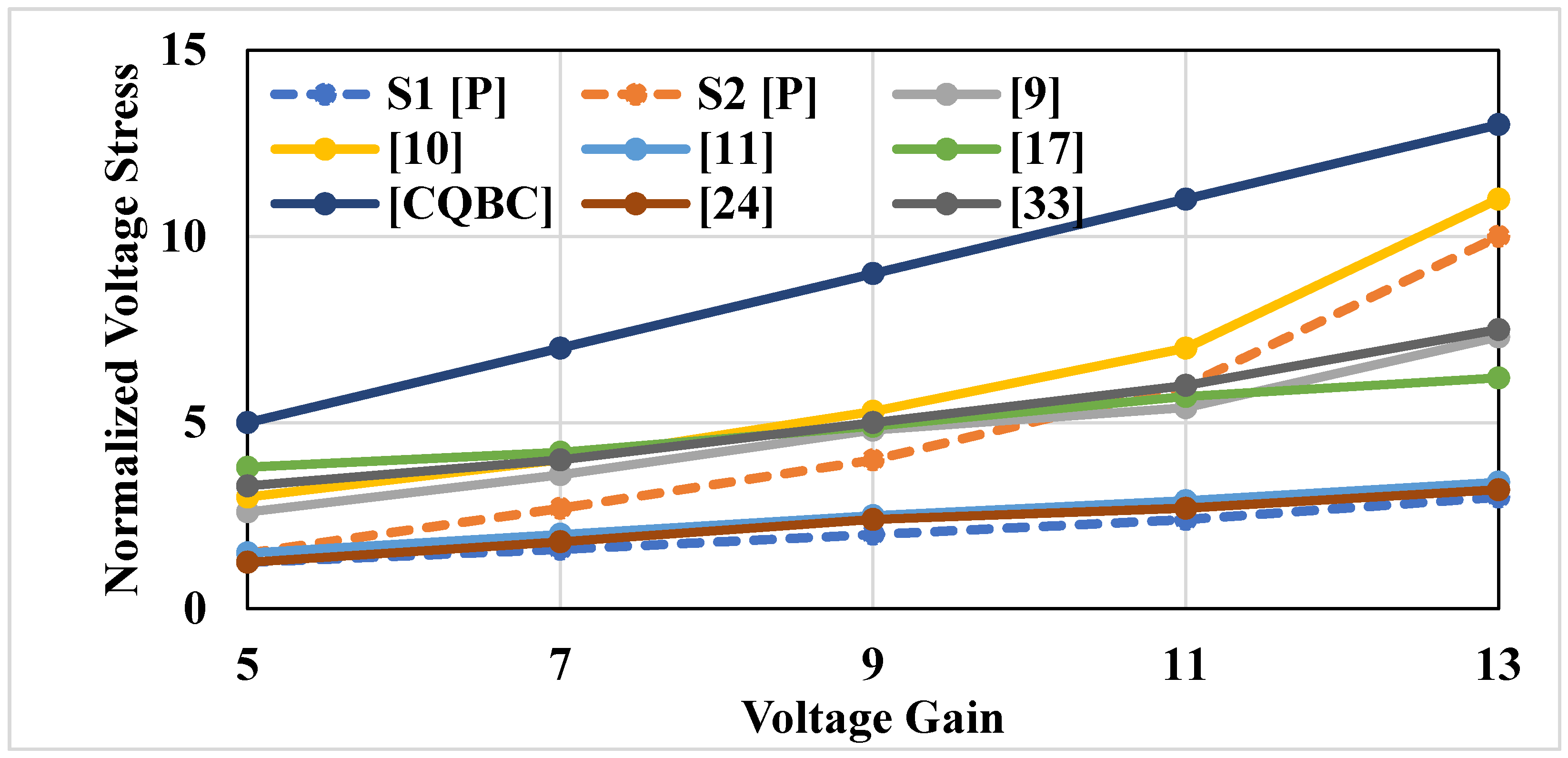

3. Voltage Stress, Current and Passive Component Selection

4. Comparison with Other Recent Topologies

5. Simulation Results and Experimental Verification of the Proposed Converter

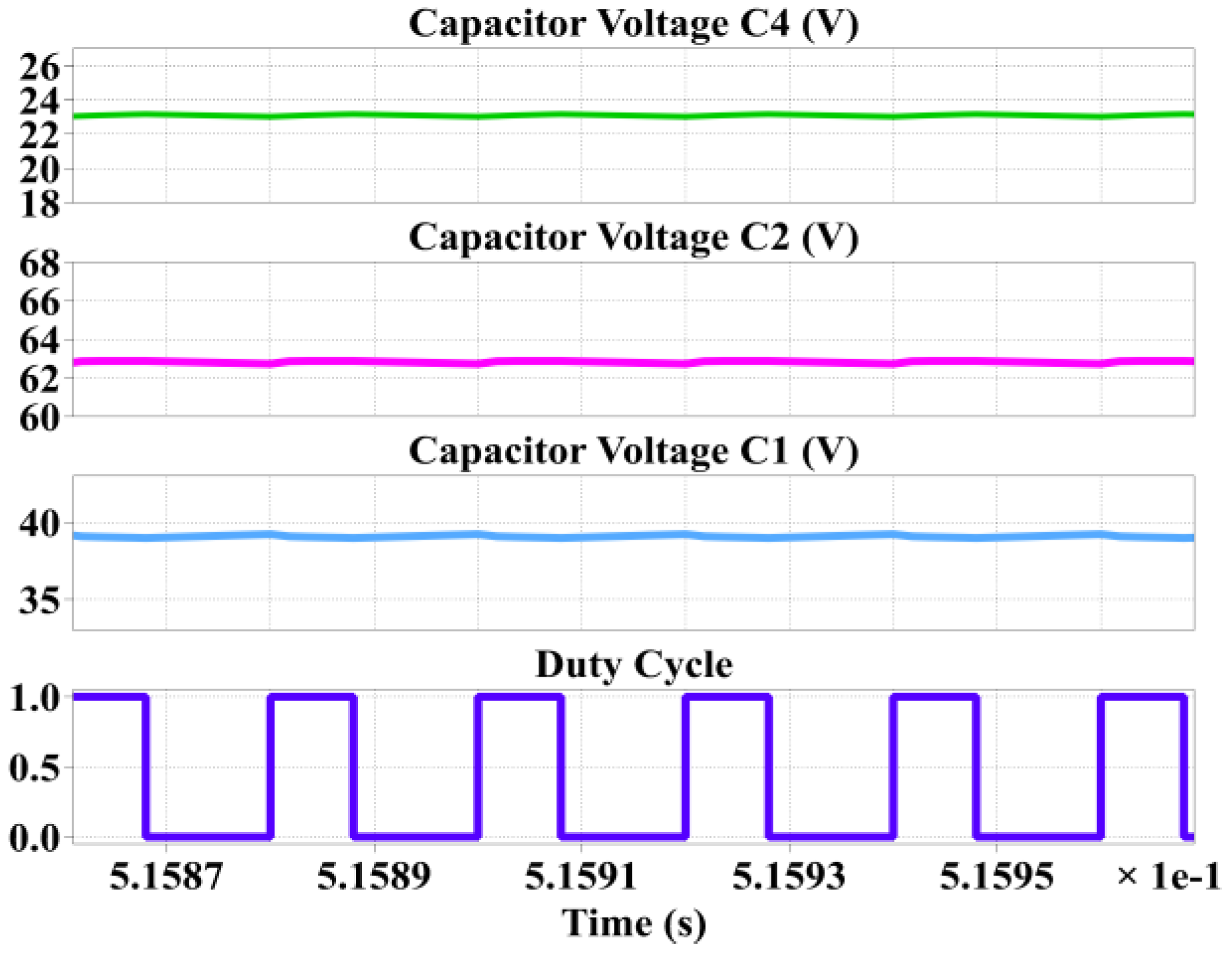

5.1. Simulation Results

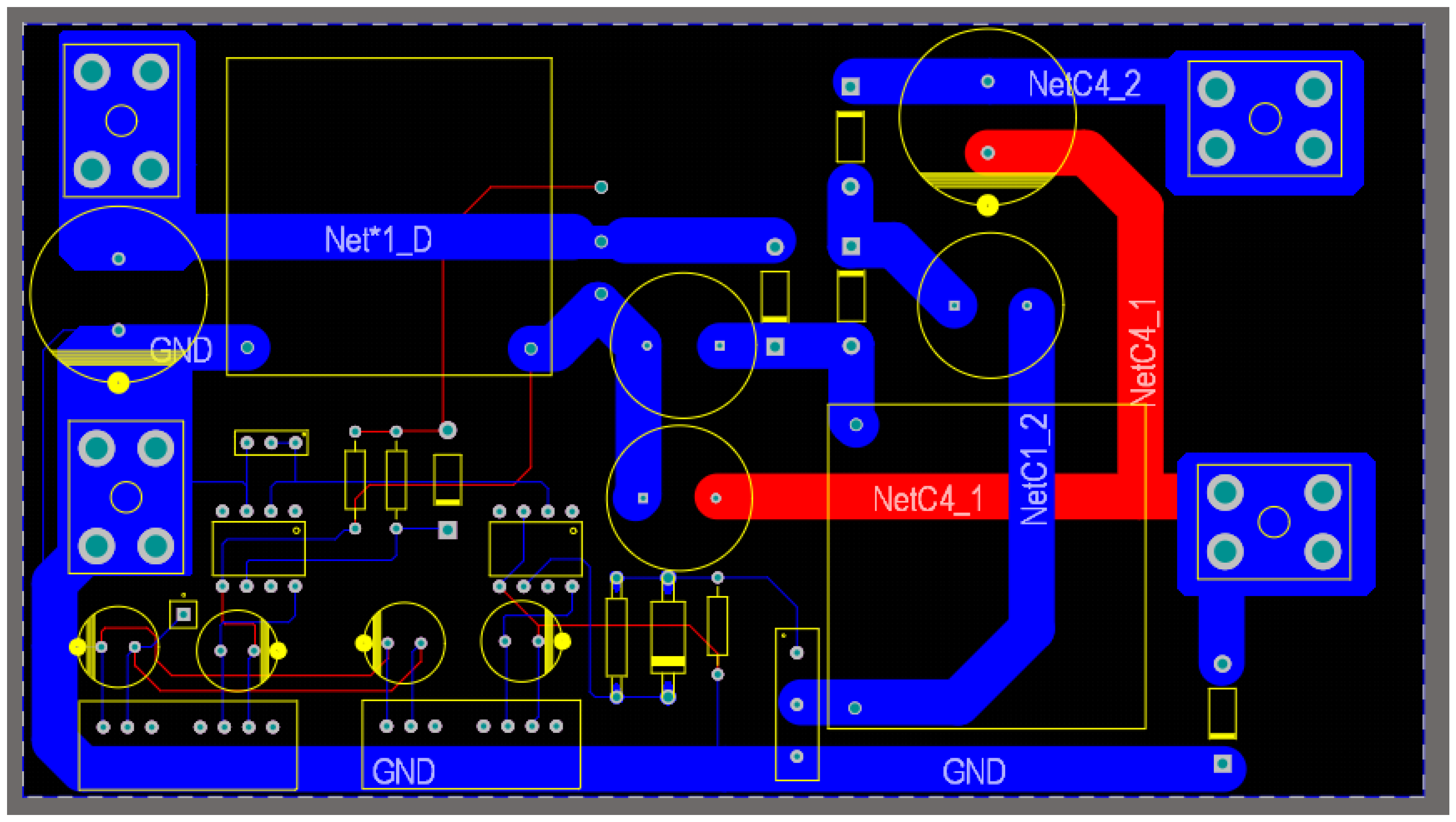

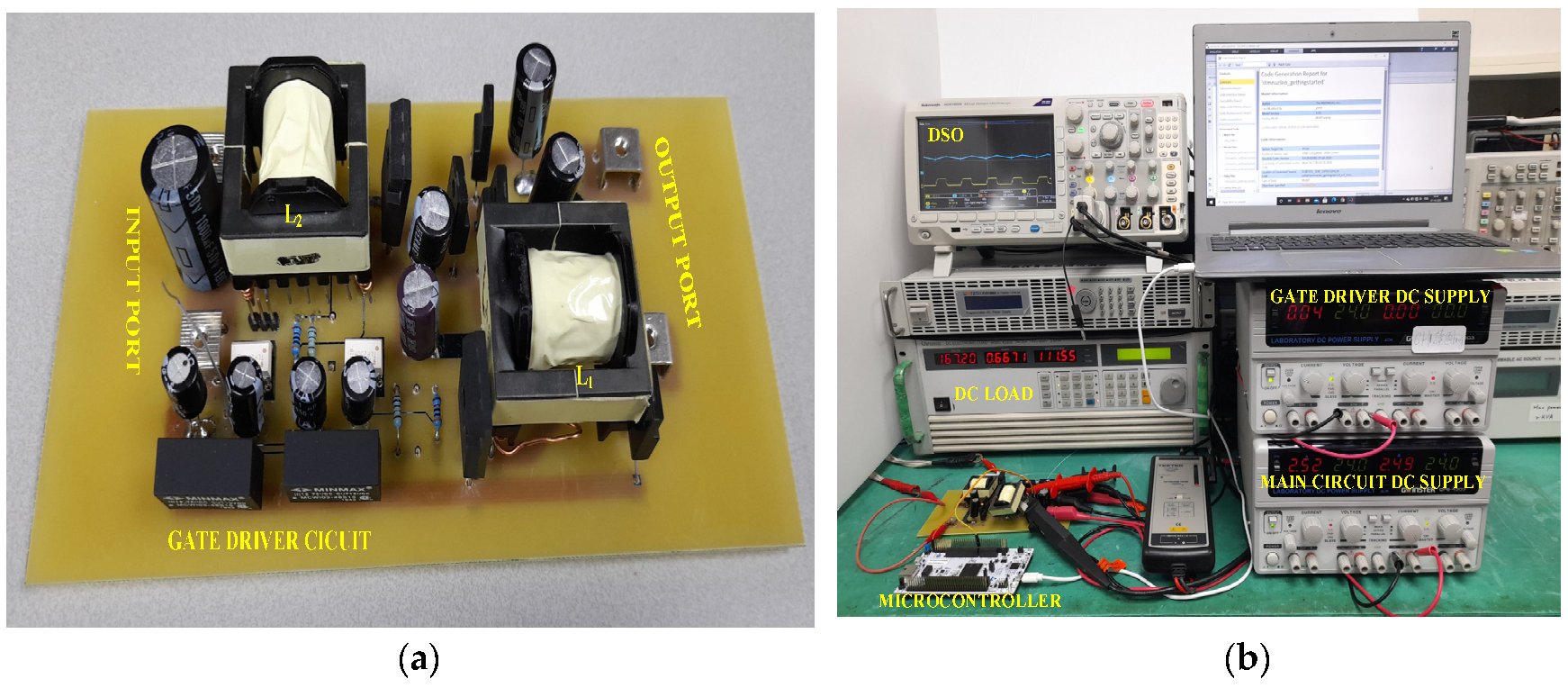

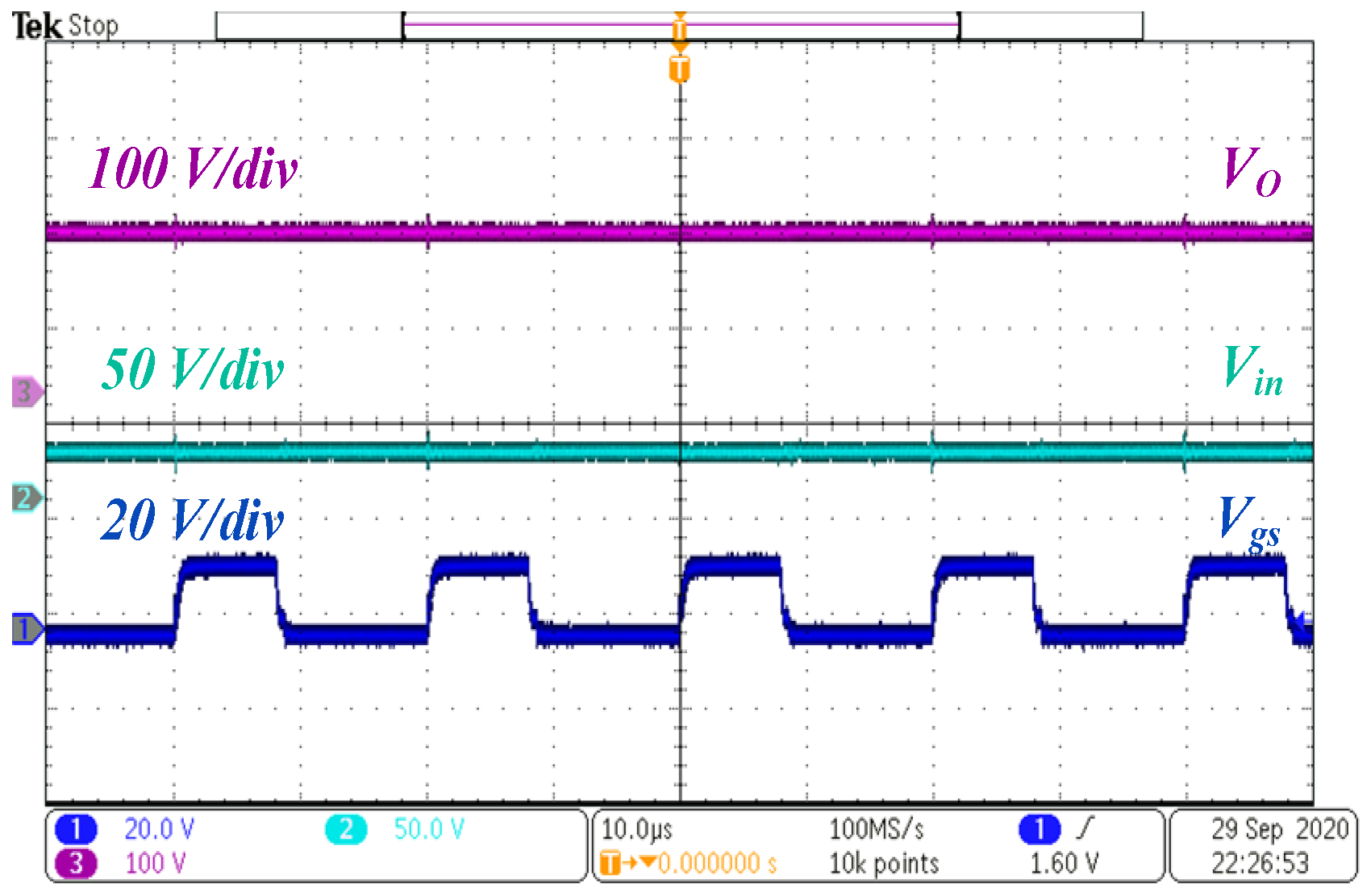

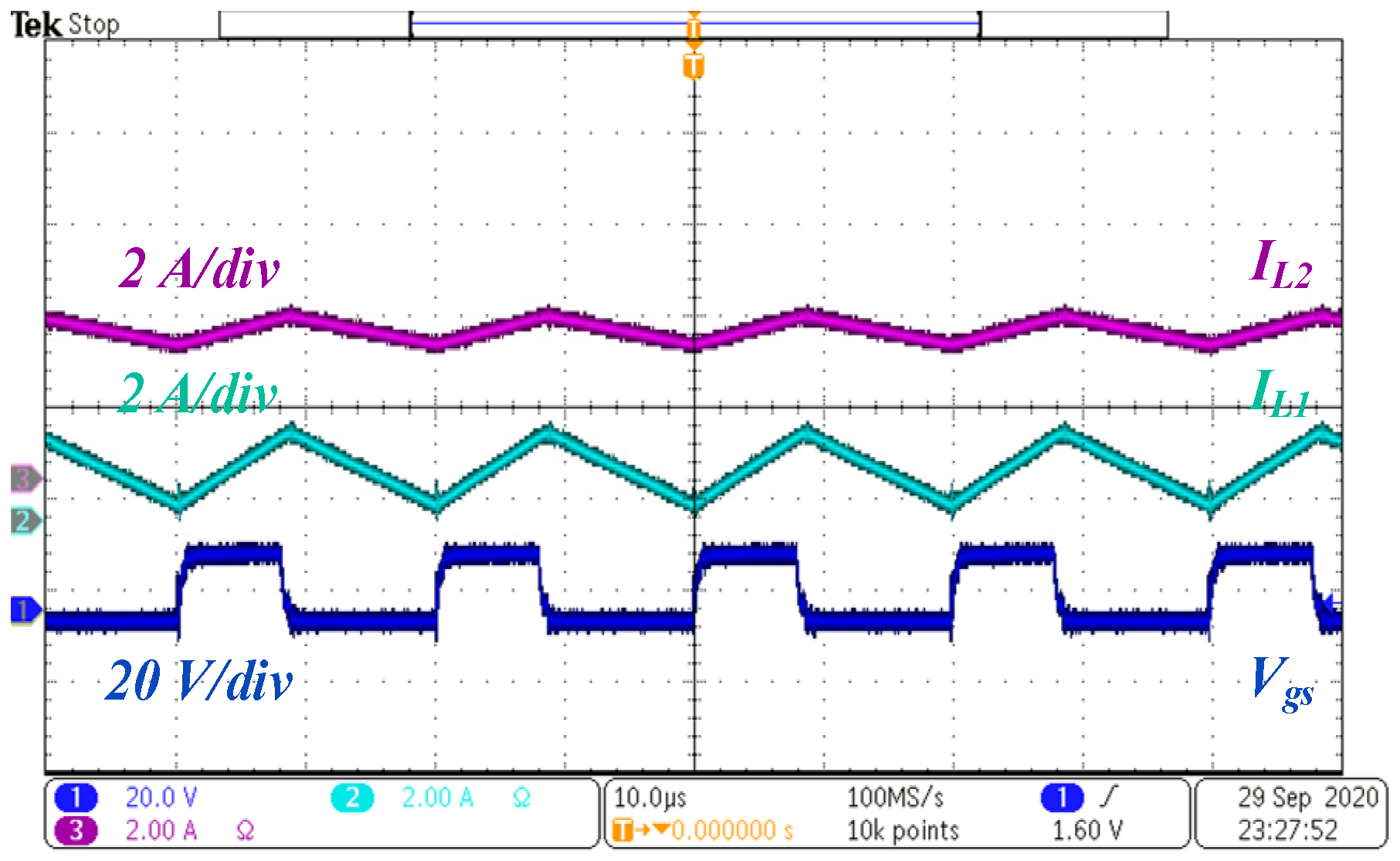

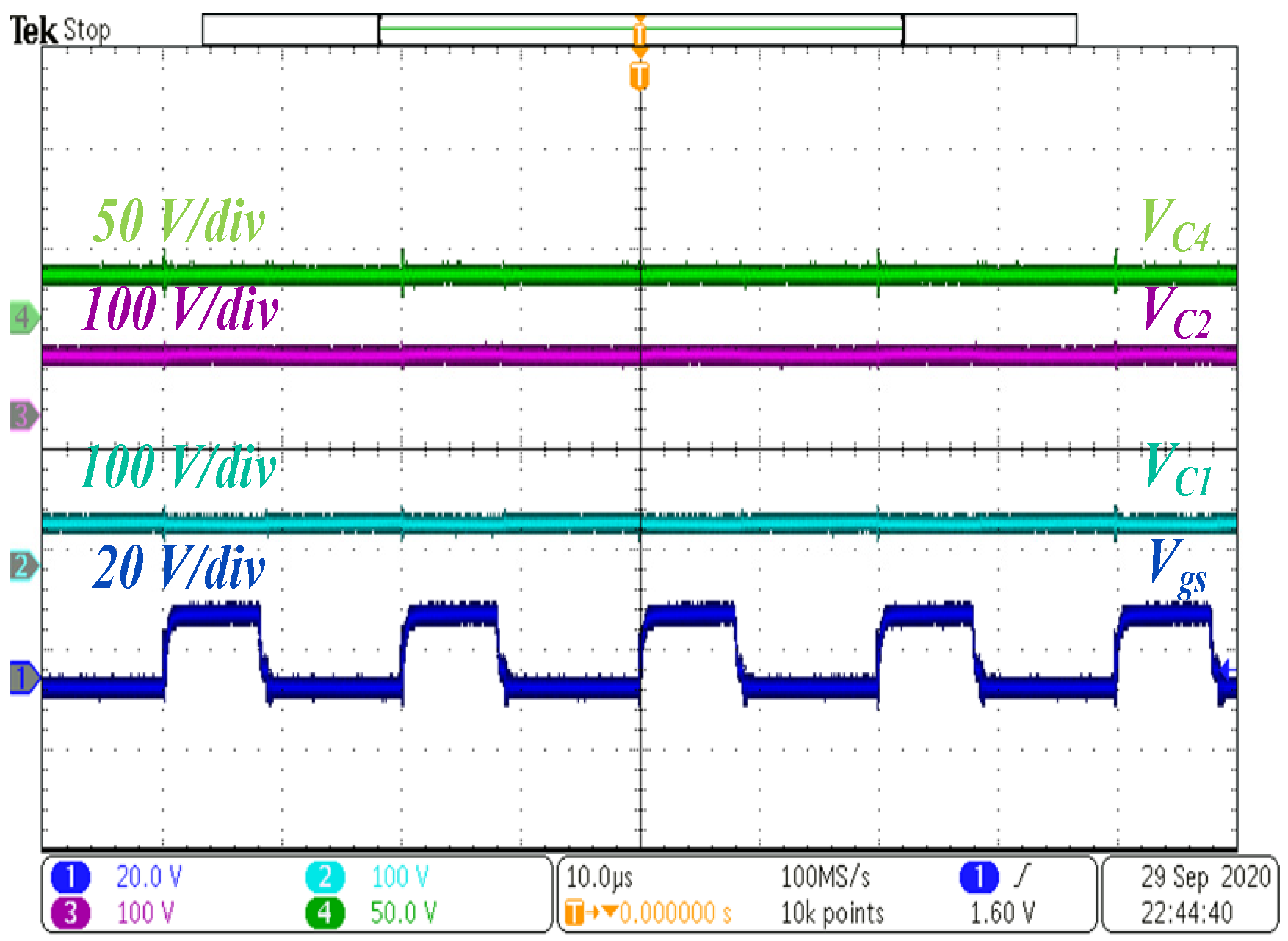

5.2. Experimental Verification

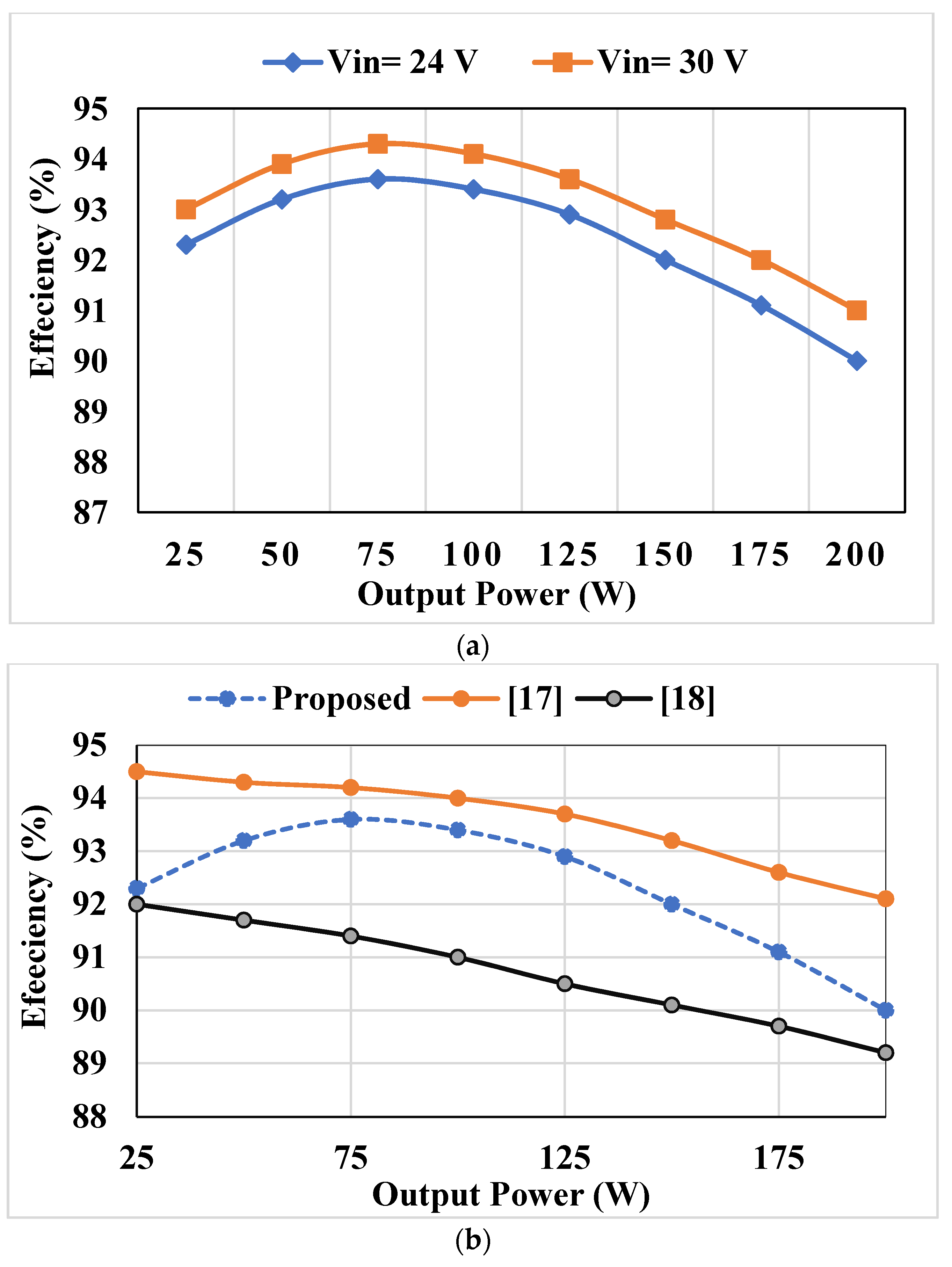

6. Efficiency Calculation

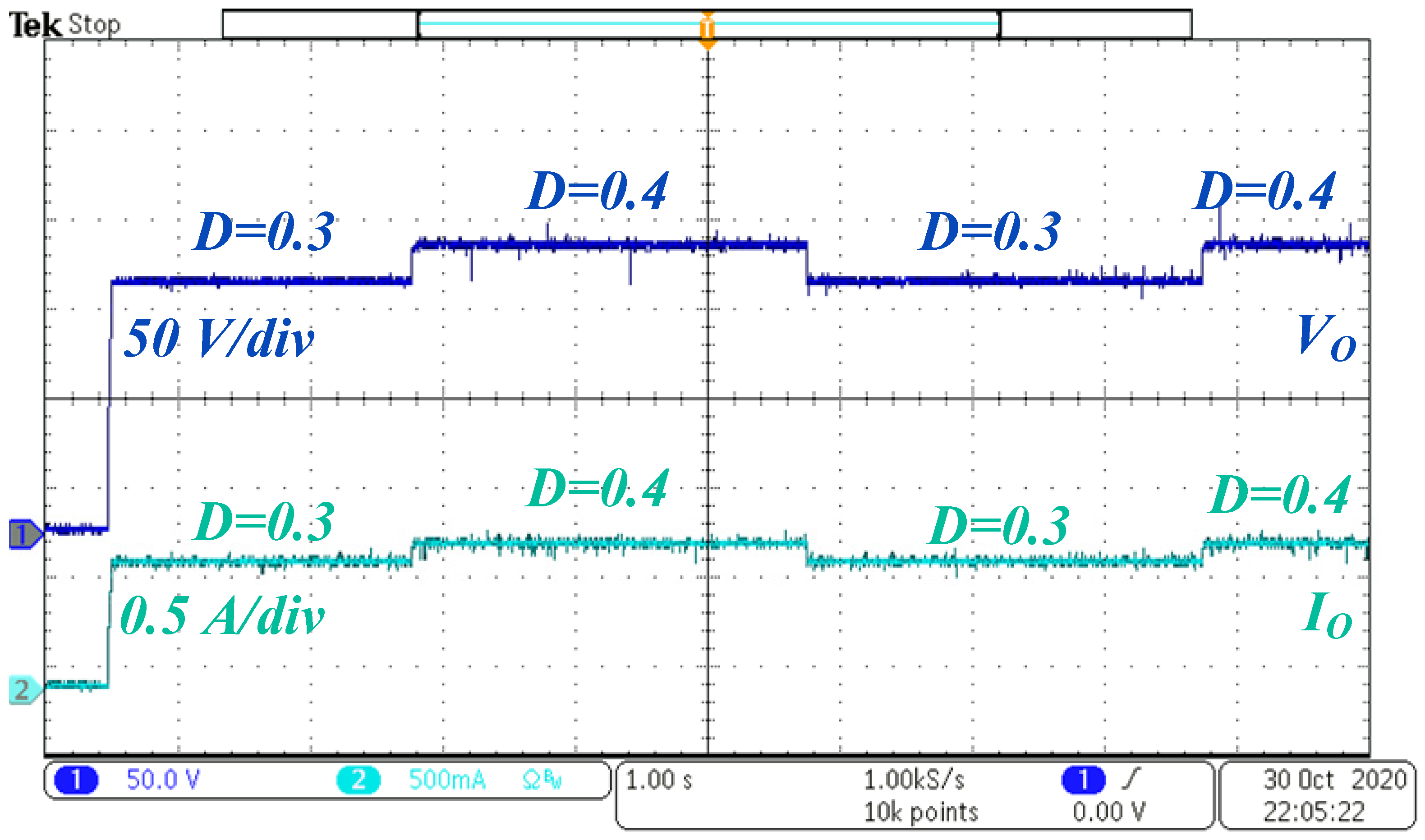

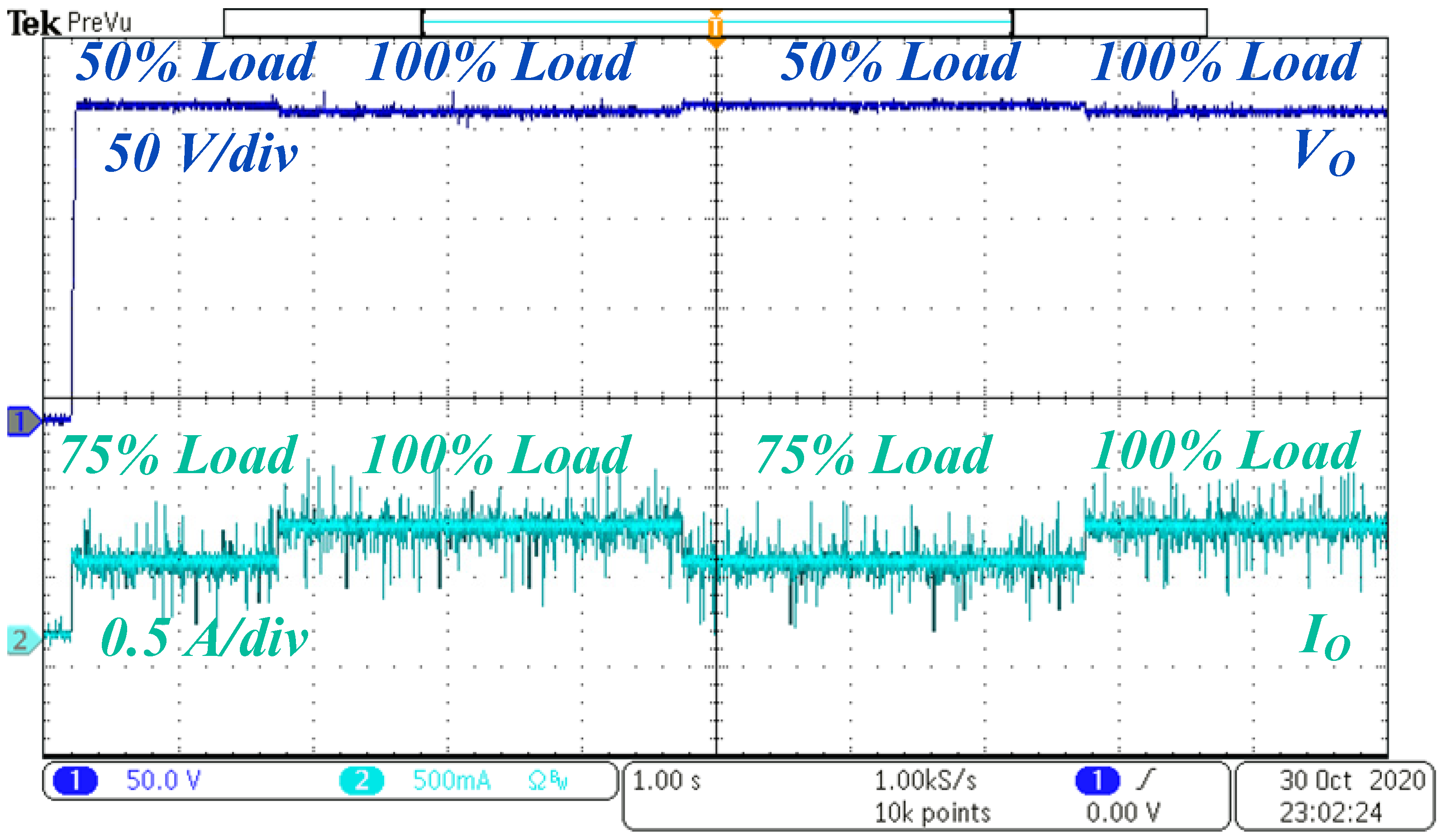

7. Performance of the Proposed Converter in Dynamic Conditions

8. Discussion

9. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviation

| Input Voltage | |

| Output Voltage | |

| Inductor Voltage | |

| Capacitor Voltage | |

| Capacitor Voltage Ripple | |

| Inductor Current Ripple | |

| R | Load Resistance |

| D | Duty Ratio |

| Input Power | |

| Output Power | |

| Power Loss | |

| rL1,rL2 | Parasitic resistance of inductor |

| rC1,rC2,rC3,rC4 | Parasitic resistance of capacitors |

| rD1,rD2,rD3,rD4 | Parasitic resistance of diodes |

References

- Almalaq, Y.; Matin, M. Three Topologies of a Nonisolated High Gain Switched-Inductor Switched-Capacitor Step-Up Cuk Converter for Renewable Energy Applications. Electronics 2018, 7, 94. [Google Scholar] [CrossRef]

- Padmanaban, S.; Bhaskar, M.S.; Maroti, P.K.; Blaabjerg, F.; Fedák, V. An Original Transformer and Switched-Capacitor (T & SC)-Based Extension for DC-DC Boost Converter for High-Voltage/Low-Current Renewable Energy Applications: Hardware Implementation of a New T & SC Boost Converter. Energies 2018, 11, 783. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Ramachandaramurthy, V.K.; Padmanaban, S.; Blaabjerg, F.; Ionel, D.M.; Mitolo, M.; Almakhles, D. Survey of DC-DC Non-Isolated Topologies for Unidirectional Power Flow in Fuel Cell Vehicles. IEEE Access 2020, 8, 178130–178166. [Google Scholar] [CrossRef]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Tofoli, F.L.; De Pereira, D.C.; Josias de Paula, W.; de Oliveira Júnior, D.S. Survey on nonisolated high-voltage step-up dc–dc topologies based on the boost converter. IET Power Electron. 2015, 8, 2044–2057. [Google Scholar] [CrossRef]

- Rosas-Caro, J.C.; Ramirez, J.M.; Peng, F.Z.; Valderrabano, A. A DC-DC multilevel boost converter. IET Power Electron. 2010, 3, 129–137. [Google Scholar] [CrossRef]

- Sarikhani, A.; Allahverdinejad, B.; Hamzeh, M. A Non-Isolated Buck-Boost DC-DC Converter with Continuous Input Current for Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2020. [Google Scholar] [CrossRef]

- Shahir, F.M.; Babaei, E.; Farsadi, M. Extended Topology for a Boost DC–D.C. Converter. IEEE Trans. Power Electron. 2019, 34, 2375–2384. [Google Scholar] [CrossRef]

- Saravanan, S.; Babu, N.R. Design and Development of Single Switch High Step-Up DC–D.C. Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 855–863. [Google Scholar] [CrossRef]

- Tang, Y.; Fu, D.; Wang, T.; Xu, Z. Hybrid Switched-Inductor Converters for High Step-Up Conversion. IEEE Trans. Ind. Electron. 2015, 62, 1480–1490. [Google Scholar] [CrossRef]

- Tang, Y.; Wang, T.; He, Y. A Switched-Capacitor-Based Active-Network Converter With High Voltage Gain. IEEE Trans. Power Electron. 2014, 29, 2959–2968. [Google Scholar] [CrossRef]

- Arunkumari, T.; Indragandhi, V.; Arunkumar, G.; Sanjeevikumar, P.; Holm-Nielsen, J.B. Implementation of high-gain nonisolated DC-DC converter for PV-fed applications. Int. Trans. Electr. Energy Syst. 2020, 30, e12165. [Google Scholar] [CrossRef]

- Wu, G.; Ruan, X.; Ye, Z. Nonisolated High Step-Up DC–D.C. Converters Adopting Switched-Capacitor Cell. IEEE Trans. Ind. Electron. 2015, 62, 383–393. [Google Scholar] [CrossRef]

- Miao, S.; Wang, F.; Ma, X. A New Transformerless Buck–Boost Converter With Positive Output Voltage. IEEE Trans. Ind. Electron. 2016, 63, 2965–2975. [Google Scholar] [CrossRef]

- Saadat, P.; Abbaszadeh, K. A Single-Switch High Step-Up DC–D.C. Converter Based on Quadratic Boost. IEEE Trans. Ind. Electron. 2016, 63, 7733–7742. [Google Scholar] [CrossRef]

- Moradpour, R.; Tavakoli, A. A DC–D.C. boost converter with high voltage gain integrating three-winding coupled inductor with low input current ripple. Int. Trans. Electr. Energy Syst. 2020, 30, e12383. [Google Scholar] [CrossRef]

- Lee, S.-W.; Do, H.-L. Quadratic Boost DC–D.C. Converter With High Voltage Gain and Reduced Voltage Stresses. IEEE Trans. Power Electron. 2019, 34, 2397–2404. [Google Scholar] [CrossRef]

- Wang, Y.; Qiu, Y.; Bian, Q.; Guan, Y.; Xu, D. A Single Switch Quadratic Boost High Step Up DC–D.C. Converter. IEEE Trans. Ind. Electron. 2019, 66, 4387–4397. [Google Scholar] [CrossRef]

- Bhaskar, M.S.; Almakhles, D.J.; Padmanaban, S.; Holm-Nielsen, J.B.; Kumar, A.R.; Masebinu, S.O. Triple-Mode Active-Passive Parallel Intermediate Links Converter With High Voltage Gain and Flexibility in Selection of Duty Cycles. IEEE Access 2020, 8, 134716–134727. [Google Scholar] [CrossRef]

- Abdel-Rahim, O.; Funato, H.; Haruna, J. A comprehensive study of three high-gain DC-DC topologies based on Cockcroft-Walton voltage multiplier for reduced power P.V. applications. IEEJ Trans. Electr. Electron. Eng. 2018, 13, 642–651. [Google Scholar] [CrossRef]

- Mohammadzadeh Shahir, F.; Babaei, E. A new structure for nonisolated boost dc-dc converter based on voltage-lift technique. In Proceedings of the 2017 8th Power Electronics, Drive Systems Technologies Conference (PEDSTC), Mashhad, Iran, 14–16 February 2017; pp. 25–30. [Google Scholar]

- Alzahrani, A.; Ferdowsi, M.; Shamsi, P. A Family of Scalable Non-Isolated Interleaved DC-DC Boost Converters With Voltage Multiplier Cells. IEEE Access 2019, 7, 11707–11721. [Google Scholar] [CrossRef]

- Meraj, M.; Bhaskar, M.S.; Iqbal, A.; Al-Emadi, N.; Rahman, S. Interleaved Multilevel Boost Converter With Minimal Voltage Multiplier Components for High-Voltage Step-Up Applications. IEEE Trans. Power Electron. 2020, 35, 12816–12833. [Google Scholar] [CrossRef]

- Pan, C.-T.; Chuang, C.-F.; Chu, C.-C. A Novel Transformer-less Adaptable Voltage Quadrupler DC Converter with Low Switch Voltage Stress. IEEE Trans. Power Electron. 2014, 29, 4787–4796. [Google Scholar] [CrossRef]

- Padmavathi, P.; Natarajan, S. Single switch quasi Z-source based high voltage gain DC-DC converter. Int. Trans. Electr. Energy Syst. 2020, 30, e12399. [Google Scholar] [CrossRef]

- Abbasi Aghdam Meinagh, F.; Yuan, J.; Yang, Y. Analysis and design of a high voltage-gain quasi-Z-source D.C.–D.C. converter. IET Power Electron. 2020, 13, 1837–1847. [Google Scholar] [CrossRef]

- Martinez, W.; Cortes, C.; Yamamoto, M.; Imaoka, J. Effect of inductor parasitic resistances on the voltage gain of high step-up D.C.–D.C. converters for electric vehicle applications. IET Power Electron. 2018, 11, 1628–1639. [Google Scholar] [CrossRef]

- Banaei, M.R.; Bonab, H.A.F. High-efficiency transformerless buck–boost D.C.–D.C. converter. Int. J. Circuit Theory Appl. 2017, 45, 1129–1150. [Google Scholar] [CrossRef]

- Lakshmi, M.; Hemamalini, S. Nonisolated High Gain DC–D.C. Converter for D.C. Microgrids. IEEE Trans. Ind. Electron. 2018, 65, 1205–1212. [Google Scholar] [CrossRef]

- Yang, P.; Xu, J.; Zhou, G.; Zhang, S. A new quadratic boost converter with high voltage step-up ratio and reduced voltage stress. In Proceedings of the 7th International Power Electronics and Motion Control Conference, Harbin, China, 2–5 June 2012; Volume 2, pp. 1164–1168. [Google Scholar]

- Jalilzadeh, T.; Rostami, N.; Babaei, E.; Maalandish, M. Nonisolated Topology for High Step-Up DC-DC Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2018. [Google Scholar] [CrossRef]

- Hu, D.; Yin, A.; Ghaderi, D. A transformer-less single-switch boost converter with high-voltage gain and mitigated-voltage stress applicable for photovoltaic utilizations. Int. Trans. Electr. Energy Syst. 2020, 30, e12569. [Google Scholar] [CrossRef]

- Shahir, F.M.; Babaei, E.; Farsadi, M. Voltage-Lift Technique Based Nonisolated Boost DC–D.C. Converter: Analysis and Design. IEEE Trans. Power Electron. 2018, 33, 5917–5926. [Google Scholar] [CrossRef]

- Park, H.; Kim, S. Single Inductor Multiple Output Auto-Buck-Boost DC–D.C. Converter with Error-Driven Randomized Control. Electronics 2020, 9, 1335. [Google Scholar] [CrossRef]

- Shi, F.; Song, D. A Novel High-Efficiency Double-Input Bidirectional DC/DC Converter for Battery Cell-Voltage Equalizer with Flyback Transformer. Electronics 2019, 8, 1426. [Google Scholar] [CrossRef]

- Ahmad, A.; Anas, M.; Sarwar, A.; Zaid, M.; Tariq, M.; Ahmad, J.; Beig, A.R. Realization of a Generalized Switched-Capacitor Multilevel Inverter Topology with Less Switch Requirement. Energies 2020, 13, 1556. [Google Scholar] [CrossRef]

- Ahmad, J.; Zaid, M.; Sarwar, A.; Tariq, M.; Sarwer, Z. A New Transformerless Quadratic Boost Converter with High Voltage Gain. Smart Sci. 2020, 8, 163–183. [Google Scholar] [CrossRef]

- Bellar, M.D.; Watanabe, E.H.; Mesquita, A.C. Analysis of the dynamic and steady-state performance of Cockcroft-Walton cascade rectifiers. IEEE Trans. Power Electron. 1992, 7, 526–534. [Google Scholar] [CrossRef]

- Ballo, A.; Bottaro, M.; Grasso, A.D.; Palumbo, G. Regulated Charge Pumps: A Comparative Study by Means of Verilog-AMS. Electronics 2020, 9, 998. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.; Palumbo, G. A Review of Charge Pump Topologies for the Power Management of IoT Nodes. Electronics 2019, 8, 480. [Google Scholar] [CrossRef]

- Liu, M. Demystifying Switched Capacitor Circuits; Elsevier: Amsterdam, The Netherlands, 2006. [Google Scholar]

| Component | Voltage Stress (Volt) | Average Current during Their Conduction (Amp) | Average Current for the Complete Cycle (Amp) | RMS Current (Amp) |

|---|---|---|---|---|

| S1 | ||||

| S2 | ||||

| D1 | ||||

| D2 | ||||

| D3 | ||||

| D4 |

| Topology | NL (Inductors) | NC (Capacitors) | NSW (Switches) | ND (Diodes) | M | S |

|---|---|---|---|---|---|---|

| [9] | 2 | 4 | 1 | 4 | ||

| [10] | 4 | 1 | 2 | 7 | ||

| [11] | 2 | 3 | 2 | 3 | ||

| [17] | 1+1 coupled inductor | 3 | 1 | 5 | ||

| [CQBC] | 2 | 2 | 1 | 3 | ||

| [24] | 2 | 4 | 2 | 4 | ||

| [33] | 2 | 3 | 1 | 3 | ||

| Proposed | 2 | 4 | 2 | 4 |

| Elements | Specification |

|---|---|

| Input Voltage (Vin) | 24 V |

| Maximum Output Power | 150 W |

| Switching Frequency | 50 kHz |

| Load Resistance | R = 250 Ω, Electronic load simulator |

| Inductors | L1 = L2 = 330 µH, ESR = 0.3 Ω |

| Capacitors | C1 = 47 µF/100 V ESR = 0.26 Ω, C2 = C3 = 33 µF/200 V ESR = 0.3 Ω & C4 = 220 µF/50 V ESR = 0.20 Ω |

| Power MOSFET (S1 & S2) | SPW52N50C3, RDSon = 70 mΩ |

| Diodes (D1, D2, D3 & D4) | SF8L60USM, Vd = 0.6 V |

| Gate Drivers IC | TLP250H |

| Gate Driver Voltage Regulator IC | MCWI03-48S15 |

| Microcontroller | STM32 Nucleo H743ZI2 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ahmad, J.; Lin, C.-H.; Zaid, M.; Sarwar, A.; Ahmad, S.; Sharaf, M.; Zaindin, M.; Firdausi, M. A New High Voltage Gain DC to DC Converter with Low Voltage Stress for Energy Storage System Application. Electronics 2020, 9, 2067. https://doi.org/10.3390/electronics9122067

Ahmad J, Lin C-H, Zaid M, Sarwar A, Ahmad S, Sharaf M, Zaindin M, Firdausi M. A New High Voltage Gain DC to DC Converter with Low Voltage Stress for Energy Storage System Application. Electronics. 2020; 9(12):2067. https://doi.org/10.3390/electronics9122067

Chicago/Turabian StyleAhmad, Javed, Chang-Hua Lin, Mohammad Zaid, Adil Sarwar, Shafiq Ahmad, Mohamed Sharaf, Mazen Zaindin, and Muhammad Firdausi. 2020. "A New High Voltage Gain DC to DC Converter with Low Voltage Stress for Energy Storage System Application" Electronics 9, no. 12: 2067. https://doi.org/10.3390/electronics9122067

APA StyleAhmad, J., Lin, C.-H., Zaid, M., Sarwar, A., Ahmad, S., Sharaf, M., Zaindin, M., & Firdausi, M. (2020). A New High Voltage Gain DC to DC Converter with Low Voltage Stress for Energy Storage System Application. Electronics, 9(12), 2067. https://doi.org/10.3390/electronics9122067