Instability in In0.7Ga0.3As Quantum-Well MOSFETs with Single-Layer Al2O3 and Bi-Layer Al2O3/HfO2 Gate Stacks Caused by Charge Trapping under Positive Bias Temperature (PBT) Stress

Abstract

1. Introduction

2. Experimental Details

3. Results and Discussion

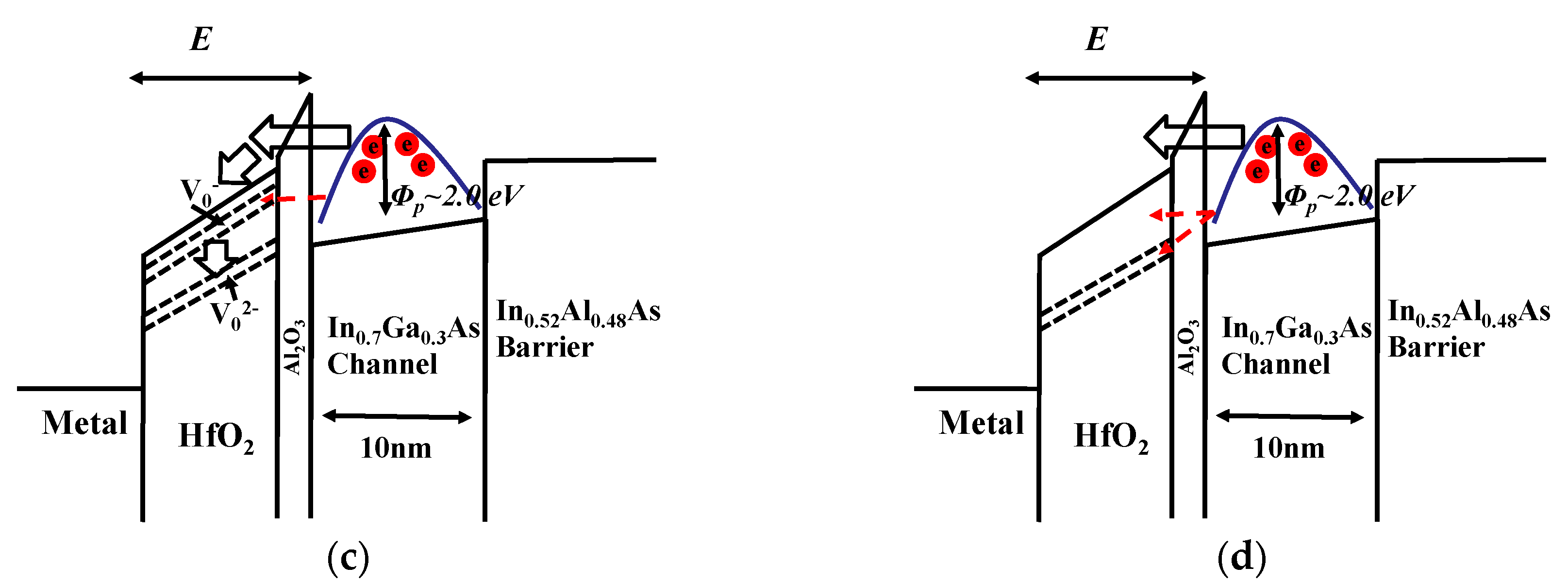

3.1. Distribution of the Electrical Field Across Gate Stacks on the Applied Stress Voltage

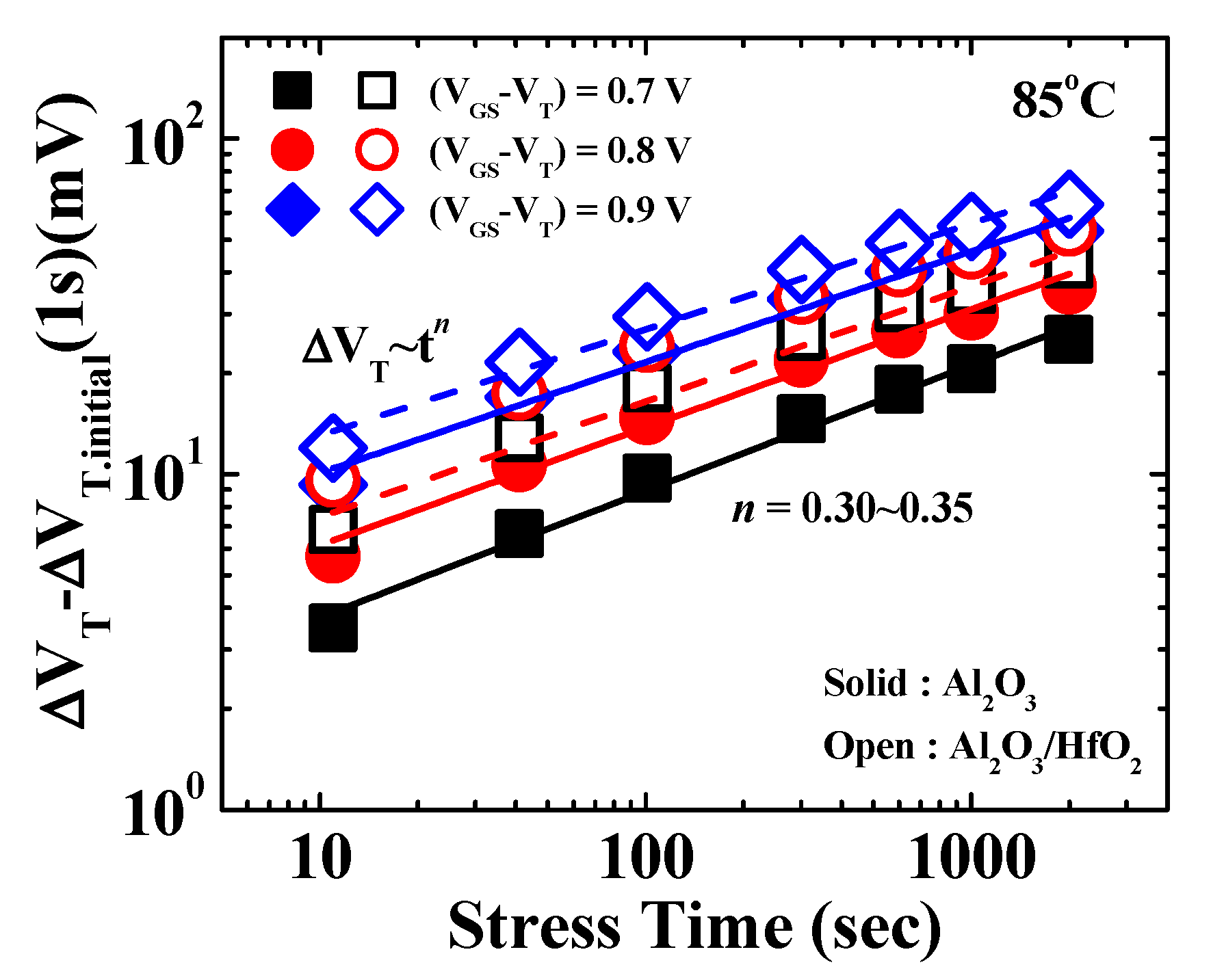

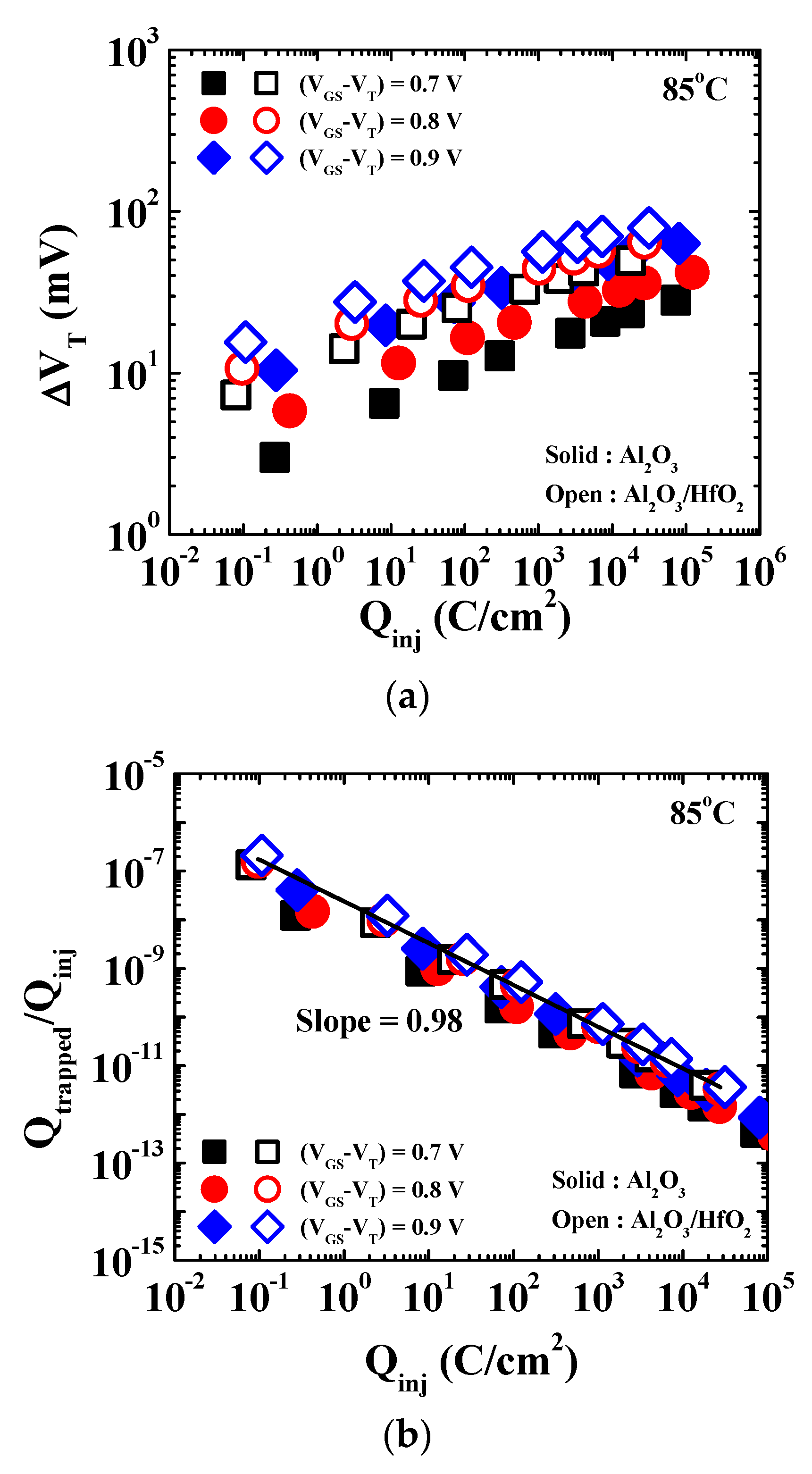

3.2. Impact of Charge Trapping in Defect Sites under Positive Bias Temperature (PBT) Stress Condition

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Del Alamo, J.A. Nanometre-scale electronics with III–V compound semiconductors. Nature 2011, 479, 317–323. [Google Scholar] [CrossRef] [PubMed]

- Waldron, N.; Merckling, C.; Teugels, L.; Ong, P.; Ansar, S.; Ibrahim, U.; Sebaai, F.; Pourghaderi, A.; Barla, K.; Collaert, N.; et al. InGaAs Gate-All-Around Nanowire Devices on 300 mm Si Substrates. IEEE Electron Device Lett. 2014, 35, 1097–1099. [Google Scholar] [CrossRef]

- Kim, T.-W.; Koh, D.-H.; Shin, C.-S.; Park, W.-K.; Orzali, T.; Hobbs, C.; Maszara, W.P.; Kim, D.-H. Lg = 80 -nm Trigate Quantum-Well In 0.53 Ga 0.47 As Metal–Oxide–Semiconductor Field-Effect Transistors With Al2O3/HfO2 Gate-Stack. IEEE Electron Device Lett. 2015, 36, 223–225. [Google Scholar] [CrossRef]

- Kim, D.; Alamo, J.A.; Antoniadis, D.A.; Brar, B. Extraction of Virtual-Source Injection Velocity in sub-100 nm III-V HFETs. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; Volume 3, pp. 861–864. [Google Scholar]

- Kim, T.-W.; Kim, D.-H.; Koh, D.-H.; Hill, R.J.W.; Lee, R.T.P.; Wong, M.H.; Cunningham, T.; del Alamo, J.A.; Banerjee, S.K.; Oktyabrsky, S.; et al. ETB-QW InAs MOSFET with scaled body for improved electrostatics. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 32.3.1–32.3.4. [Google Scholar]

- Taoka, N.; Yokoyama, M.; Kim, S.H.; Suzuki, R.; Iida, R.; Lee, S.; Hoshii, T.; Jevasuwan, W.; Maeda, T.; Yasuda, T.; et al. Impact of Fermi Level Pinning inside Conduction Band on Electron Mobility of In x Ga 1-x As MOSFETs and Mobility Enhancement by Pinning Modulation. In Proceedings of the International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 27.2.1–27.2.4. [Google Scholar]

- Engel-Herbert, R.; Hwang, Y.; Stemmer, S. Comparison of methods to quantify interface trap densities at dielectric/III-V semiconductor interfaces. J. Appl. Phys. 2010, 108, 124101. [Google Scholar] [CrossRef]

- Yum, J.H.; Akyol, T.; Ferrer, D.A.; Lee, J.C.; Banerjee, S.K.; Lei, M.; Downer, M.; Hudnall, T.W.; Bielawski, C.W.; Bersuker, G. Comparison of the self-cleaning effects and electrical characteristics of BeO and Al2O3 deposited as an interface passivation layer on GaAs MOS devices. J. Vac. Sci. Technol. A Vac. Surf. Films 2013, 29, 061501. [Google Scholar] [CrossRef]

- Yuan, Y.; Wang, L.; Yu, B.; Shin, B.; Ahn, J.; McIntyre, P.C.; Asbeck, P.M.; Rodwell, M.J.W.; Taur, Y. A Distributed Model for Border Traps in Al2O3—InGaAs MOS Devices. IEEE Electron Device Lett. 2011, 32, 485–487. [Google Scholar] [CrossRef]

- Goel, N.; Heh, D.; Koveshnikov, S.; Ok, I.; Oktyabrsky, S.; Tokranov, V.; Kambhampatic, R.; Yakimov, M.; Sun, Y.; Pianetta, P.; et al. Addressing The Gate Stack Challenge For High Mobility InxGa1-xAs Channels For NFETs. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar]

- Bersuker, G.; Park, C.S.; Barnett, J.; Lysaght, P.S.; Kirsch, P.D.; Young, C.D.; Choi, R.; Forank, B.H.L.; Benthem, V.; Lenahan, S.J.P.M.; et al. The effect of interfacial layer properties on the performance of Hf-based gate stack devices the effect of interfacial layer properties on the performance of Hf-based gate stack devices. J. Appl. Phys. 2006, 100, 094108. [Google Scholar] [CrossRef]

- Chowdhury, N.A.; Bersuker, G. Breakdown characteristics of nFETs in inversion with metal/HfO2 gate stacks. Microelectron. Eng. 2008, 85, 27–35. [Google Scholar] [CrossRef]

- Heh, D.; Young, C.D.; Choi, R.; Bersuker, G. Extraction of the Threshold-Voltage Shift by the Single-Pulse Technique. IEEE Electron Device Lett. 2007, 28, 734–736. [Google Scholar] [CrossRef]

- Heh, D.; Young, C.D.; Brown, G.A.; Hung, P.Y.; Diebold, A.; Bersuker, G.; Vogel, E.M.; Bernstein, J.B.; Vogel, E.M.; Bernstein, J.B. Spatial distributions of trapping centers in HfO2/SiO2 gate stacks. Appl. Phys. Lett. 2011, 88, 152907. [Google Scholar] [CrossRef]

- Young, C.D.; Zeitzoff, P.; Brown, G.A.; Member, L.S.; Bersuker, G.; Lee, B.H.; Hauser, J.R.; Fellow, S.; Hauser, J.R. Intrinsic mobility evaluation of high-/spl kappa/gate dielectric transistors using pulsed Id-Vg. IEEE Electron Device Lett. 2005, 26, 586–589. [Google Scholar] [CrossRef]

- Young, C.D.; Heh, D.; Neugroschel, A.; Choi, R. Electrical characterization and analysis techniques for the high-κ era. Microelectron. Reliab. 2007, 47, 479–488. [Google Scholar] [CrossRef]

- Choi, E.A.; Chang, K.J. Charge-transition levels of oxygen vacancy as the origin of device instability in HfO2 gate stacks through quasiparticle energy calculations. Appl. Phys. Lett. 2009, 94, 122901. [Google Scholar] [CrossRef]

- Wu, W.C.; Lai, C.-S.; Wang, T.-M.; Wang, J.-C.; Hsu, C.W.; Ma, M.W.; Lo, W.-C.; Chao, T.S. Carrier Transportation Mechanism of the TaN/HfO2/IL/Si Structure with Silicon Surface Fluorin Implantation. IEEE Trans. Electron Devices 2008, 55, 1639–1646. [Google Scholar] [CrossRef]

- Cho, M.; Lee, J.; Aoulaiche, M.; Kaczer, B.; Roussel, P.; Kauerauf, T.; Degraeve, R.; Franco, J.; Ragnarsson, L.-åke; Groeseneken, G. Insight Into N/PBTI Mechanisms in Sub-1-nm-EOT Devices. IEEE Trans. Electron Devices 2012, 59, 2042–2048. [Google Scholar] [CrossRef]

- Kreber, A.; Cartier, E.; Pantisano, L.; Rosmeulen, M.; Degraeve, R.; Kauerauf, T.; Groeseneken, G.; Maes, H.E.; Schwalke, U. Characterization Of The Vt-Instability In Sio2/Hfo2 Gate Dielectrics. Proc. IEEE Int. Reliab. Phys. Symp. 2003, 41–45. [Google Scholar] [CrossRef]

- Park, H.; Rahman, M.S.; Chang, M.; Lee, B.H.; Choi, R.; Young, C.D. Improved Interface Quality and Charge-Trapping Characteristics of MOSFETs with High- Gate Dielectric. IEEE Electron Device Lett. 2005, 26, 725–727. [Google Scholar] [CrossRef]

- Bersuker, G.; Sim, J.H.; Park, C.S.; Young, C.D.; Nadkarni, S.V.; Choi, R.; Lee, B.H. Mechanism of Electron Trapping and Characteristics of Traps in HfO2 Gate Stacks. IEEE Trans. Device Mater. Reliab. 2007, 7, 138–145. [Google Scholar] [CrossRef]

- Afanas’ev, V.; Stesmans, A.; Chen, F.; Shi, X.; Campbell, S.A. Internal photoemission of electrons and holes from (100) Si into HfO2. Appl. Phys. Lett 2002, 81, 1053–1055. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kwon, H.-M.; Kim, D.-H.; Kim, T.-W. Instability in In0.7Ga0.3As Quantum-Well MOSFETs with Single-Layer Al2O3 and Bi-Layer Al2O3/HfO2 Gate Stacks Caused by Charge Trapping under Positive Bias Temperature (PBT) Stress. Electronics 2020, 9, 2039. https://doi.org/10.3390/electronics9122039

Kwon H-M, Kim D-H, Kim T-W. Instability in In0.7Ga0.3As Quantum-Well MOSFETs with Single-Layer Al2O3 and Bi-Layer Al2O3/HfO2 Gate Stacks Caused by Charge Trapping under Positive Bias Temperature (PBT) Stress. Electronics. 2020; 9(12):2039. https://doi.org/10.3390/electronics9122039

Chicago/Turabian StyleKwon, Hyuk-Min, Dae-Hyun Kim, and Tae-Woo Kim. 2020. "Instability in In0.7Ga0.3As Quantum-Well MOSFETs with Single-Layer Al2O3 and Bi-Layer Al2O3/HfO2 Gate Stacks Caused by Charge Trapping under Positive Bias Temperature (PBT) Stress" Electronics 9, no. 12: 2039. https://doi.org/10.3390/electronics9122039

APA StyleKwon, H.-M., Kim, D.-H., & Kim, T.-W. (2020). Instability in In0.7Ga0.3As Quantum-Well MOSFETs with Single-Layer Al2O3 and Bi-Layer Al2O3/HfO2 Gate Stacks Caused by Charge Trapping under Positive Bias Temperature (PBT) Stress. Electronics, 9(12), 2039. https://doi.org/10.3390/electronics9122039