Evaluation of Quadrature Signal Generation Methods with Reduced Computational Resources for Grid Synchronization of Single-Phase Power Converters through Phase-Locked Loops

Abstract

1. Introduction

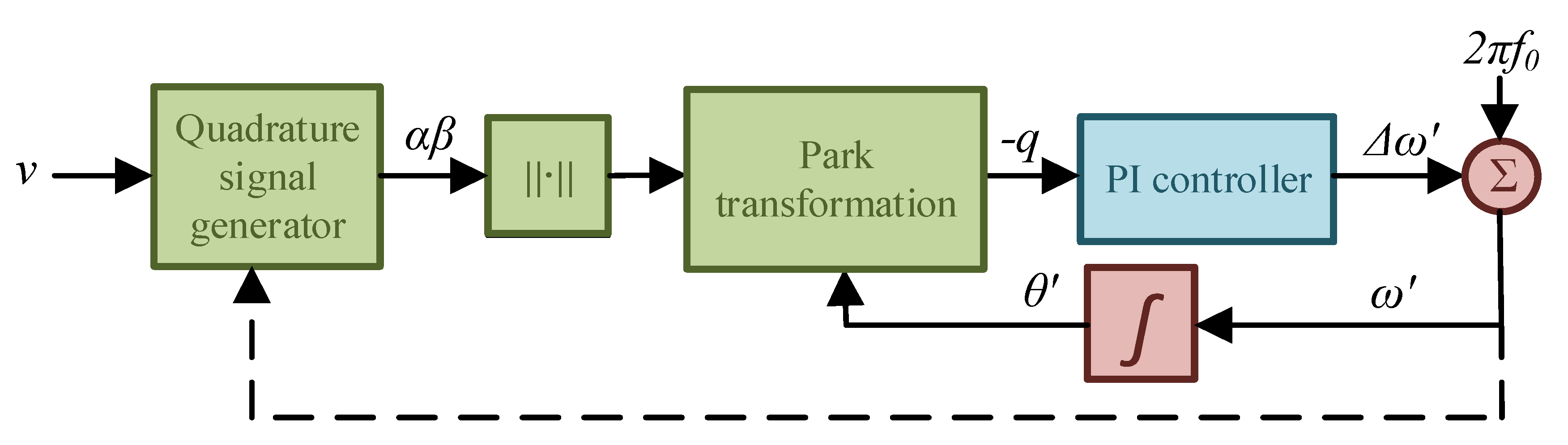

2. Principle of Operation and Types of PLLs

3. PLLs Based on Park Transformation

3.1. Transport Delay PLL

3.2. PLL Based on Inverse Park Transformation

3.3. PLL Based on Synthesis Circuit

3.4. PLL Based on Hilbert Transform

3.5. PLL Based on Signal Delay Compensation

3.6. Derivative PLL

3.7. PLL Based on Recursive Discrete Fourier Transform

3.8. PLL Based on Kalman Filtering

3.9. PLL Based on Second-Order Generalized Integrator

3.10. PLL Based on First-Order All-Pass Filters

3.11. PLL Based on Two-Sample

3.12. Evaluation

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| APF PLL | PLL based on first-order all-pass filters |

| CORDIC | Coordinate Rotation Digital Computer |

| D | Derivative |

| DC | Direct current |

| DCO | Digitally Controlled Oscillator |

| DSO | Distribution system operators |

| DSC | Delay Signal Compensation |

| DSP | Digital signal processor |

| D PLL | PLL based on derivative |

| EPLL | Enhanced Phase-Locked Loop |

| FIR | Finite Impulse Response |

| FPGA | Field Programmable Gate Array |

| FSM | Finite state machine |

| HT | Hilbert transform |

| IIR | Infinite Impulse Response |

| IP | Intellectual Property |

| IPT PLL | Phase-Locked Loop based on the inverse of Park transformation |

| KF | Kalman filter |

| LF | Loop filter |

| LHS | Latin Hypercube Sampling |

| LKF | Limiting Kalman filter |

| LUT | Look Up Tables |

| LV | Low-voltage |

| MC | Monte Carlo |

| MHDC PLL | Phase-locked loop based on multiharmonic decoupling cell |

| MSOGI | Multisecond-order generalized integrator |

| NTD | Nonfrequency-dependent TD |

| PD | Phase detector |

| Probability density function | |

| PI | Proportional–integral |

| PLL | Phase-locked loop |

| pPLL | Power-based phase-locked loop |

| SC PLL | Synthesis circuit phase-locked loop |

| SOGI PLL | PLL based on the second-order generalized integrator |

| QSG | Quadrature signal generation |

| QSG PLL | PLLs based on the quadrature signal generation |

| RDFT PLL | PLL based on recursive discrete Fourier transform |

| SRF PLL | Synchronous reference frame phase-locked loop |

| TD PLL | Transport delay phase-locked loop |

| VCO | Voltage controlled oscillator |

| 2S-QSG | Quadrature signal generation based on two samples |

References

- Teodorescu, R.; Liserre, M.; Rodriguez, P. Grid Converters for Photovoltaic and Wind Power Systems; John Wiley & Sons: Hoboken, NJ, USA, 2011; Volume 29. [Google Scholar]

- Peña Asensio, A.; Gonzalez-Longatt, F.; Arnaltes, S.; Rodríguez-Amenedo, J.L. Analysis of the Converter Synchronizing Method for the Contribution of Battery Energy Storage Systems to Inertia Emulation. Energies 2020, 13, 1478. [Google Scholar] [CrossRef]

- Zhu, R.; Liserre, M. Control of Smart Transformer Under Single-Phase to Ground Fault Condition. IEEE Trans. Power Electron. 2020, 35, 2034–2043. [Google Scholar] [CrossRef]

- Liu, S.-M.; Tu, C.-H.; Lin, C.-L.; Liu, V.-T. Field-Oriented Driving/Braking Control for Electric Vehicles. Electronics 2020, 9, 1484. [Google Scholar] [CrossRef]

- Ku, B.; Liu, J. Converter-Switching Surges: Railroad Vehicle Power Converter Impact Studies. IEEE Veh. Technol. Mag. 2012, 7, 57–66. [Google Scholar] [CrossRef]

- Hazell, P.; Mather, P.; Longstaff, A.; Fletcher, S. Digital System Performance Enhancement of a Tent Map-Based ADC for Monitoring Photovoltaic Systems. Electronics 2020, 9, 1554. [Google Scholar] [CrossRef]

- Cho, S.-M.; Kim, J.-C.; Yun, S.-Y. Optimum State-of-Charge Operating Range for Frequency Regulation of Energy Storage Systems Using a Master–Slave Parallel Genetic Algorithm. Electronics 2020, 9, 1298. [Google Scholar] [CrossRef]

- Ashabani, M.; Freijedo, F.D.; Golestan, S.; Guerrero, J.M. Inducverters: PLL-Less Converters with Auto-Synchronization and Emulated Inertia Capability. IEEE Trans. Smart Grid 2016, 7, 1660–1674. [Google Scholar] [CrossRef]

- Yu, B. An Improved Frequency Measurement Method from the Digital PLL Structure for Single-Phase Grid-Connected PV Applications. Electronics 2018, 7, 150. [Google Scholar] [CrossRef]

- Zeb, K.; Islam, S.U.; Din, W.U.; Khan, I.; Ishfaq, M.; Busarello, T.D.C.; Ahmad, I.; Kim, H.J. Design of Fuzzy-PI and Fuzzy-Sliding Mode Controllers for Single-Phase Two-Stages Grid-Connected Transformerless Photovoltaic Inverter. Electronics 2019, 8, 520. [Google Scholar] [CrossRef]

- Lo, Y.; Lee, T.; Wu, K. Grid-Connected Photovoltaic System with Power Factor Correction. IEEE Trans. Ind. Electron. 2008, 55, 2224–2227. [Google Scholar] [CrossRef]

- Choudhury, A.R.; Pati, S.; Choudhury, A.; Mohanty, K.B. Control of voltage & frequency of a hybrid microgrid using a FLC based bidirectional converter equipped with BESS. In Proceedings of the 2018 Technologies for Smart-City Energy Security and Power (ICSESP), Bhubaneswar, India, 28–30 March 2018; pp. 1–6. [Google Scholar]

- Faisal, M.; Hannan, M.A.; Ker, P.J.; Rahman, M.S.B.A.; Mollik, M.S.; Mansur, M.B. Review of Solid State Transfer Switch on Requirements, Standards, Topologies, Control, and Switching Mechanisms: Issues and Challenges. Electronics 2020, 9, 1396. [Google Scholar] [CrossRef]

- Best, R.E. Simulation and Applications. In Phase-Locked Loops. Design, 4th ed.; McGraw Hill Professional: New York, NY, USA, 1999. [Google Scholar]

- Gardner, F.M. Phaselock Techniques; John Wiley and Sons Ltd: Hoboken, NJ, USA, 2005. [Google Scholar]

- Golestan, S. Modeling, Analyzing, and Designing Advanced Synchronization Techniques for Power Converters; Aalborg University: Aalborg, Denmark, 2018. [Google Scholar]

- Karimi-Ghartema, M. Enhanced Phase-Locked Loop Structures for Power and Energy Applications, 1st ed.; IEEE Press Series on Microelec: Hoboken, NJ, USA, 2014; ISBN 978-1-118-79502-6. [Google Scholar]

- Golestan, S.; Monfared, M.; Freijedo, F.D.; Guerrero, J.M. Advantages and Challenges of a Type-3 PLL. IEEE Trans. Power Electron. 2013, 28, 4985–4997. [Google Scholar] [CrossRef]

- Liu, H.; Wu, Z. Demodulation of Angular Position and Velocity from Resolver Signals via Chebyshev Filter-Based Type III Phase Locked Loop. Electronics 2018, 7, 354. [Google Scholar] [CrossRef]

- Yang, Y.; Zhou, K.; Blaabjerg, F. Exploitation of digital filters to advance the single-phase T/4 delay PLL system. In Proceedings of the 2016 IEEE 2nd Annual Southern Power Electronics Conference (SPEC), Auckland, New Zealand, 5–8 December 2016; pp. 1–6. [Google Scholar]

- Gonzalez-Espin, F.; Figueres, E.; Garcera, G. An Adaptive Synchronous-Reference-Frame Phase-Locked Loop for Power Quality Improvement in a Polluted Utility Grid. IEEE Trans. Ind. Electron. 2012, 59, 2718–2731. [Google Scholar] [CrossRef]

- Sumathi, P.; Janakiraman, P.A. Phase locking scheme based on look-up-table-assisted sliding discrete fourier transform for low-frequency power and acoustic signals. IET Circuits Devices Syst. 2011, 5, 494–504. [Google Scholar] [CrossRef]

- Meyer-Baese, U. Signals and Communication Technology. In Digital Signal Processing with Field Programmable Gate Arrays, 3rd ed.; Springer: Berlin/Heidelberg, Germany, 2007; ISBN 978-3-540-72613-5. [Google Scholar]

- Panda, S.R.; Babu, B.C. Phase estimation for grid synchronization using CORDIC algorithm with SRF-PLL. In Proceedings of the 2012 IEEE Students’ Conference on Electrical, Electronics and Computer Science, Bhopal, India, 1–2 March 2012; pp. 1–4. [Google Scholar]

- Huimei, Y.; Hao, S.; Yu, S. Optimized Design and Implementation of Three-Phase PLL Based on FPGA. In Proceedings of the 2009 International Conference on Computer Engineering and Technology, Singapore, 22–24 January 2009; Volume 1, pp. 129–133. [Google Scholar]

- Freijedo, F.D.; Doval-Gandoy, J.; Lopez, O.; Cabaleiro, J. Robust phase locked loops optimized for DSP implementation in power quality applications. In Proceedings of the 2008 34th Annual Conference of IEEE Industrial Electronics, Orlando, FL, USA, 10–13 November 2008; pp. 3052–3057. [Google Scholar]

- Lamo, P.; Pigazo, A.; Ruiz, G.A.; Azcondo, F.J.; López, F. An Optimized Implementation of a Two-Sample Phase Locked Loop with Frequency Feedback for Single-Phase Sensorless Bridgeless PFC. In Proceedings of the 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), Padua, Italy, 25–28 June 2018; pp. 1–6. [Google Scholar]

- Masoud, K.G. Linear and Pseudolinear Enhanced Phased-Locked Loop (EPLL) Structures. IEEE Trans. Ind. Electron. 2014, 61, 1464–1474. [Google Scholar]

- Ghartemani, M.K.; Khajehoddin, S.A.; Jain, P.K.; Bakhshai, A. Problems of Startup and Phase Jumps in PLL Systems. IEEE Trans. Power Electron. 2012, 27, 1830–1838. [Google Scholar] [CrossRef]

- Khadkikar, V.; Chandra, A.; Singh, B.N. Generalised single-phase p-q theory for active power filtering: Simulation and DSP-based experimental investigation. IET Power Electron. 2009, 2, 67–78. [Google Scholar] [CrossRef]

- Correa, J.M.; Farret, F.A.; Simoes, M.G. Application of a Modified Single-Phase P-Q Theory in the Control of Shunt and Series Active Filters in a 400 Hz Microgrid. In Proceedings of the 2005 IEEE 36th Power Electronics Specialists Conference, Recife, Brazil, 16 June 2005; pp. 2585–2591. [Google Scholar]

- Yang, Y.; Blaabjerg, F. Synchronization in single-phase grid-connected photovoltaic systems under grid faults. In Proceedings of the 2012 3rd IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Aalborg, Denmark, 25–28 June 2012; pp. 476–482. [Google Scholar]

- Liu, J.; Yang, J.; Wang, Z. A new approach for single-phase harmonic current detecting and its application in a hybrid active power filter. In Proceedings of the 25th Annual Conference of the IEEE Industrial Electronics Society, 1999. IECON ’99 Proceedings, San Jose, CA, USA, 29 November–3 December 1999; Volume 2, pp. 849–854. [Google Scholar]

- Haque, M.T. Single-phase pq theory for active filters. In Proceedings of the TENCON ’02. Proceedings, 2002 IEEE Region 10 Conference on Computers, Communications, Control and Power Engineering, Beijing, China, 28–31 October 2002; Volume 3, pp. 1941–1944. [Google Scholar]

- Gupta, A.; Porippireddi, A.; Srinivasa, V.U.; Sharma, A.; Kadam, M. Comparative study of single phase PLL algorithms for grid synchronization applications. IJECT 2012, 3, 237–245. [Google Scholar]

- Hadjidemetriou, L.; Yang, Y.; Kyriakides, E.; Blaabjerg, F. A Synchronization Scheme for Single-Phase Grid-Tied Inverters under Harmonic Distortion and Grid Disturbances. IEEE Trans. Power Electron. 2016. [Google Scholar] [CrossRef]

- Golestan, S.; Guerrero, J.M.; Vidal, A.; Yepes, A.G.; Doval-Gandoy, J.; Freijedo, F.D. Small-Signal Modeling, Stability Analysis and Design Optimization of Single-Phase Delay-Based PLLs. IEEE Trans. Power Electron. 2016, 31, 3517–3527. [Google Scholar] [CrossRef]

- Golestan, S.; Guerrero, J.; Abusorrah, A.; Al-Hindawi, M.; Al-Turki, Y. An Adaptive Quadrature Signal Generation-Based Single-Phase Phase-Locked Loop for Grid-Connected Applications. IEEE Trans. Ind. Electron. 2016. [Google Scholar] [CrossRef]

- Choi, J.W.; Kim, Y.K.; Kim, H.G. Digital PLL control for single-phase photovoltaic system. IEE Proc. Electr. Power Appl. 2006, 153, 40–46. [Google Scholar] [CrossRef]

- Nicastri, A.; Nagliero, A. Comparison and evaluation of the PLL techniques for the design of the grid-connected inverter systems. In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 4–7 July 2010; pp. 3865–3870. [Google Scholar]

- Silva, S.M.; Lopes, B.M.; Filho, B.J.C.; Campana, R.P.; Bosventura, W.C. Performance evaluation of PLL algorithms for single-phase grid-connected systems. In Proceedings of the Conference Record of the 2004 IEEE Industry Applications Conference, 39th IAS Annual Meeting, Seattle, WA, USA, 3–7 October 2004; Volume 4, pp. 2259–2263. [Google Scholar]

- Han, Y.; Luo, M.; Zhao, X.; Guerrero, J.M.; Xu, L. Comparative Performance Evaluation of Orthogonal-Signal-Generators-Based Single-Phase PLL Algorithms—A Survey. IEEE Trans. Power Electron. 2016, 31, 3932–3944. [Google Scholar] [CrossRef]

- Filho, R.M.S.; Seixas, P.F.; Cortizo, P.C.; Torres, L.A.B.; Souza, A.F. Comparison of Three Single-Phase PLL Algorithms for UPS Applications. IEEE Trans. Ind. Electron. 2008, 55, 2923–2932. [Google Scholar] [CrossRef]

- Hadjidemetriou, L.; Kyriakides, E.; Yang, Y.; Blaabjerg, F. Power quality improvement of single-phase photovoltaic systems through a robust synchronization method. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 2625–2632. [Google Scholar]

- Hadjidemetriou, L.; Kyriakides, E.; Yang, Y.; Blaabjerg, F. A Synchronization Method for Single-Phase Grid-Tied Inverters. IEEE Trans. Power Electron. 2016, 31, 2139–2149. [Google Scholar] [CrossRef]

- Fang, X.; Wang, Y.; Li, M.; Liu, J. A novel frequency-adaptive PLL for single-phase grid-connected converters. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 414–419. [Google Scholar]

- Karimi-Ghartemani, M. A Unifying Approach to Single-Phase Synchronous Reference Frame PLLs. IEEE Trans. Power Electron. 2013, 28, 4550–4556. [Google Scholar] [CrossRef]

- Kumm, M.; Sanjari, M.S. Digital hilbert transformers for FPGA-based phase-locked loops. In Proceedings of the 2008 International Conference on Field Programmable Logic and Applications, Heidelberg, Germany, 8–10 September 2008; pp. 251–256. [Google Scholar]

- Komodromos, M.Z.; Russell, S.F.; Tang, P.T.P. Design of FIR Hilbert transformers and differentiators in the complex domain. IEEE Trans. Circuits Syst. Fundam. Theory Appl. 1998, 45, 64–67. [Google Scholar] [CrossRef]

- Giampaolo, B.; Barater, D.; Tarisciotti, L.; Zanchetta, P. High-dynamic single-phase Hilbert-based PLL for improved phase-jump ride-through in grid-connected inverters. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 4932–4939. [Google Scholar]

- Ingle, V.K.; Proakis, J.G. Digital Signal Processing Using MATLAB, 3rd ed.; CL Engineering: Stamford, CT, USA, 2011; ISBN 978-1-111-42737-5. [Google Scholar]

- Kaiser, J.; Hamming, R. Sharpening the response of a symmetric nonrecursive filter by multiple use of the same filter. In Proceedings of the Acoustics, Speech, and Signal Processing, IEEE International Conference on ICASSP ’77, Hartford, CT, USA, 9–11 May 1977; Volume 2, pp. 82–85. [Google Scholar]

- Golestan, S.; Freijedo, F.D.; Vidal, A.; Yepes, A.G.; Guerrero, J.M.; Doval-Gandoy, J. An Efficient Implementation of Generalized Delayed Signal Cancellation PLL. IEEE Trans. Power Electron. 2016, 31, 1085–1094. [Google Scholar] [CrossRef]

- Galkin, I.; Vorobyov, M. Optimizing of sampling in a low-cost single-phase instantaneous AC-grid synchronization unit with discrete calculation of derivative function. In Proceedings of the IECON 2015—41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015; pp. 004538–004543. [Google Scholar]

- Picardi, C.; Sgrò, D.; Gioffré, G. A simple and low-cost PLL structure for single-phase grid-connected inverters. In Proceedings of the SPEEDAM 2010, Pisa, Italy, 14–16 June 2010; pp. 358–362. [Google Scholar]

- Galkin, I.; Vorobyov, M. Implementation of single-phase grid synchronization module with low-end microcontrollers. In Proceedings of the 2014 55th International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON), Riga, Latvia, 14 October 2014; pp. 84–87. [Google Scholar]

- Subramanian, C.; Kanagaraj, R. Single-Phase Grid Voltage Attributes Tracking for the Control of Grid Power Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 1041–1048. [Google Scholar] [CrossRef]

- Darwish, H.A.; Fikri, M. Practical Considerations for Recursive DFT Implementation in Numerical Relays. IEEE Trans. Power Deliv. 2007, 22, 42–49. [Google Scholar] [CrossRef]

- McGrath, B.P.; Holmes, D.G.; Galloway, J.J.H. Power converter line synchronization using a discrete Fourier transform (DFT) based on a variable sample rate. IEEE Trans. Power Electron. 2005, 20, 877–884. [Google Scholar] [CrossRef]

- Chui, C.K.; Chen, G. Kalman Filtering with Real Time Applications, 4th ed.; Springer: New York, NY, USA, 2009. [Google Scholar]

- Girgis, A.A.; Chang, W.B.; Makram, E.B. A digital recursive measurement scheme for online tracking of power system harmonics. IEEE Trans. Power Deliv. 1991, 6, 1153–1160. [Google Scholar] [CrossRef]

- Brabandere, K.D.; Loix, T.; Engelen, K.; Bolsens, B.; den Keybus, J.V.; Driesen, J.; Belmans, R. Design and Operation of a Phase-Locked Loop with Kalman Estimator-Based Filter for Single-Phase Applications. In Proceedings of the IECON 2006—32nd Annual Conference on IEEE Industrial Electronics, Paris, France, 6–10 November 2006; pp. 525–530. [Google Scholar]

- Rodriguez, P.; Teodorescu, R.; Candela, I.; Timbus, A.V.; Liserre, M.; Blaabjerg, F. New Positive-sequence Voltage Detector for Grid Synchronization of Power Converters under Faulty Grid Conditions. In Proceedings of the 2006 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–7. [Google Scholar]

- Ciobotaru, M.; Teodorescu, R.; Blaabjerg, F. A New Single-Phase PLL Structure Based on Second Order Generalized Integrator. In Proceedings of the 37th IEEE Power Electronics Specialists Conference (PESC ’06), Jeju, Korea, 18–22 June 2006; pp. 1–6. [Google Scholar]

- Golestan, S.; Monfared, M.; Freijedo, F.D.; Guerrero, J.M. Dynamics Assessment of Advanced Single-Phase PLL Structures. IEEE Trans. Ind. Electron. 2013, 60, 2167–2177. [Google Scholar] [CrossRef]

- Monter, A.R. Contributions to Cascade Linear Control Strategies Applied to Grid-Connected Voltage-Source Converters. Ph.D. Thesis, Universidad de Alcalá de Henares, Alcalá de Henares, Spain, 2013. [Google Scholar]

- Ciobotaru, M.; Teodorescu, R.; Agelidis, V.G. Offset rejection for PLL based synchronization in grid-connected converters. In Proceedings of the 2008 Twenty-Third Annual IEEE Applied Power Electronics Conference and Exposition, Austin, TX, USA, 24–28 February 2008; pp. 1611–1617. [Google Scholar]

- Shinnaka, S. A Robust Single-Phase PLL System with Stable and Fast Tracking. IEEE Trans. Ind. Appl. 2008, 44, 624–633. [Google Scholar] [CrossRef]

- Trento, B.; Wang, B.; Sun, K.; Tolbert, L.M. Integration of phase-locked loop based real-time oscillation tracking in grid synchronized systems. In Proceedings of the 2014 IEEE PES General Meeting Conference Exposition, National Harbor, MD, USA, 27–31 July 2014; pp. 1–5. [Google Scholar]

- Karimi-Ghartemani, M.; Khajehoddin, S.A.; Jain, P.K.; Bakhshai, A.; Mojiri, M. Addressing DC Component in PLL and Notch Filter Algorithms. IEEE Trans. Power Electron. 2012, 27, 78–86. [Google Scholar] [CrossRef]

- Fedele, G.; Ferrise, A.; Muraca, P. An adaptive quasi-notch filter for a biased sinusoidal signal estimation. In Proceedings of the 2011 9th IEEE International Conference on Control and Automation (ICCA), Santiago, Chile, 19–21 December 2011; pp. 1060–1065. [Google Scholar]

- Fedele, G.; Ferrise, A. Non Adaptive Second-Order Generalized Integrator for Identification of a Biased Sinusoidal Signal. IEEE Trans. Autom. Control 2012, 57, 1838–1842. [Google Scholar] [CrossRef]

- Matas, J.; Castilla, M.; Miret, J.; de Vicuña, L.G.; Guzman, R. An Adaptive Prefiltering Method to Improve the Speed/Accuracy Tradeoff of Voltage Sequence Detection Methods Under Adverse Grid Conditions. IEEE Trans. Ind. Electron. 2014, 61, 2139–2151. [Google Scholar] [CrossRef]

- Xin, Z.; Wang, X.; Qin, Z.; Lu, M.; Loh, P.C.; Blaabjerg, F. An Improved Second-Order Generalized Integrator Based Quadrature Signal Generator. IEEE Trans. Power Electron. 2016, 31, 8068–8073. [Google Scholar] [CrossRef]

- Rodriguez, P.; Luna, A.; Candela, I.; Mujal, R.; Teodorescu, R.; Blaabjerg, F. Multiresonant Frequency-Locked Loop for Grid Synchronization of Power Converters Under Distorted Grid Conditions. IEEE Trans. Ind. Electron. 2011, 58, 127–138. [Google Scholar] [CrossRef]

- Thacker, T.; Wang, R.; Dong, D.; Burgos, R.; Wang, F.; Boroyevich, D. Phase-Locked Loops using State Variable Feedback for Single-Phase Converter Systems. In Proceedings of the 2009 Twenty-Fourth Annual IEEE Applied Power Electronics Conference and Exposition, Washington, DC, USA, 15–19 February 2009; pp. 864–870. [Google Scholar]

- Blanco, C.; Reigosa, D.; Briz, F.; Guerrero, J.M. Quadrature signal generator based on all-pass filter for single-phase synchronization. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 2655–2662. [Google Scholar]

- Ramezani, M.; Golestan, S.; Li, S. Non-frequency sensitive all-pass filter based single-phase PLLs. In Proceedings of the 2016 IEEE/PES Transmission and Distribution Conference and Exposition (T D), Dallas, TX, USA, 3–5 May 2016; pp. 1–5. [Google Scholar]

- Lamo, P.; López, F.; Pigazo, A.; Azcondo, F.J. An Efficient FPGA Implementation of a Quadrature Signal-Generation Subsystem in SRF PLLs in Single-Phase PFCs. IEEE Trans. Power Electron. 2017, 32, 3959–3969. [Google Scholar] [CrossRef]

- Lamo, P.; Pigazo, A.; Azcondo, F.J. Two-Sample PLL with Harmonic Filtering Capability Applicable to Single-Phase Grid-Connected Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2020. [Google Scholar] [CrossRef]

- De Normalización, A.E. UNE-EN 50160: Voltage Characteristics of Electricity Supplied by Public Electricity Networks. Available online: https://www.une.org/encuentra-tu-norma/busca-tu-norma/norma?c=N0055031 (accessed on 1 October 2020).

| Functional Blocks | Type | Computational Burden | Dynamics |

|---|---|---|---|

| PD | EPLL [29,30] | Medium | Performance issues due to the π/2 phase shift |

| pPLL [31,32] | Medium | Oscillations of the phase error signal | |

| QSG PLL | Depend on the selected strategy (see next section) | ||

| LF | Zero order [17] | Low | Performance issues under phase ramps and frequency variations |

| First order [1] | Low | Good under slow variations in the grid frequency | |

| High order [19,20] | Medium–High | Good | |

| Adaptive [21,22] | High | Good | |

| VCO | LUTs [22] | High | Good |

| CORDIC [24,25] | High | Good | |

| DCO [26] | Low | Good | |

| Approach | ||

|---|---|---|

| D-backward | ||

| D-central difference | ||

| D-Richardson extrapolation |

| QSG | +/− | ×/÷ | T | M |

|---|---|---|---|---|

| SOGI [65] | 4 | 3 | 0 | 2 |

| MSOGI [75] | 1 + 6F | 4F | 0 | 2F |

| DSC [37] | 1 | 1 | 0 | 2 × round(N/4) |

| DSC + filter [53] | 10 | 23 | 6 | 16 × round(N) |

| 2S [79] | 2 | 3 | 0 | 2 |

| 2S + filter [80] | 3 + 3F | 3 + 4F | 0 | 2 + 3F |

| T/4 [1] | 0 | 0 | 0 | round(N/4) |

| Recent T/4 [39] | 1 | 1 | 0 | round(N/4) |

| KF [60] | 407 | 349 | 6 | 0 |

| LKF [62] | 8 | 13 | 0 | 0 |

| IPT [40] | 6 | 7 | 0 | 6 |

| MHDC [44,45] | 9 | 12 | 2 | 9 |

| SC [46] | 2 | 3 | 1 | 1 |

| HT [1] | 5 | 3 | 0 | 10 |

| APF [39,76] | 2 | 2 | 0 | 2 |

| D-backward | 1 | 1 | 0 | 1 |

| D-central difference | 1 | 1 | 0 | 5 |

| D-Richardson extrapolation | 3 | 2 | 0 | 14 |

| RDFT [22] | 4 | 5 | 0 | N + 3 |

| pq theory [31] | 3 | 4 | 1 | 1 |

| Enhanced [28] | 2 | 5 | 2 | 1 |

| T/4 | 2S | DSC | Hilbert | SOGI | |||||

|---|---|---|---|---|---|---|---|---|---|

| Units | Units | % | Units | % | Units | % | Units | % | |

| Registers | 3472 | 3486 | 100.40 | 3521 | 101.41 | 3754 | 108.12 | 3552 | 102.30 |

| LUTs | 4927 | 5449 | 110.59 | 5015 | 101.79 | 5812 | 117.96 | 5393 | 109.46 |

| Occupied sections | 1697 | 1861 | 109.66 | 1686 | 99.35 | 1999 | 117.80 | 1876 | 110.55 |

| LUT flip-flop pairs | 5144 | 5682 | 110.46 | 5244 | 101.94 | 6175 | 120.04 | 5644 | 109.72 |

| RAMB36E1 /FIFO36E1s | 0 | 0 | 100.00 | 0 | 100.00 | 0 | 100.00 | 0 | 100.00 |

| RAMB18E1 /FIFO18E1s | 3 | 2 | 66.67 | 4 | 133.33 | 2 | 66.67 | 2 | 66.67 |

| BUFG/BUGCTROLs | 1 | 1 | 100.00 | 1 | 100.00 | 1 | 100.00 | 1 | 100.00 |

| DSP48E1s | 64 | 72 | 112.50 | 64 | 100.00 | 64 | 100.00 | 72 | 112.50 |

| Design Using Specific Hardware | Rapid Prototyping | ||||

|---|---|---|---|---|---|

| Based on IPs | Based on Reconfigurable Arithmetic Module | SysGen | C Language | ||

| Based on DSPs | Based on LUTs | ||||

| Registers | 299 | 300 | 357 | 237 | 525 |

| LUTs | 465 | 1100 | 669 | 1355 | 451 |

| Occupied sections | 242 | 406 | 257 | 482 | 170 |

| LUT flip-flop pairs | 598 | 1213 | 736 | 1231 | 595 |

| RAMB36E1 /FIFO36E1s | 0 | 0 | 0 | 0 | 0 |

| RAMB18E1 /FIFO18E1s | 0 | 0 | 0 | 1 | 0 |

| BUFG/BUGCTROLs | 2 | 2 | 1 | 1 | 1 |

| DSP48E1s | 3 | 0 | 0 | 28 | 16 |

| Necessary clock cycles | 17 | 17 | 157 | - | 17 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lamo, P.; Pigazo, A.; Azcondo, F.J. Evaluation of Quadrature Signal Generation Methods with Reduced Computational Resources for Grid Synchronization of Single-Phase Power Converters through Phase-Locked Loops. Electronics 2020, 9, 2026. https://doi.org/10.3390/electronics9122026

Lamo P, Pigazo A, Azcondo FJ. Evaluation of Quadrature Signal Generation Methods with Reduced Computational Resources for Grid Synchronization of Single-Phase Power Converters through Phase-Locked Loops. Electronics. 2020; 9(12):2026. https://doi.org/10.3390/electronics9122026

Chicago/Turabian StyleLamo, Paula, Alberto Pigazo, and Francisco J. Azcondo. 2020. "Evaluation of Quadrature Signal Generation Methods with Reduced Computational Resources for Grid Synchronization of Single-Phase Power Converters through Phase-Locked Loops" Electronics 9, no. 12: 2026. https://doi.org/10.3390/electronics9122026

APA StyleLamo, P., Pigazo, A., & Azcondo, F. J. (2020). Evaluation of Quadrature Signal Generation Methods with Reduced Computational Resources for Grid Synchronization of Single-Phase Power Converters through Phase-Locked Loops. Electronics, 9(12), 2026. https://doi.org/10.3390/electronics9122026