The topology shown in

Figure 1 is comprised of four stages: the first stage consists of two current sources (

L1 and

L2) and a DC voltage source (

VDC), the second stage by a parallel resonant tank (

LPrimary and

CR) with magnetic isolation derived by

LPrimary, where

LPrimary is coupled to

LSecondary (from part A to B), the third stage by a full-wave rectifier (

D3–

D6), and the fourth stage by the decoupling elements (

Cc and

Lc). The operation of the circuit is as follows: the two inductors

L1 and

L2 provide the two current sources to the parallel resonant tank, the unidirectional switches

S1 and

S2 short-circuit the current sources periodically in order to feed the parallel resonant tank formed by the transformer (composed by

LPrimary and

LSecondary) and the resonant capacitor

CR with a square current waveform. The parallel resonant tank filters this waveform and applies a sinusoidal voltage waveform to the full-bridge rectifier (

D3, D4, D5 and

D6). The rectified signal is filtered by

LC and

CC and it is applied to the load (

RLOAD). One important characteristic of the CFRC (

Figure 1) is the need to have an overlapped control, because if there is no overlapping control between

M1 and

M2, the inductance (

L1) would be charged by the current

iL1 (t), and the current

iL2 (t) from the second inductance (

L2) would flow directly through the resonant tank. Under the dual condition,

iL1 (t) would flow through the resonant tank and

iL2 (t) through

L2. However, if there is no overlapped control,

iL1 (t) and

iL2 (t) could be canceled, although not completely, producing a considerable increase in the losses on the unidirectional switches. Furthermore, the resonant tank and the components used need to be carefully selected, since these parameters directly affect the overlap signals in

S1 and

S2. Additionally, the high frequency transformer is a critical part of the resonant converter. Its design affects efficiency, weight, and dimension of the whole topology. This fact is important to improve the efficiency of the topology. Considering these statements, a brief comparison of different semiconductor devices should be performed. As a result of the advancement in the field of power semiconductor technologies [

37,

38,

39], SiC MOSFETs, SiC junction gate field-effect transistors (JFETs), SiC Schottky barrier diodes, and gallium nitride (GaN) transistors provide a valuable opportunity to obtain high efficient performance with compact size. Part of the primary characteristics in all power semiconductor devices are related to the operating at high power, high frequency, and high temperature. In fact, many works have been reported in the literature analyzing the physical breakdown mechanisms, modeling, characterizations, and the trade-off characteristics between the breakdown voltage and the on-resistance of Si, SiC, and GaN-based power semiconductor devices [

40,

41,

42,

43]. As a result of these studies, some characteristics are shown in

Table 1.

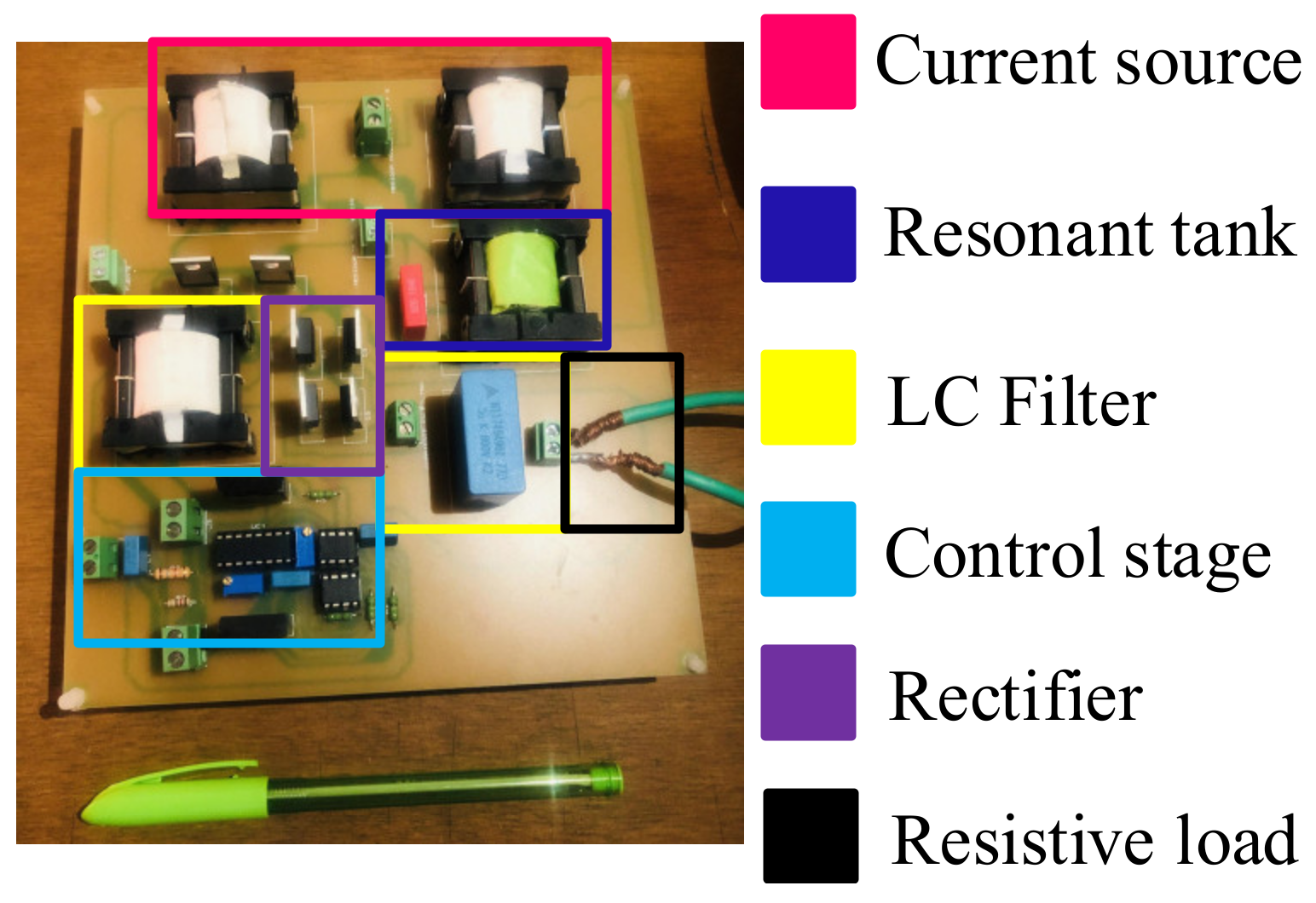

Overlap in Gate-Signals of M1 and M2

To determine the effect of the overlap, an initial simulation study is developed under the following considerations: (1) time delay proposed between the turn on of

M1 and

M2 is 0.49, this value was taken because

TD must be as close as 0.5, with the aim of not having such a long overlap; (2) a quality factor of the resonant tank is sufficiently high to filter all the current harmonics, except the fundamental; (3) all inductors and capacitors are lossless; (4)

D3, D4, D5, and

D6 are ideal diodes; and (5) unidirectional switches were performed by SiC diodes (C4D08120) and SiC MOSFETs (C2M0160120D), because of their improvements for AC-DC and DC-DC converters. These devices can operate with reduced conduction and switching losses over higher frequencies, and higher temperatures minimize the requirements for the passive components and reduce cooling demands [

47,

48,

49]; however, the performance given by SiC power devices will be compared with Si and GaN. The switching frequency (

Fsw) was considered to be 200 kHz. The simulation results in

Figure 2 created in PSpice

® show the key waveforms of

S1 (

Figure 2a),

S2 (

Figure 2b),

D1 (

Figure 2c), gate-signals in

M2 (

Figure 2d), and

M1 (

Figure 2e). These simulation results are also based on the design parameters and design methodology shown in

Table 2 and

Table 3.

From

Figure 2, when the overlap begins (gate-signal in

M1 and gate-signal in

M2 are in the on-state)

, the current

iS1 decreases to zero, and the current

iS2 increases. This behavior is related to the charge and discharge of the internal stray capacitances of

D1 and

D2.

In this sense, when

S2 is in the on-state,

M2 can be modeled by its output parasitic capacitance in parallel with its parasitic resistance, and

D2 as a parallel made up of the same diode and its stray capacitance. Furthermore,

Figure 3 shows the hard switching in

D1 and

M1 caused by the effect given by the overlap. In this manner, to determine the converter performance effects, based on

Figure 3, three modes are proposed considering the current and voltage waveforms of

S1 and

S2; therefore, the first mode (MODE A from

t0 to

t2) performs a fall-rise of

is1 and a rise-fall of

is2, the second mode (MODE B from

t2 to

t3) represents the time when

is1 keeps its value and

is2 is zero, and the third mode (MODE C from

t3 to

t4) represents the dual condition of MODE B.

From

Figure 3 and based on times

t0 to

t4, the equivalent circuits are obtained, as shown in

Figure 4. In these circuits, an equivalent resistance (

Requ) was considered as the load in the resonant tank, where

Requ represents the

RLOAD seen from

Lr. Then, based on the operation, MODES are shown during the overlap and equivalent circuits in

Figure 3 and

Figure 4, respectively. The modes A, B, and C are detailed below:

Time

t0-t1 (

Figure 4a): this time starts when the gate-signal in

M2 is in the on-state, thereby the overlap starts. During this time,

iS1 decreases to zero (and remains at 0 A) and

iS2 increases its value the same as the input current (

IL). Moreover, since

S2 is in the on-state, the diode

D1 can be modeled as a parallel by the same diode and its stray capacitance

CD1, and

M1 by a drain-source resistance

RDSON M1. In this moment, the voltage of the stray capacitance in

D1 (

VCD1) can be represented as shown in Equation (1).

where

VRES is the voltage of the resonant tank,

VDSM1 represents the voltage drain-source in

M1,

VDSM2 the voltage drain-source in

M2, and

VD2 the forward voltage in

D2. Furthermore, in this time, there is a “charge” condition in

CD1 which generates an increase of switching losses in

S1 until the voltage in

D1 reaches its forward voltage.

Time

t1–

t2: It represents the instant when

iS1 increases and

iS2 decreases its value, turning on

S1, and modeled

D2 as a parallel by

D2 and its stray capacitance

CD2, and

M2 by a drain-source resistance

RDSON M2 (

Figure 4b). In this time, the voltage of the stray capacitance in

D2 (

VCD2) can be represented as shown in Equation (2), where

VD1 represents the forward voltage in

D1.

Time

t2–

t3: In MODE B (

Figure 4c),

M1 and

M2 are in the on-state. Furthermore,

is1 stays constant and

is2 stays at 0A, modeling

D2 and

M2 the same as from

t1 to

t2. On the other hand, there is no current in

S2 but there is a voltage in

D2, increasing the power losses. Moreover, the voltage of the stray capacitance in

D2 (

VCD2) can be represented the same as Equation (2).

Time

t3–

t4: MODE C starts (

Figure 4d), the gate-signal in

M1 is in the off-state, and thus the overlap is finished. Furthermore,

M2 is in the on-state and

is2 is increasing. During this time,

S1 is in the off-state after finishing the discharging process, which causes the stored energy to be lost not only in

M2 but also in

D2. Additionally, as a result of

M1 in the off-state,

VRES will be split in

D1 and

M1 with a complementary voltage in

D2. In fact,

VCD2 can be modeled as shown in Equation (3).

From

Figure 3 and

Figure 4, the behavior given by the recovery time in

D1 and

D2 during their shutdown states causes

D1 and

D2 to be in the on-state even when

M1 and

M2 are in the off-state, which indicates that if the complete switch is analyzed, the MOSFET and diode do not share the same shutdown time. Furthermore, in MODE A,

iS2 increases, and the stray capacitance in

D1 is discharging, causing

iS1 to decrease to zero, then, the current

iS1 increases its value because the current

iS2 decreases. This current will be zero, until the voltage in

D2 is zero again.

In this sense, when the voltage in

D2 is zero, the current

iS2 will increase, therefore, this is the main reason to generate hard switching in the complete switch. On the other hand, the power losses achieved in the simulation by

S1 plus

S2 are 31 W with a global efficiency of 62% and a time delay between gate-signals of 0.49. It is important to estimate the applied overlap. Therefore,

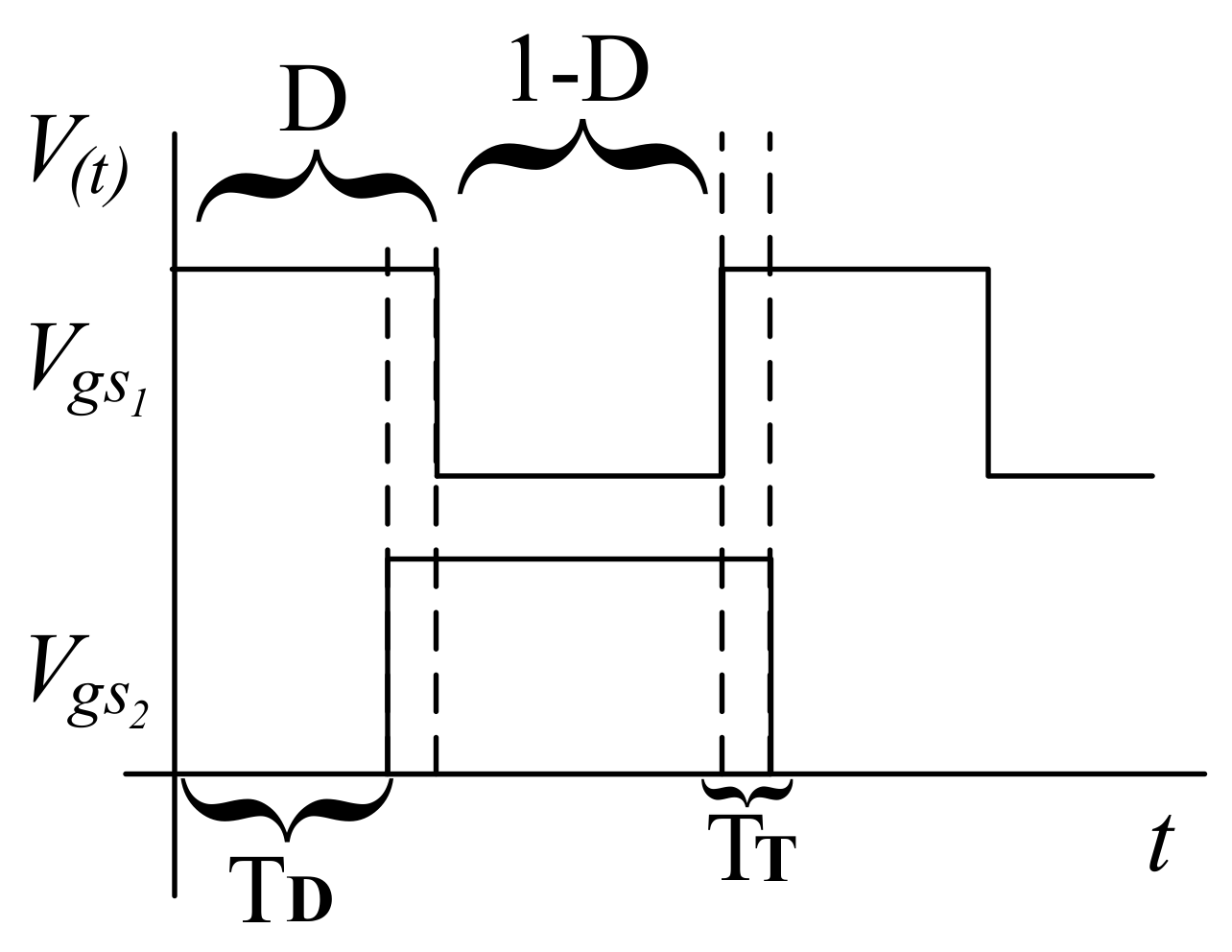

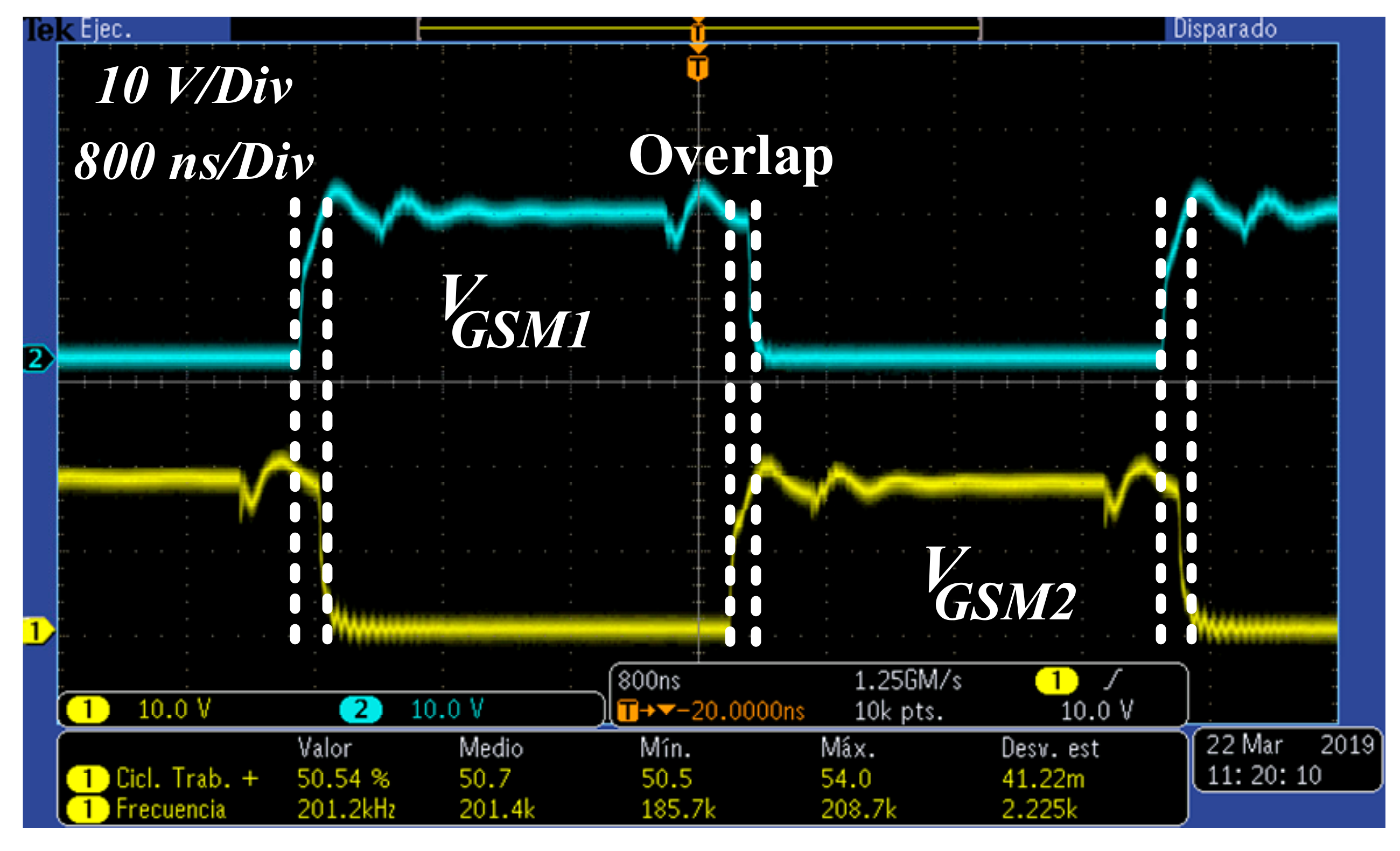

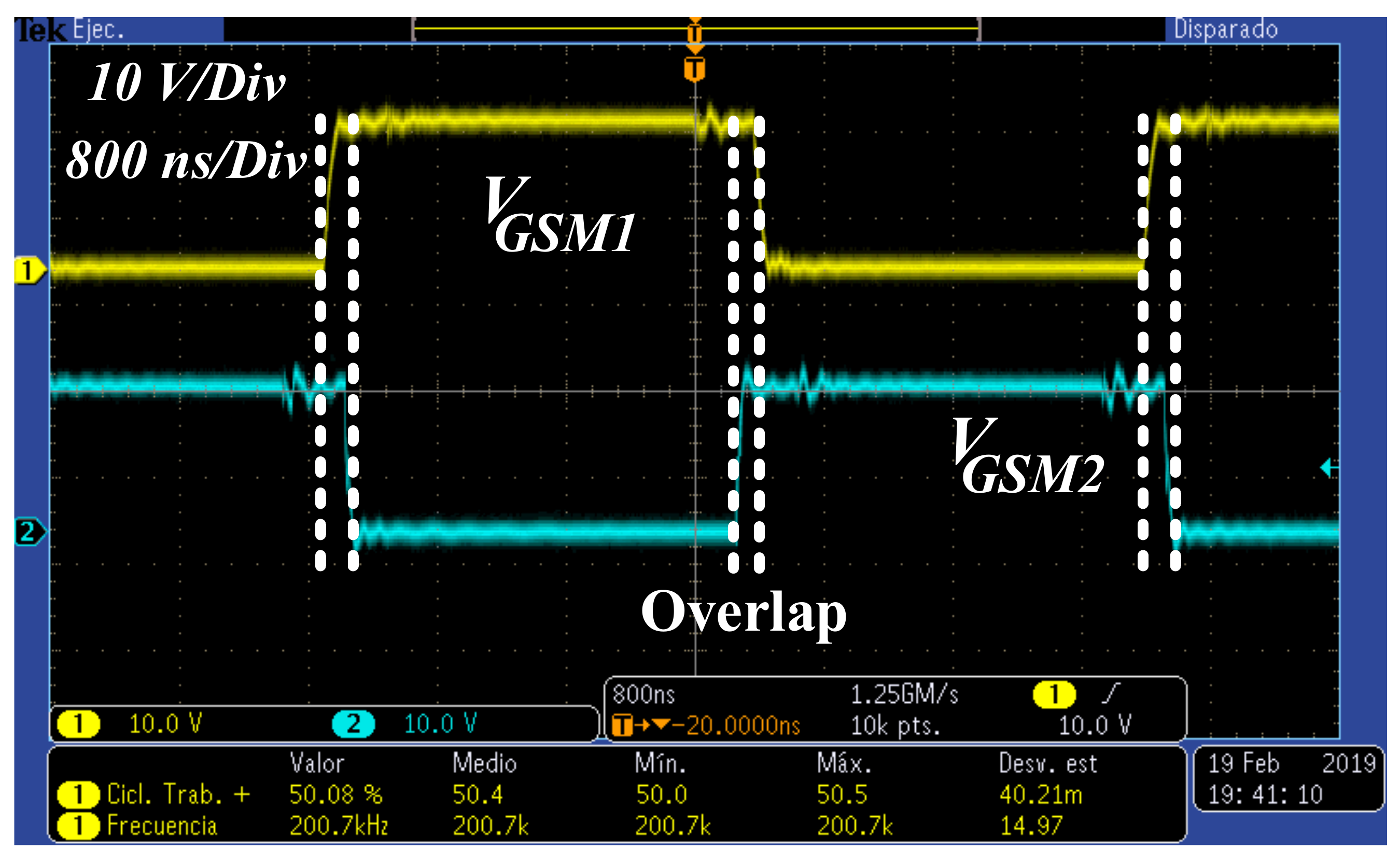

Figure 5 shows the overlap to consider in the analysis.

From

Figure 5,

D is the applied duty cycle, the time delay between the gate-signals of

M1 and

M2 (

VGSM1 and

VGSM2), and represents the overlap time when

M1 and

M2 are in the on-state. As mentioned,

TT is defined in Equation (4) and

TD is defined in Equation (5).

Replacing (4) into (5) and considering that the energy transferred to the load depends on the duty cycle, the selected duty cycle of the resonant tank is 0.5.

To assess the combination of power semiconductor devices in the unidirectional switch and to verify Equation (7) based on the parameters and design methodology described above, three different converters are designed combining Si-MOSFET and diode (first array), SiC-MOFET and diode (second array), and GaN-transistor SiC-diode (third array). The power devices are selected based on the stress level calculations as well as the similarity in the electrical ratings between the Si and SiC devices (as a result of the reduced drain to source voltage in the GaN-transistor), parasitic capacitances, current rating, switching speed, on-resistance, maximum junction temperature, and following the primary comparison between the characteristics of every device [

50,

51], mainly focused in the work presented in [

52]. Therefore,

Table 4 shows the specifications of each power device used in the design.

Figure 6 shows the efficiency versus variations in

TD performed by different power semiconductor devices obtained in the simulation.

According to

Figure 6 and considering

TD = 0.5, a global efficiency and total power losses (switching plus conduction) in

S1 plus

S2 of 86% and 27 W were performed by the Si-MOSFET and Si-diode combination. Furthermore, SiC-MOSFET plus SiC-diode performed an efficiency and power losses in

S1 plus

S2 of 92.7% and 14 W, respectively. Finally, the performance given by the combination of GaN-transistor plus SiC-diode were similar to the combination of SiC-MOSFET plus SiC-diode with an efficiency of 94% and power losses in

S1 plus

S2 of 11 W.

Moreover, the performance given by the overlap dramatically affects the efficiency of the whole converter, thus, it is suggested to take into account an overlapped control in a CFRC since the problems associated with the discharging of the transistor output the capacitance (

Cout). When the switch voltage increases, the MOSFET (M

1)

Cout is charged via

D1 to the peak value of the switch voltage, and then remains at that voltage until the transistor turns on. At this time, the capacitance

Cout is discharged through the transistor, resulting in switching loss. According to

Figure 6, with

TD estimated to be 0.5, the power losses in

S1 plus

S2 and global efficiency performed by SiC-MOSFET plus SiC-diode were 14 W and 92.7 %, which performance is reasonably similar in comparison with the combination of GaN-transistor plus SiC-diode. In this way, the complete simulation results achieved from the DC-DC resonant converter performed by SiC-MOSFET plus SiC-diode are presented in

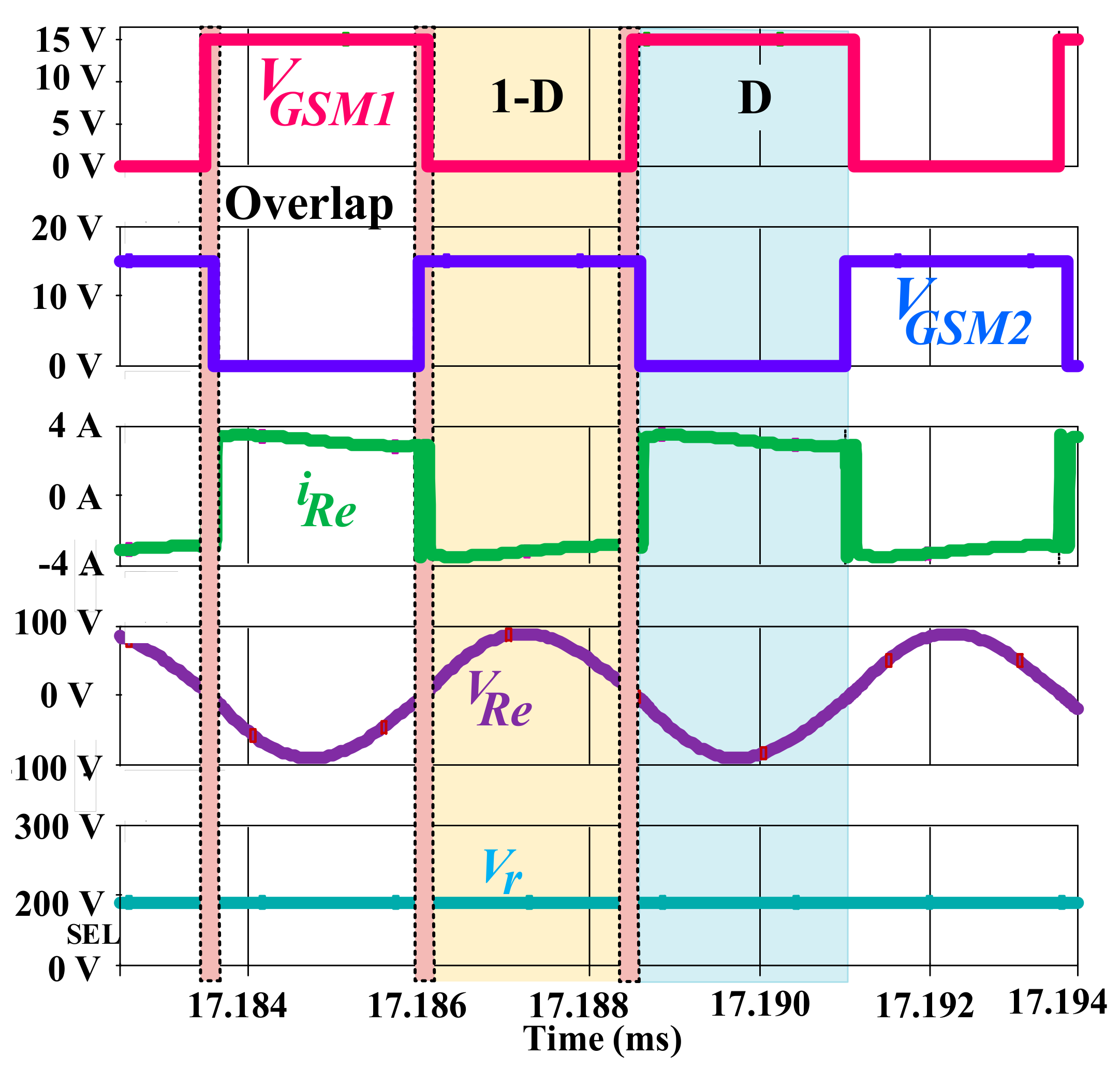

Figure 7.

The key waveforms from the resonant tank in

Figure 7 show the previously calculated overlap of

M1 and

M2. Alternatively, both the input current (

iRe) and voltage (

VRe) at the resonant tank show a condition close to resonance since both signals are in phase. Furthermore, the output voltage (

Vr) is 207 V, which indicates that the parameters proposed in

Table 2 have a relative error of 1.42% between them and the simulation results.

On the other hand, with the aim to compare the performance and conditions given for the topology, a comparison of a non-overlapped (

Figure 8a) and overlapped control (

Figure 8b) was made, focusing its attention on

vS1 and

iS1.

From

Figure 8a, with a non-overlapped control, not only the voltage and current on S1, but also the resonance condition will be dramatically affected, causing negative voltages, as shown in

Figure 8a. This issue would affect the entire efficiency because an overlap control provides a ramp shift signal to the ramp generator in response to a detection signal that indicates activity of the switches in the power stage. The ramp shift signal adjusts the first and second ramp signals relative to each other so as to minimize any gap and any overlap between the first and second ramp signals.

In this way, to have a good relation overlap-efficiency, an important point to consider is to work with an overlapped control to have optimal conditions, as shown in

Figure 8b. Furthermore,

Figure 8b shows less power losses as a result of the less current peaks obtained in comparison with the non-overlapped behavior presented in

Figure 8a.