A Learning-Based Framework for Circuit Path Level NBTI Degradation Prediction

Abstract

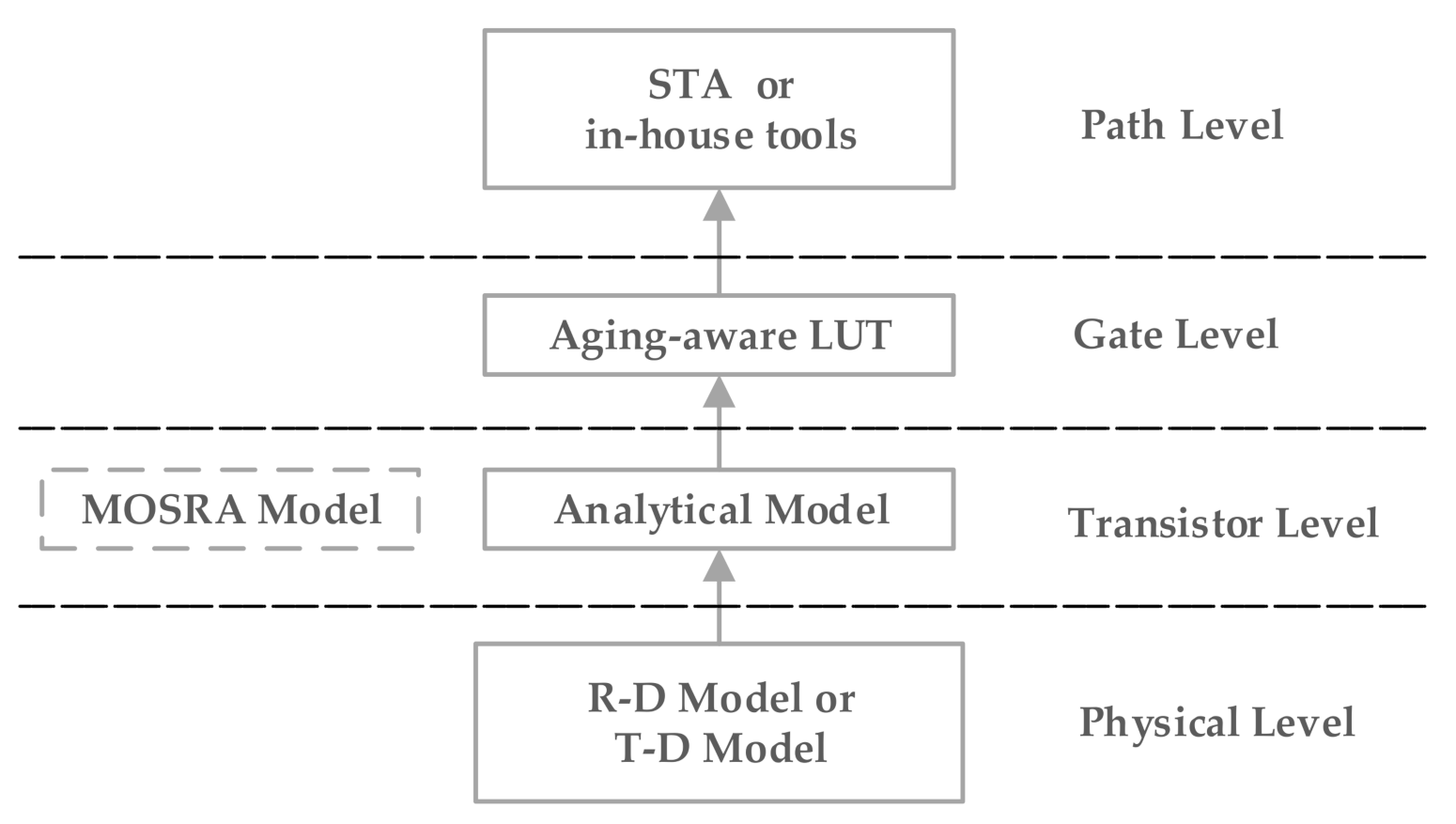

1. Introduction

2. Literature Review on NBTI Degradation Research

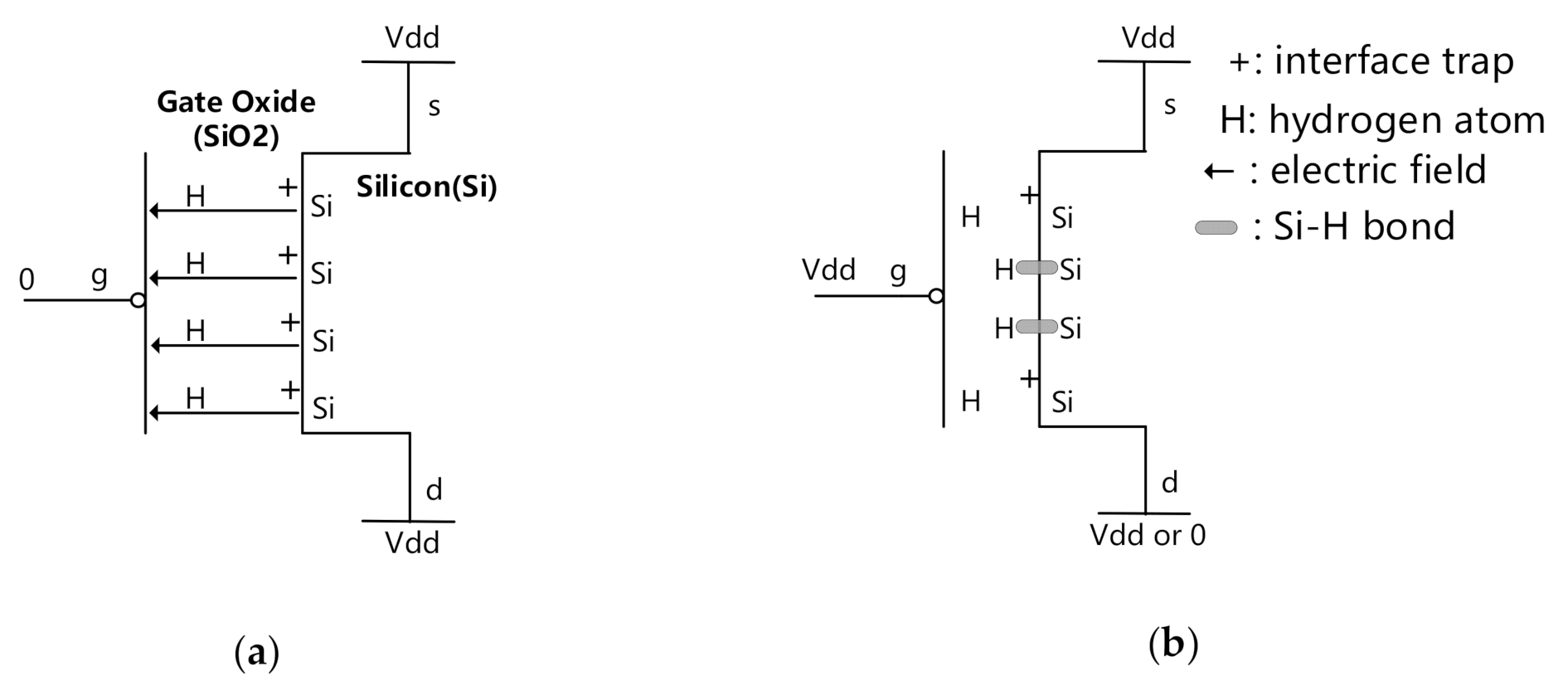

2.1. Physical Level

2.2. Transistor Level

2.2.1. NBTI Analytical Model

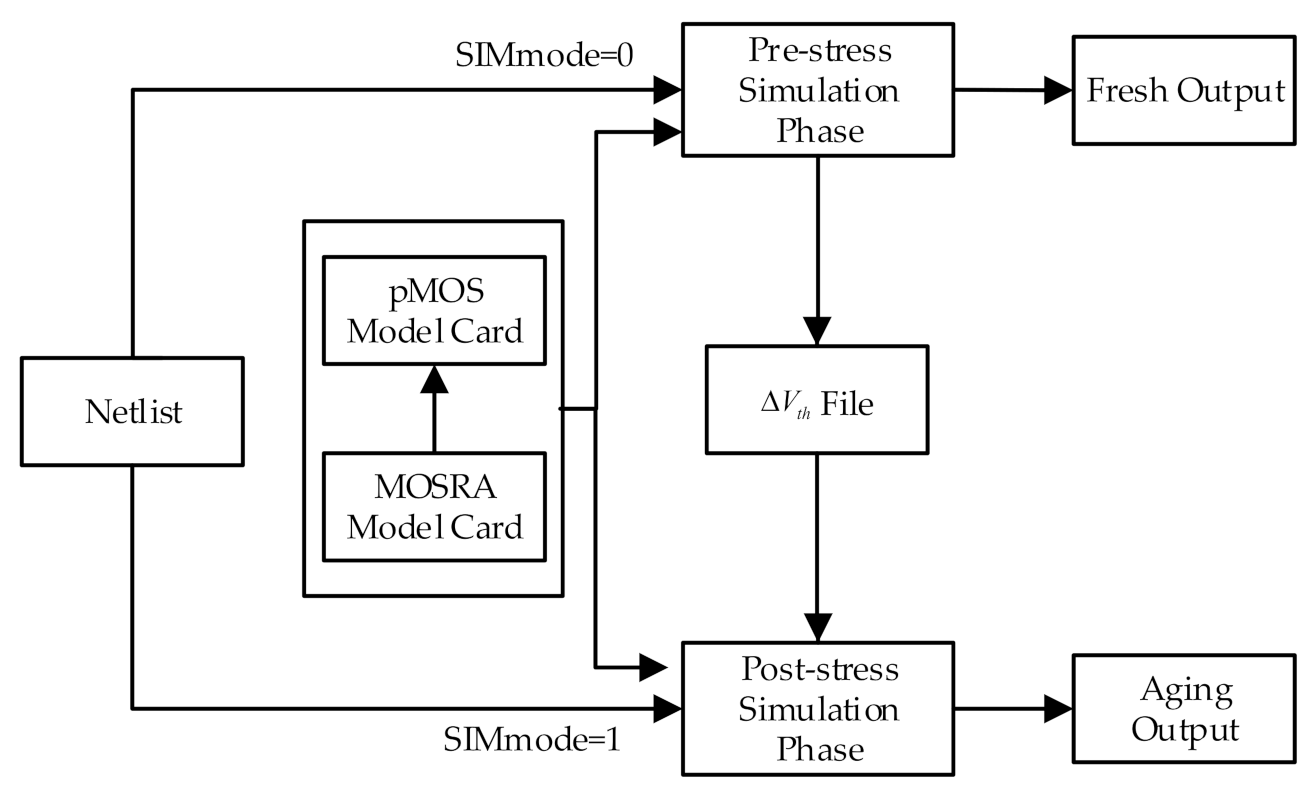

2.2.2. MOSFET Model Reliability Analysis (MOSRA) Aging Model

2.3. Gate Level

2.4. Path Level

3. Main Idea

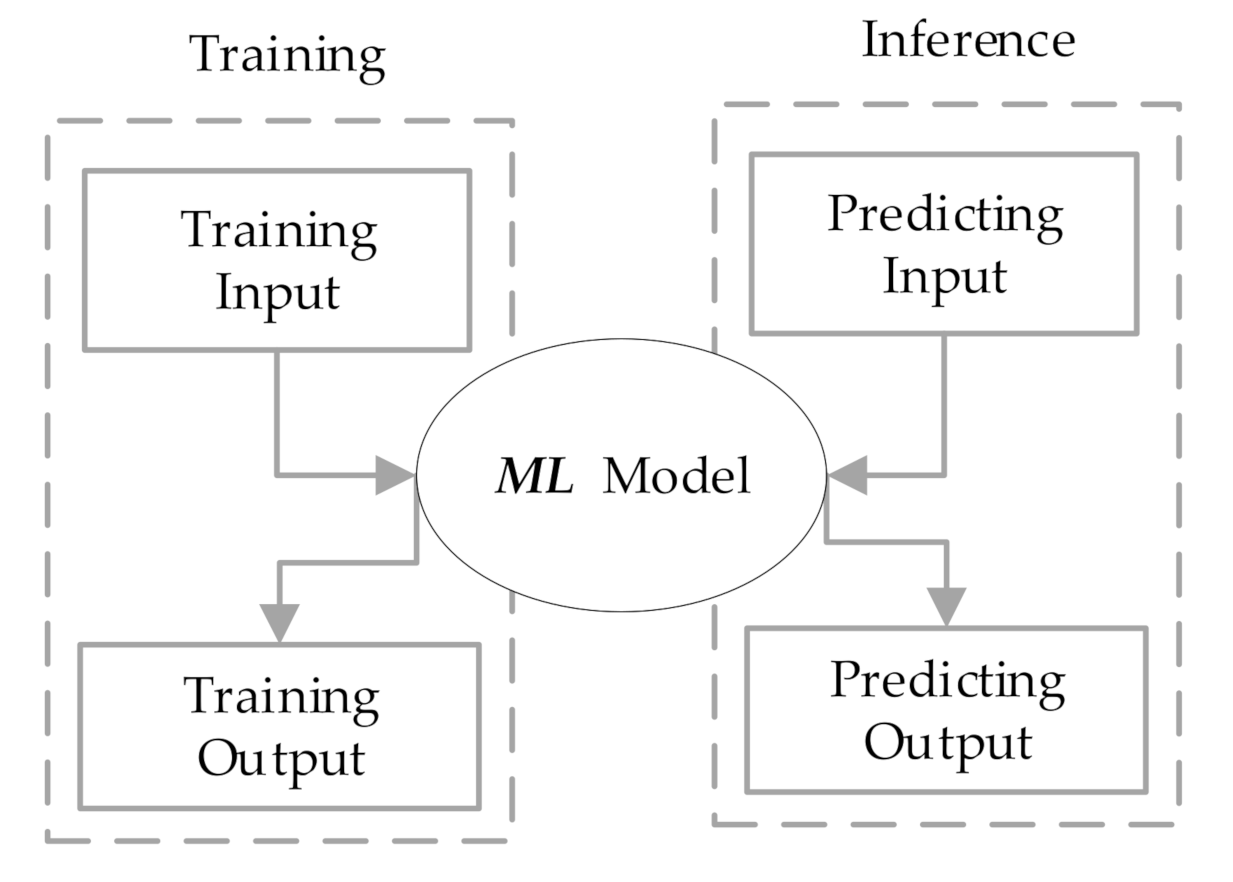

4. Proposed Learning-Based Framework

5. Numerical Experiment

5.1. Circuit Level Experiment Setup

5.2. Experiment Result

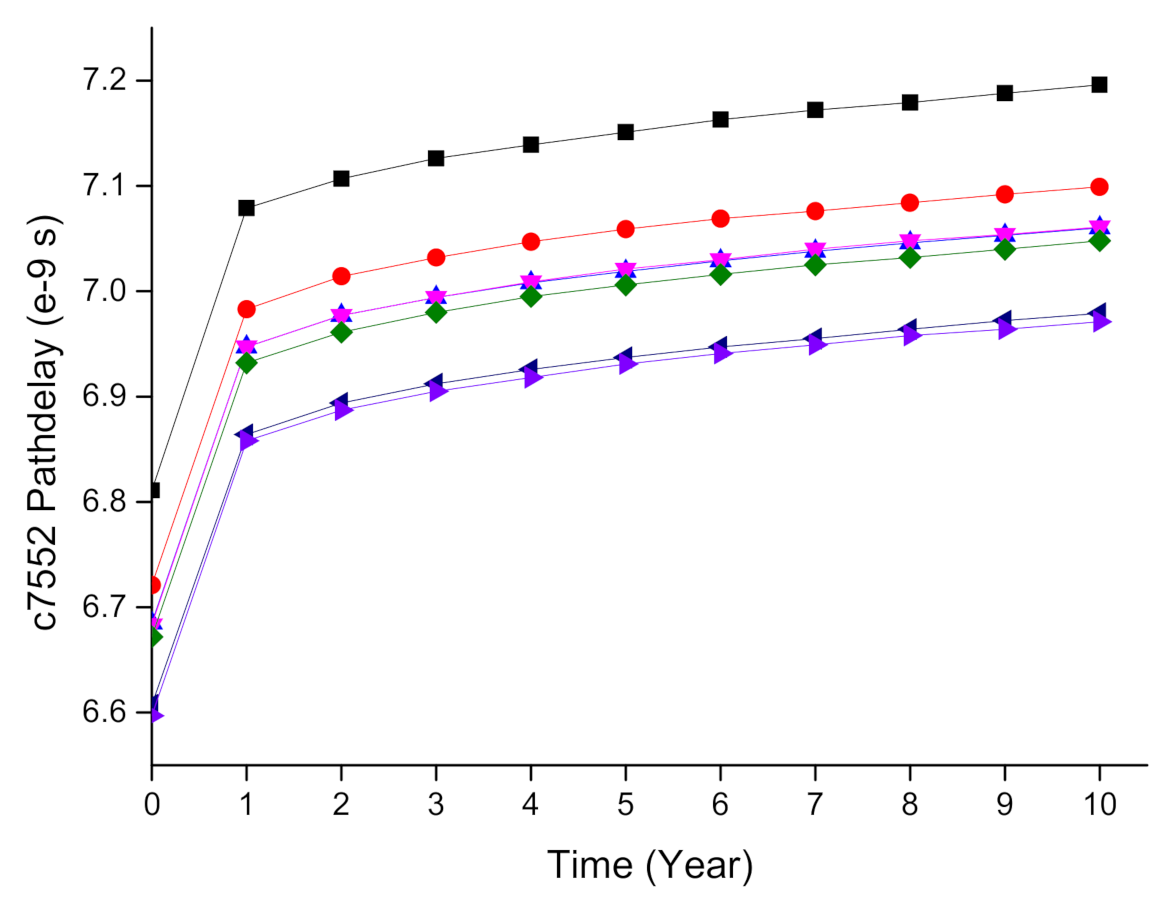

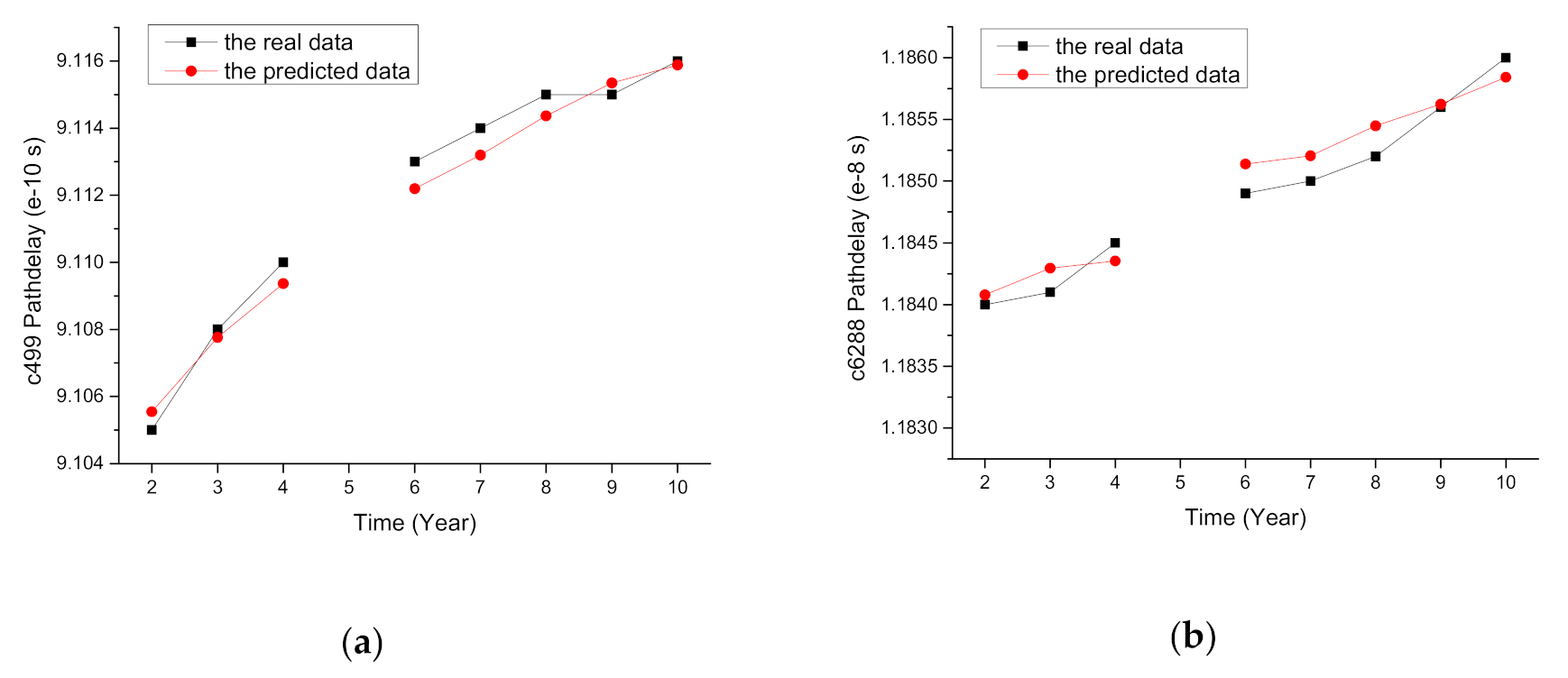

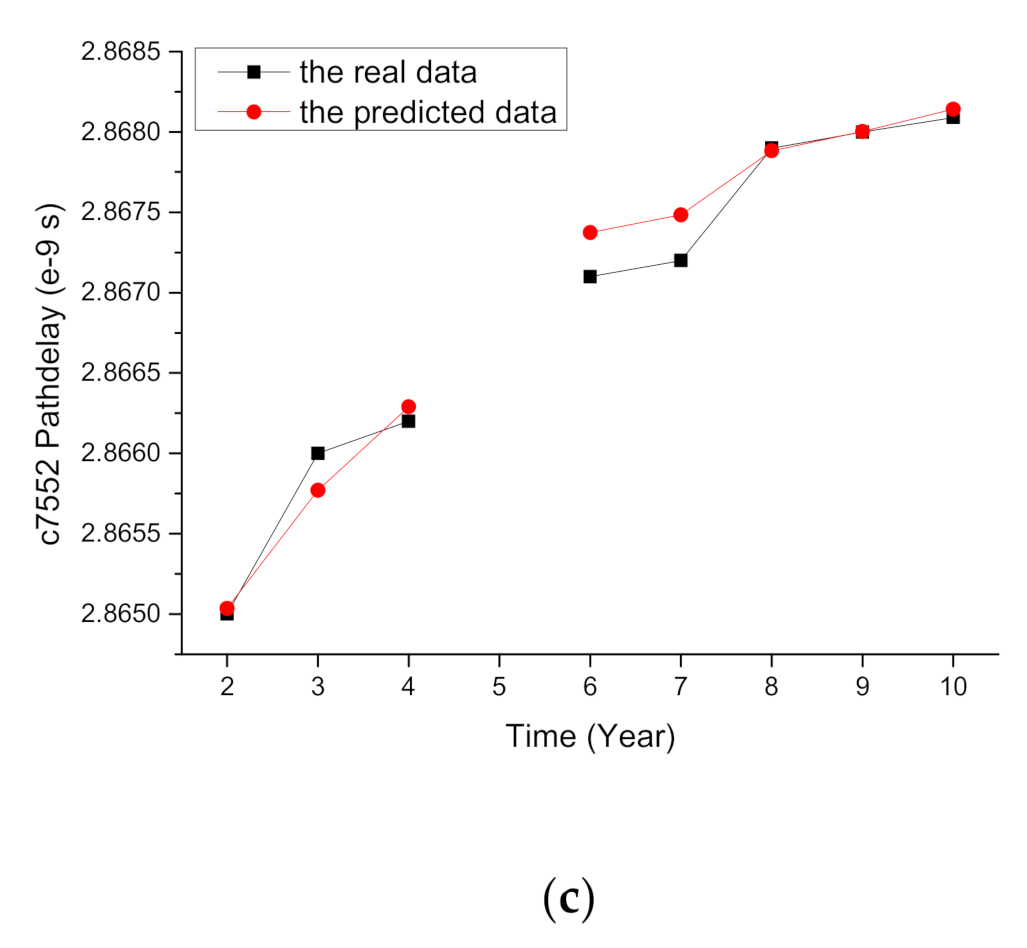

5.2.1. Static NBTI Condition

5.2.2. Dynamic NBTI Condition

5.2.3. Comparison with Other Studies

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Khalid, U.; Mastrandrea, A.; Olivieri, M. Effect of NBTI aging and process variations on write failures in CMOS and FinFET flip-flops. Microelectron. Reliab. 2015, 55, 2614–2626. [Google Scholar] [CrossRef]

- Lu, Y.H.; Shang, L.; Zhou, H.; Zhu, H.L.; Yang, F.; Zeng, X. Statistical reliability analysis under process variation and aging effects. In Proceedings of the 2009 46th Design Automation Conference, San Francisco, CA, USA, 26–31 July 2009; pp. 514–519. [Google Scholar]

- Nur, A.Z.; Hanim, H.; Muhamad, F.Z.; Abdul, K.H. Investigation of negative bias temperature instability (NBTI) effects on standard cell library circuits performance. In Proceedings of the 2019 IEEE Regional Symposium on Micro and Nanoelectronics, Genting Highland, Pahang, Malaysia, 21–23 August 2019; pp. 30–33. [Google Scholar]

- Hussam, A.; Victor, M.; Jörg, H. Estimating and optimizing BTl aging effects: From physics to CAD. In Proceedings of the 2018 International Conference on Computer-Aided Design, San Diego, CA, USA, 5–8 November 2018; pp. 1–6. [Google Scholar]

- Hiroaki, K.; Yukio, M.; Masanori, H.; Takao, O. Comparative study on delay degrading estimation due to NBTI with circuit/instance/transistor-level stress probability consideration. In Proceedings of the 11th International Symposium on Quality Electronic Design, San Jose, CA, USA, 22–24 March 2010; pp. 646–651. [Google Scholar]

- Denais, M.; Parthasarathy, C.; Ribes, G.; Rey-Tauriac, Y.; Revil, N.; Bravaix, A.; Huard, V.; Perrier, F. On-the-fly characterization of NBTI in ultra-thin gate oxide PMOSFET’s. In Proceedings of the 2004 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 13–15 December 2004; pp. 109–112. [Google Scholar]

- Chaudhary, A.; Mahapatra, S. A physical and SPICE mobility degradation analysis for NBTI. IEEE Trans. Electron Devices 2013, 60, 2096–2103. [Google Scholar] [CrossRef]

- Sun, H.C.; Huang, C.F.; Chen, Y.T.; Wu, T.Y.; Liu, C.W.; Hsu, Y.J.; Chen, J.S. Threshold voltage and mobility extraction of NBTI degradation of Poly-Si thin-film transistors. IEEE Trans. Electron Devices 2010, 57, 3186–3189. [Google Scholar] [CrossRef]

- Herfst, R.W.; Schmitz, J.; Scholten, A.J. Simultaneous extraction of threshold voltage and mobility degradation from on-the-fly NBTI measurements. In Proceedings of the 2011 International Reliability Physics Symposium, Monterey, CA, USA, 10–14 April 2011; pp. XT.6.1–XT.6.4. [Google Scholar]

- Krishnan, A.T.; Chancellor, C.; Chakravarthi, S.; Nicollian, P.E. Material dependence of hydrogen diffusion: Implications for NBTI degradation. In Proceedings of the 2005 IEEE International Electron Devices Meeting, Washington, DC, USA, 5 December 2005; pp. 688–691. [Google Scholar]

- Mahapatra, S.; Goel, N.; Desai, S.; Gupta, S.; Jose, B.; Mukhopadhyay, S.; Joshi, K.; Jain, A.; Islam, A.E.; Alam, M.A. A comparative study of different physics based NBTI models. IEEE Trans. Electron Devices 2013, 60, 901–916. [Google Scholar] [CrossRef]

- Tibor, G.; Wolfgang, G.; Victor, S.; Ben, K. The universality of NBTI relaxation and its implications for modeling and characterization. In Proceedings of the 45th Annual IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 15–19 April 2007; pp. 268–280. [Google Scholar]

- Naphade, T.; Goel, N.; Nair, P.R.; Mahapatra, S. Investigation of stochastic implementation of reaction diffusion (RD) models for NBTI related interface trap generation. In Proceedings of the 2013 IEEE International Reliability Physics Symposium, Anaheim, CA, USA, 14–18 April 2013; pp. XT.5.1–XT.5.11. [Google Scholar]

- Vattikonda, R.; Wang, W.; Cao, Y. Modeling and minimization of PMOS NBTI effect for robust naometer design. In Proceedings of the 2006 Design Automation Conference, San Francisco, CA, USA, 24–28 July 2006; pp. 1047–1052. [Google Scholar]

- Bhardwaj, S.; Wang, W.; Vattikonda, R.; Cao, Y.; Vrudhula, S. Predictive modeling of the NBTI effect for reliable design. In Proceedings of the 2006 IEEE Custom Integrated Circuits Conference, Jose, CA, USA, 10–13 September 2006; pp. 1047–1052. [Google Scholar]

- Chen, J.; Wang, S.; Tehranipoor, M. Critical-reliability path identification and delay analysis. ACM J. Emerg. Technol. Comput. Syst. 2014, 10, 12. [Google Scholar] [CrossRef]

- Mohamad Saofi, M.S.S.; Hussin, H.; Muhamad, M.; Abdul, W.Y. Investigation of the NBTI and PBTI effects on multiplexer circuit performances. In Proceedings of the 2020 IEEE International Conference on Semiconductor Electronics, Kuala Lumpur, Malaysia, 28–29 July 2020; pp. 49–52. [Google Scholar]

- Zainudin, M.F.; Hussin, H.; Halim, A.K.; Jamilah, K. Effects of permanent and recoverable component of NBTI mechanisms on flip flop circuits designed using planar MOSFET and FinFET. In Proceedings of the 2018 IEEE Symposium on Computer Applications & Industrial Electronics, Penang, Malaysia, 28–29 April 2018; pp. 145–149. [Google Scholar]

- Zainudin, M.F.; Hussin, H.; Halim, A.K.; Karim, J. Aging analysis of high performance FinFET flip-flop under dynamic NBTI simulation configuration. In Proceedings of the 2017 International Conference on Applied Electronic and Engineering, Kuching, Sarawak, Malaysia, 7–8 August 2017; p. 012012. [Google Scholar]

- Tudor, B.; Wang, J.; Chen, Z.; Tan, R.; Liu, W.; Lee, F. An accurate and scalable MOSFET aging model for circuit simulation. In Proceedings of the 12th International Symposium on Quality Electronic Design, Santa Clara, CA, USA, 14–16 March 2011; pp. 1–4. [Google Scholar]

- Tudor, B.; Wang, J.; Sun, C.; Chen, Z.; Liao, Z.; Tan, R.; Liu, W.; Lee, F. MOSRA: An efficient and versatile MOS aging modeling and reliability analysis solution for 45 nm and below. In Proceedings of the 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 1–4 November 2010; pp. 1645–1647. [Google Scholar]

- Firouzi, F.; Kiamehr, S.; Tahoori, M.; Nassif, S. Incorporating the impacts of workload-dependent runtime variations into timing analysis. In Proceedings of the 2013 Design, Automation & Test in Europe Conference & Exhibition, Grenoble, France, 18–22 March 2013; pp. 1022–1025. [Google Scholar]

- Bian, S.; Shintani, M.; Morita, S.; Hiromoto, M.; Sato, T. Nonlinear delay-table approach for full-chip NBTI degradation prediction. In Proceedings of the 2016 17th International Symposium on Quality Electronic Design, Santa Clara, CA, USA, 15–16 March 2016; pp. 307–312. [Google Scholar]

- Bian, S.; Hiromoto, M.; Shintani, M.; Sato, T. LSTA: Learning-based static timing analysis for high-dimensional correlated on-chip variations. In Proceedings of the 2017 54th ACM/EDAC/IEEE Design Automation Conference, Austin, TX, USA, 18–22 June 2017; pp. 1–6. [Google Scholar]

- Pan, Z.; Li, M.; Yao, J.; Lu, H.; Ye, Z.; Li, Y.; Wang, Y. Low-cost high-accuracy variation characterization for nanoscale IC technologies via novel learning-based techniques. In Proceedings of the 2018 Design, Automation & Test in Europe Conference & Exhibition, Dresden, Germany, 19–23 March 2018; pp. 797–802. [Google Scholar]

| Path | 0 Years (xi1) | 1 Years (xi2) | 2 Years (xo1) | 3 Years (xo2) | 4 Years (xo3) | 5 Years (xi3) | 6 Years (xo4) | 7 Years (xo5) |

|---|---|---|---|---|---|---|---|---|

| tr1 | 9.077 | 9.102 | 9.105 | 9.108 | 9.110 | 9.111 | 9.113 | 9.114 |

| tr2 | 8.850 | 8.875 | 8.879 | 8.881 | 8.882 | 8.884 | 8.885 | 8.886 |

| tr3 | 8.831 | 8.855 | 8.858 | 8.860 | 8.862 | 8.863 | 8.865 | 8.866 |

| tr4 | 8.825 | 8.848 | 8.852 | 8.854 | 8.856 | 8.857 | 8.858 | 8.859 |

| pr1 | 8.726 | 8.749 | ^ | ^ | ^ | 8.757 | ^ | ^ |

| Signal Expression | Stress Probability | NBTI Mode | |

|---|---|---|---|

| Case 1 | pwl (0ns vdd 10n vdd 10.005n 0) | / | Static |

| Case 2 | pulse (vdd 0 10n 20n 20n 130n 500n) | 0.3 | Dynamic |

| Case 3 | pulse (vdd 0 10n 20n 20n 230n 500n) | 0.5 | Dynamic |

| Case 4 | pulse (vdd 0 10n 20n 20n 330n 500n) | 0.7 | Dynamic |

| c499 | c6288 | c7552 | ||

|---|---|---|---|---|

| rRMSE (%) | Linear | 0.04355 | 0.06647 | 0.09132 |

| k-nearest neighbor | 0.0677 | 0.0806 | 2.5468 | |

| random forest | 0.0333 | 0.493 | 6.15 | |

| MAE (unit: × 10−9 s) | linear | 0.000281 | 0.000454 | 0.000249 |

| k-nearest neighbor | 0.005849 | 0.006720 | 0.111890 | |

| random forest | 0.002848 | 0.030402 | 0.218054 | |

| runtime (unit: s) | linear | 0.0015 | 0.0010 | 0.0010 |

| k-nearest neighbor | 0.045 | 0.035 | 0.037 | |

| random forest | 0.30 | 0.28 | 0.29 | |

| HSPICE | 7.77 | 243.08 | 91.51 | |

| s13207 | s15850 | s38584 | ||

|---|---|---|---|---|

| rRMSE (%) | Linear | 0.00923 | 0.00889 | 0.021880 |

| k-nearest neighbor | 2.7448 | 3.7535 | 1.4827 | |

| random forest | 1.3906 | 1.7398 | 1.4831 | |

| MAE (unit: × 10−9 s) | linear | 0.000286 | 0.000317 | 0.000449 |

| k-nearest neighbor | 0.096324 | 0.165775 | 0.0375 | |

| random forest | 0.048801 | 0.07683 | 0.0393 | |

| runtime (unit: s) | linear | 0.001 | 0.001 | 0.001 |

| k-nearest neighbor | 0.032 | 0.015 | 0.027 | |

| random forest | 0.10 | 0.18 | 0.11 | |

| HSPICE | 17.41 | 27.78 | 287.43 | |

| b04 | b08 | b14 | ||

|---|---|---|---|---|

| rRMSE (%) | Linear | 0.007117 | 0.009027 | 0.008589 |

| k-nearest neighbor | 1.1185 | 0.9861 | 1.5987 | |

| random forest | 3.8164 | 2.3412 | 0.1256 | |

| MAE (unit: × 10−9s) | linear | 0.000431 | 0.00054 | 0.00021 |

| k-nearest neighbor | 0.076392 | 0.03325 | 0.05170 | |

| random forest | 0.026064 | 0.02579 | 0.009126 | |

| runtime (unit: s) | linear | 0.002 | 0.002 | 0.002 |

| k-nearest neighbor | 0.021 | 0.032 | 0.001 | |

| random forest | 0.1 | 0.16 | 0.09 | |

| HSPICE | 16.88 | 3.38 | 228.91 | |

| c499 | c6288 | c7552 | |||

|---|---|---|---|---|---|

| rRMSE (%) | Case 2 | 0.015479 | 0.063536 | 0.008688 | |

| Case 3 | 0.016181 | 0.032483 | 0.014611 | ||

| Case 4 | 0.024792 | 0.027314 | 0.006447 | ||

| MAE (unit: × 10−9 s) | Case 2 | 0.0004844 | 0.0008411 | 0.0003512 | |

| Case 3 | 0.0003159 | 0.0004020 | 0.0004363 | ||

| Case 4 | 0.0005395 | 0.0003656 | 0.0003260 | ||

| runtime (unit: s) | Case 2 | linear | 0.001 | 0.001 | 0.001 |

| HSPICE | 28.34 | 1065.51 | 442.02 | ||

| Case 3 | linear | 0.003 | 0.001 | 0.002 | |

| HSPICE | 27.62 | 920.70 | 400.06 | ||

| Case 4 | linear | 0.002 | 0.002 | 0.001 | |

| HSPICE | 27.59 | 909.23 | 385.02 | ||

| s13207 | s15850 | s38584 | |||

|---|---|---|---|---|---|

| rRMSE (%) | Case 2 | 0.03725 | 0.03547 | 0.02246 | |

| Case 3 | 0.03368 | 0.03840 | 0.04346 | ||

| Case 4 | 0.00294 | 0.02441 | 0.03850 | ||

| MAE (unit: × 10−9 s) | Case 2 | 0.0008536 | 0.0007864 | 0.0005098 | |

| Case 3 | 0.0003525 | 0.0004211 | 0.0007097 | ||

| Case 4 | 0.0003785 | 0.0006108 | 0.0007053 | ||

| runtime (unit: s) | Case 2 | linear | 0.001 | 0.001 | 0.001 |

| HSPICE | 66.12 | 102.43 | 1135.46 | ||

| Case 3 | linear | 0.001 | 0.002 | 0.002 | |

| HSPICE | 65.31 | 98.35 | 1056.31 | ||

| Case 4 | linear | 0.001 | 0.002 | 0.001 | |

| HSPICE | 64.29 | 95.77 | 1018.32 | ||

| b04 | b08 | b16 | |||

|---|---|---|---|---|---|

| rRMSE (%) | Case 2 | 0.00715 | 0.01938 | 0.03235 | |

| Case 3 | 0.01322 | 0.02213 | 0.01684 | ||

| Case 4 | 0.02125 | 0.02653 | 0.03548 | ||

| MAE (unit: × 10−9 s) | Case 2 | 0.0004990 | 0.0003845 | 0.0003645 | |

| Case 3 | 0.0001245 | 0.0003214 | 0.0002923 | ||

| Case 4 | 0.0003025 | 0.0001631 | 0.0000985 | ||

| runtime (unit: s) | Case 2 | linear | 0.001 | 0.001 | 0.002 |

| HSPICE | 59.08 | 9.21 | 849.93 | ||

| Case 3 | linear | 0.001 | 0.001 | 0.001 | |

| HSPICE | 58.15 | 9.15 | 816.03 | ||

| Case 4 | linear | 0.001 | 0.001 | 0.002 | |

| HSPICE | 56.23 | 8.92 | 805.77 | ||

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bu, A.; Li, J. A Learning-Based Framework for Circuit Path Level NBTI Degradation Prediction. Electronics 2020, 9, 1976. https://doi.org/10.3390/electronics9111976

Bu A, Li J. A Learning-Based Framework for Circuit Path Level NBTI Degradation Prediction. Electronics. 2020; 9(11):1976. https://doi.org/10.3390/electronics9111976

Chicago/Turabian StyleBu, Aiguo, and Jie Li. 2020. "A Learning-Based Framework for Circuit Path Level NBTI Degradation Prediction" Electronics 9, no. 11: 1976. https://doi.org/10.3390/electronics9111976

APA StyleBu, A., & Li, J. (2020). A Learning-Based Framework for Circuit Path Level NBTI Degradation Prediction. Electronics, 9(11), 1976. https://doi.org/10.3390/electronics9111976