Performance Analysis and Design Optimization of Parallel-Type Slew-Rate Enhancers for Switched-Capacitor Applications

Abstract

1. Introduction

- Class-AB input pairs employ input devices with a variable bias current which allows for dynamic increase of both OTA transconductance and current capacity following large voltage steps. Class-AB input pairs can be implemented by dynamically controlling the tail current injected into the common source of the input differential pair, or by topological modifications of the input pair based on the flipped-voltage follower [1]. Different strategies have been proposed: (i) charge release synchronized with clock phases [2], (ii) current boosting by sensing input voltage steps [3,4,5,6,7] or (iii) at other OTA’s internal nodes [8,9,10]. However, large impulsive currents in the internal branches do not contribute directly to the current delivered to the output capacitive load and, consequently, represent wasted power; furthermore, the upset caused by large increases of the internal currents may result in a settling penalty due to saturation of sensitive devices [11] or it may even cause trojan states [12].

- Non-linear current steering: this category comprises many families of single-stage OTA topologies that differ about the specific current operations performed by the network that conveys the currents of the input devices to the output port. Generally, all the topologies falling in this category aim to achieve class-AB action on the output branches maintaining the simplicity of the differential pair in the input section. This can be implemented through: (i) non-linear current mirrors [13,14,15,16,17], (ii) transconductor nesting [18,19] or (iii) current recycling [20,21,22,23,24,25,26,27,28,29]. The important feature of such implementations is that the increased output current capability does not involve an increased dc supply power, in contrast with what happens with a static current amplification approach. However, in many of these implementations, the appearance of non-dominant internal singularities makes the optimization difficult for small-to-medium capacitive loads due to phase margin degradation [30].

- RC-tie [31] or quasi-floating gate [32,33] configurations for OTA output branches efficiently provide class-AB action directly on the OTA output branches. They are implemented through a decoupling capacitor across the gates of the respective p-type and n-type transistors statically charged to maintain an adequate bias current through the stacked output devices. Any ac signal coupled to either the NMOS or the PMOS will be transferred to the stack in a push-pull fashion. Globally, the OTA presents a band-pass open loop characteristic which can be tuned to cover the range of frequency of interest.

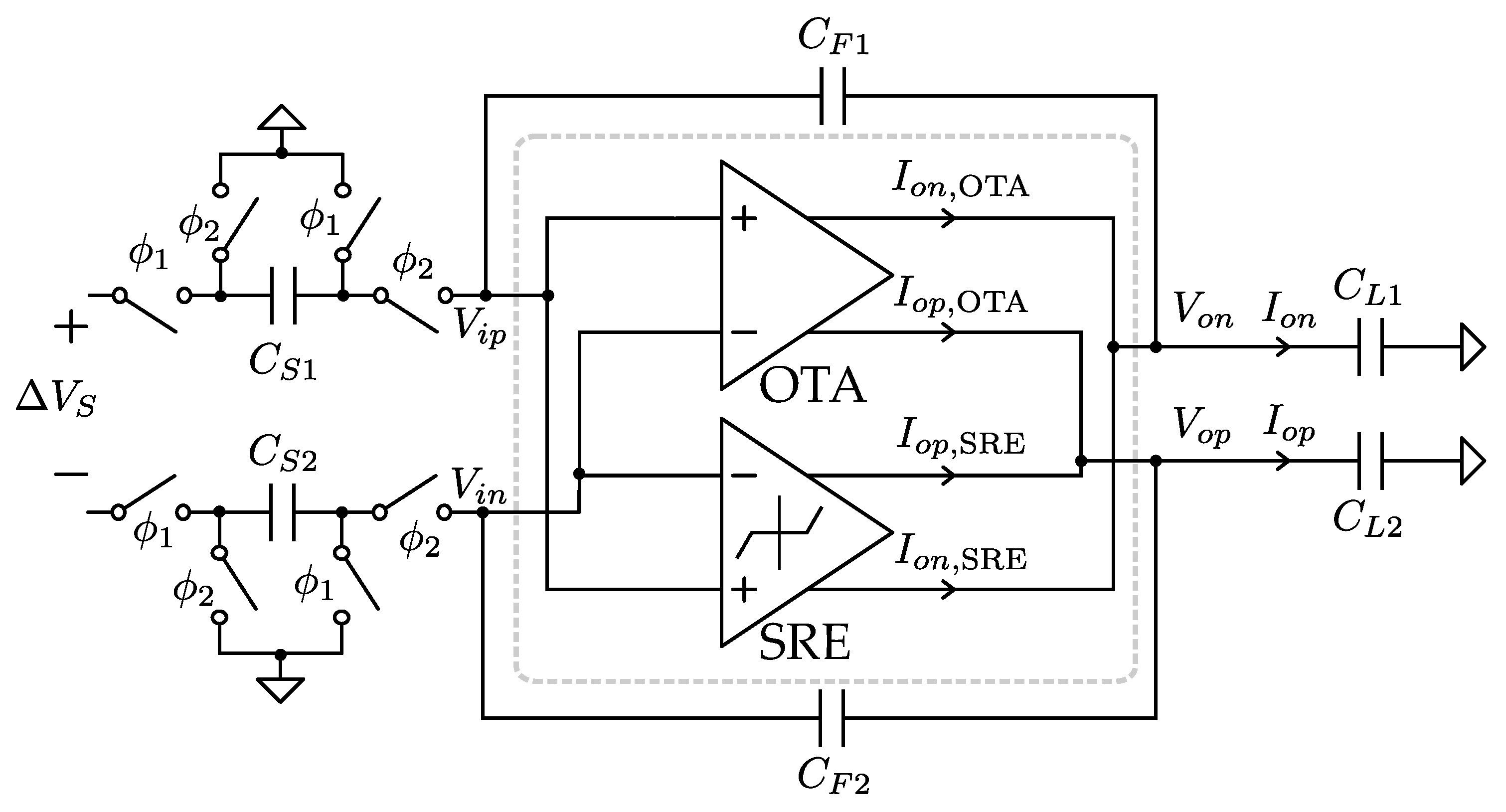

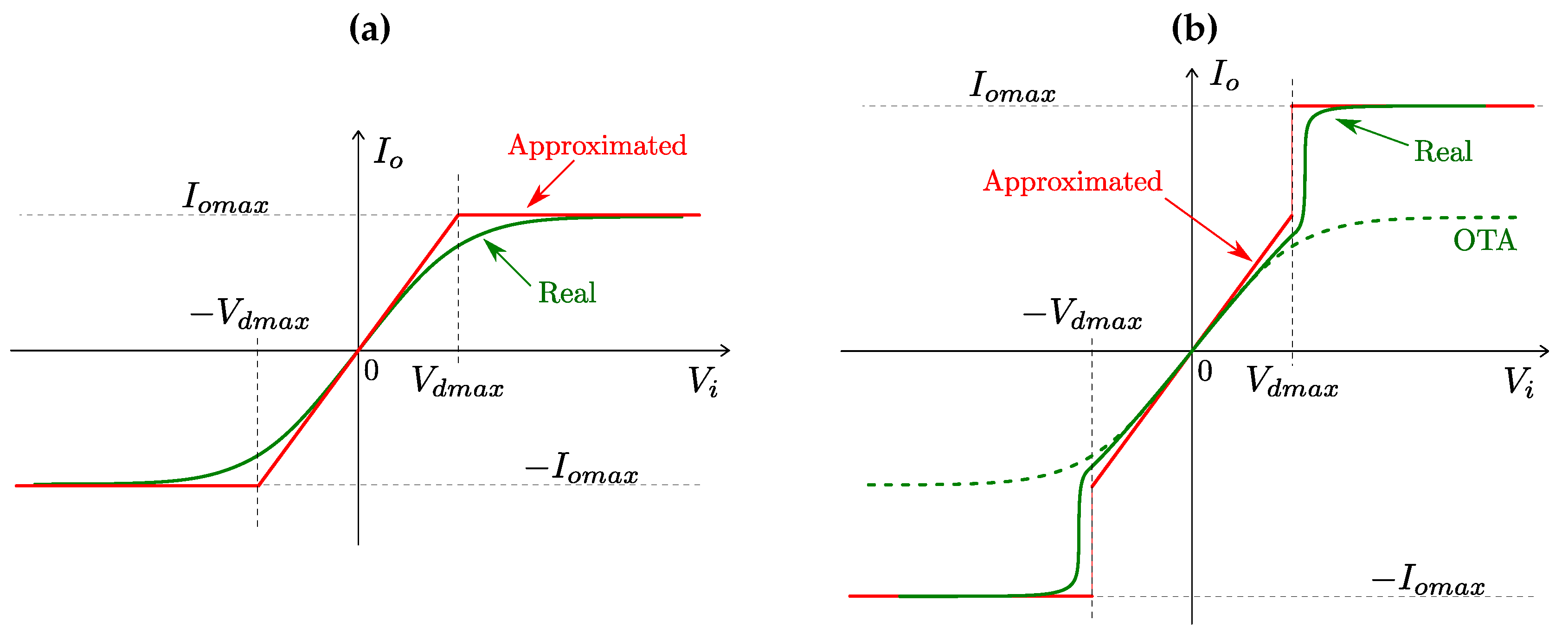

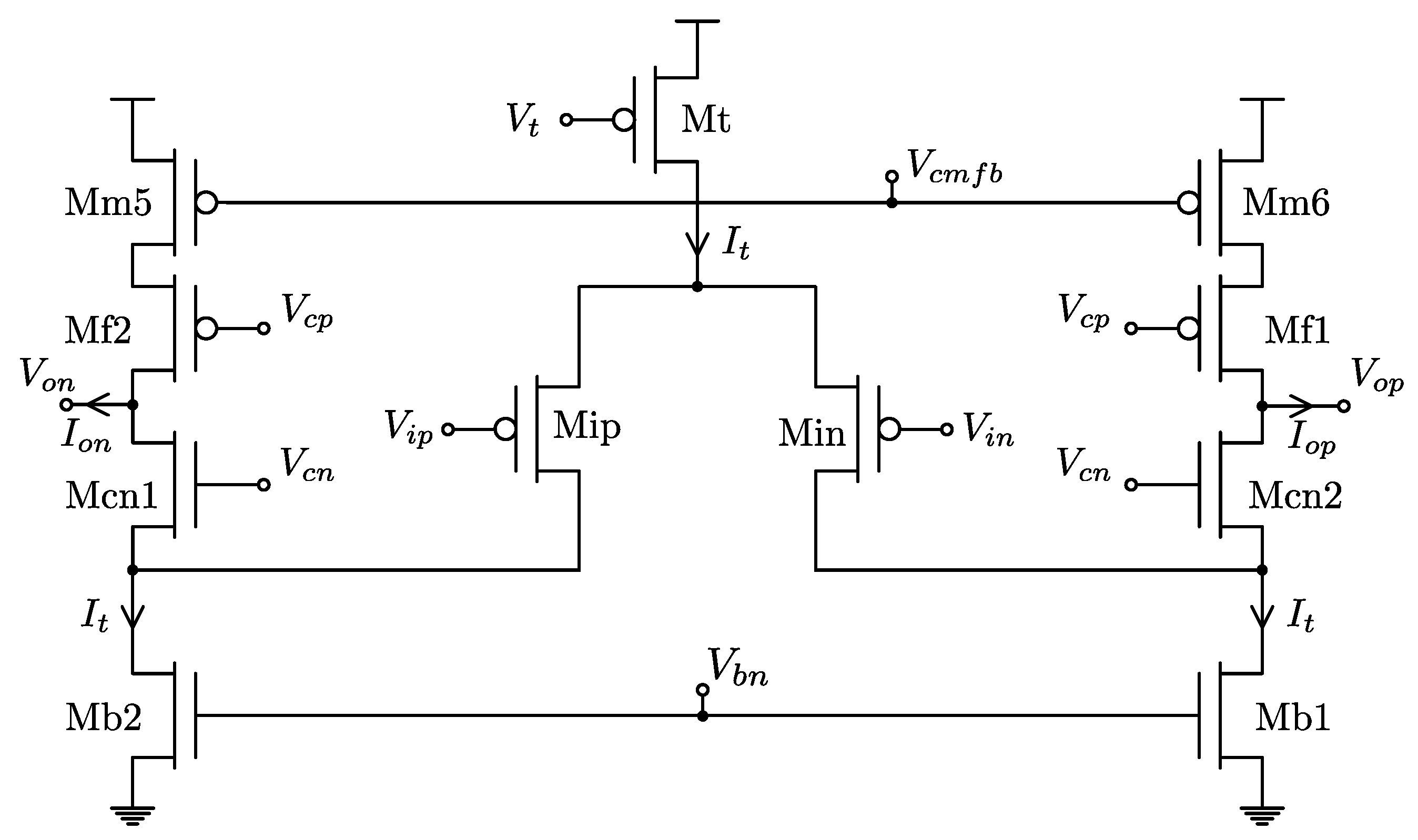

- An auxiliary OTA structure or part of it can be used as slew-rate enhancer (SRE) which aims to add an extra current directly to the output load in parallel with the main OTA current path. In order to achieve low power operation, the auxiliary circuit automatically turns off once the current needed by the load is small. This is fundamental in single-stage architectures where the main OTA provides gain through its high-impedance output nodes. Any gain loss due to the presence of parallel branches in the output nodes would cause precision loss at the end of the operation time. This can be avoided by forcing the cut-off state of the auxiliary SRE. This technique is of general use and can be extended also to multi-stage OTA configurations [34,35]. Auxiliary SRE implementations contemplate main-OTA internal-node sensing [36,37,38,39,40,41], or direct sensing of the OTA inputs (parallel-type SRE) [42,43,44]. In the latter case, a complete OTA/SRE system is used as shown in Figure 1. A totally passive, OTA-free SRE technique has been recently proposed for modulators [45].

2. OTA-Assisted Charge Transfer Process

2.1. The Switched-Capacitors Stage

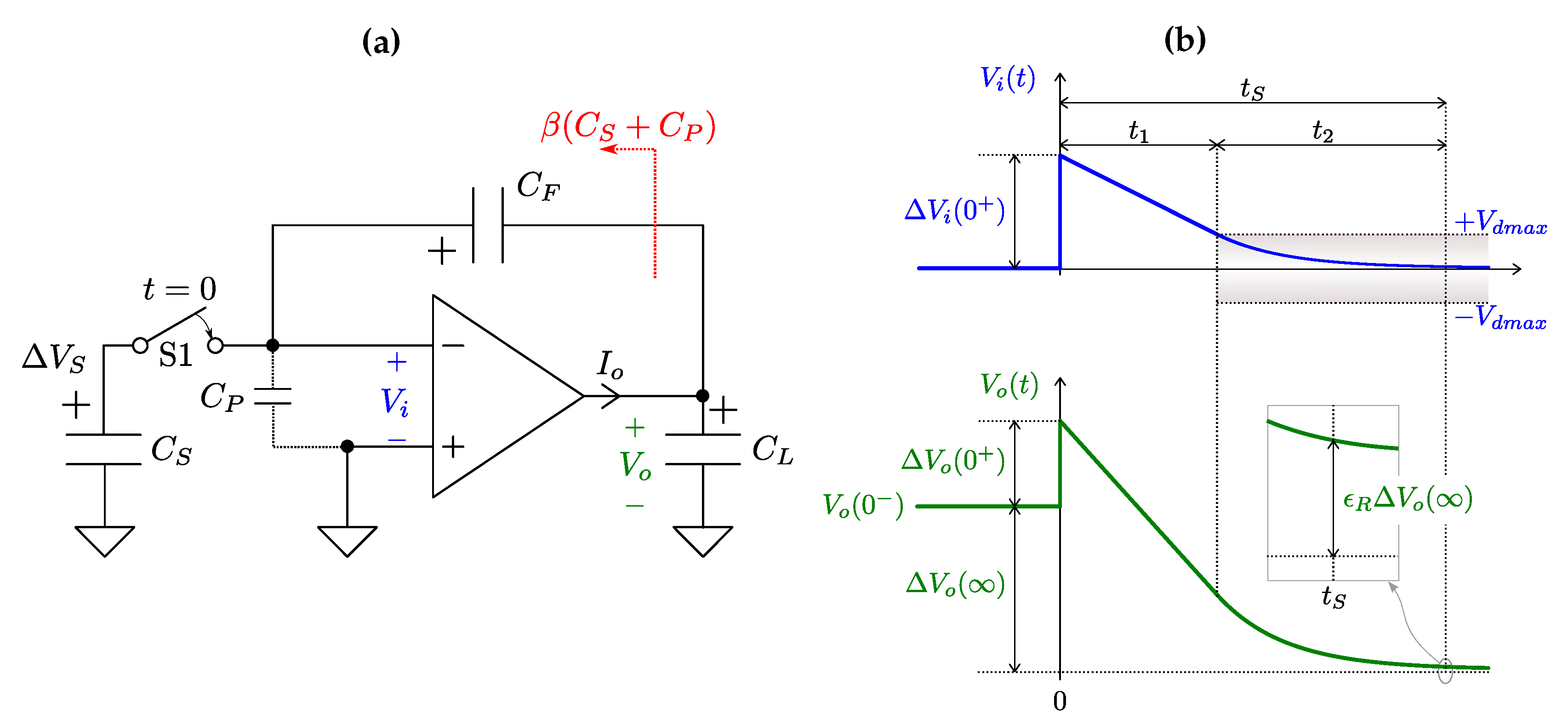

2.2. Simplified Model of Charge Transfer Transient

- , : both parameters descend from system-level specifications. The former contains: (i) which is strictly related to (see Equation (2)) and thus to kT/C-noise specifications, (ii) , which is the maximum stimulus that can be applied to the circuit (may approach the supply voltage in SC ADCs) and (iii) , which is determined by the power budget. On the other hand, can be related to precision, linearity and maximum tolerable harmonic distortion, depending on the application of the SC amplifier/integrator.

- and : both parameters mainly depend on the capacitive feedback network (, ) and on the load . The ratio is determined at system level to achieve the desired gain or integrator coefficient, through Equation (3). The contribution of the input capacitance to the coefficients and may be significant when input devices with large gate area are chosen to minimize the offset voltage and the flicker noise and/or particularly small values are chosen for , and to enable fast clock frequencies.

- and express the efficiency by which the OTA uses the given supply current to produce large output currents and large transconductances, respectively.

- is composed by a specification (), dictated by the application, and by , which is a real degree of freedom that characterizes the design of the OTA.

3. Slew-Rate Enhancer Design

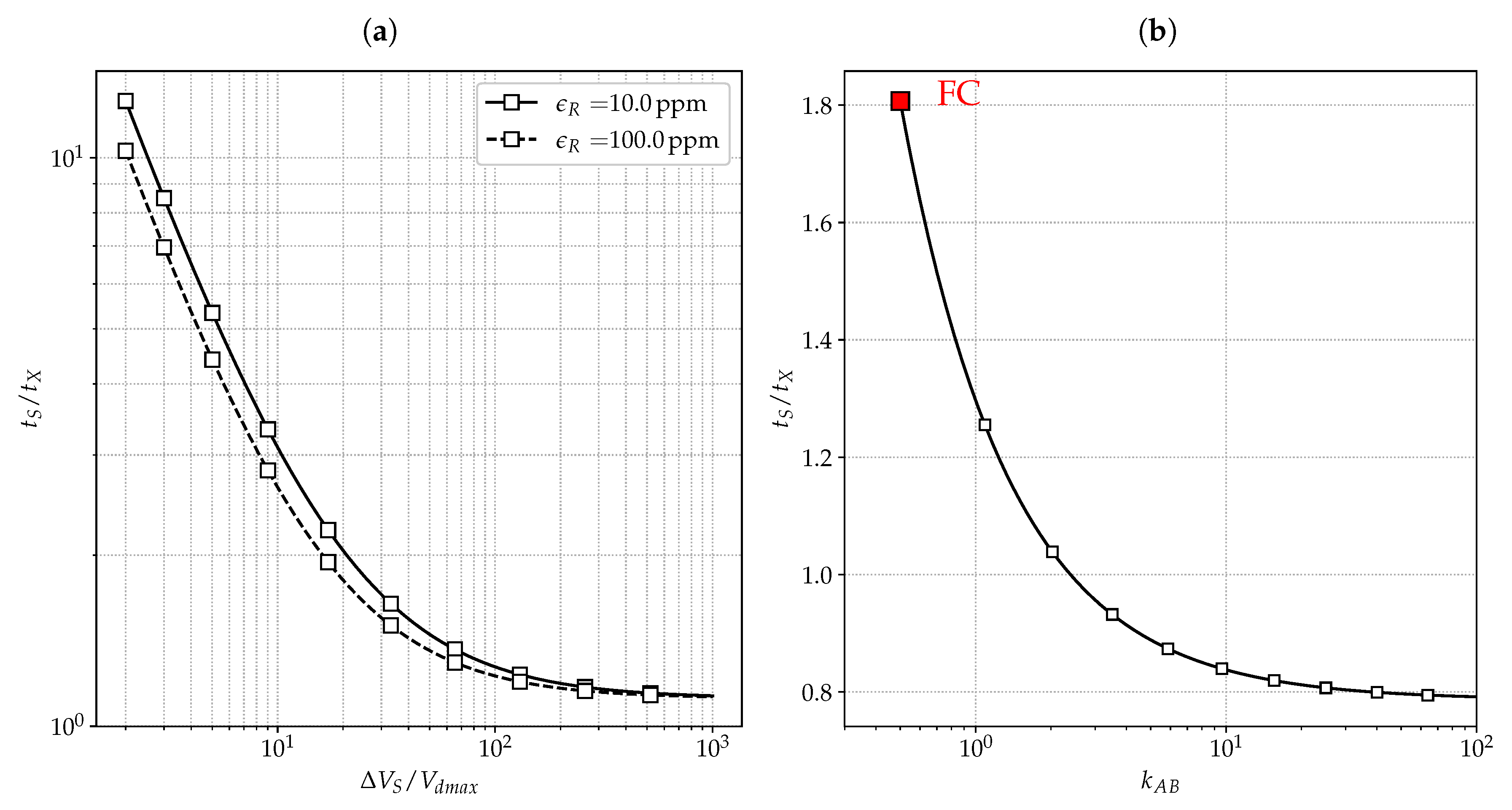

3.1. Ideal Behaviour and Static Power Overhead of Parallel-Type SRE

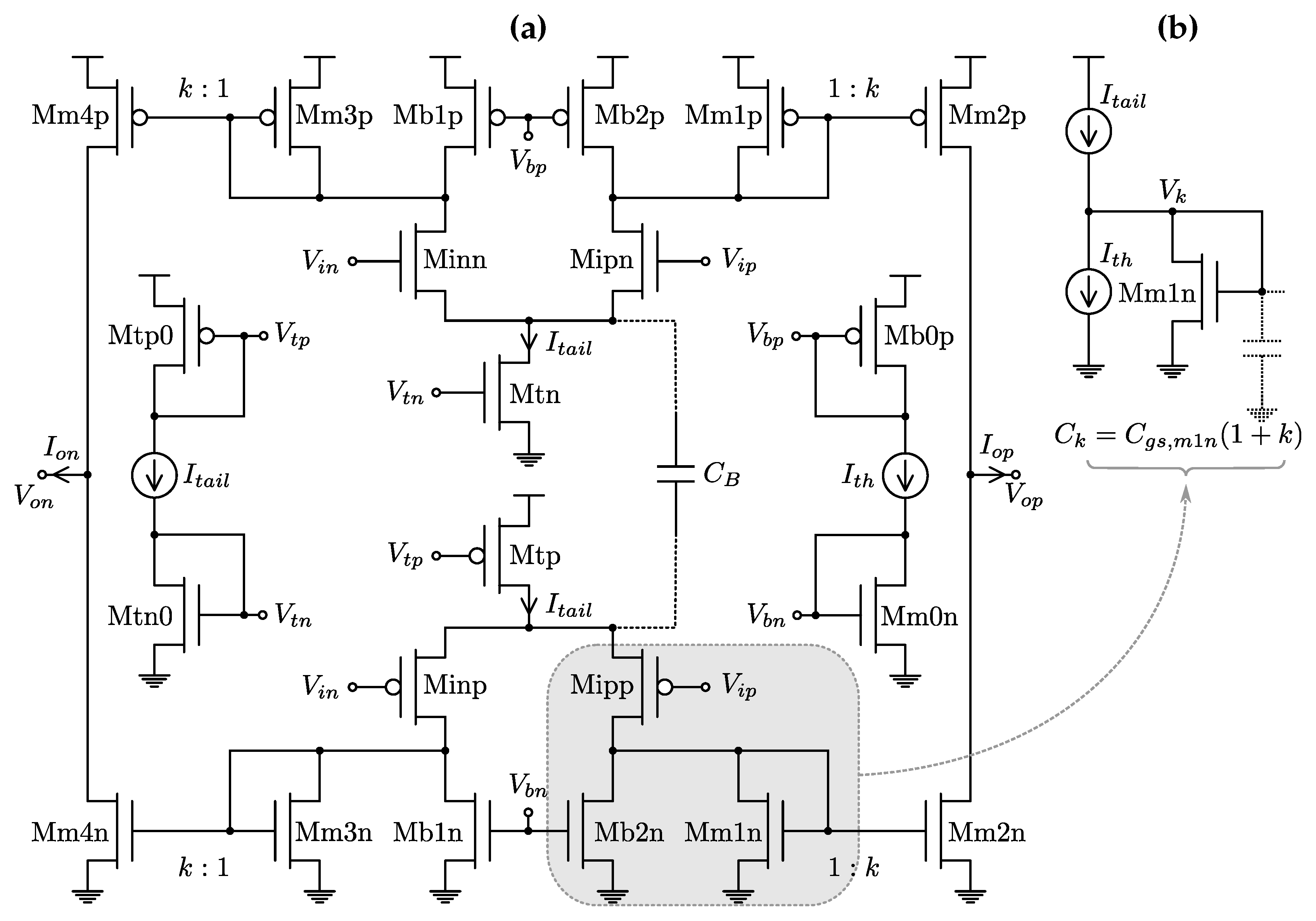

3.2. Nagaraj’s SRE

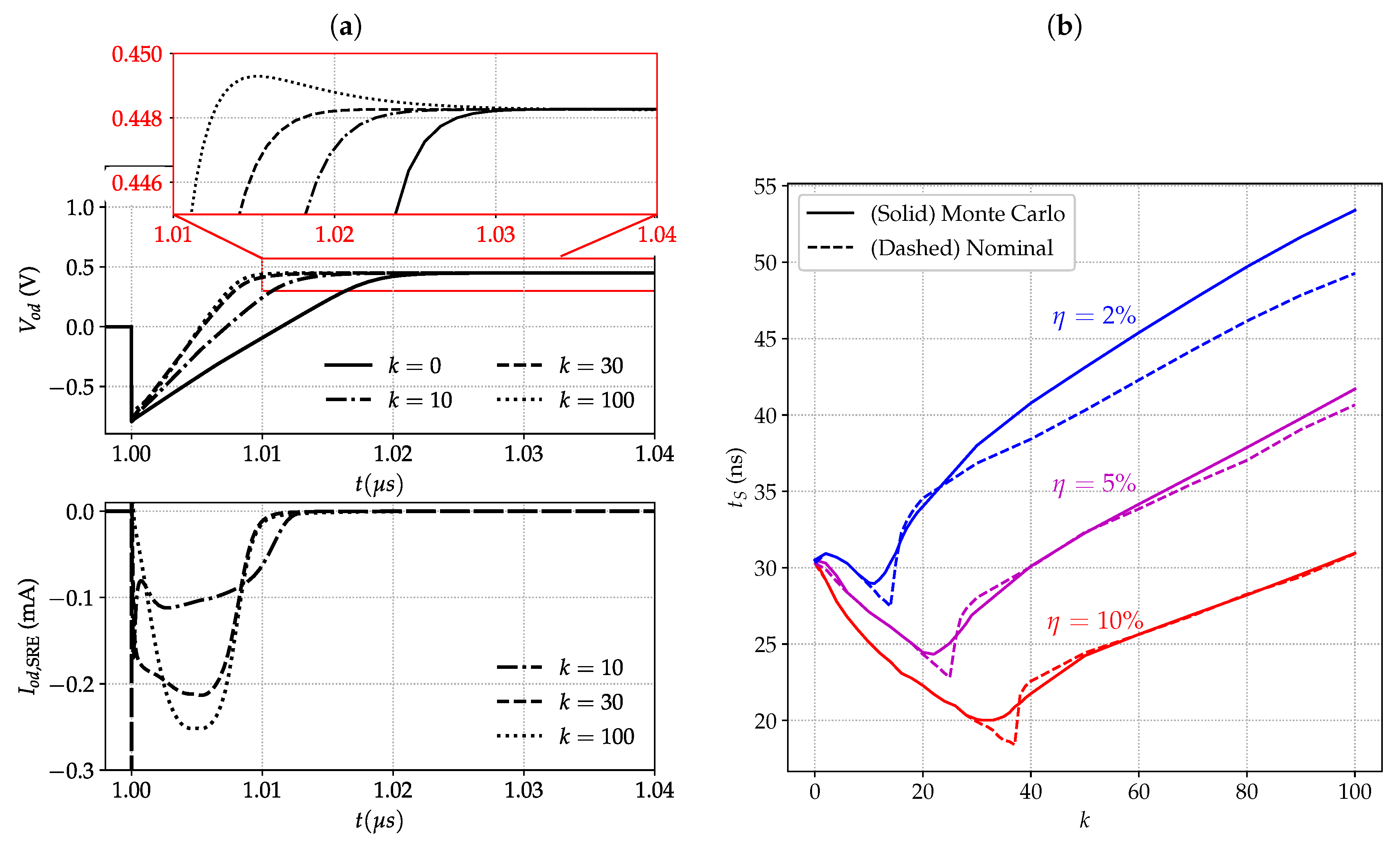

3.3. SRE Simulations and Turn-On/Off Effects

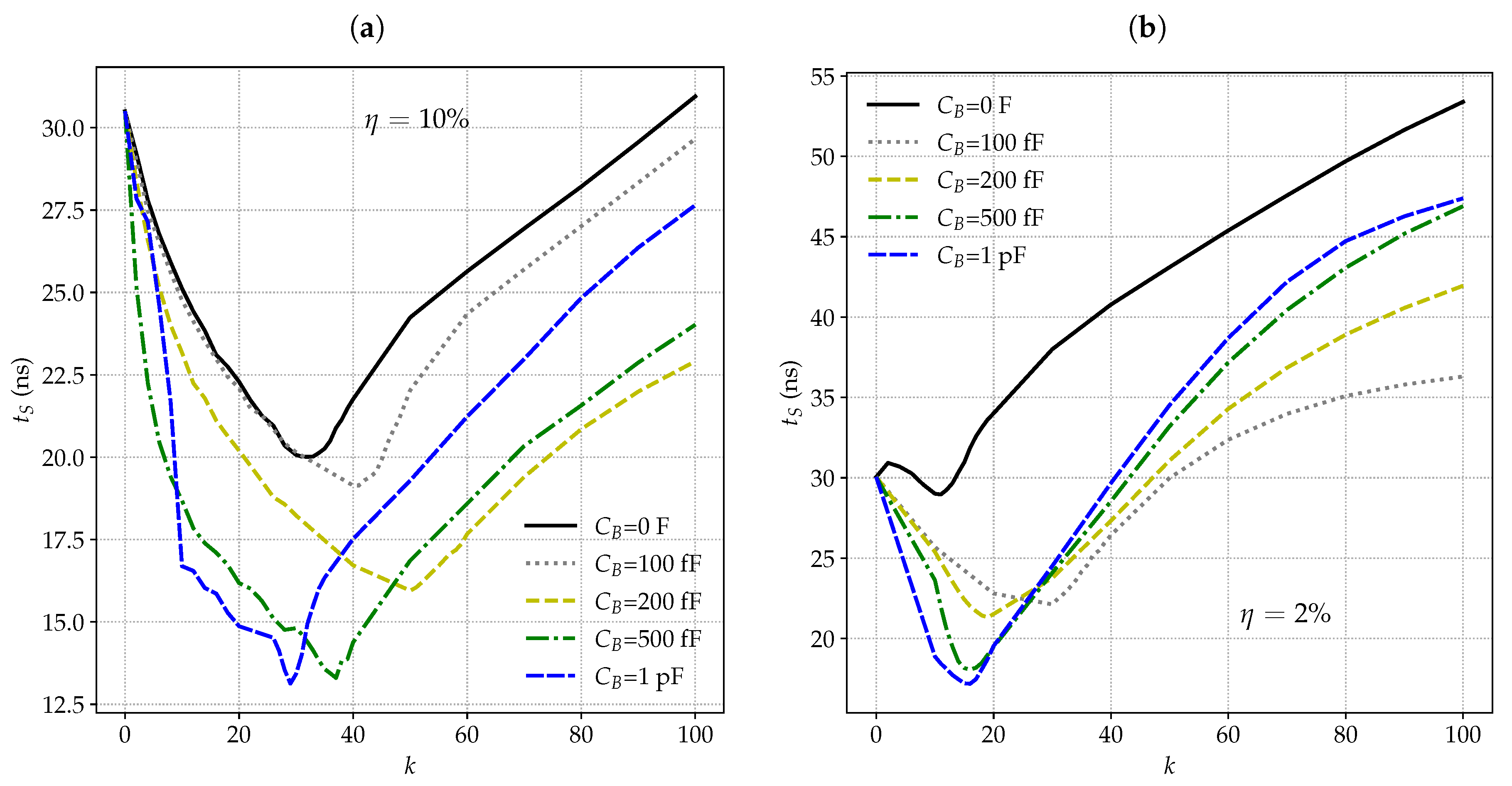

3.4. Capacitive-Boosted Nagaraj’s SRE

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Carvajal, R.G.; Ramirez-Angulo, J.; Lopez-Martin, A.J.; Torralba, A.; Galan, J.A.G.; Carlosena, A.; Chavero, F.M. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Hosticka, B.J. Dynamic CMOS amplifiers. IEEE J. Solid-State Circuits 1980, 15, 881–886. [Google Scholar] [CrossRef]

- Peluso, V.; Vancorenland, P.; Steyaert, M.; Sansen, W. 900 mV differential class AB OTA for switched opamp applications. Electron. Lett. 1997, 33, 1455–1456. [Google Scholar] [CrossRef]

- Harjani, R.; Heineke, R.; Wang, F. An integrated low-voltage class AB CMOS OTA. IEEE J. Solid-State Circuits 1999, 34, 134–142. [Google Scholar] [CrossRef]

- Bernal, M.R.V.; Celma, S.; Medrano, N.; Calvo, B. An Ultralow-Power Low-Voltage Class-AB Fully Differential OpAmp for Long-Life Autonomous Portable Equipment. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 643–647. [Google Scholar] [CrossRef]

- Vi, S.; Gupta, A.; Mittal, A. An Operational Amplifier with Recycling Folded Cascode Topology and Adaptive Biasing. Int. J. VLSI Des. Commun. Syst. 2014, 5. [Google Scholar] [CrossRef]

- Akbari, M.; Hashemipour, O.; Moradi, F. A High Slew Rate CMOS OTA with Dynamic Current Boosting Paths. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Degrauwe, M.G.; Rijmenants, J.; Vittoz, E.A.; Man, H.J.D. Adaptive biasing CMOS amplifiers. IEEE J. Solid-State Circuits 1982, 17, 522–528. [Google Scholar] [CrossRef]

- Huang, B.; Xu, L.; Chen, D. Slew rate enhancement via excessive transient feedback. Electron. Lett. 2013, 49, 930–932. [Google Scholar] [CrossRef]

- Hung, C.H.; Zheng, Y.; Guo, J.; Leung, K.N. Bandwidth and Slew Rate Enhanced OTA with Sustainable Dynamic Bias. IEEE Trans. Circuits Syst. II: Express Briefs 2020, 67, 635–639. [Google Scholar] [CrossRef]

- Nizza, N.; Mondini, A.; Bruschi, P. A current feedback adaptive biasing method for class-AB OTA cells. In Proceedings of the PRIME 2005, Lausanne, Switzerland, 28 July 2005; pp. 390–393. [Google Scholar]

- Cai, C.; Chen, D. A slew-rate enhancement technique for fully differential amplifier without inducing Trojan state. In Proceedings of the 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), Fort Collins, CO, USA, 2–5 August 2015; pp. 1–4. [Google Scholar]

- Ramirez-Angulo, J. A novel slew-rate enhancement technique for one-stage operational amplifiers. In Proceedings of the 39th Midwest Symposium on Circuits and Systems, Ames, IA, USA, 21–21 August 1996; Volume 1, pp. 7–10. [Google Scholar]

- Lopez-Martin, A.J.; Baswa, S.; Ramirez-Angulo, J.; Carvajal, R.G. Low-Voltage Super class AB CMOS OTA cells with very high slew rate and power efficiency. IEEE J. Solid-State Circuits 2005, 40, 1068–1077. [Google Scholar] [CrossRef]

- Galan, J.A.; Lopez-Martin, A.J.; Carvajal, R.G.; Ramirez-Angulo, J.; Rubia-Marcos, C. Super Class-AB OTAs With Adaptive Biasing and Dynamic Output Current Scaling. IEEE Trans. Circuits Syst. Regul. Pap. 2007, 54, 449–457. [Google Scholar] [CrossRef]

- Wan, X.P.; Zhang, F.X.; Zhen, S.W.; He, Y.J.; Luo, P. Efficient slew-rate enhanced operational transconductance amplifier. J. Electron. Sci. Technol. 2015, 13, 14–19. [Google Scholar]

- Sutula, S.; Dei, M.; Terés, L.; Serra-Graells, F. Variable-Mirror Amplifier: A New Family of Process-Independent Class-AB Single-Stage OTAs for Low-Power SC Circuits. IEEE Trans. Circuits Syst. Regul. Pap. 2016, 63, 1101–1110. [Google Scholar] [CrossRef]

- Yan, Z.; Mak, P.; Law, M.; Martins, R.P.; Maloberti, F. Nested-Current-Mirror Rail-to-Rail-Output Single-Stage Amplifier With Enhancements of DC Gain, GBW and Slew Rate. IEEE J. Solid-State Circuits 2015, 50, 2353–2366. [Google Scholar] [CrossRef]

- Lee, J.; Song, S.; Roh, J. A 103 dB DR Fourth-Order Delta-Sigma Modulator for Sensor Applications. Electronics 2019, 8, 1093. [Google Scholar] [CrossRef]

- Roh, J. High-Gain Class-AB OTA with Low Quiescent Current. Analog. Integr. Circuits Signal Process. 2006, 47, 225–228. [Google Scholar] [CrossRef]

- Assaad, R.S.; Silva-Martinez, J. The Recycling Folded Cascode: A General Enhancement of the Folded Cascode Amplifier. IEEE J. Solid-State Circuits 2009, 44, 2535–2542. [Google Scholar] [CrossRef]

- Li, Y.L.; Han, K.F.; Tan, X.; Yan, N.; Min, H. Transconductance enhancement method for operational transconductance amplifiers. Electron. Lett. 2010, 46, 1321–1323. [Google Scholar]

- Yavari, M. Single-Stage Class AB Operational Amplifier for SC Circuits. Electron. Lett. 2010, 46, 977–979. [Google Scholar] [CrossRef]

- Zhao, X.; Fang, H.; Xu, J. A new low power symmetric folded cascode amplifier by recycling current in 65 nm CMOS technology. In Proceedings of the 9th IEEE International Conference on ASIC, Xiamen, China, 25–28 October 2011; pp. 820–823. [Google Scholar]

- Akbari, M. Single-stage fully recycling folded cascode OTA for switched-capacitor circuits. Electron. Lett. 2015, 51, 977–979. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.J.; Carvajal, R.G.; Galan, J.A.; Ramirez-Angulo, J. Super class AB RFC OTA using non-linear current mirrors. Electron. Lett. 2018, 54, 1317–1318. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.J.; Carvajal, R.G.; Ramirez-Angulo, J. Super class AB RFC OTA with adaptive local common-mode feedback. Electron. Lett. 2018, 54, 1272–1274. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.; Carvajal, R.G.; Ramrez-Angulo, J. Super Class-AB Recycling Folded Cascode OTA. IEEE J. Solid-State Circuits 2018, 53, 2614–2623. [Google Scholar] [CrossRef]

- Wang, Y.; Zhang, Q.; Yu, S.S.; Zhao, X.; Trinh, H.; Shi, P. A Robust Local Positive Feedback Based Performance Enhancement Strategy for Non-Recycling Folded Cascode OTA. IEEE Trans. Circuits Syst. Regul. Pap. 2020, 67, 2897–2908. [Google Scholar] [CrossRef]

- Cisneros-Fernández, J.; Terés, L.; Dei, M.; Serra-Graells, F. Design methodology for power-efficient SC delta-sigma modulators based on switched-VMAs. In Proceedings of the 2017 32nd Conference on Design of Circuits and Integrated Systems (DCIS), Barcelona, Spain, 22–24 November 2017; pp. 1–6. [Google Scholar]

- Silva-Martinez, J.; Yan, T.; Jiang, J.; Shao, J. Efficient Broadband Class AB Amplifier. In Proceedings of the 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Dallas, TX, USA, 4–7 August 2019; pp. 1045–1048. [Google Scholar]

- Algueta-Miguel, J.M.; Lopez-Martin, A.; Garde, M.P.; De, C.A. La Cruz and J. Ramirez-Angulo, ±0.5 V 15 μW Recycling Folded Cascode Amplifier With 34,767 MHz·pF/mA FOM. IEEE Solid State Circuits Lett. 2018, 1, 170–173. [Google Scholar] [CrossRef]

- Garde, M.P.; Lopez-Martin, A.; Algueta, J.M.; Carvajal, R.G.; Ramirez-Angulo, J. Class AB amplifier with enhanced slew rate and GBW. Int. J. Circ. Theor. Appl. 2019, 47, 1199–1210. [Google Scholar] [CrossRef]

- Perez, A.P.; Kumar, Y.B.N.; Bonizzoni, E.; Maloberti, F. Slew-rate and gain enhancement in two stage operational amplifiers. In Proceedings of the 2009 IEEE International Symposium on Circuits and Systems (ISCAS), Taipei, Taiwan, 24–27 May 2009; pp. 2485–2488. [Google Scholar]

- Naderi, M.H.; Prakash, S.; Silva-Martinez, J. Operational Transconductance Amplifier With Class-B Slew-Rate Boosting for Fast High-Performance Switched-Capacitor Circuits. IEEE Trans. Circuits Syst. Regul. Pap. 2018, 65, 3769–3779. [Google Scholar] [CrossRef]

- Lee, H.; Mok, P.K.T. A CMOS current-mirror amplifier with compact slew rate enhancement circuit for large capacitive load applications. In Proceedings of the The 2001 IEEE International Symposium on Circuits and Systems, Sydney, NSW, Australia, 6–9 May 2001; Volume 1, pp. 220–223. [Google Scholar]

- Lee, H.; Mok, P.K.T. Single-point-detection slew-rate enhancement circuits for single-stage amplifiers. In Proceedings of the 2002 IEEE International Symposium on Circuits and Systems, Proceedings (Cat. No.02CH37353), Phoenix-Scottsdale, AZ, USA, 26–29 May 2002. [Google Scholar]

- Rezaei, M.; Zhian-Tabasy, E.; Ashtiani, S.J. Slew rate enhancement method for folded-cascode amplifiers. Electron. Lett. 2008, 44, 1226–1228. [Google Scholar] [CrossRef]

- Leung, K.; Ng, Y. A CMOS voltage buffer with slew-rate enhancement. Int. J. Electron. 2013, 101, 820–830. [Google Scholar] [CrossRef]

- Bu, S.; Tse, H.W.; Leung, K.N.; Guo, J.; Ho, M. Gain and slew rate enhancement for amplifiers through current starving and feeding. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 2073–2076. [Google Scholar]

- Akbari, M.; Hassanzadeh, A.; Hashemipour, O. Slew rate boosting technique for an upgraded transconductance amplifier. Analog. Integr. Circuits Signal Process. 2016, 88, 57–63. [Google Scholar] [CrossRef]

- Nagaraj, K. Slew rate enhancement method for folded-cascode amplifiers. Electron. Lett. 1989, 25, 1226–1228. [Google Scholar]

- Nagaraj, K. CMOS amplifiers incorporating a novel slew rate enhancement technique. In Proceedings of the IEEE Proceedings of the Custom Integrated Circuits Conference, Boston, MA, USA, 13–16 May 1990; pp. 11.6/1–11.6/5. [Google Scholar]

- Tan, C.; Chen, Z. An efficient CMOS operational amplifier for driving large capacitive loads. In Proceedings of the 2007 7th International Conference on ASIC, Guilin, China, 22–25 October 2007; pp. 643–646. [Google Scholar]

- Kareppagoudr, M.; Caceres, E.; Kuo, Y.; Shakya, J.; Wang, Y.; Temes, G.C. Passive slew rate enhancement technique for Switched-Capacitor Circuits. In Proceedings of the 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), Dallas, TX, USA, 4–7 August 2019; pp. 913–916. [Google Scholar]

- Haug, K.; Maloberti, F.; Temes, G.C. Switched-capacitor integrators with low finite-gain sensitivity. Electron. Lett. 1985, 21, 1156–1157. [Google Scholar] [CrossRef]

- Martin, K.; Ozcolak, L.; Lee, Y.S.; Temes, G.C. A differential switched-capacitor amplifier. IEEE J. Solid-State Circuits 1987, 22, 104–106. [Google Scholar] [CrossRef]

- Martin, K.; Sedra, A.S. Strays-insensitive switched-capacitor filters based on bilinear Z-transform. Electron. Lett. 1979, 15, 365–366. [Google Scholar] [CrossRef]

- del Rio, R.; Medeiro, F.; Perez-Verdu, B.; Rodriguez-Vazquez, A. Reliable analysis of settling errors in SC integrators-application to the design of high-speed ΣΔ modulators. In Proceedings of the 2000 IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, 28–31 May 2000; Volume 4, pp. 417–420. [Google Scholar]

- Nairn, D.G. Analytic Step Response of MOS Current Mirrors. IEEE Trans. Circuits Syst. Fundam. Theory Appl. 1993, 40, 133–135. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Catania, A.; Cicalini, M.; Dei, M.; Piotto, M.; Bruschi, P. Performance Analysis and Design Optimization of Parallel-Type Slew-Rate Enhancers for Switched-Capacitor Applications. Electronics 2020, 9, 1949. https://doi.org/10.3390/electronics9111949

Catania A, Cicalini M, Dei M, Piotto M, Bruschi P. Performance Analysis and Design Optimization of Parallel-Type Slew-Rate Enhancers for Switched-Capacitor Applications. Electronics. 2020; 9(11):1949. https://doi.org/10.3390/electronics9111949

Chicago/Turabian StyleCatania, Alessandro, Mattia Cicalini, Michele Dei, Massimo Piotto, and Paolo Bruschi. 2020. "Performance Analysis and Design Optimization of Parallel-Type Slew-Rate Enhancers for Switched-Capacitor Applications" Electronics 9, no. 11: 1949. https://doi.org/10.3390/electronics9111949

APA StyleCatania, A., Cicalini, M., Dei, M., Piotto, M., & Bruschi, P. (2020). Performance Analysis and Design Optimization of Parallel-Type Slew-Rate Enhancers for Switched-Capacitor Applications. Electronics, 9(11), 1949. https://doi.org/10.3390/electronics9111949