An Ultra-Low Quiescent Current Under-Voltage Lockout Circuit for a High-Voltage Gate Driver IC

Abstract

1. Introduction

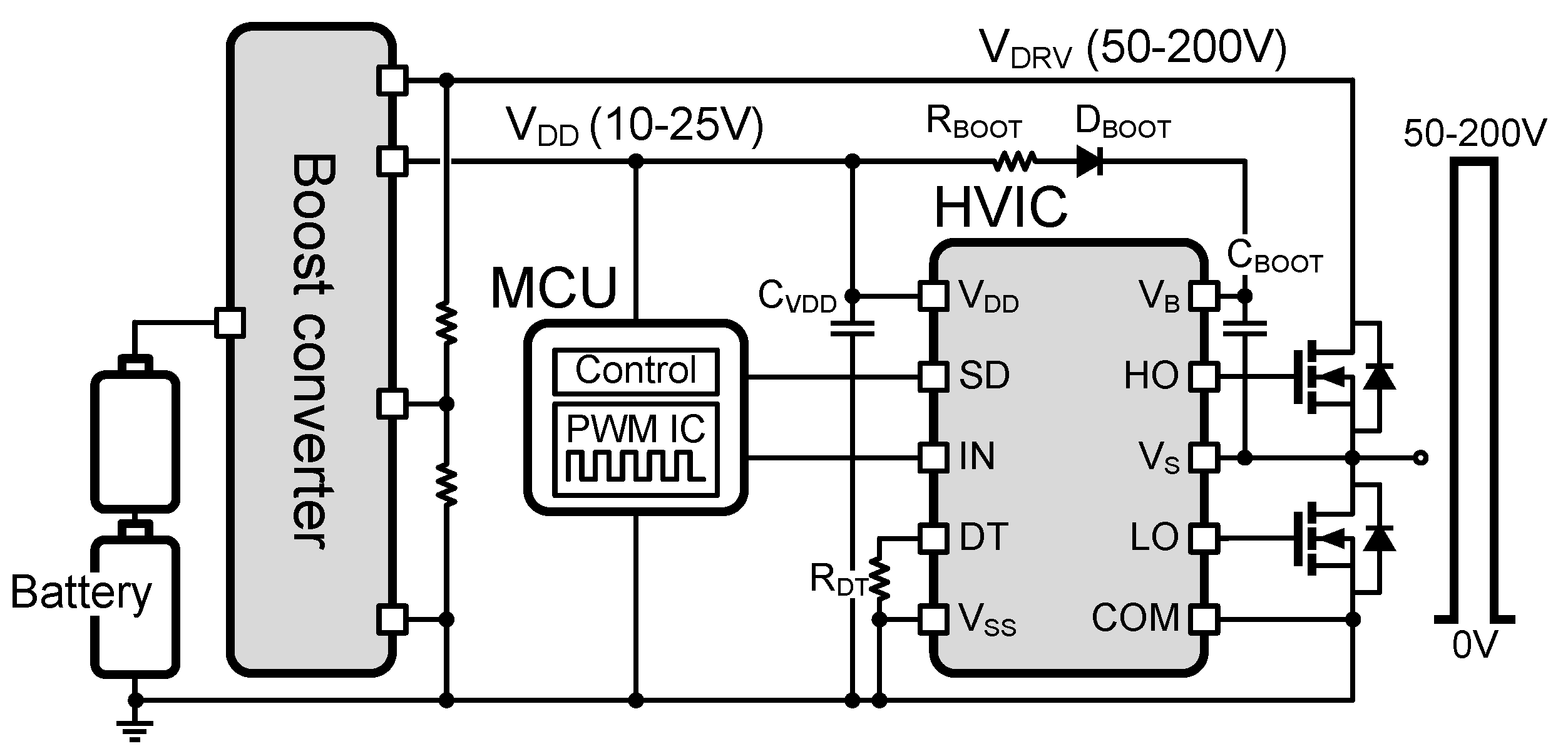

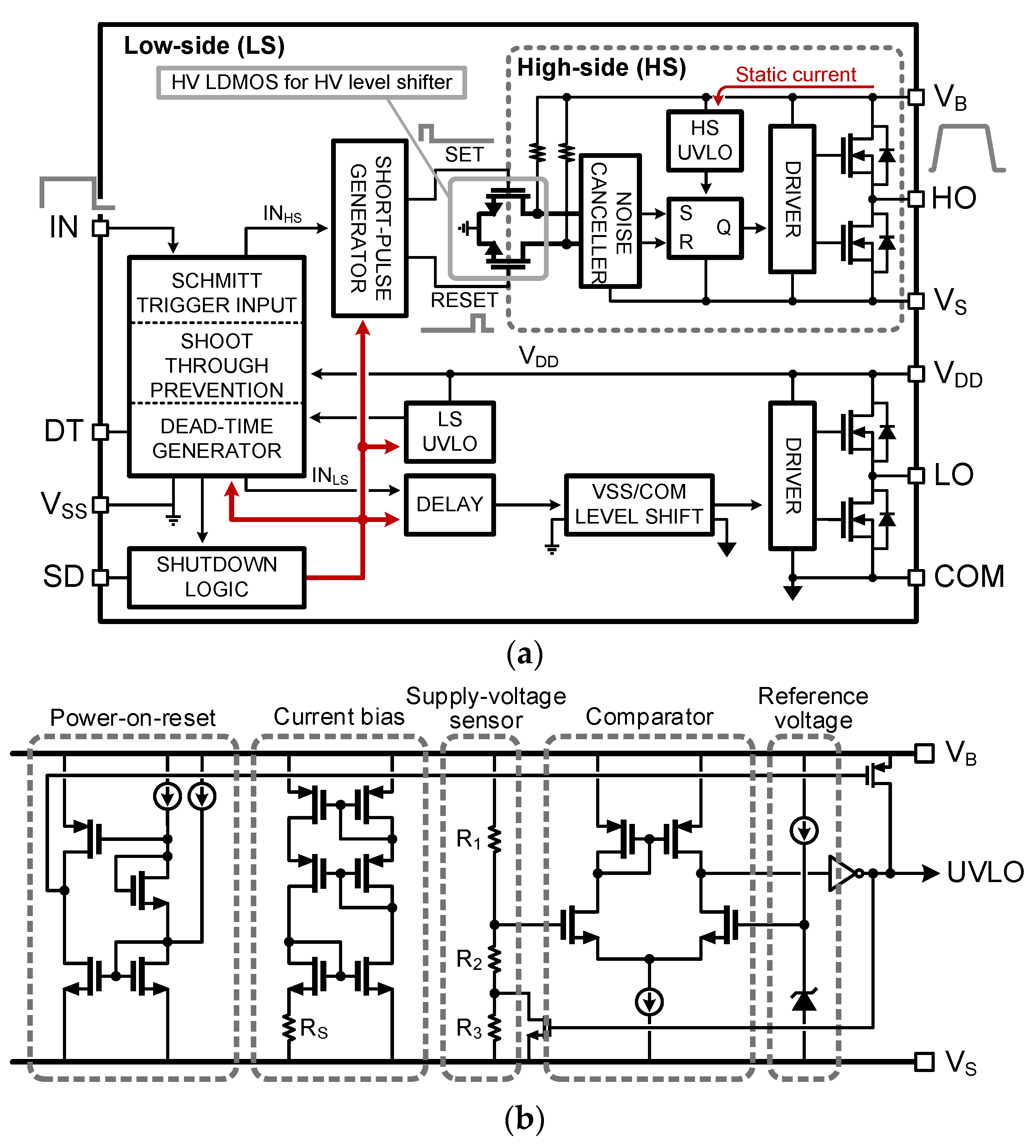

2. High-Voltage Gate Driver IC

2.1. Architecture

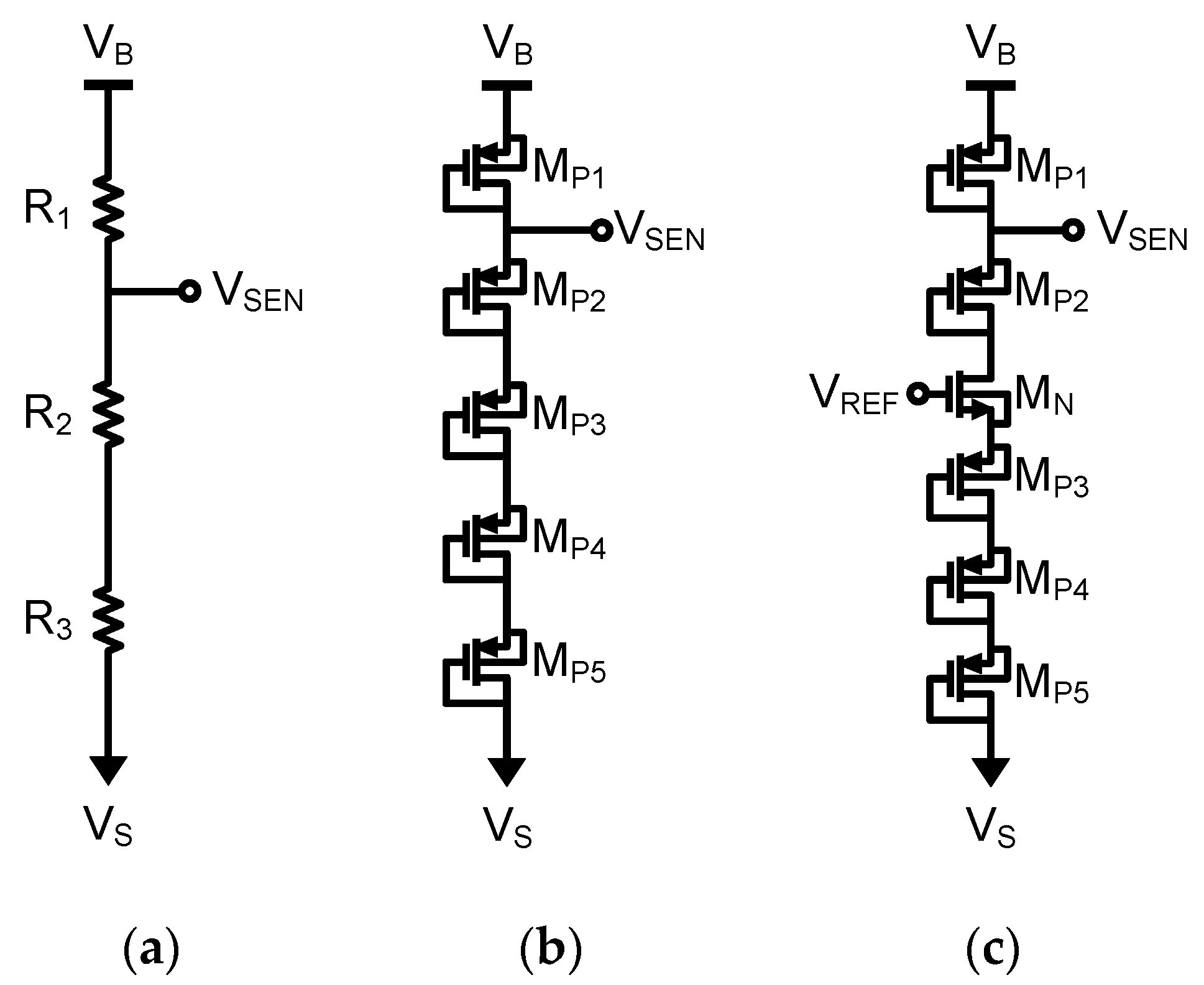

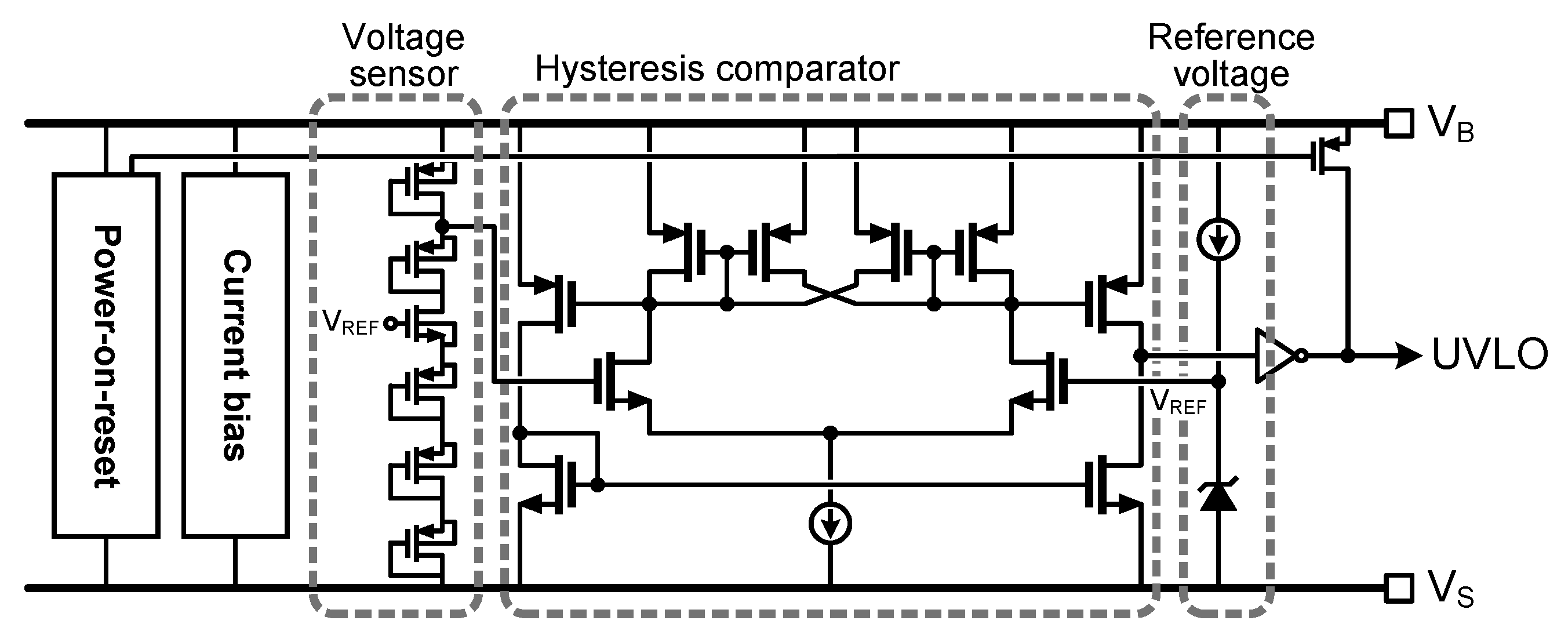

2.2. Under-Voltage Lockout Circuit

3. Low-Quiescent Current High-Side UVLO

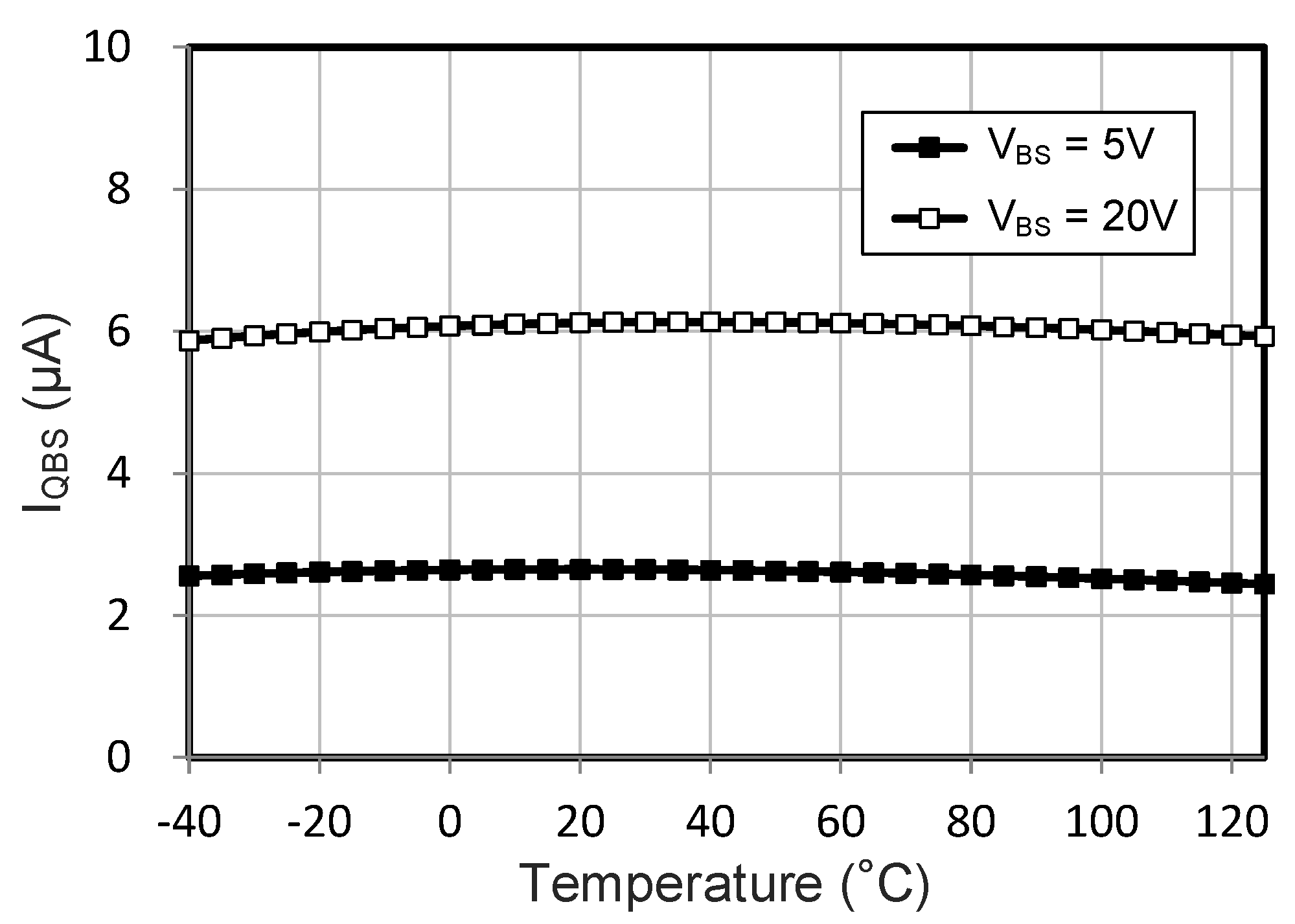

4. Simulation Results

5. Conclusions

Funding

Acknowledgments

Conflicts of Interest

References

- Yamaji, M.; Jonishi, A.; Tanaka, T.; Sumida, H.; Hashimoto, Y. A 600 V High-Voltage IC Technique With a New Self-Shielding Structure for High Noise Tolerance and Die Shrink. IEEE Trans. Electron Devices 2015, 62, 1524–1529. [Google Scholar] [CrossRef]

- Yunwu, Z.; Jing, Z.; Guodong, S.; Cuichun, L.; Weifeng, S.; Qinsong, Q. A noise immunity improved level shift structure for a 600 V HVIC. J. Semicond. 2013, 34, 065008. [Google Scholar]

- Zhu, J.; Sun, G.; Sun, W.; Zhang, Y. Negative voltage surge resistant circuit design in HVIC. IET Electron. Lett. 2013, 49, 1476–1477. [Google Scholar] [CrossRef]

- Cho, K.; Lee, S.; Kwon, D. A high voltage half bridge gate driver with mismatch-insensitive dead-time generator. IEICE Electron. Express 2012, 9, 1322–1328. [Google Scholar] [CrossRef][Green Version]

- 625V, 3.3/5V input logic compatible, 2.5/2.5A sink/source current, half bridge gate-drive IC with variable DT control and SD protection. FAN7393A datasheet, ON Semiconductor, July 2012.

- 600 V half-bridge gate driver IC with shutdown. IR2184 datasheet, Infineon, April 2006.

- 600 V half-Bridge MOSFET or IGBT driver. MIC4608 datasheet, Microchip, 2015.

- Guo, W.; Lin, T.; Lei, L.; Du, S.; Ma, Q.J.; Zhu, Y. Under voltage lockout circuit design for enhanced GaN HEMT drive. In Proceedings of the EITCE, Xiamen, China, 18–20 October 2019; pp. 671–675. [Google Scholar]

- Choi, J.; Oh, W.; Song, K.; Shin, S. Advanced functionality of HVIC technology for intelligent power module. In Proceedings of the PCIM Europe, Nuremberg, Germany, 5–7 June 2018; pp. 1–4. [Google Scholar]

- Lee, S.; Cho, K.; Lee, M.; Jin, W. A leakage reduced HVIC with coarse-fine UVLO. In Proceedings of the IEEE International SoC Design Conference (ISOCC), Jeju Island, Korea, 4–7 November 2012; pp. 408–411. [Google Scholar]

- Song, K.; Oh, W.; Choi, J. A UVLO with zero static power consumption power-on reset circuit in HVIC. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 1085–1089. [Google Scholar]

- Järvenhaara, J.; Herzog, H.; Sipilä, S.; Tian, J.; Filanovsky, I.M.; Tchamov, N.T. High speed DC-DC dead time architecture. IEICE Electron. Express 2015, 12, 20150662. [Google Scholar] [CrossRef]

- Zhu, J.; Zhang, Y.; Sun, W.; Lu, Y.; Shi, L.; Gu, Y.; Zhang, S. Noise immunity and its temperature characteristics study of the capacitive-loaded level shift circuit for high voltage gate drive IC. IEEE Trans. Ind. Electron. 2017, 65, 3027–3034. [Google Scholar] [CrossRef]

- Hwang, J.T.; Jung, M.S.; Kim, J.S.; Kim, D.H. Noise immunity enhanced 625V high-side driver. In Proceedings of the IEEE European Solid-State Circuits Conference (ESSCIRC), Montreux, Switzerland, 19–21 September 2006; pp. 572–575. [Google Scholar]

- Song, K.; Oh, W.; Choi, J.; Hong, S.; Park, S. A new 1200 V HVIC with high side edge trigger in order to solve the latch on failure by the negative VS surge. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 351–354. [Google Scholar]

- Zhu, J.; Yu, S.; Lu, Y.; Sun, W.; Cheng, C.; Yan, D.; Zhang, Y.; Li, S.; Zhang, L.; Zhang, S. Study and implementation of 600V high voltage gate driver IC with the common mode dualinterlock technique for GaN Devices. IEEE Trans. Ind. Electron. 2020. Early Access. [Google Scholar] [CrossRef]

- Murari, B.; Bertotti, F.; Vignola, G.A. Smart Power ICs; Springer: Berlin/Heidelberg, Germany, 2002; pp. 361–370. [Google Scholar]

- Novelli, A.; Giussani, L.; Bellomo, I. New generation of half bridge gate driver ICs for use with low power 3.3 V control applications. In Proceedings of the IEEE Power Electronics Specialists Conference (PESC), Aachen, Germany, 20–25 June 2004; pp. 3237–3242. [Google Scholar]

- Akahane, M.; Jonishi, A.; Yamaji, M.; Kanno, H.; Tanaka, T.; Nishio, H.; Sumida, H. A new level up shifter for HVICs with high noise tolerance. In Proceedings of the International Power Electronics Conference (IPEC), Hiroshima, Japan, 18–21 May 2014; pp. 2302–2309. [Google Scholar]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cho, K. An Ultra-Low Quiescent Current Under-Voltage Lockout Circuit for a High-Voltage Gate Driver IC. Electronics 2020, 9, 1729. https://doi.org/10.3390/electronics9101729

Cho K. An Ultra-Low Quiescent Current Under-Voltage Lockout Circuit for a High-Voltage Gate Driver IC. Electronics. 2020; 9(10):1729. https://doi.org/10.3390/electronics9101729

Chicago/Turabian StyleCho, Kunhee. 2020. "An Ultra-Low Quiescent Current Under-Voltage Lockout Circuit for a High-Voltage Gate Driver IC" Electronics 9, no. 10: 1729. https://doi.org/10.3390/electronics9101729

APA StyleCho, K. (2020). An Ultra-Low Quiescent Current Under-Voltage Lockout Circuit for a High-Voltage Gate Driver IC. Electronics, 9(10), 1729. https://doi.org/10.3390/electronics9101729