1. Introduction

Microcontrollers (

Cs) have been applied in many areas: industrial automation, control, instrumentation, consumer electronics, and various other areas. Nonetheless, there is an ever-growing demand for these devices, especially in emerging sectors such as the Internet of Things (IoT), the smart grid, Machine to Machine (M2M), and edge computing [

1].

A C can be classified as programmable hardware platform that enables embedded system applications in specific cases. It is important to know that Cs are mainly composed of a General-Purpose Processor (GPP) of 8, 16, or 32 bits. Then, this GPP is connected to some peripherals such as Random Access Memory (RAM), flash memory, counters, signal generators, communication protocol specific hardware, analog-to-digital and digital-to-analog converters, and others.

An important fact is that in most products that are available today, the

Cs embedded into them encapsulate an 8-bit GPP with enough computational power and memory storage for use as a resourceful platform for many embedded applications. However, these same 8-bit

Cs are considered low-power and low-cost platforms when compared with other platforms that are used to implement AI applications with Artificial Neural Networks (ANNs) [

2,

3].

The use of artificial intelligence algorithms, such as (ANN, Fuzzy, SVM, Genetic Algorithms, and other ) for embedded systems with real-time constraints, has been a recurrent research topic for many [

4,

5,

6,

7,

8,

9,

10,

11,

12,

13,

14]. Many of the works devised from this topic are driven by the growing demand for AI techniques for IoT, M2M, and edge computing applications.

A major problem with implementing ANN applications into embedded systems is the computational complexity associated with ANNs. In regard to the Multilayer Perceptron (MLP) described in this work, there are many inherent multiplications and calculations of nonlinear functions [

4,

5,

6]. Besides the feedforward process between the input and the synaptic weights, the MLP also has a training algorithm associated with it to find the optimum weights of the neural network. This training algorithm is very computationally expensive [

15]. If the training process is also performed in real time, the computational complexity is increased several times. This increase in complexity automatically raises the processing time and requirements for memory storage from the hardware platform used in the application [

4,

5,

6].

The use of MLP neural networks for real-time applications in

Cs is not a new field. In [

16], the authors describe a method to linearize the nonlinear characteristics of many sensors using an MLP-NN on an 8-bit PIC18F45J10

C. The obtained results show that if the network architecture is right, even very difficult problems of linearization can be solved with just a few neurons.

In [

17], a fully connected multilayer ANN is implemented on a low-end and inexpensive

C. Furthermore, a pseudo-floating-point multiplication is devised to make use of the internal multiplier circuit inside the PIC18F45J10

C used. The authors managed to store 256 weights into the 1KB SRAM of the

C and deemed it enough for most embedded applications.

In [

18], Farooq et al. implemented a hurdle-avoidance system controller for a carlike robot using an AT89C52

C as a system embedding platform. They implemented an MLP with a back-propagation training algorithm and a single hidden layer. The proposed system was tested in various environments containing obstacles and was found to avoid obstacles successfully.

The paper [

19] presents a neural network that is trained with the backpropagation (BP) algorithm and validated using a low-end and inexpensive PIC16F876A 8-bit

C. The authors chose a chemical process as a realistic example of a nonlinear system to demonstrate the feasibility and performance of this approach, as well as the results found using the microcontroller, against a computer implementation. With three inputs, five hidden neurons, and an output neuron on the MLP, the application showed complete suitability for a

C-based approach. The results comparing the

C implementation showed almost no difference in Mean Square Error (MSE) after 30 iterations of the training algorithm. The work presented in [

20] shows an embedded MLP with two layers on the microcontroller. The proposal uses an external tool for training and embedding a trained ANN.

In [

21], the authors implemented a classification application for the MNIST dataset. This implementation processes the 10 digits and full classification with

testing accuracy. In addition, this is implemented with a knowingly highly resource-hungry ANN model, the Convolutional Neural Network (CNN), using less than 2 KB of SRAM memory and also 6 KB of program memory, FLASH. This work was embedded on a Arduino Uno development kit that is composed of a breakout board for the 8-bit ATMega328p

C, with 32 KB of program memory and 2 KB of work memory, running at 16 MHz.

In [

22], the authors present an approach of reordering the operations on an ANN, reducing the memory usage for a CNN. They deployed a SwiftNet Cell with 250 KB of parameters into a Cortex-M7, 32-bit

C, running at 216 MHz, with 512 KB of SRAM. The results of reordering the operations showed an increase in inference time and energy use of less than 1% and a decrease of approximately 53% of peak memory usage, thus showing that such applications can be made in 32-bit

Cs.

The reference works presented above demonstrate different aspects of implementing ANNs on

Cs. In [

17,

18,

19], you will find application proposals showing MLP-ANNs trained with the backpropagation (BP) algorithm implemented on

Cs with good results; however, none of these talk about memory usage and processing-time parameters that vary according to the MLP hyperparameters. In [

16,

23,

24], the authors present some results regarding processing time, but none are dependent on the number of artificial neurons or even comparing the time required to train the ANN in real time or not.

Therefore, this work proposes an implementation of an MLP-ANN that can be trained with the BP algorithm into an ATMega2560 8-bit C in the C language to show that many applications with ANNs are suitable on the C platform. This work also presents two implementations regarding a model that is trained on the C platform in real time and another implementation that is trained with MatLab and then ported to the same architecture to execute classification in real time.

In addition to the implementation proposal, the parameters of the processing time for each feedforward step and backward steps in the training and classification process are presented. In addition, the variation of these parameters is shown due to the variation of the hyperparameters of the MLP. The validation of the classification and training results on a Hardware-In-the-Loop (HIL) strategy also are presented in this work.

3. Methodology

The implementation was validated using the HIL simulation strategy, as explained in [

3] and illustrated in

Figure 2. The tested variables are execution time for the FFM-1 for the hidden layer as seen in

Figure 1 defined as

, execution time for the FFM-2, feedforward for the output layer of neurons,

, error module

, backpropagation of the output neurons layer,

, and the backpropagation of the hidden neurons layer,

.

A parameter that was also analyzed is the memory occupation, regarding both memories of the ATMega-2560 C used in this paper, FLASH or program memory and SRAM or work memory.

As previously mentioned, the modules were implemented in the C program language for AVR Cs using the avr-gcc version 5.4.0, inside the Atmel Studio 7 development environment, an Integrated Development Environment (IDE) made available by Microchip. After compilation and binary code generation, the solution was embedded into an Atmega-2560. This C has an 8-bit GPP integrated with 256 KBytes of FLASH program memory and 8 KBytes of SRAM work memory, and its maximum processing speed is 1 MIPS/MHz.

The Atmega-2560 is associated with an Arduino Mega v2.0 development kit: the Arduino Mega is a development kit that provides a breakout board for all the ATmega-2560 pins and some other components required for the C to function properly. A great feature of this development kit is the onboard Universal Serial Bus (USB) programmer that enables the developer to simply connect a USB port to a computer and test various implementations easily on the C.

This work was validated using two cases. First, the MLP-BP was trained to behave as an XOR operation as the simplest case possible to train an MLP and evaluate its ability to learn a nonlinear relationship between two inputs. Secondly, the network was trained to aid a carlike virtual robot in avoiding obstacles in a virtual map using MatLab and three cases of increasing ANN architecture complexity. The assembly and analysis of these two validation cases are presented in the following subsections.

3.1. Hardware-In-the-Loop Simulation

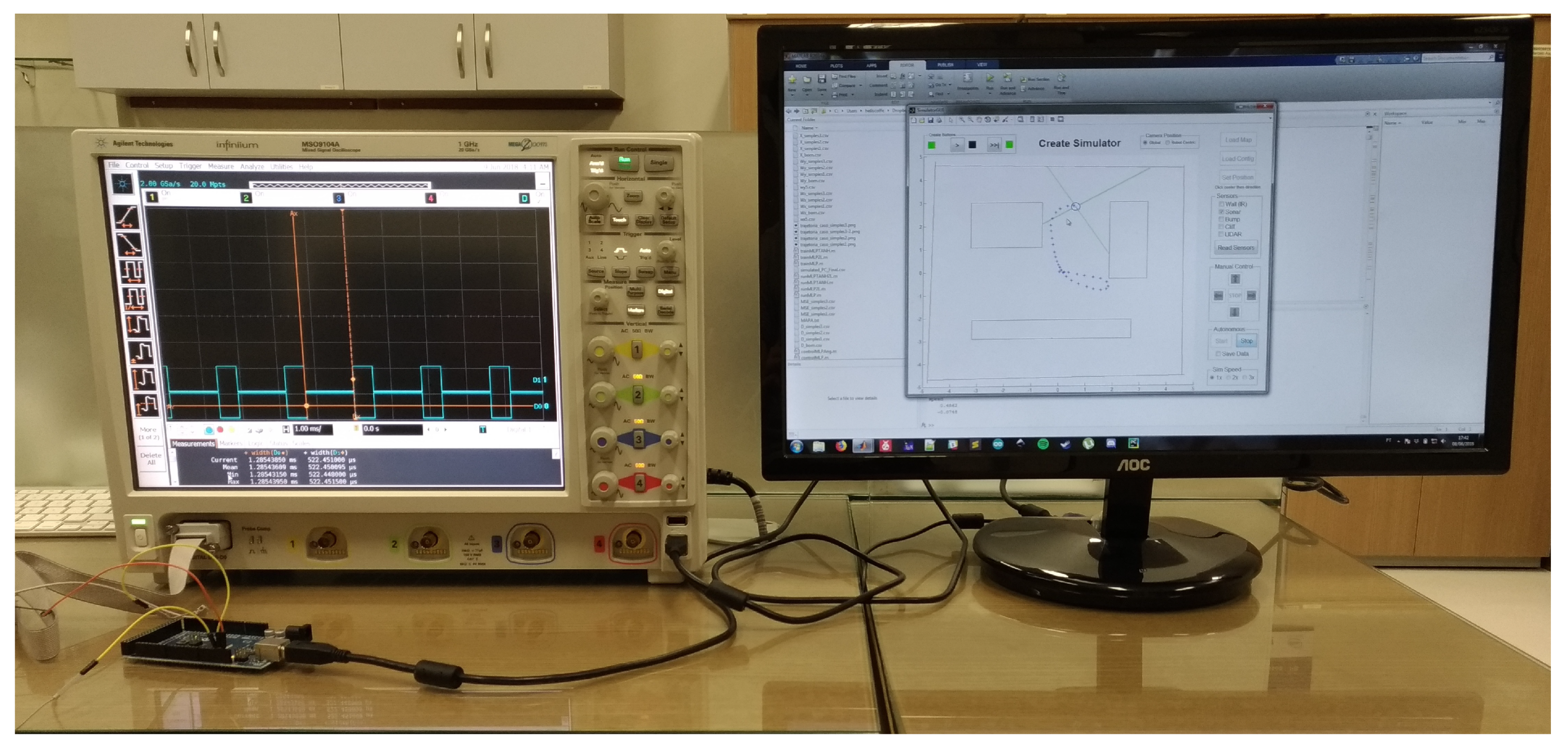

The tests were executed with the

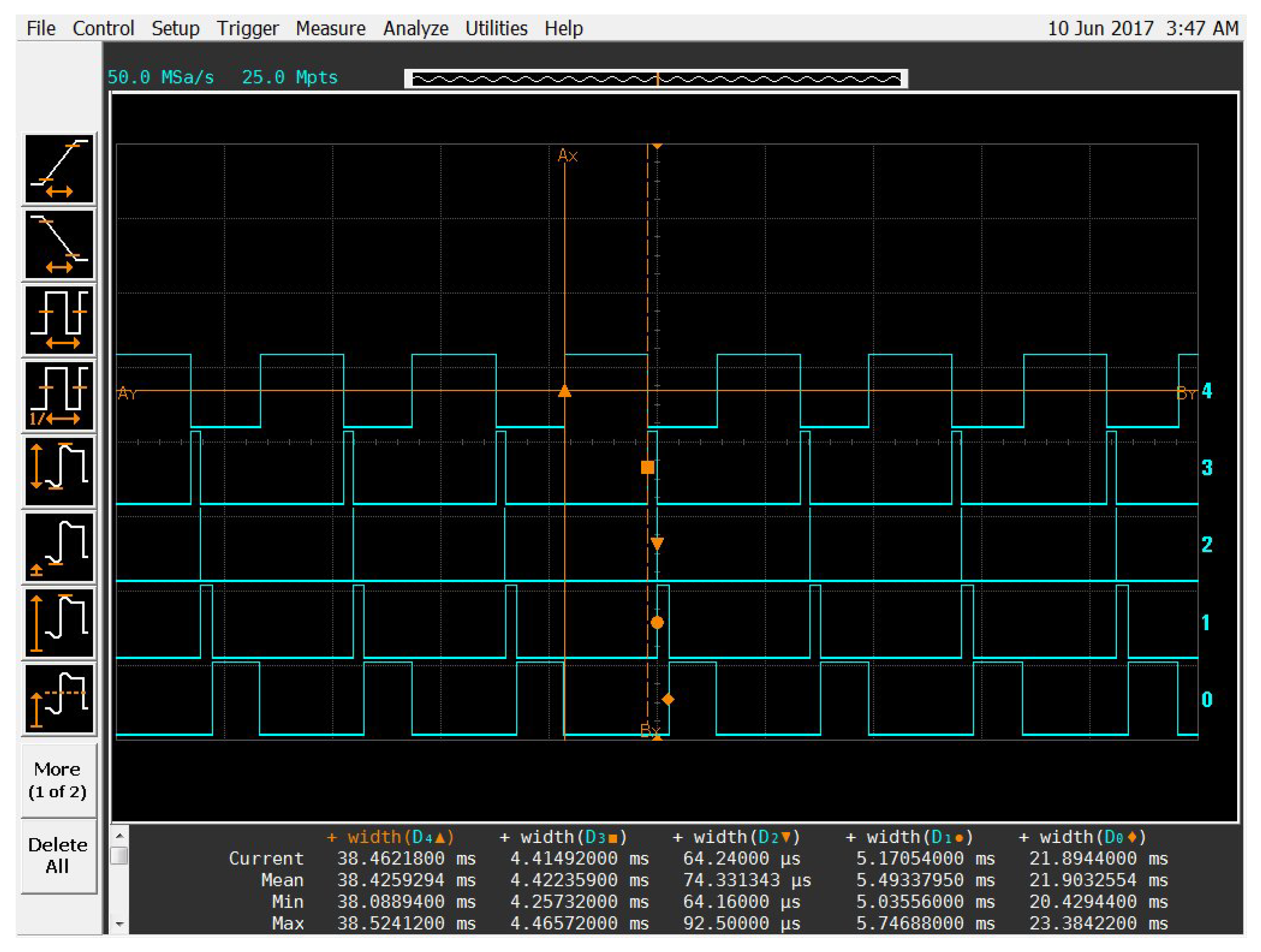

C running at a clock of 16 MHz. The results were obtained by setting the level of a digital pin of the ATMega-2560 to HIGH, executing one of the modules and setting the same digital pin logical value to LOW, and measuring the time of logic HIGH on an oscilloscope for this digital pin. This can be easily seen on

Figure 2, and a picture of the HIL assembly is shown in

Figure 3.

Figure 4 gives a closer look at the oscilloscope measurements, taking into account all the modules being measured according to their duration of execution for the XOR validation case described below.

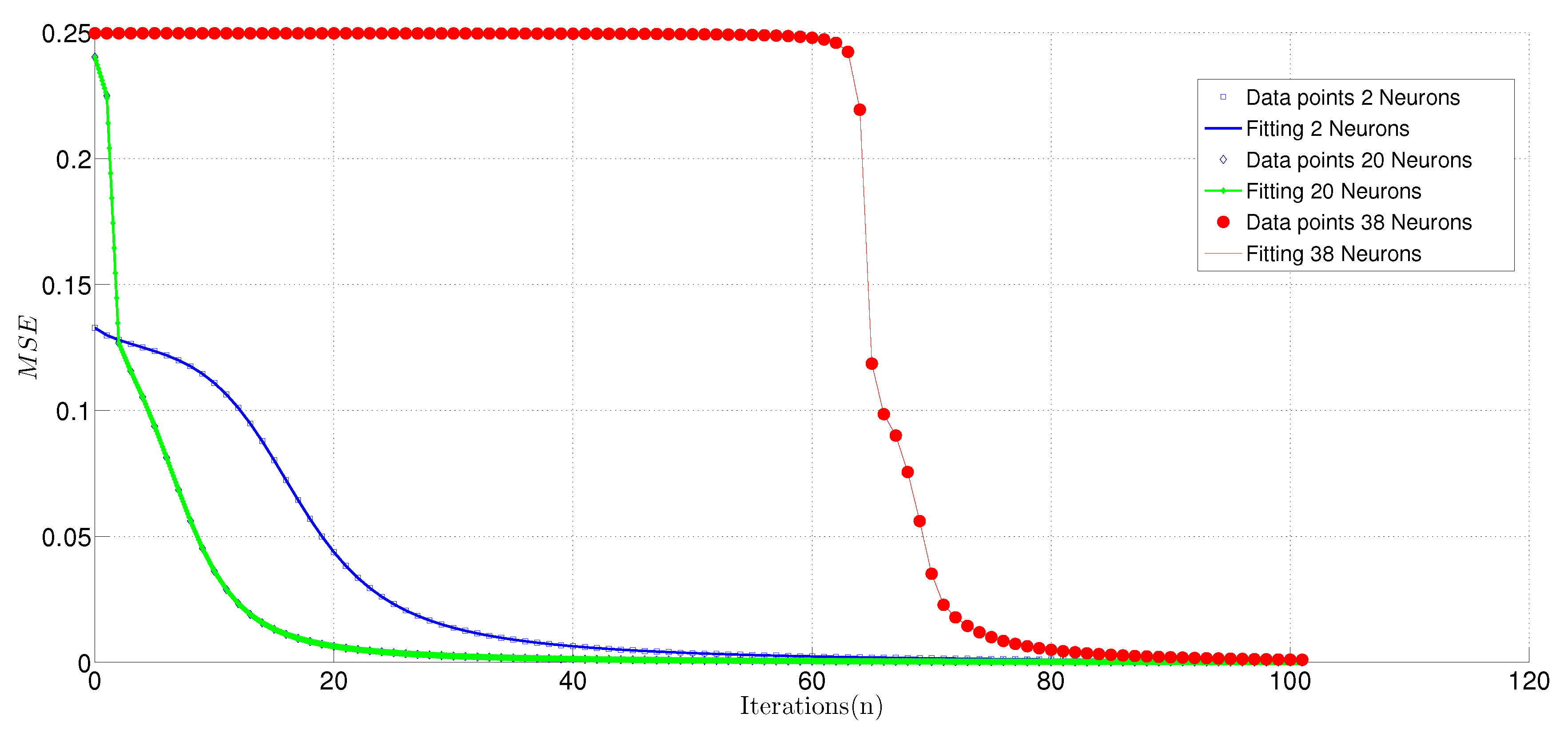

The calculation of the MSE during training was also embedded into the

C implementation and they were transmitted through Universal Serial Synchronous Asynchronous Receiver Transmitter (USART) protocol to a computer. The calculation of the MSE is defined as

where

is the implementation seen in Algorithm 5.

3.2. XOR Operation

A validation of the real-time embedded training using the

module was devised for a XOR operation, as described in

Table 1, the most basic MLP validation case. This test was performed with training and classification phases, both running in the

C, considering a configuration as seen in

Figure 1. The test was executed on batch mode with

, two layers of neurons (

), two input signals (

), a varying amount of neurons in the hidden neurons layer (

), and a single neuron in the output layer (

). It is important to notice that the strategy herein presented can be assembled with various different configurations only modifying the

and

M parameters, with the

Cs internal memories being the limiting factor for the ANN architecture size.

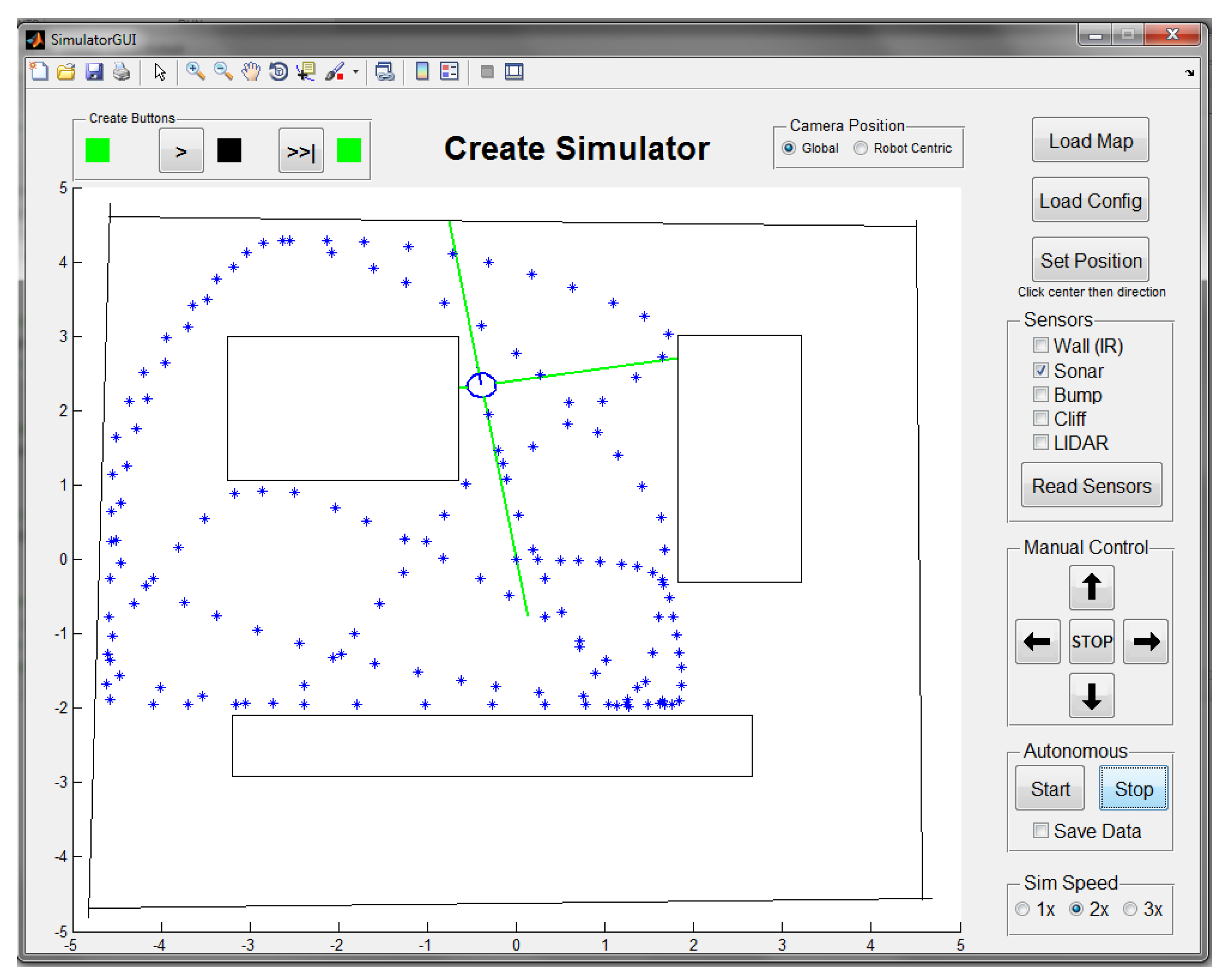

3.3. Virtual Carlike Robot

This work also tested an MLP-BP model to control a virtual carlike robot from the

iRobot MatLab toolbox, provided by the United States Naval Academy (USNA) [

27]. This toolbox provides a virtual environment and an interface to test control algorithms on a deferentially steered robot on various maps with different obstacles and different combinations of distance or proximity sensors.

As previously stated, this virtual environment provides an interface to control a deferentially steered virtual robot. This robot is controlled by changing the angular speed in rad/s of the two wheels, Right Wheel (RW) and Left Wheel (LW). Furthermore, this work used three proximity sensors with a virtual 3 m range to provide input to the MLP. The sensors are Front-Sensor (FS), Left-Sensor (LS) and Right-Sensor (RS).

The MLP model with three different datasets was tested, increasing the hyperparameters to evaluate the behavior of the robot. The cases are composed of three tables with five columns each, as seen in

Table 2. The first case is very simple with only eight conditions provided to train the network, which means the network must be able to devise a knowledge representation of how to behave with cases not previously trained from these simple constraints.

The second case has a greater complexity with 18 conditions, as seen in

Table 3. In addition, as mentioned in

Table 3, this case required the same amount of neurons in the hidden layer, meaning that the first architecture could still be used for a more complex case.

The third was the most complex case with 27 conditions (see

Table 4) to train the MLP-BP. This dataset required a bigger architecture than the previous datasets, with double the amount of neurons in the hidden layer (

).

5. Comparison with the State-of-the-Art

The work McDanel et al. [

29] shows two implementations of an MLP-BP with single and dual hidden layers and their respective execution times for a classification with the results shown in

Table 7. In [

21], the authors were able to embed a full MNIST-10 classification model using CNNs with under 2 KB of SRAM; the inference times were also in the order of 640 ms per input sample.

It is important to note that the times measurements presented in

Table 7 take only the inferencing time into account. The implementation for McDanel et al. [

29] trained the model offline using MatLab. For the Gural & Murmann [

21] paper, the training was also executed offline on a Jupyter Notebook running Tensorflow-Keras models and optimizations before porting the synaptic weights and kernels to the

C.

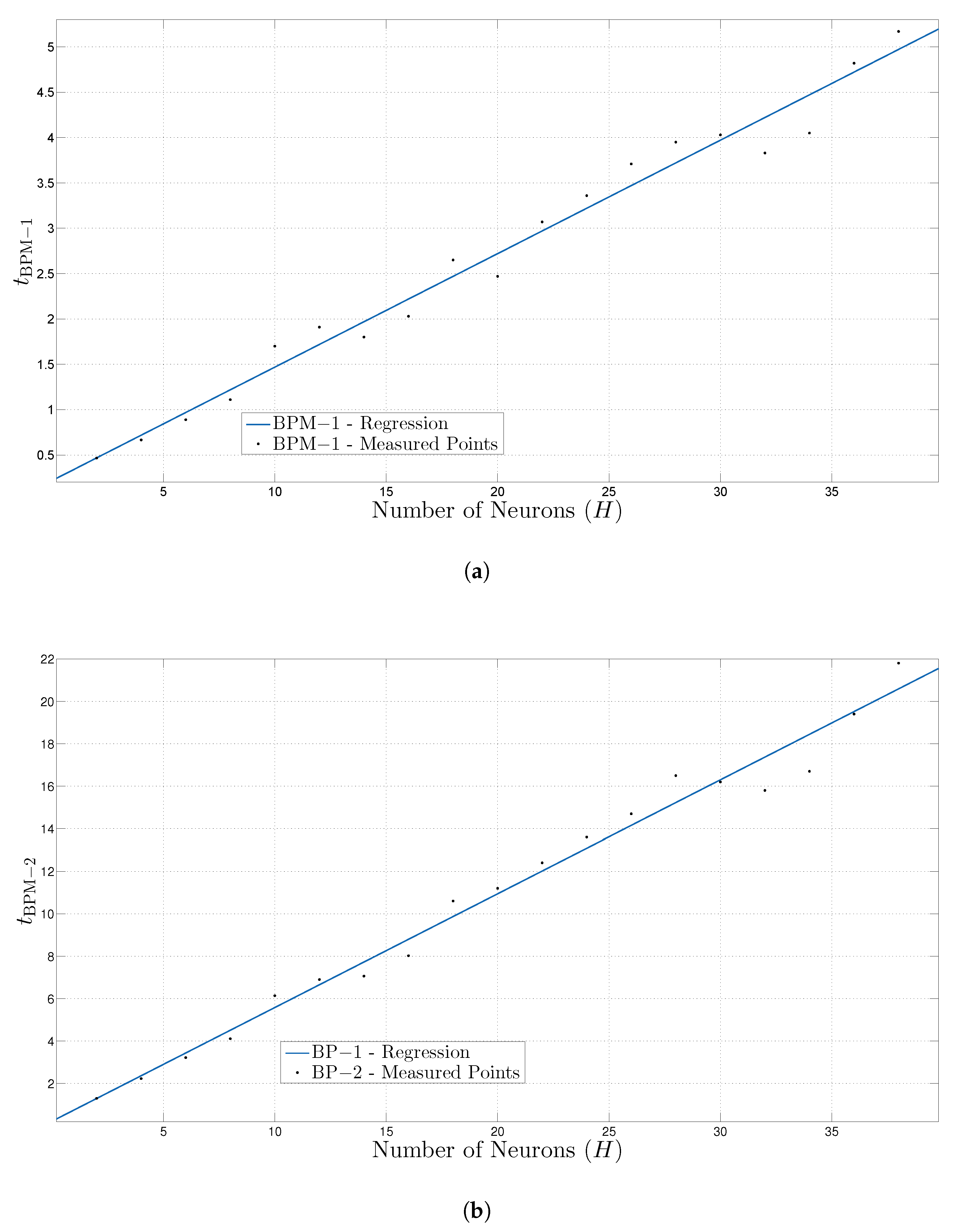

It is possible to analyze this proposal, regarding how this system would behave if it had to support the same hyperparameters that some of these state-of-the-art applications have. The work presented by McDanel et al. [

29] uses an MLP ANN with a single layer with 100 artificial neurons. This same work also presents another implementation with a two-layer MLP with 200 artificial neurons. Analyzing the

, and

fitted curves from

Table 5, we obtained four predictive equations that define how much time is required to process this MLP implementation.

The equation expressed as

shows us again that there is a linear relationship between inference time and hyperparameters for the proposal in this work, specifically artificial neurons. Evaluating Equation (

16), with 100 units, a feedfowarding time of

is observed for the first layer.

Taking into account the same amount of neurons for the equation characterized as

of feedforwarding time for the second layer was achieved. This amounts to of total inferencing time with 100 neurons.

If the embedded training is to be also considered with this amount of neurons, the time duration for this process increases to

by evaluating the equation expressed as

Furthermore, evaluating the equation

for the second layer, considering two hidden layers for training, the time duration increases to

. This analysis shows that the modular implementation of the MLP herein presented performs in compatible training and inference times.

6. Conclusions

This work proposes an implementation of an MLP-ANN with embedded backpropagation training for an 8-bit C. We present a modular and matrix-based MLP with an analysis of the time-to-inference of each module on two test cases. We measured the application code size and compared it with different architectures and hyperparameters.

The results of both these two analyses showed that, for this proposal, the number of hyperparameters presents a directly proportional relationship with the time-to-inference. Furthermore, code-size and memory occupancy grow proportional to the number of artificial neurons, layers, and inputs. This gives the ANN designer a chance to better comprehend the memory requirements for a model and also which hardware platforms can fit the desired ML application.

The comparison presented in this work explores how our modular proposal would behave using the same set of hyperparameters as the reference works. This information is extracted from evaluating the four regression equations in the previous section and showed that for 100 units in the first hidden layer, the inference time would increase to 1.30 s and 1.44 s with embedded training in the MCU. In addition, it is important to note that this comparison is a 32-bits C against the 8-bits Atmega-2560.

Finally, the results we present show that the inference latency and code-size achieved with this proposal for MLPs are compatible with the works of SOTA and that embedding MLPs on Cs is a viable option, using low-cost and low-power devices.