Frequency Selective Degeneration for 6–18 GHz GaAs pHEMT Broadband Power Amplifier Integrated Circuit

Abstract

1. Introduction

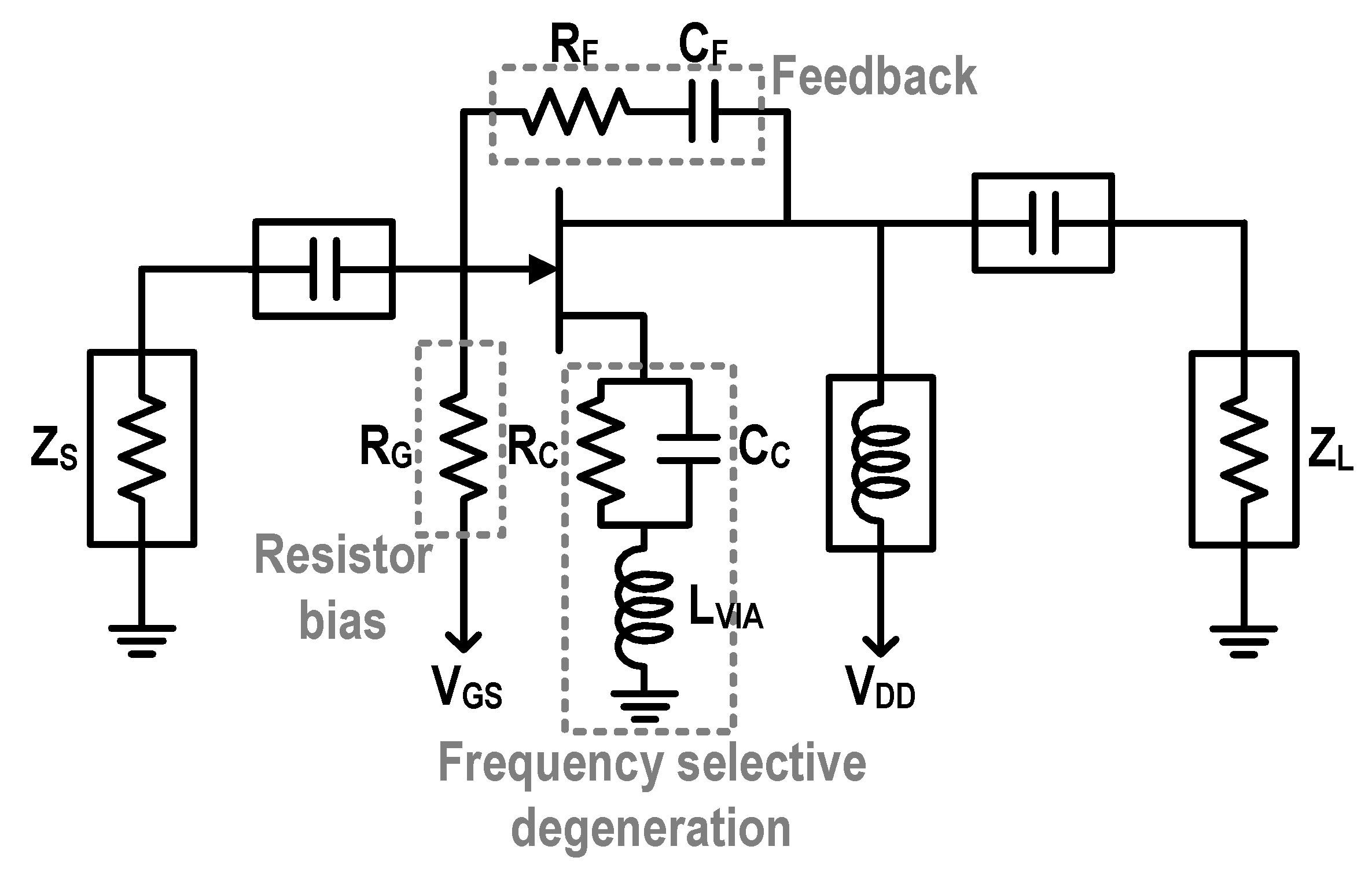

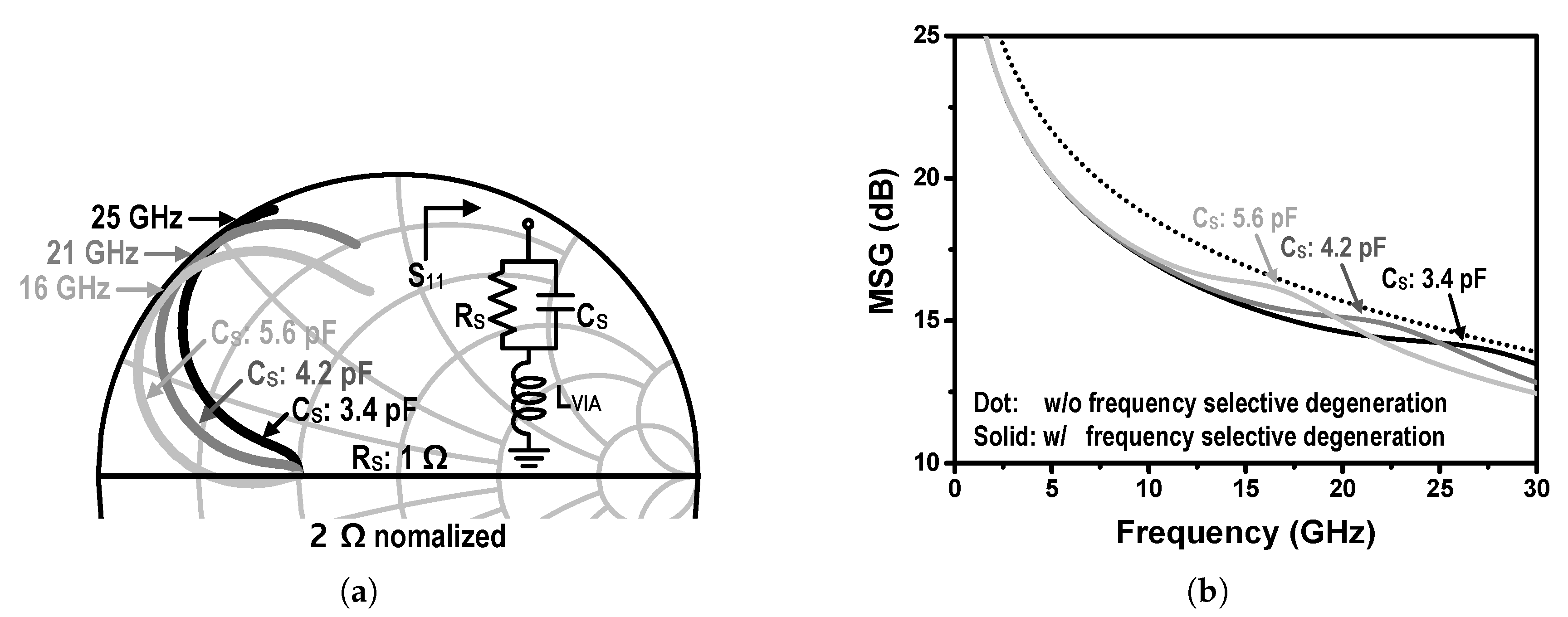

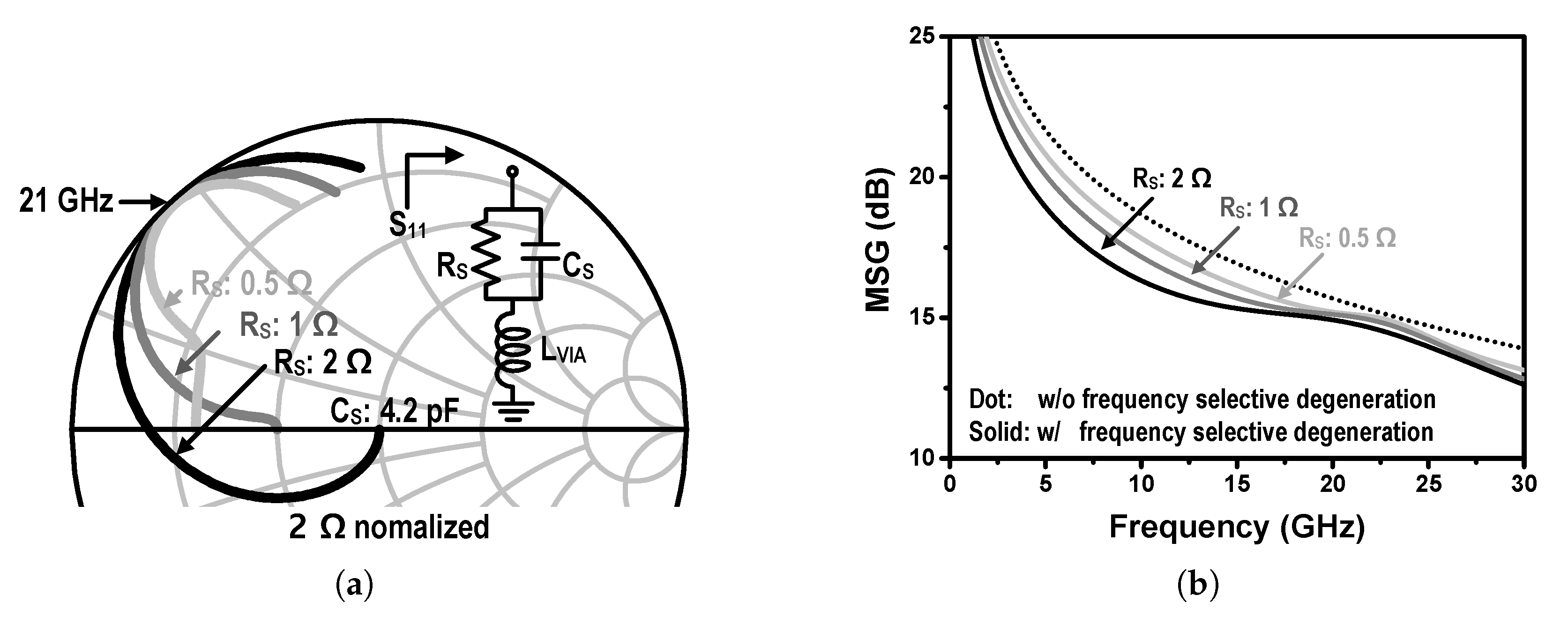

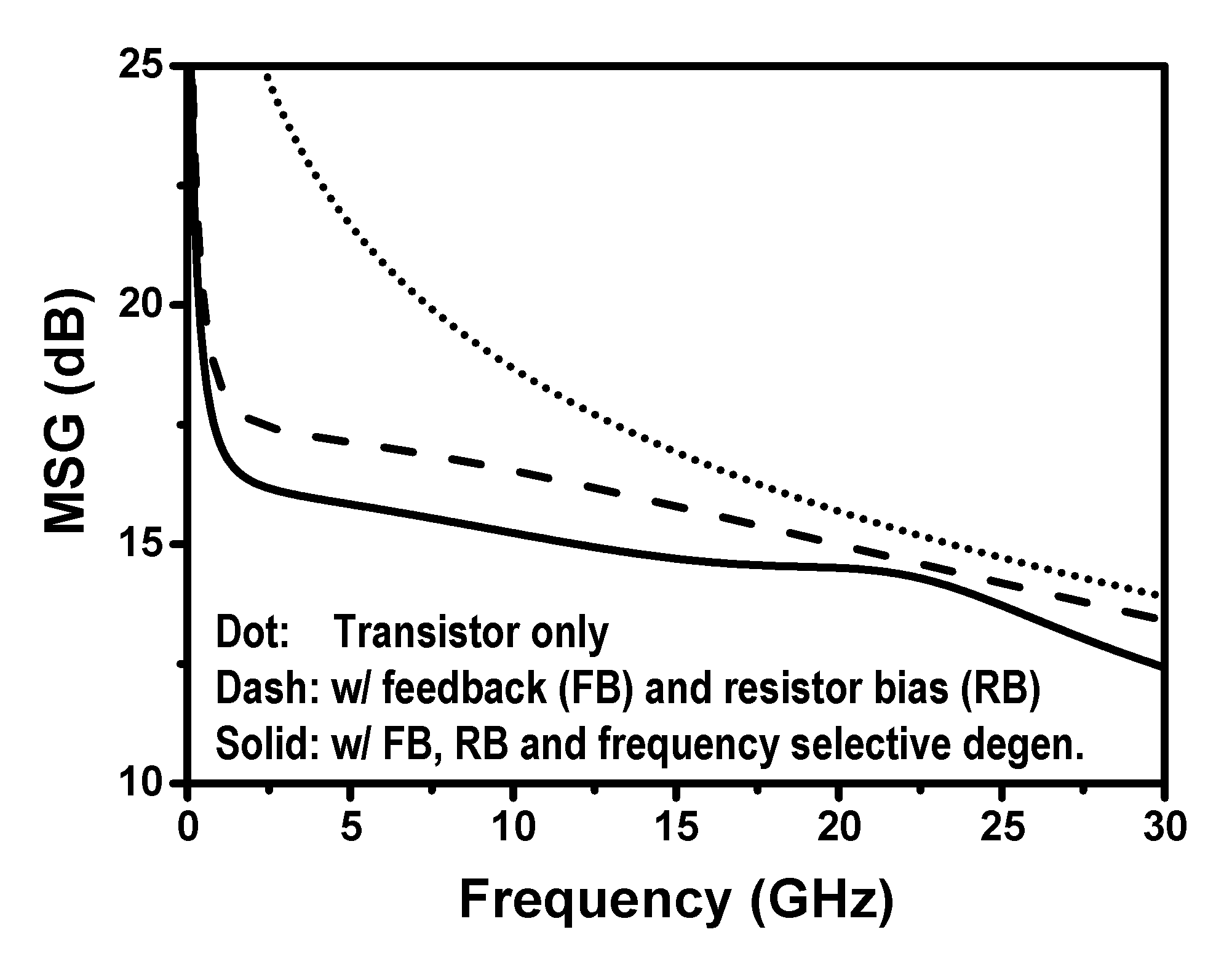

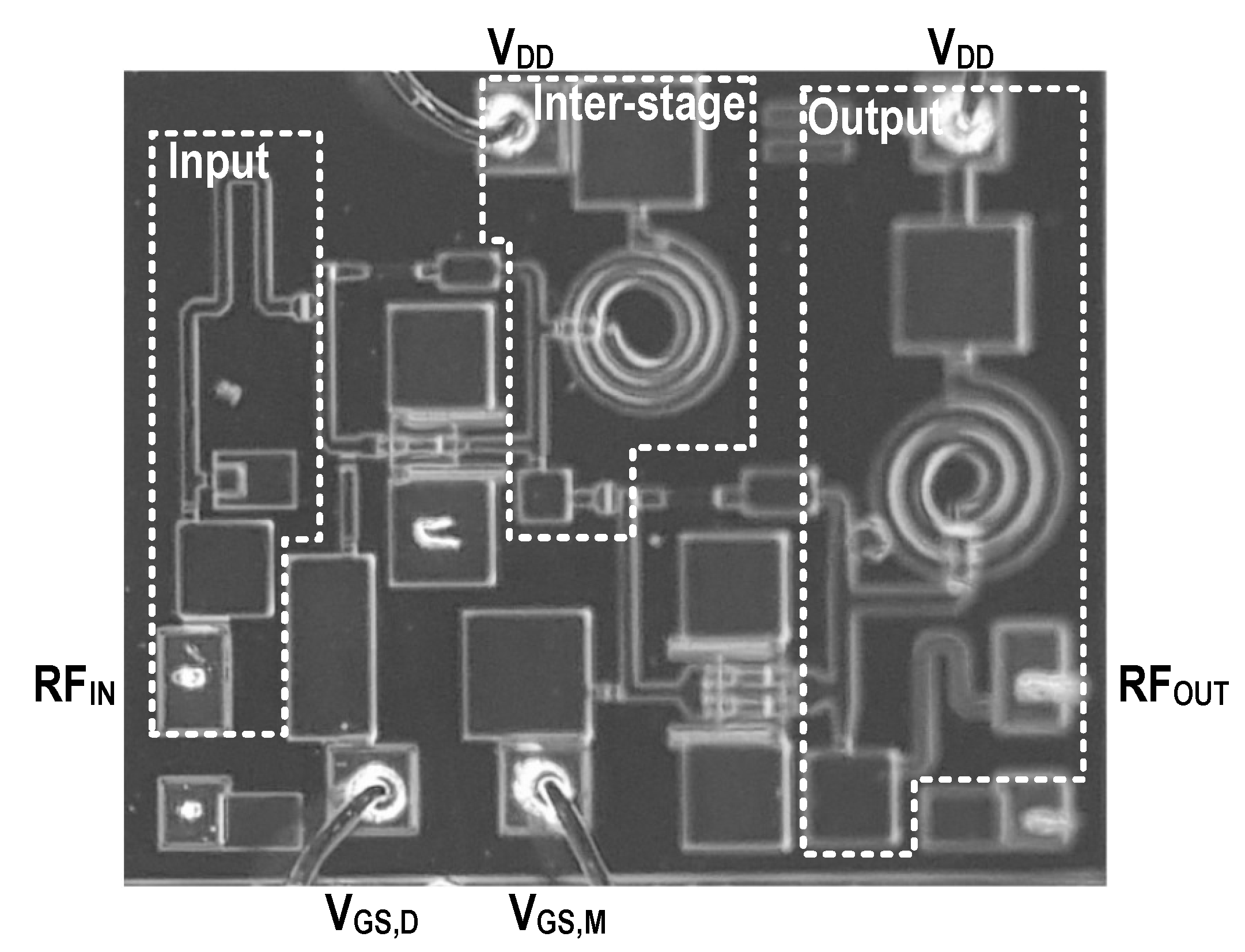

2. Design of the Proposed Broadband PAIC

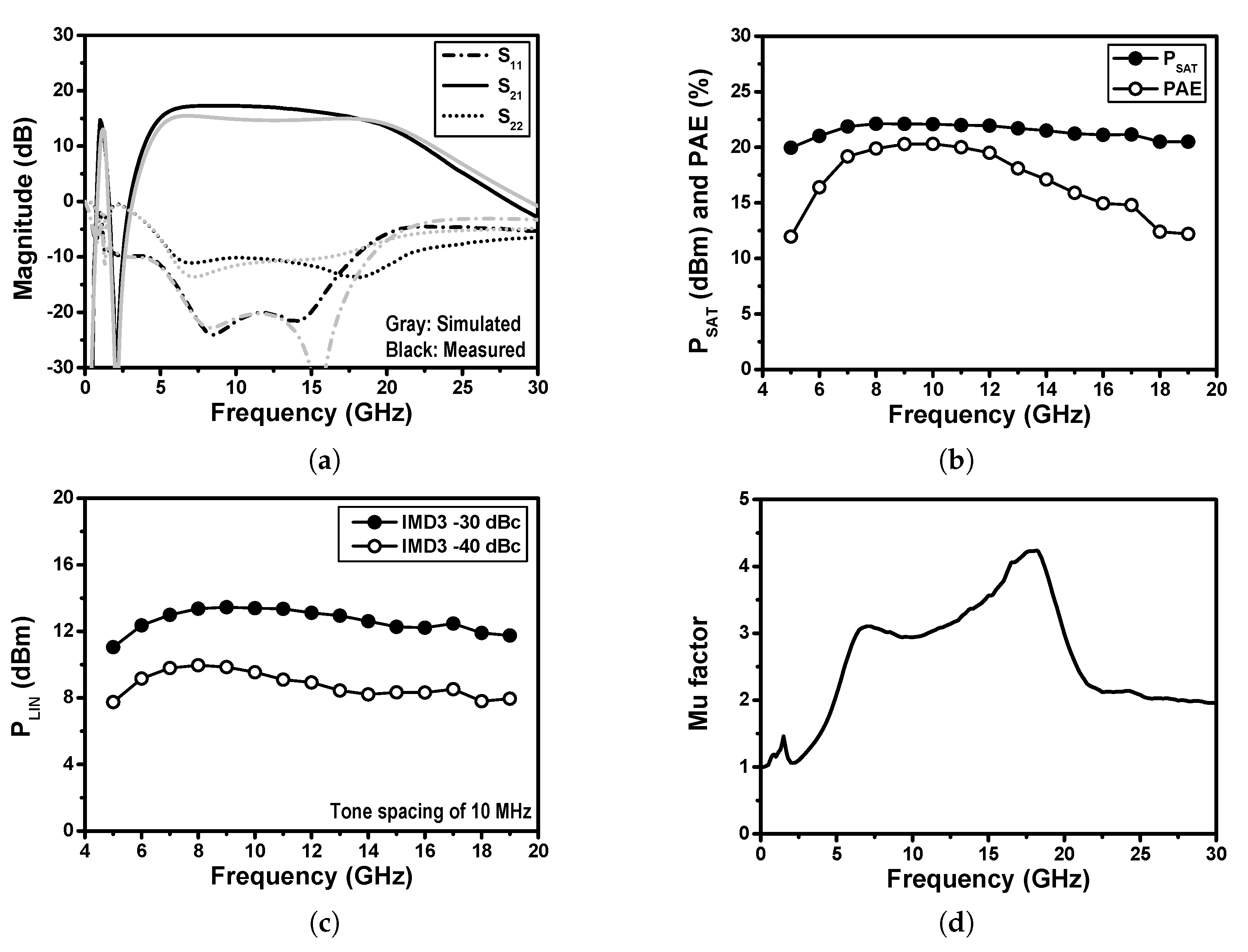

3. Experimental Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kerherve, E.; Demirel, N.; Ghiotto, A.; Larie, A.; Deltimple, N.; Pham, J.M.; Mancuso, Y.; Garrec, P. A Broadband 4.5–15.5-GHz SiGe Power Amplifier With 25.5-dBm Peak Saturated Output Power and 28.7% Maximum PAE. IEEE Trans. Microw. Theory Tech. 2015, 63, 1621–1632. [Google Scholar] [CrossRef]

- Lee, H.; Lee, W.; Kim, T.; Helaoui, M.; Ghannouchi, F.M.; Yang, Y. 6–18 GHz GaAs pHEMT Broadband Power Amplifier Based on Dual-Frequency Selective Impedance Matching Technique. IEEE Access 2019, 7, 66275–66280. [Google Scholar] [CrossRef]

- Jeong, J.; Yom, I.; Kim, J.; Lee, W.; Lee, C. A 6–18-GHz GaAs Multifunction Chip With 8-bit True Time Delay and 7-bit Amplitude Control. IEEE Trans. Microw. Theory Tech. 2018, 66, 2220–2230. [Google Scholar] [CrossRef]

- de Hek, P.; Van Caekenberghe, K.; van Dijk, R. A 3–14 GHz pseudo-differential distributed low noise amplifier. In Proceedings of the 5th European Microwave Integrated Circuits Conference, Paris, France, 27–28 September 2010; pp. 337–340. [Google Scholar]

- Santhakumar, R.; Thibeault, B.; Higashiwaki, M.; Keller, S.; Chen, Z.; Mishra, U.K.; York, R.A. Two-Stage High-Gain High-Power Distributed Amplifier Using Dual-Gate GaN HEMTs. IEEE Trans. Microw. Theory Tech. 2011, 59, 2059–2063. [Google Scholar] [CrossRef]

- Park, H.; Nam, H.; Choi, K.; Kim, J.; Kwon, Y. A 6–18-GHz GaN Reactively Matched Distributed Power Amplifier Using Simplified Bias Network and Reduced Thermal Coupling. IEEE Trans. Microw. Theory Tech. 2018, 66, 2638–2648. [Google Scholar] [CrossRef]

- Campbell, C.; Lee, C.; Williams, V.; Kao, M.Y.; Tserng, H.Q.; Saunier, P.; Balisteri, T. A Wideband Power Amplifier MMIC Utilizing GaN on SiC HEMT Technology. IEEE J. Solid-State Circuits 2009, 44, 2640–2647. [Google Scholar] [CrossRef]

- Oreja-Gigorro, E.; Pascual, E.D.; Sanchez-Martínez, J.J.; Gil-Heras, M.L.; Bueno-Fernandez, V.; Bodalo-Marquez, A.; Grajal, J. A 6–18 GHz GaN on SiC High Power Amplifier MMIC for Electronic Warfare. In Proceeding of the 13th European Microwave Integrated Circuits Conference (EuMIC), Madrid, Spain, 23–25 September 2018; pp. 85–88. [Google Scholar]

- Meghdadi, M.; Medi, A. Design of 6–18-GHz High-Power Amplifier in GaAs pHEMT Technology. IEEE Trans. Microw. Theory Tech. 2017, 65, 2353–2360. [Google Scholar] [CrossRef]

- Schmid, U.; Sledzik, H.; Schuh, P.; Schroth, J.; Oppermann, M.; Brückner, P.; van Raay, F.; Quay, R.; Seelmann-Eggebert, M. Ultra-Wideband GaN MMIC Chip Set and High Power Amplifier Module for Multi-Function Defense AESA Applications. IEEE Trans. Microw. Theory Tech. 2013, 61, 3043–3051. [Google Scholar] [CrossRef]

- Xia, Q.; Li, D.; Huang, J.; Li, J.; Chang, H.; Sun, B.; Liu, H. A 28 GHz Linear Power Amplifier Based on CPW Matching Networks with Series-Connected DC-Blocking Capacitors. Electronics 2020, 9, 617. [Google Scholar] [CrossRef]

- Lee, W.; Kang, H.; Lee, H.; Lim, W.; Bae, J.; Koo, H.; Yoon, J.; Hwang, K.C.; Lee, K.Y.; Yang, Y. Broadband InGaP/GaAs HBT Power Amplifier Integrated Circuit Using Cascode Structure and Optimized Shunt Inductor. IEEE Trans. Microw. Theory Tech. 2019, 67, 5090–5100. [Google Scholar] [CrossRef]

- Sharma, T.; Aflaki, P.; Helaoui, M.; Ghannouchi, F.M. Octave Bandwidth Doherty Power Amplifier Using Multiple Resonance Circuit for the Peaking Amplifier. IEEE Trans. Circuits Syst. I Reg. Pap. 2019, 66, 583–593. [Google Scholar]

- Kim, D.-M.; Kim, D.; Jeong, H.-G.; Im, D. A Reconfigurable CMOS Inverter-based Stacked Power Amplifier with Antenna Impedance Mismatch Compensation for Low Power Short-Range Wireless Communications. Electronics 2020, 9, 562. [Google Scholar] [CrossRef]

- Yang, Z.; Yao, Y.; Liu, Z.; Li, M.; Li, T.; Dai, Z. Design of High Efficiency Broadband Continuous Class-F Power Amplifier Using Real Frequency Technique With Finite Transmission Zero. IEEE Access 2018, 6, 61983–61993. [Google Scholar] [CrossRef]

- Lee, W.; Kang, H.; Choi, S.; Lee, S.; Kwon, H.; Hwang, K.; Lee, K.-Y.; Yang, Y. Scaled GaN-HEMT Large-Signal Model Based on EM Simulation. Electronics 2020, 9, 632. [Google Scholar] [CrossRef]

- Sharma, T.; Aflaki, P.; Helaoui, M.; Ghannouchi, F.M. Broadband GaN Class-E Power Amplifier for Load Modulated Delta Sigma and 5G Transmitter Applications. IEEE Access 2018, 6, 4709–4719. [Google Scholar] [CrossRef]

- Lee, S.; Park, H.; Choi, K.; Kwon, Y. A Broadband GaN pHEMT Power Amplifier Using Non-Foster Matching. IEEE Trans. Microw. Theory Tech. 2015, 63, 4406–4414. [Google Scholar] [CrossRef]

- Huang, C.; He, S.; Shi, W.; Song, B. Design of Broadband High-Efficiency Power Amplifiers Based on the Hybrid Continuous Modes With Phase Shift Parameter. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 159–161. [Google Scholar] [CrossRef]

- Amirpour, R.; Darraji, F.; Ghannouchi, F.; Quay, R. Enhancement of the Broadband Efficiency of a Class-J Power Amplifier With Varactor-based Dynamic Load Modulation. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 180–182. [Google Scholar] [CrossRef]

- Saad, P.; Hou, R.; Hellberg, R.; Berglund, B. A 1.8–3.8-GHz Power Amplifier With 40% Efficiency at 8-dB Power Back-Off. IEEE Trans. Microw. Theory Tech. 2018, 66, 4870–4882. [Google Scholar] [CrossRef]

- Liu, B.; Mao, M.; Khanna, D.; Boon, C.; Choi, P.; Fitzgerald, E.A. A Novel 2.6–6.4 GHz Highly Integrated Broadband GaN Power Amplifier. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 37–39. [Google Scholar] [CrossRef]

| Main Stage | Drive Stage | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| 200 Ω | 1 pF | 50 Ω | 1 Ω | 4.2 pF | 300 Ω | 1 pF | 126 Ω | 1 Ω | 4.2 pF |

| Ref. | Process | Freq. (GHz) | Gain * (dB) | Gain Flatness (dB) | Input Reflection ** (dB) | Output Reflection ** (dB) | *** (dBm) | Flatness (dB) | PAE (%) | Size (mm2) | Structure |

|---|---|---|---|---|---|---|---|---|---|---|---|

| [1] | 0.13 m SiGe BiCMOS | 4.5–15.5 | 13.8 | ±2.8 | 21.3 | ±2.1 | 11.9–28.7 | 1.96 | Cascode differential | ||

| [5] | 0.2 m GaN HEMT | 2.0–18.0 | 19.5 | ±1.5 | + | + | 26.0 | ±2.0 | 5.0–12.0 | 8.0 | Distributed |

| [4] | 0.15 m GaAs pHEMT | 3.0–14.0 | 17.0 | ±1.0 | 15.0 | - | - | 7.44 | Distributed | ||

| [3] | 0.25 m GaAs pHEMT | 6.0–18.0 | 12.0 | ±1.0 | + | + | 15.0 | ±1.5 | - | 5.2 | Two-stage |

| [2] | 0.15 m GaAs pHEMT | 6.0–18.0 | 17.4 | ±1.0 | + | - | 19.2 | ±0.9 | 13.0–21.7 | 0.97 | Two-stage |

| This work | 0.15 m GaAs pHEMT | 6.0–18.0 | 16.1 | ±1.1 | 20.5 | ±0.8 | 12.4–20.3 | 0.89 | Two-stage |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Oh, S.; Yoo, E.; Oh, H.; Koo, H.; Shin, J.; Hwang, K.C.; Lee, K.-Y.; Yang, Y. Frequency Selective Degeneration for 6–18 GHz GaAs pHEMT Broadband Power Amplifier Integrated Circuit. Electronics 2020, 9, 1588. https://doi.org/10.3390/electronics9101588

Oh S, Yoo E, Oh H, Koo H, Shin J, Hwang KC, Lee K-Y, Yang Y. Frequency Selective Degeneration for 6–18 GHz GaAs pHEMT Broadband Power Amplifier Integrated Circuit. Electronics. 2020; 9(10):1588. https://doi.org/10.3390/electronics9101588

Chicago/Turabian StyleOh, Sungjae, Eunjoo Yoo, Hansik Oh, Hyungmo Koo, Jaekyung Shin, Keum Cheol Hwang, Kang-Yoon Lee, and Youngoo Yang. 2020. "Frequency Selective Degeneration for 6–18 GHz GaAs pHEMT Broadband Power Amplifier Integrated Circuit" Electronics 9, no. 10: 1588. https://doi.org/10.3390/electronics9101588

APA StyleOh, S., Yoo, E., Oh, H., Koo, H., Shin, J., Hwang, K. C., Lee, K.-Y., & Yang, Y. (2020). Frequency Selective Degeneration for 6–18 GHz GaAs pHEMT Broadband Power Amplifier Integrated Circuit. Electronics, 9(10), 1588. https://doi.org/10.3390/electronics9101588