A Fast Transient Response Digital LDO with a TDC-Based Signal Converter

Abstract

:1. Introduction

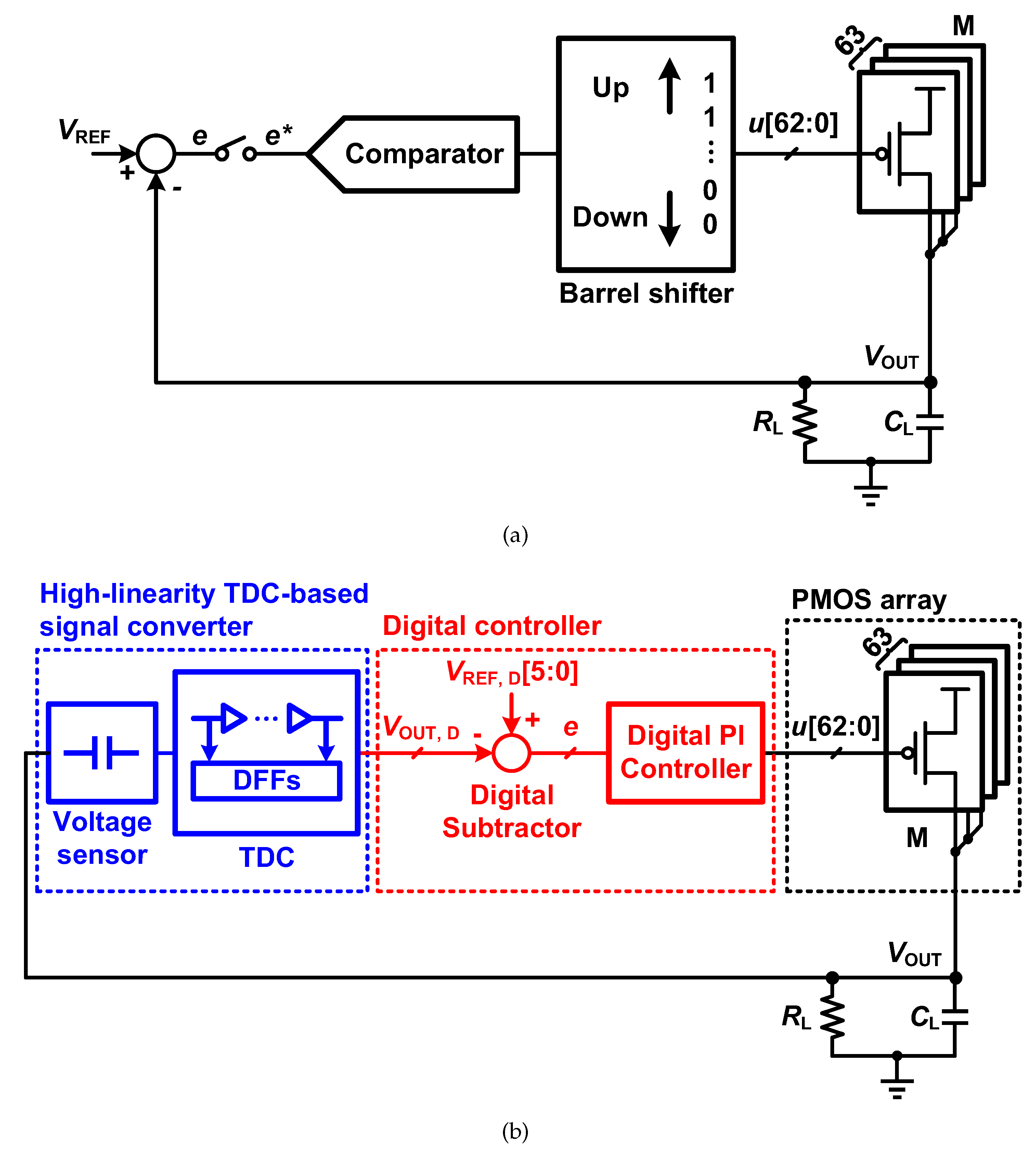

2. System Overview

2.1. The Architecture of the Proposed DLDO

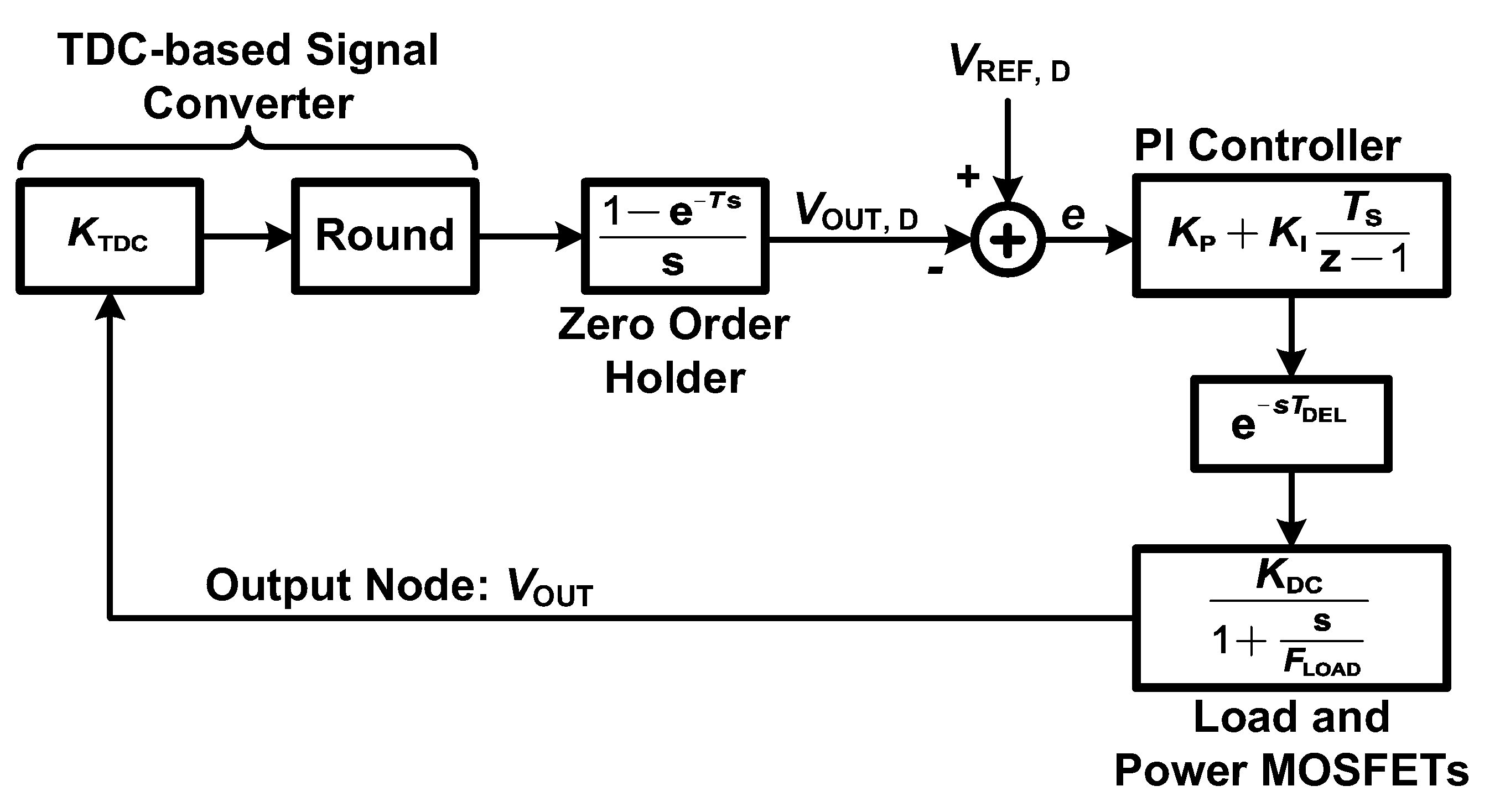

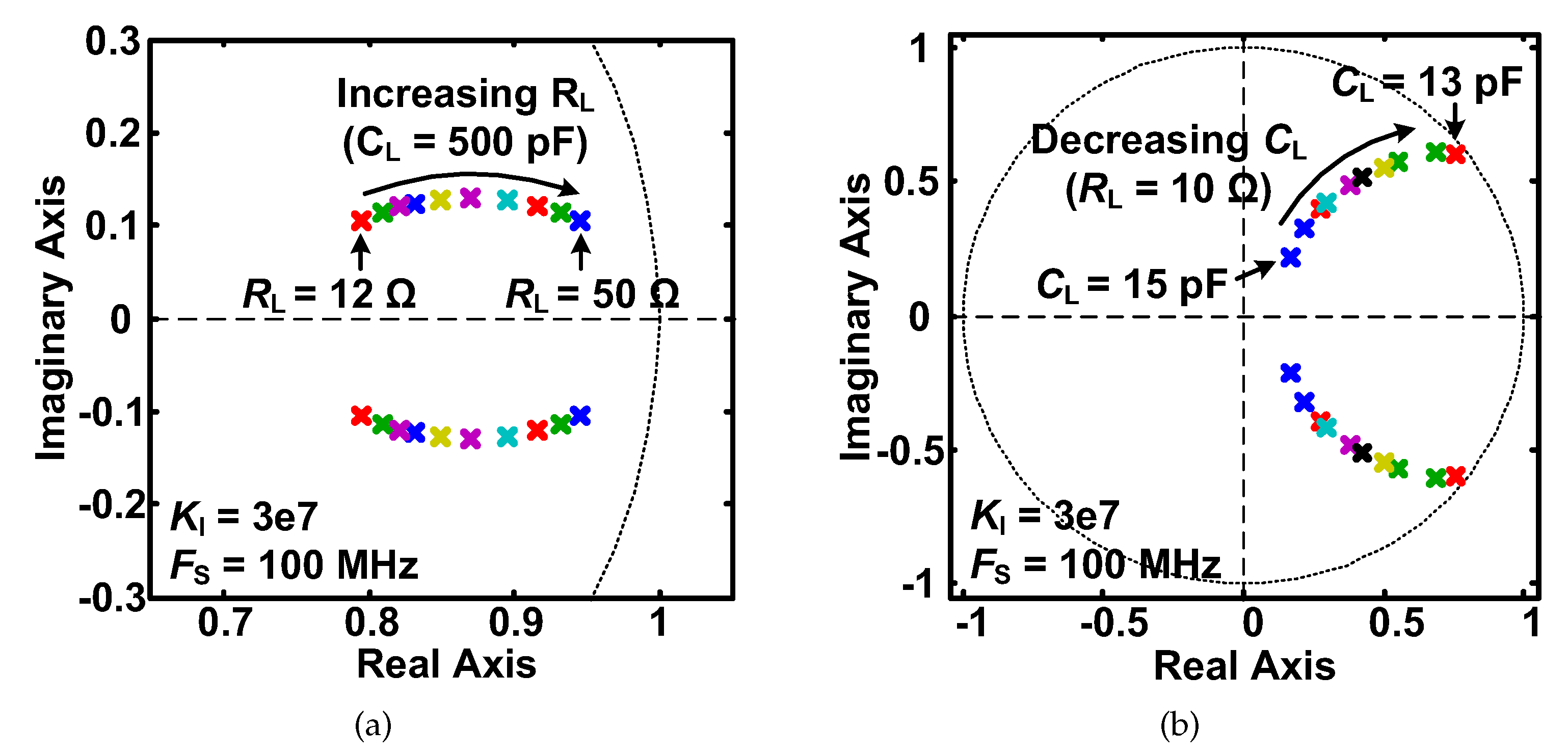

2.2. System Hybrid Model

3. Circuit Implementation

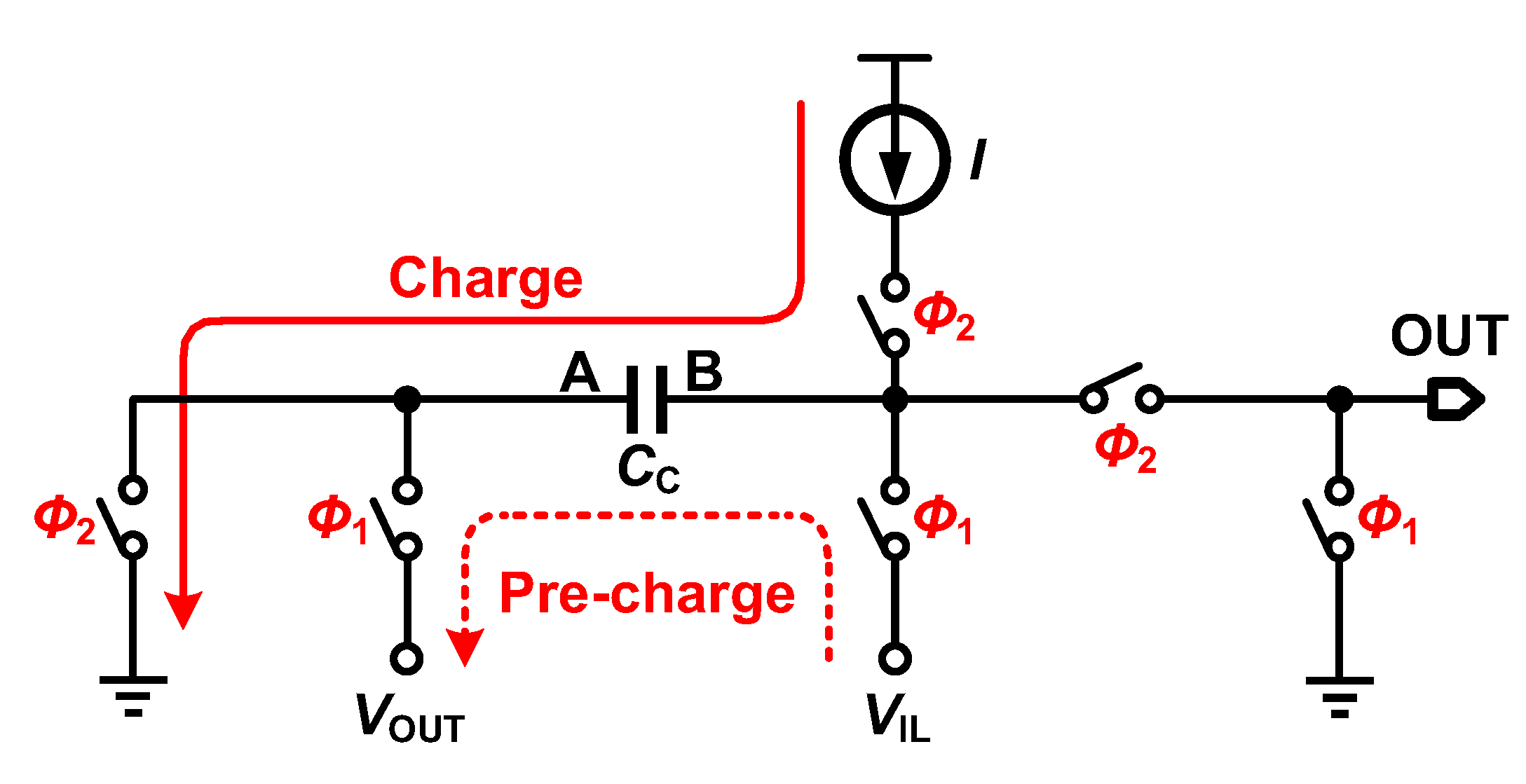

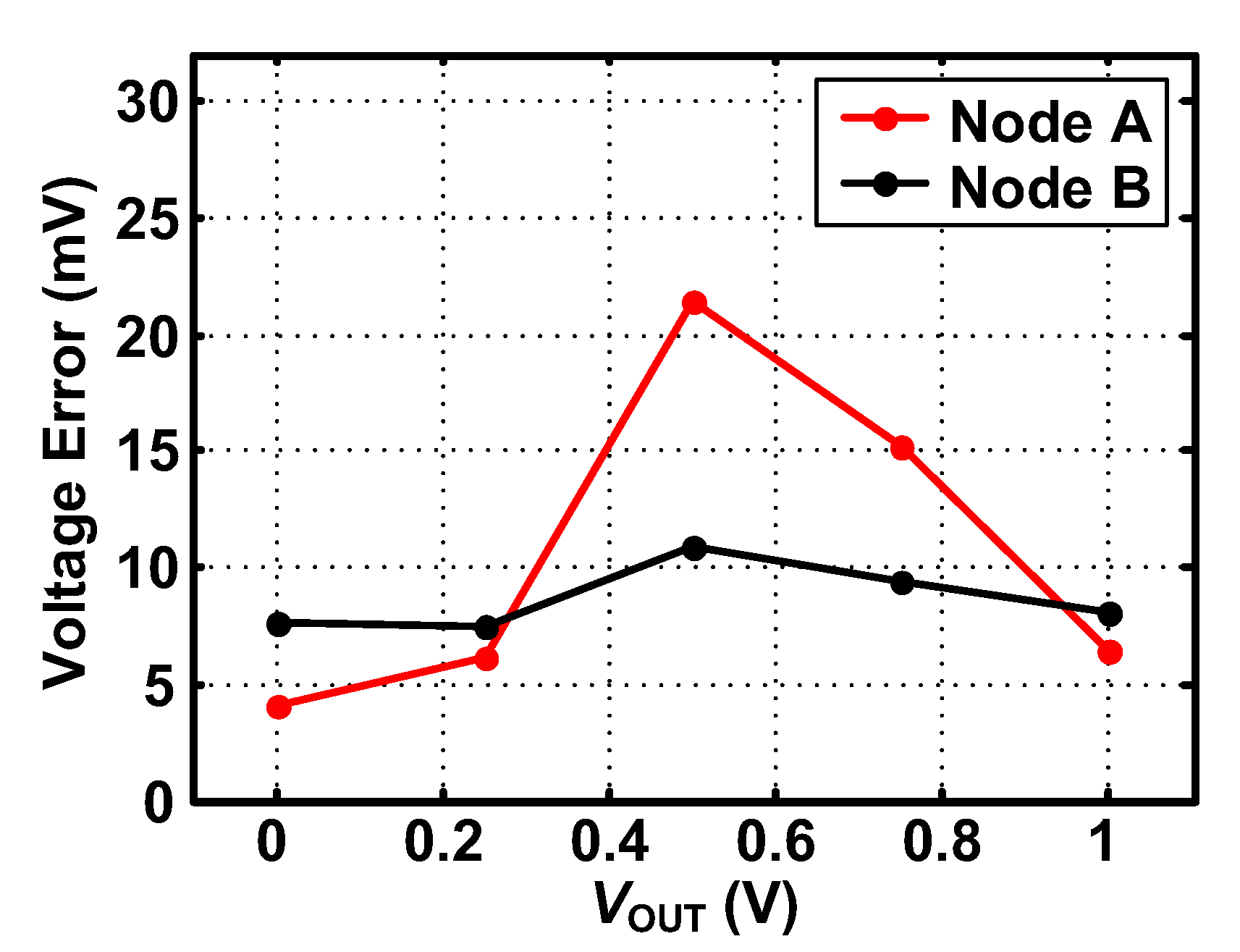

3.1. Voltage Sensor

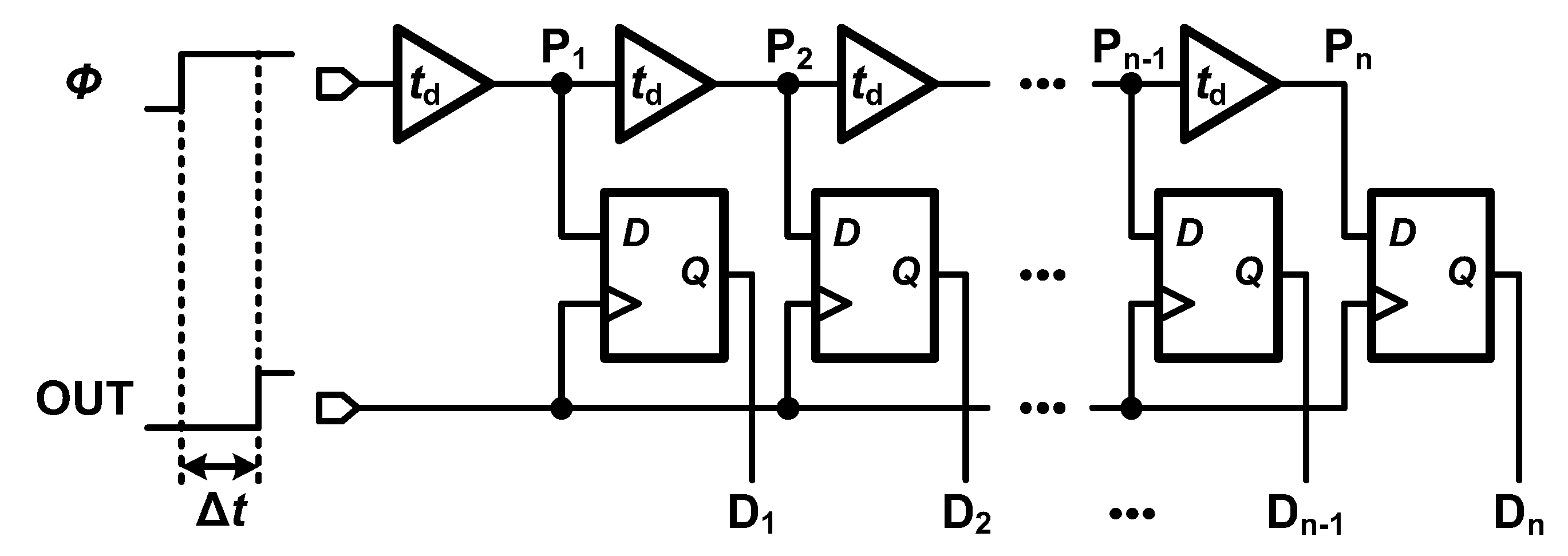

3.2. Time-to-Digital Converter

3.3. Digital Controller

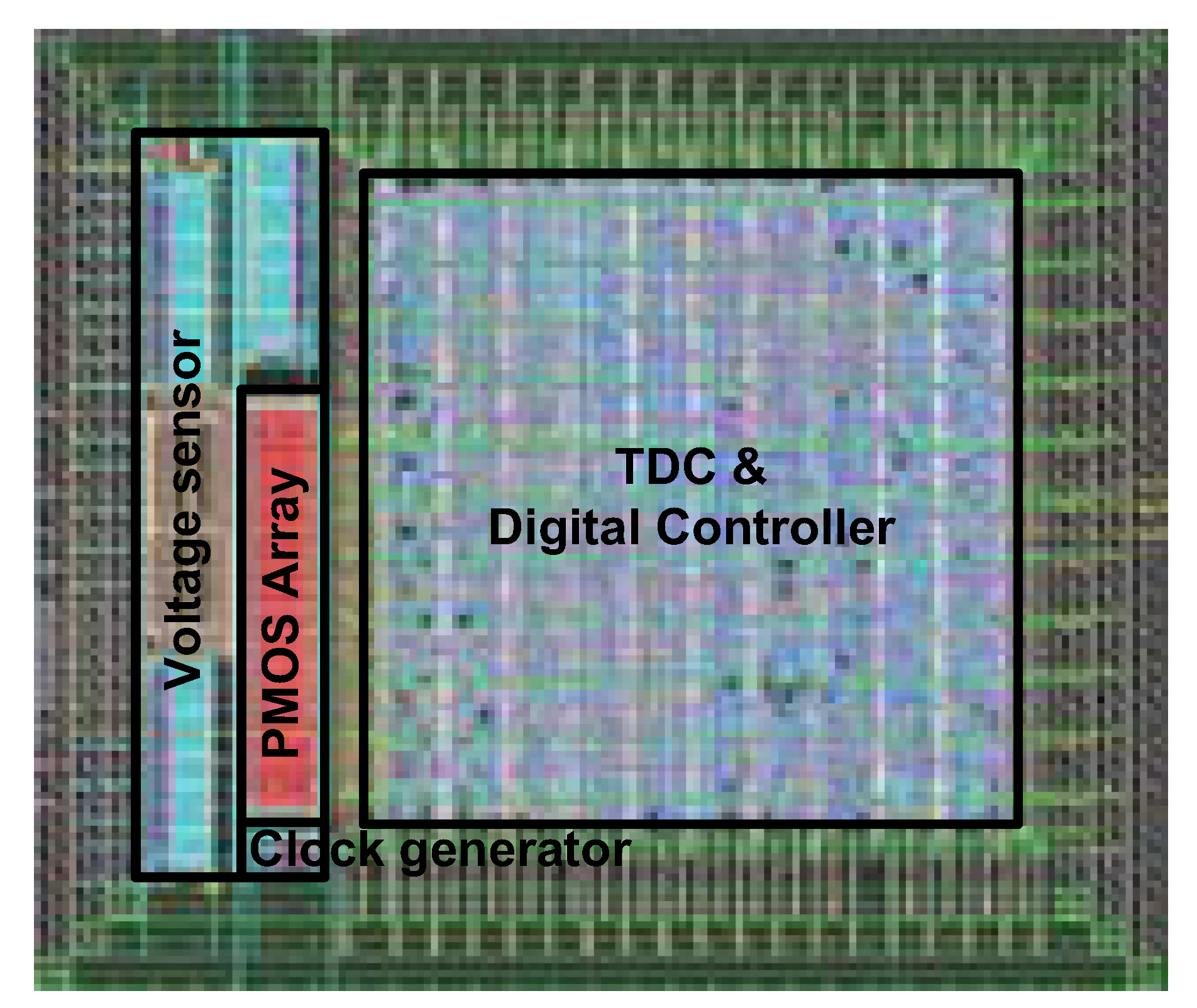

4. Simulation and Results

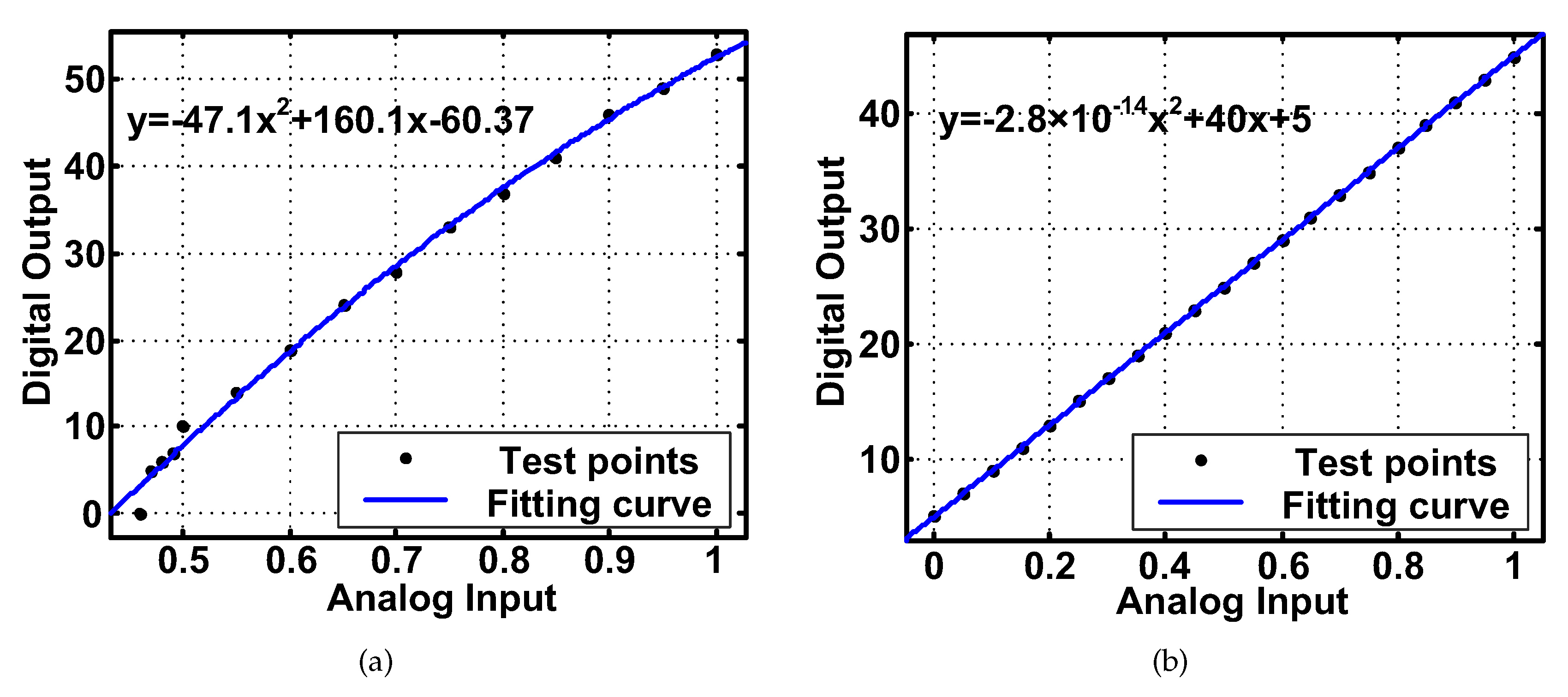

4.1. TDC-Based Signal Converter

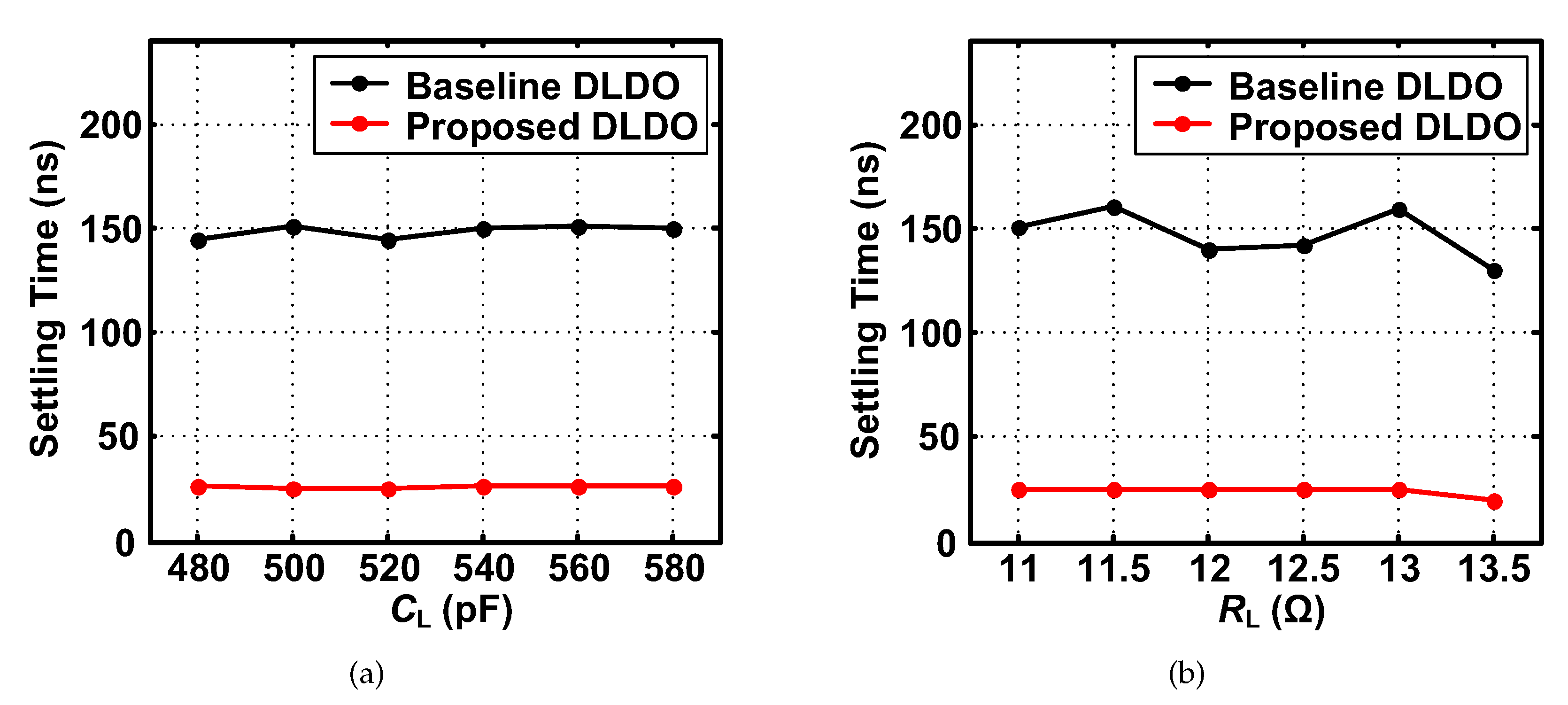

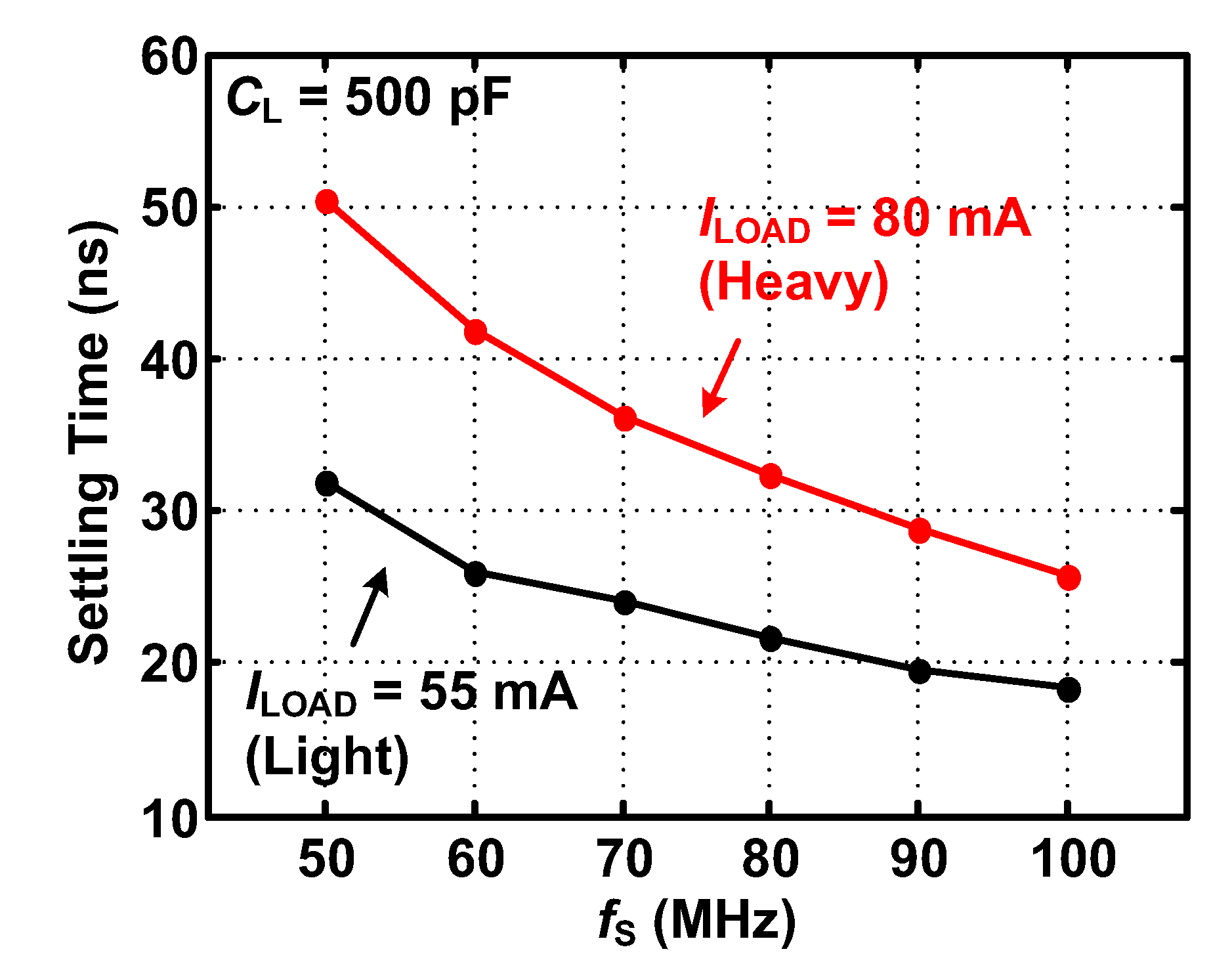

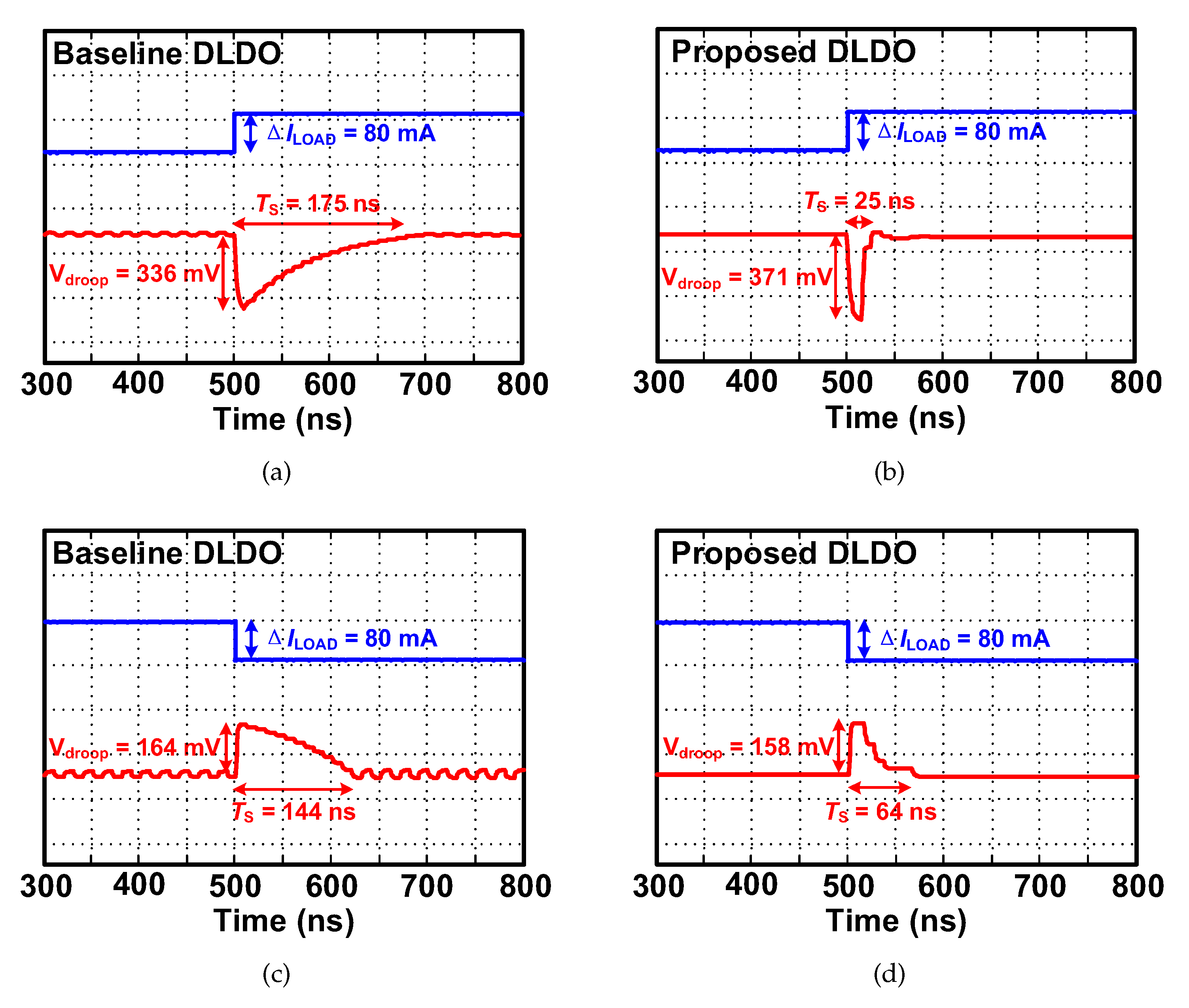

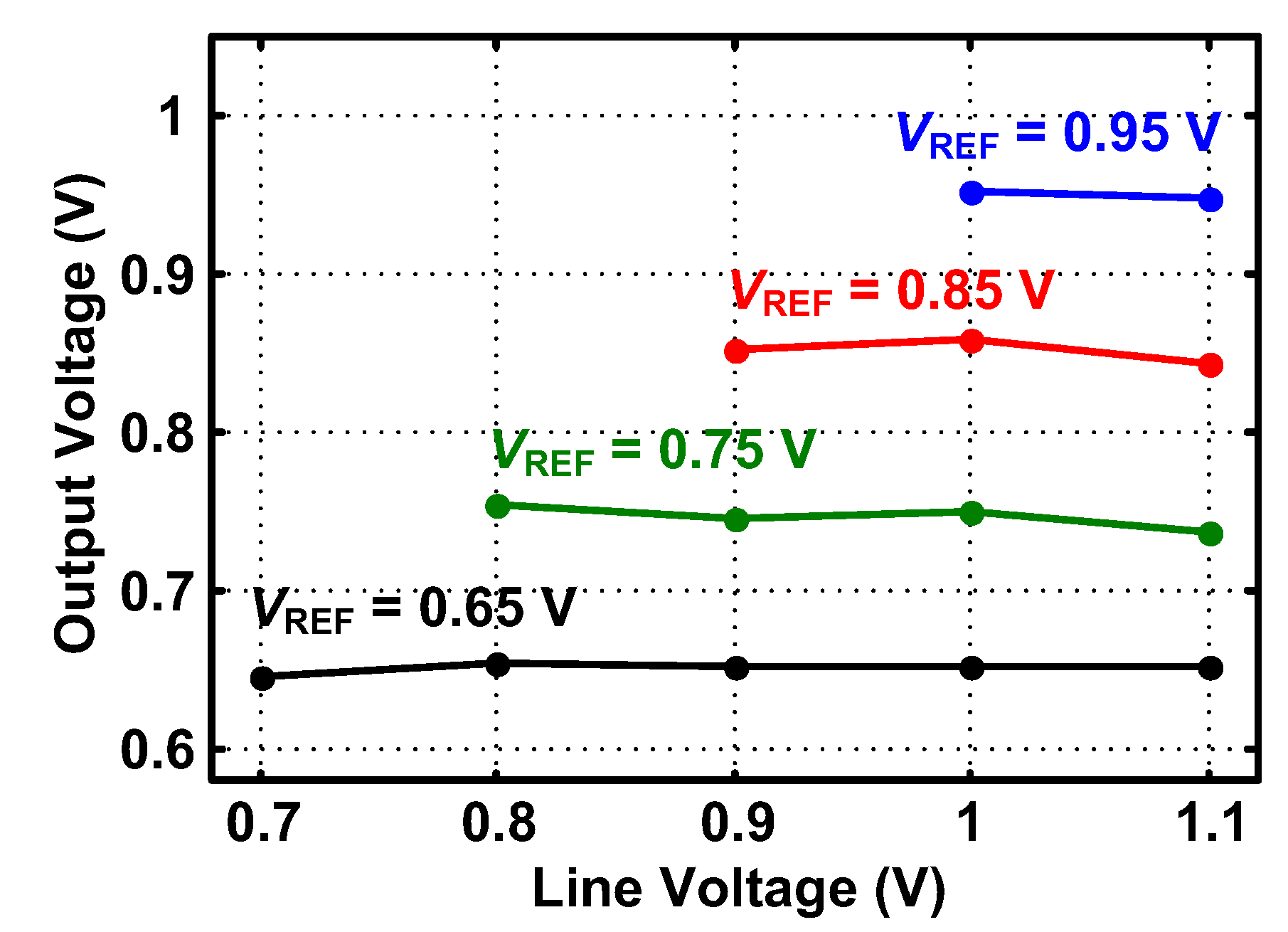

4.2. Proposed DLDO

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ma, X.; Lu, Y.; Martins, R.P.; Li, Q. A 0.4 V 430nA quiescent current NMOS digital LDO with NAND-based analog-assisted loop in 28 nm CMOS. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 306–308. [Google Scholar]

- Oh, T.J.; Hwang, I.C. A 110-nm CMOS 0.7-V input transient-enhanced digital low-dropout regulator with 99.98% current efficiency at 80-mA load. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 23, 1281–1286. [Google Scholar] [CrossRef]

- Li, Y.; Zhang, X.; Zhang, Z.; Lian, Y. A 0.45-to-1.2-V fully digital low-dropout voltage regulator with fast-transient controller for near/subthreshold circuits. IEEE Trans. Power Electron. 2015, 31, 6341–6350. [Google Scholar] [CrossRef]

- Yang, F.; Mok, P.K. A nanosecond-transient fine-grained digital LDO with multi-step switching scheme and asynchronous adaptive pipeline control. IEEE J. Solid-State Circuits 2017, 52, 2463–2474. [Google Scholar] [CrossRef]

- Huang, M.; Lu, Y.; Seng-Pan, U.; Martins, R.P. An output-capacitor-free analog-assisted digital low-dropout regulator with tri-loop control. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 342–343. [Google Scholar]

- Salem, L.G.; Warchall, J.; Mercier, P.P. A 100 nA-to-2 mA successive-approximation digital LDO with PD compensation and sub-LSB duty control achieving a 15.1 ns response time at 0.5 V. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 340–341. [Google Scholar]

- Okuma, Y.; Ishida, K.; Ryu, Y.; Zhang, X.; Chen, P.H.; Watanabe, K.; Sakurai, T. 0.5-V input digital LDO with 98.7% current efficiency and 2.7-μA quiescent current in 65nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 19–22 September 2010; pp. 1–4. [Google Scholar]

- Lee, J.; Bang, J.; Lim, Y.; Choi, J. A 0.5 VV IN, 0.29 ps-Transient-FOM, and Sub-2mV-Accuracy Adaptive-Sampling Digital LDO Using Single-VCO-Based Edge-Racing Time Quantizer. In Proceedings of the 2019 Symposium on VLSI Circuits, Kyoto, Japan, 9–14 June 2019; pp. C130–C131. [Google Scholar]

- Nasir, S.B.; Gangopadhyay, S.; Raychowdhury, A. A 0.13 μm fully digital low-dropout regulator with adaptive control and reduced dynamic stability for ultra-wide dynamic range. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Kundu, S.; Liu, M.; Wong, R.; Wen, S.J.; Kim, C.H. A fully integrated 40 pF output capacitor beat-frequency-quantizer-based digital LDO with built-in adaptive sampling and active voltage positioning. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 308–310. [Google Scholar]

- Nasir, S.B.; Sen, S.; Raychowdhury, A. Switched-mode-control based hybrid LDO for fine-grain power management of digital load circuits. IEEE J. Solid-State Circuits 2017, 53, 569–581. [Google Scholar] [CrossRef]

- Tsou, W.J.; Yang, W.H.; Lin, J.H.; Chen, H.; Chen, K.H.; Wey, C.L.; Tsai, T.Y. Digital low-dropout regulator with anti PVT-variation technique for dynamic voltage scaling and adaptive voltage scaling multicore processor. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 338–339. [Google Scholar]

- Kundu, S.; Liu, M.; Wen, S.J.; Wong, R.; Kim, C.H. A Fully Integrated Digital LDO With Built-In Adaptive Sampling and Active Voltage Positioning Using a Beat-Frequency Quantizer. IEEE J. Solid-State Circuits 2018, 54, 109–120. [Google Scholar] [CrossRef]

- Kim, D.; Seok, M. A fully integrated digital low-dropout regulator based on event-driven explicit time-coding architecture. IEEE J. Solid-State Circuits 2017, 52, 3071–3080. [Google Scholar] [CrossRef]

- Kim, D.; Kim, J.; Ham, H.; Seok, M. A 0.5 VV IN 1.44 mA-class event-driven digital LDO with a fully integrated 100 pF output capacitor. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 5–9 February 2017; pp. 346–347. [Google Scholar]

- Ding, Z.; Xu, X.; Song, H.; Rhee, W.; Wang, Z. Flash ADC-based digital LDO with non-linear decoder and exponential-ratio array. Electron. Lett. 2019, 55, 585–587. [Google Scholar] [CrossRef]

- Lim, C.; Mandal, D.; Bakkaloglu, B.; Kiaei, S. A 50-mA 99.2% peak current efficiency, 250-ns settling time digital low-dropout regulator with transient enhanced PI controller. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 2360–2370. [Google Scholar] [CrossRef]

- Otsuga, K.; Onouchi, M.; Igarashi, Y.; Ikeya, T.; Morita, S.; Ishibashi, K.; Yanagisawa, K. An on-chip 250 mA 40 nm CMOS digital LDO using dynamic sampling clock frequency scaling with offset-free TDC-based voltage sensor. In Proceedings of the 2012 IEEE International SOC Conference, Falls, NY, USA, 12–14 September 2012; pp. 11–14. [Google Scholar]

- Ojima, N.; Nakura, T.; Iizuka, T.; Asada, K. A synthesizable digital low-dropout regulator based on voltage-to-time conversion. In Proceedings of the 2018 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), Verona, Italy, 8–10 October 2018; pp. 55–58. [Google Scholar]

- Nasir, S.B.; Gangopadhyay, S.; Raychowdhury, A. All-digital low-dropout regulator with adaptive control and reduced dynamic stability for digital load circuits. IEEE Trans. Power Electron. 2016, 31, 8293–8302. [Google Scholar] [CrossRef]

- Hazucha, P.; Karnik, T.; Bloechel, B.A.; Parsons, C.; Finan, D.; Borkar, S. Area-efficient linear regulator with ultra-fast load regulation. IEEE J. Solid-State Circuits 2005, 40, 933–940. [Google Scholar] [CrossRef]

- Chen, L.; Cheng, Q.; Guo, J.; Chen, M. High-PSR CMOS LDO with embedded ripple feedforward and energy-efficient bandwidth extension. In Proceedings of the 2015 28th IEEE International System-on-Chip Conference (SOCC), Beijing, China, 8–11 September 2015; pp. 384–389. [Google Scholar]

- Ding, Z.; Rhee, W.; Wang, Z. A VCO-dedicated digital LDO with multi-comparator coarse loop and 1-bit ΔΣ fine loop for robust frequency generation. In Proceedings of the 2018 IEEE MTT-S International Wireless Symposium (IWS), Chengdu, China, 6–10 May 2018; pp. 1–4. [Google Scholar]

- Adorni, N.; Stanzione, S.; Boni, A. A 10-mA LDO With 16-nA IQ and Operating From 800-mV Supply. IEEE J. Solid-State Circuits 2019, 1–10. [Google Scholar] [CrossRef]

- Kim, S.J.; Kim, D.; Ham, H.; Kim, J.; Seok, M. A 67.1-ps FOM, 0.5-V-hybrid digital LDO with asynchronous feedforward control via slope detection and synchronous PI with state-based hysteresis clock switching. IEEE Solid-State Circuits Lett. 2018, 1, 130–133. [Google Scholar] [CrossRef]

| 1 | 38 | 0.02 | 10 | 500 pF | 32 MHz | 10 ps |

| Paper | 2015 [22] | 2018 [23] | 2019 [24] | 2018 [25] | This Work |

|---|---|---|---|---|---|

| Type | Analog | Digital | Analog | Digital | Digital |

| Process | 180 nm | 65 nm | 55 nm | 65 nm | 65 nm |

| Active area [mm] | 0.021 | NA | 0.042 | 0.012 | 0.017 |

| [V] | 1.3–1.8 | 0.8–1 | <0.8 | 0.5–1 | 0.7–1.1 |

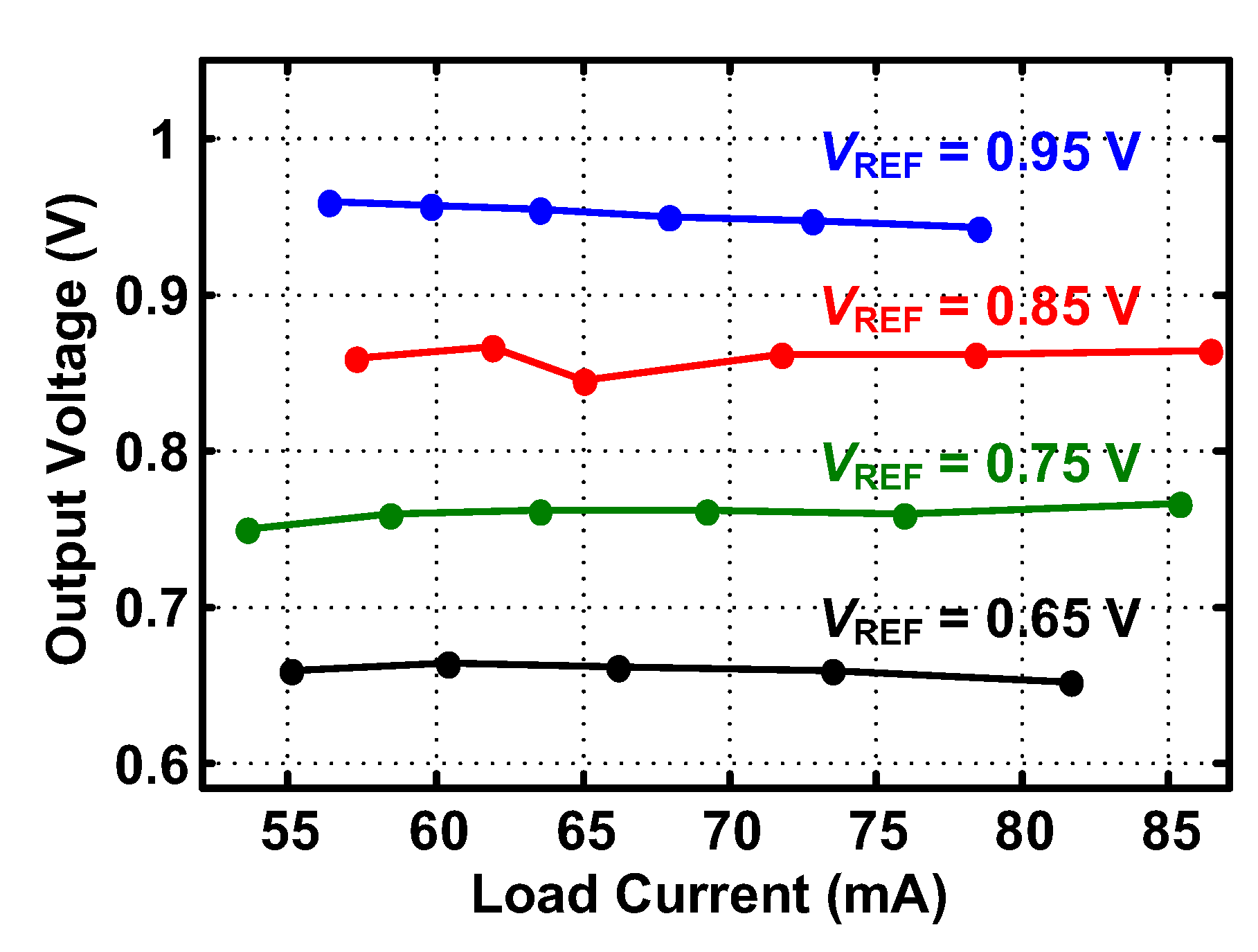

| [V] | 1.2 | 0.75–0.95 | 0.6 | 0.35–0.95 | 0.65–1.05 |

| Quiescent [A] | 10 | 24 | 0.016 | 45.2 | 495 |

| [mA] | 25 | 13 | 10 | 2.8 | 120 |

| Peak current efficiency [%] | 99.9 | 99.8 | 99.8 | 98.4 | 99.6 |

| Line regulation [mV/V] | 0.5 | NA | 0.5 | NA | 15 |

| Load regulation [mV/mA] | 0.14 | NA | 1.05 | NA | 0.6 |

| Load capacitor [nF] | 4700 | 0.2 | 1000 | 0.1 | 0.5 |

| Max voltage droop [mV] @ Load step | 2 @ 25 mA | 100 @ 6 mA | 70 @ 10 mA | 46 @ 1.76 mA | 371 @ 80 mA |

| Response time * [ns] | 376 | 3.3 | 7000 | 2.63 | 2.1 |

| FOM ** [ps] | 150 | 13.3 | 11.4 | 67.1 | 8.7 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, H.; Wan, P.; Geng, J.; Liu, Z.; Chen, Z. A Fast Transient Response Digital LDO with a TDC-Based Signal Converter. Electronics 2020, 9, 132. https://doi.org/10.3390/electronics9010132

Zhang H, Wan P, Geng J, Liu Z, Chen Z. A Fast Transient Response Digital LDO with a TDC-Based Signal Converter. Electronics. 2020; 9(1):132. https://doi.org/10.3390/electronics9010132

Chicago/Turabian StyleZhang, Hongda, Peiyuan Wan, Jiarong Geng, Zhaozhe Liu, and Zhijie Chen. 2020. "A Fast Transient Response Digital LDO with a TDC-Based Signal Converter" Electronics 9, no. 1: 132. https://doi.org/10.3390/electronics9010132

APA StyleZhang, H., Wan, P., Geng, J., Liu, Z., & Chen, Z. (2020). A Fast Transient Response Digital LDO with a TDC-Based Signal Converter. Electronics, 9(1), 132. https://doi.org/10.3390/electronics9010132