Active Power Decoupling Design of a Single-Phase AC–DC Converter

Abstract

:1. Introduction

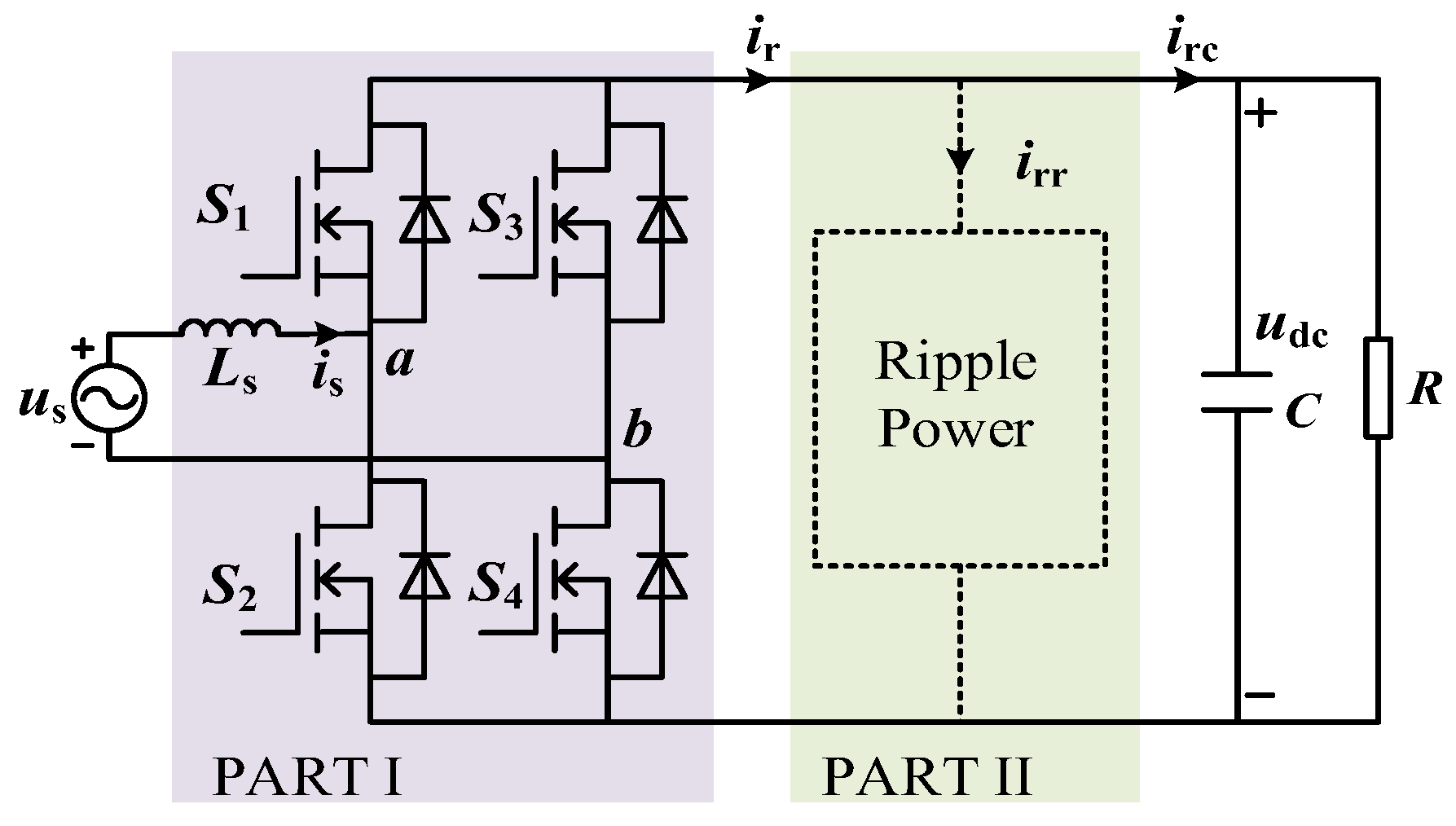

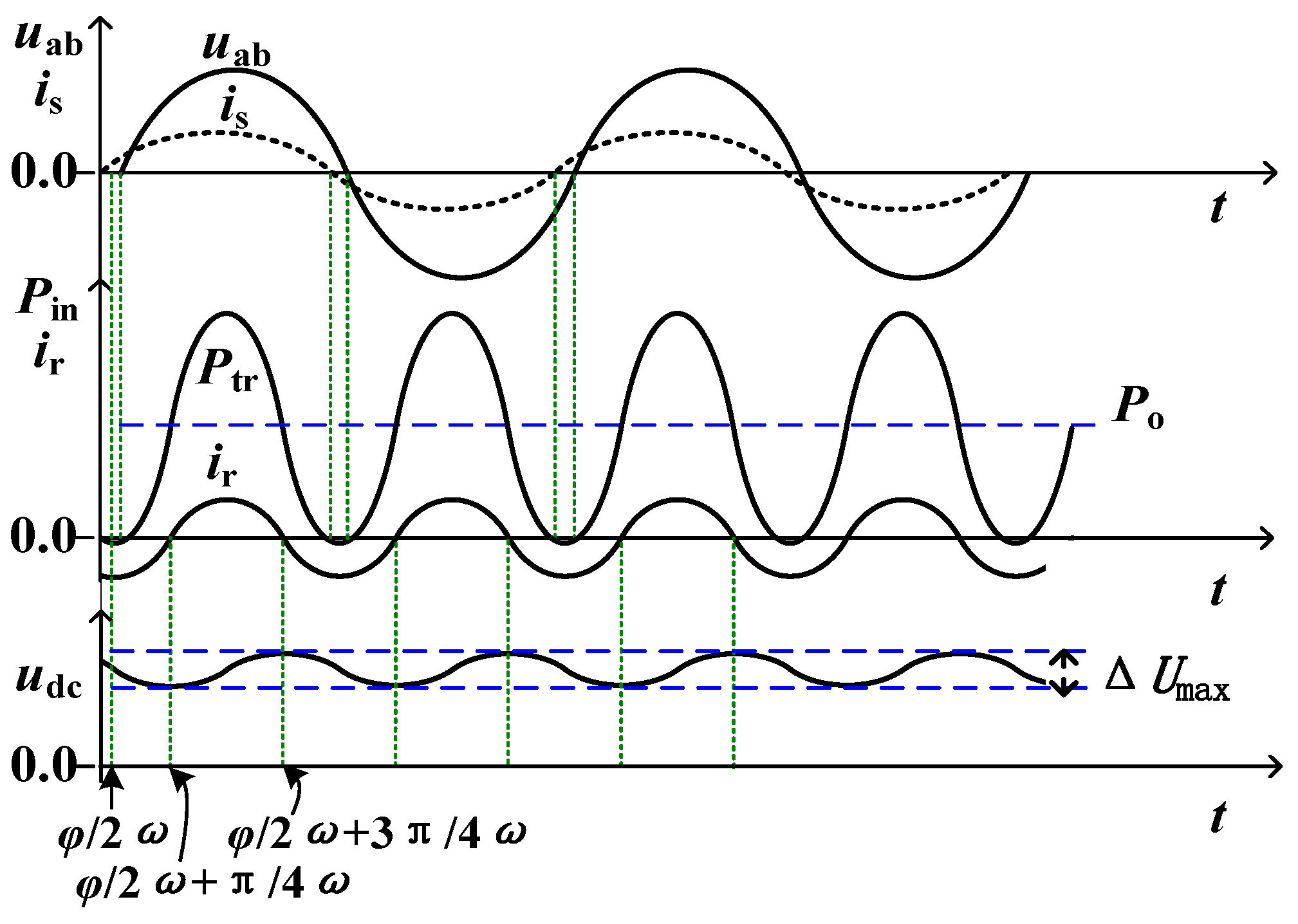

2. Power Analysis of a Single-Phase Rectifier

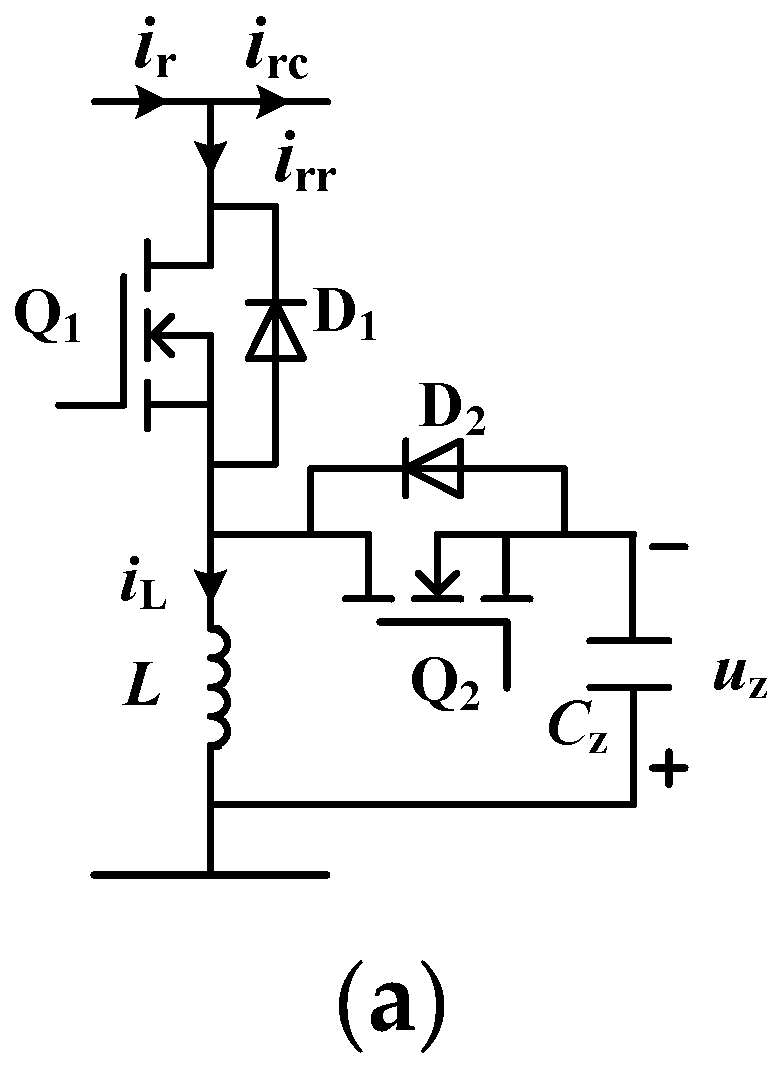

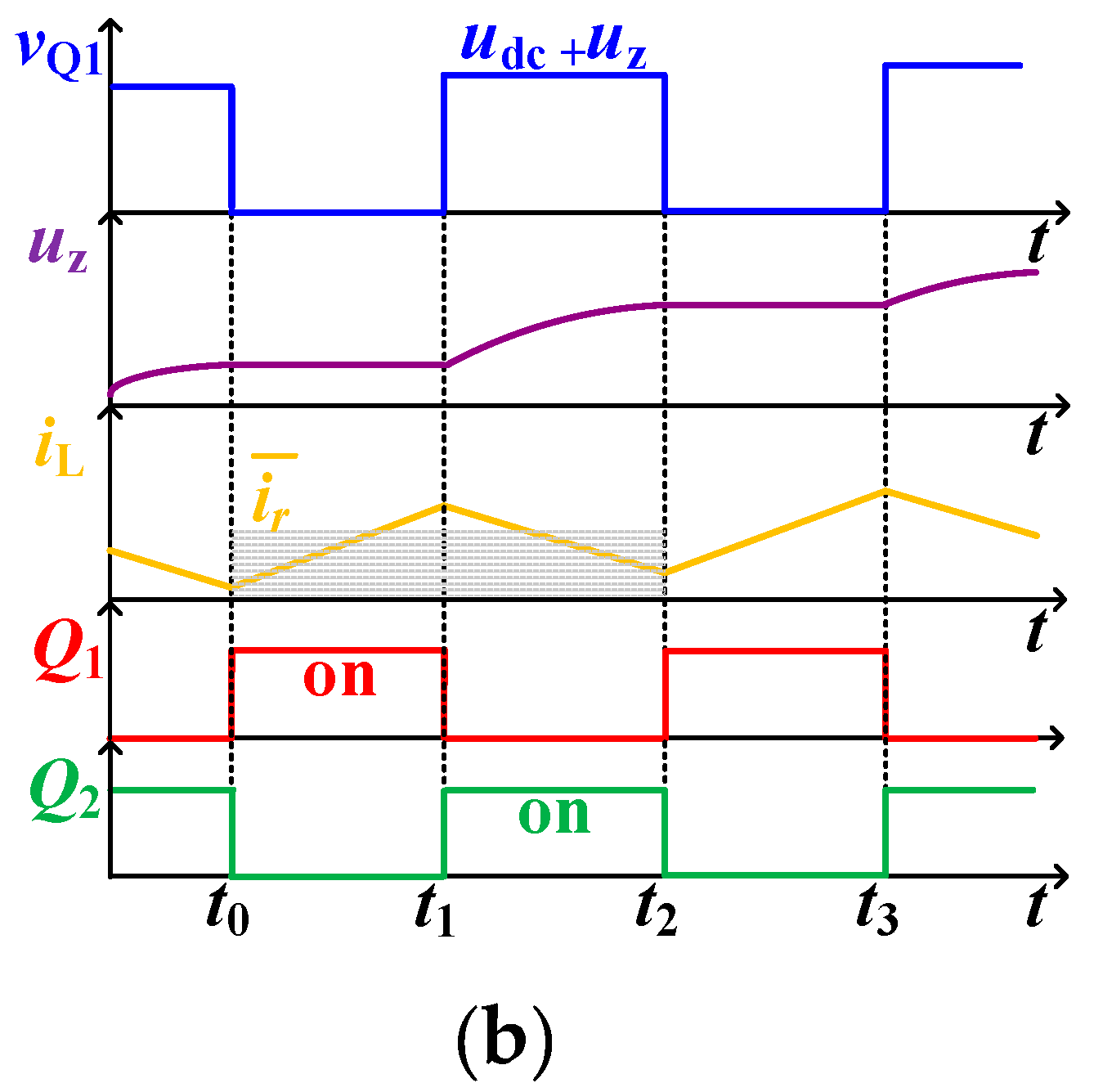

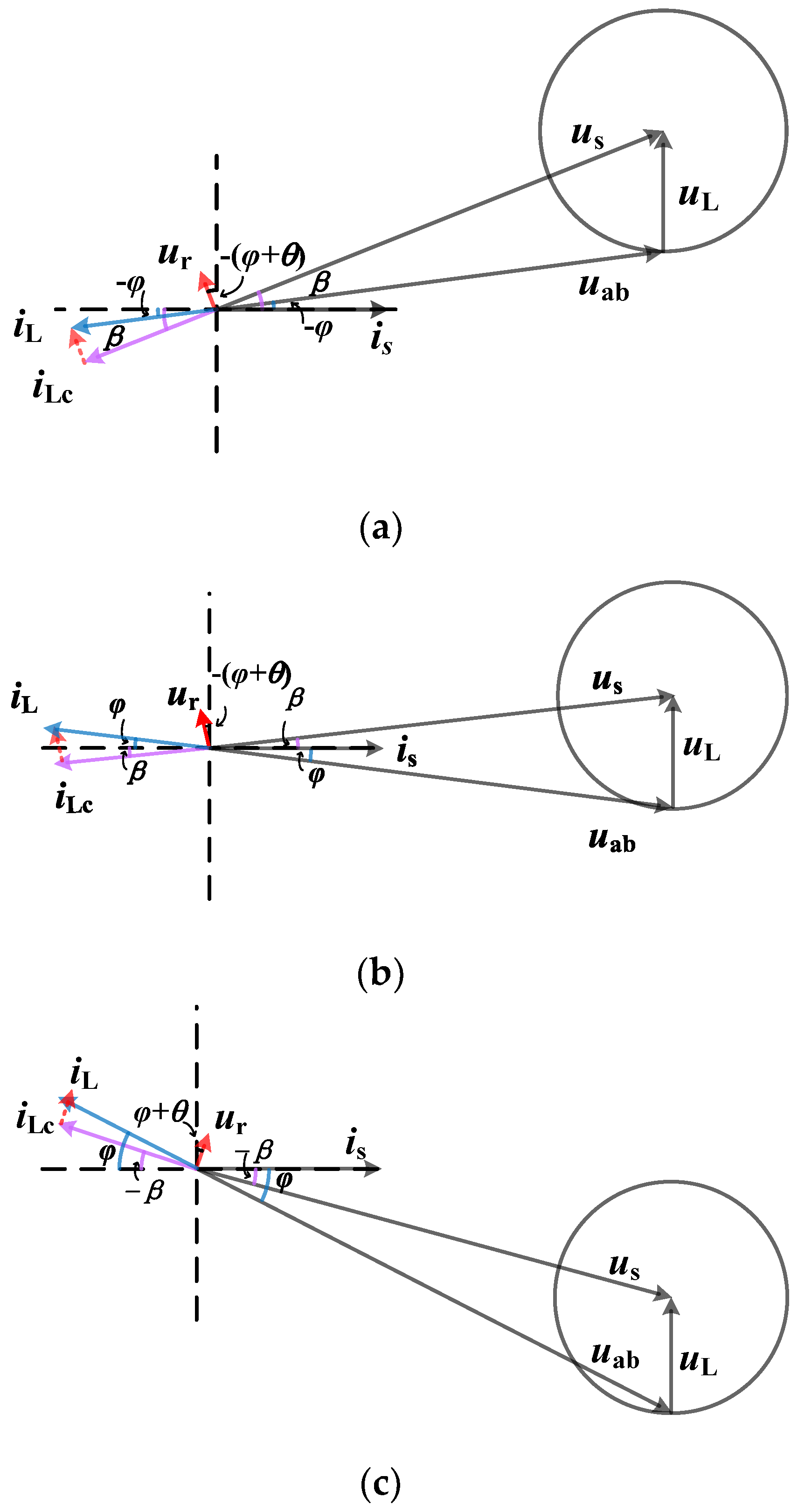

3. Analysis of an Active Power Decoupling Circuit

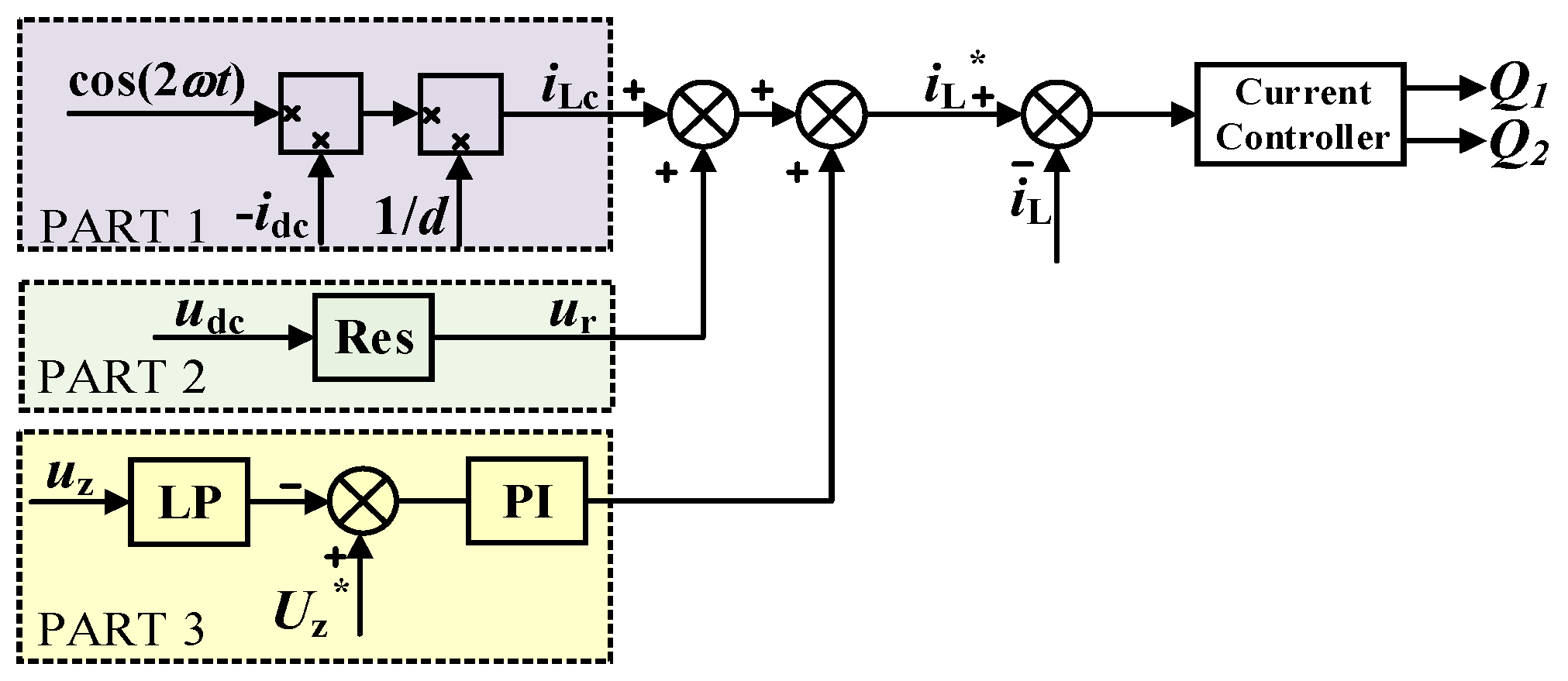

4. Control System Design

5. Parameter Design

5.1. Inductance Design of the Power Decoupling Circuit

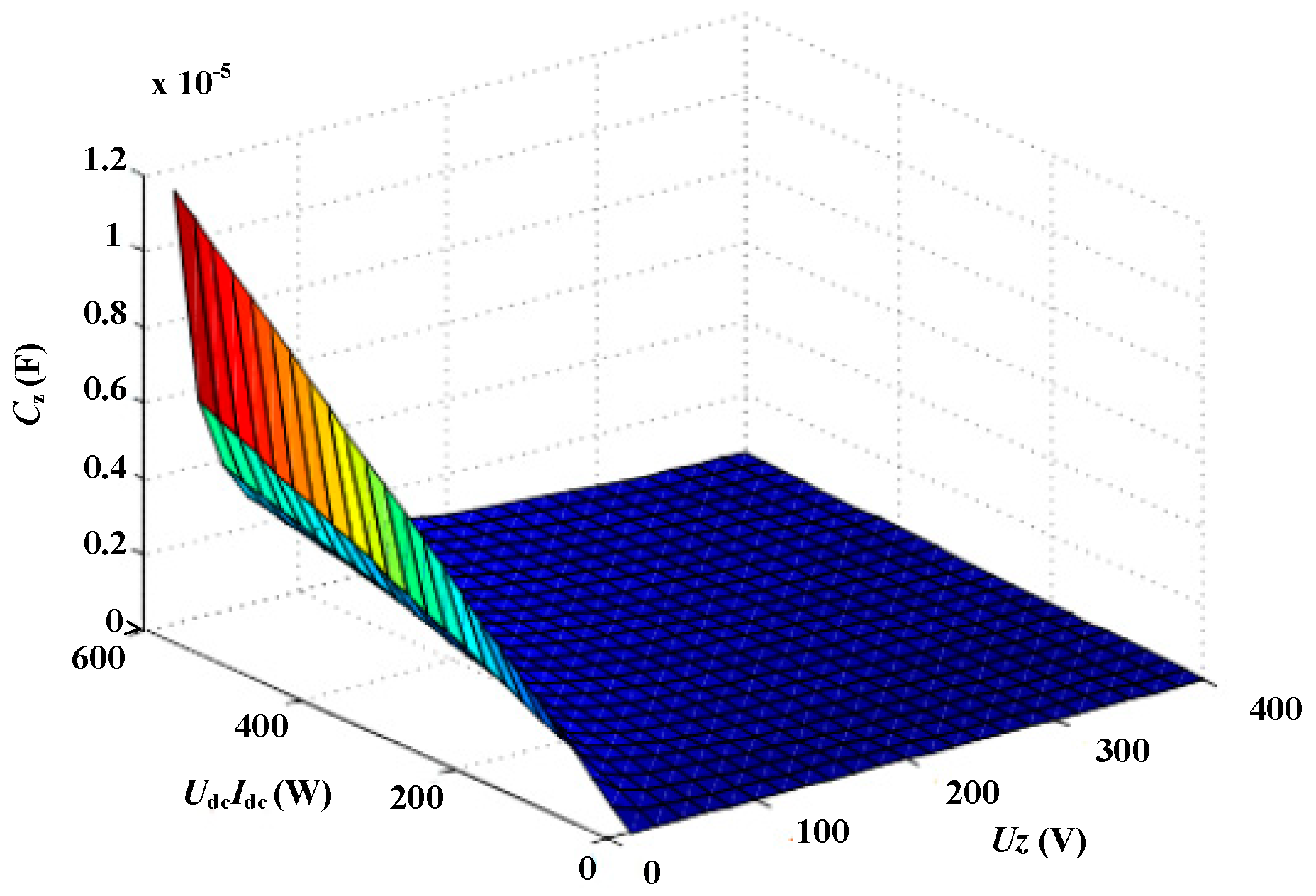

5.2. Capacitance Design of the Power Decoupling Circuit

6. Simulation and Experiment

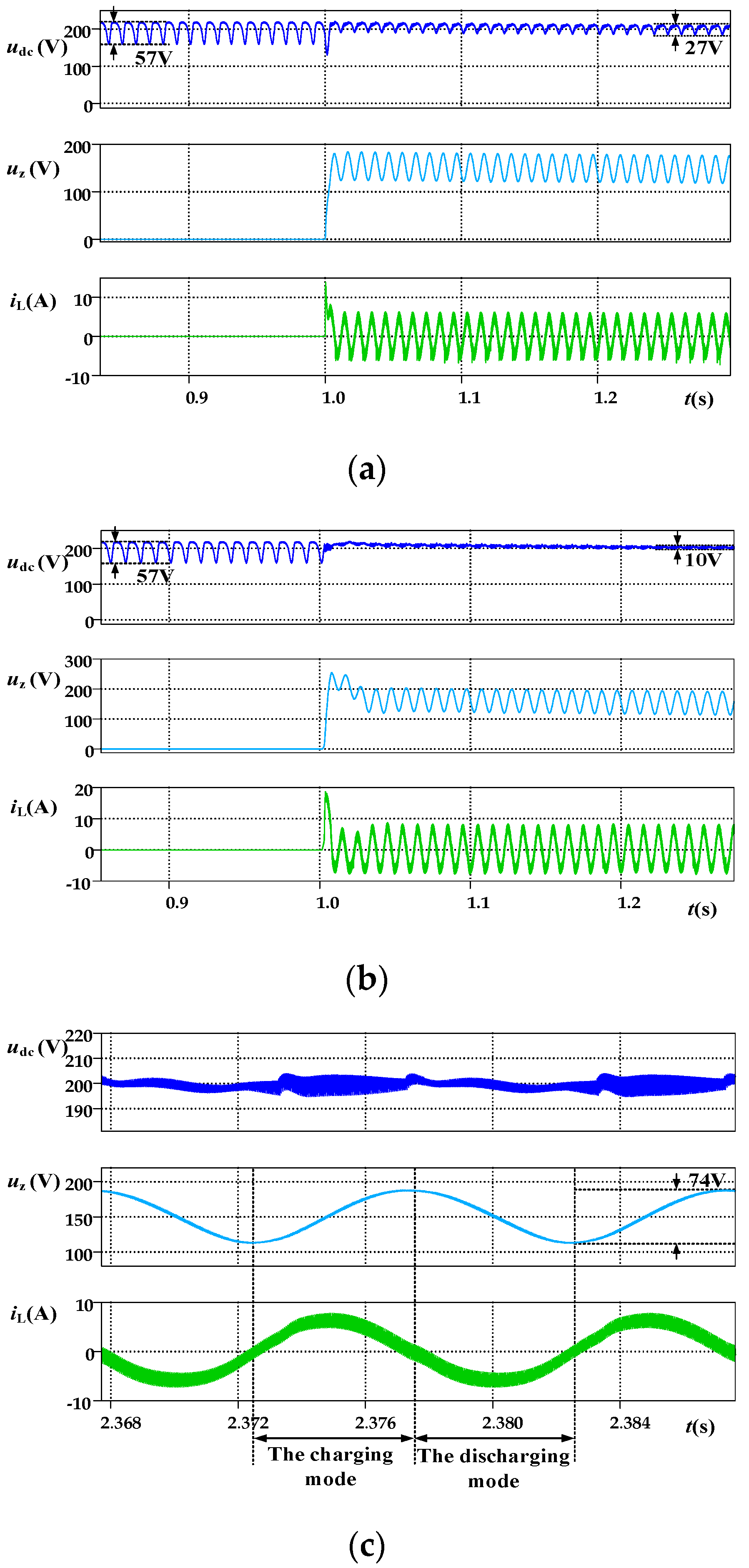

6.1. Simulation Verification

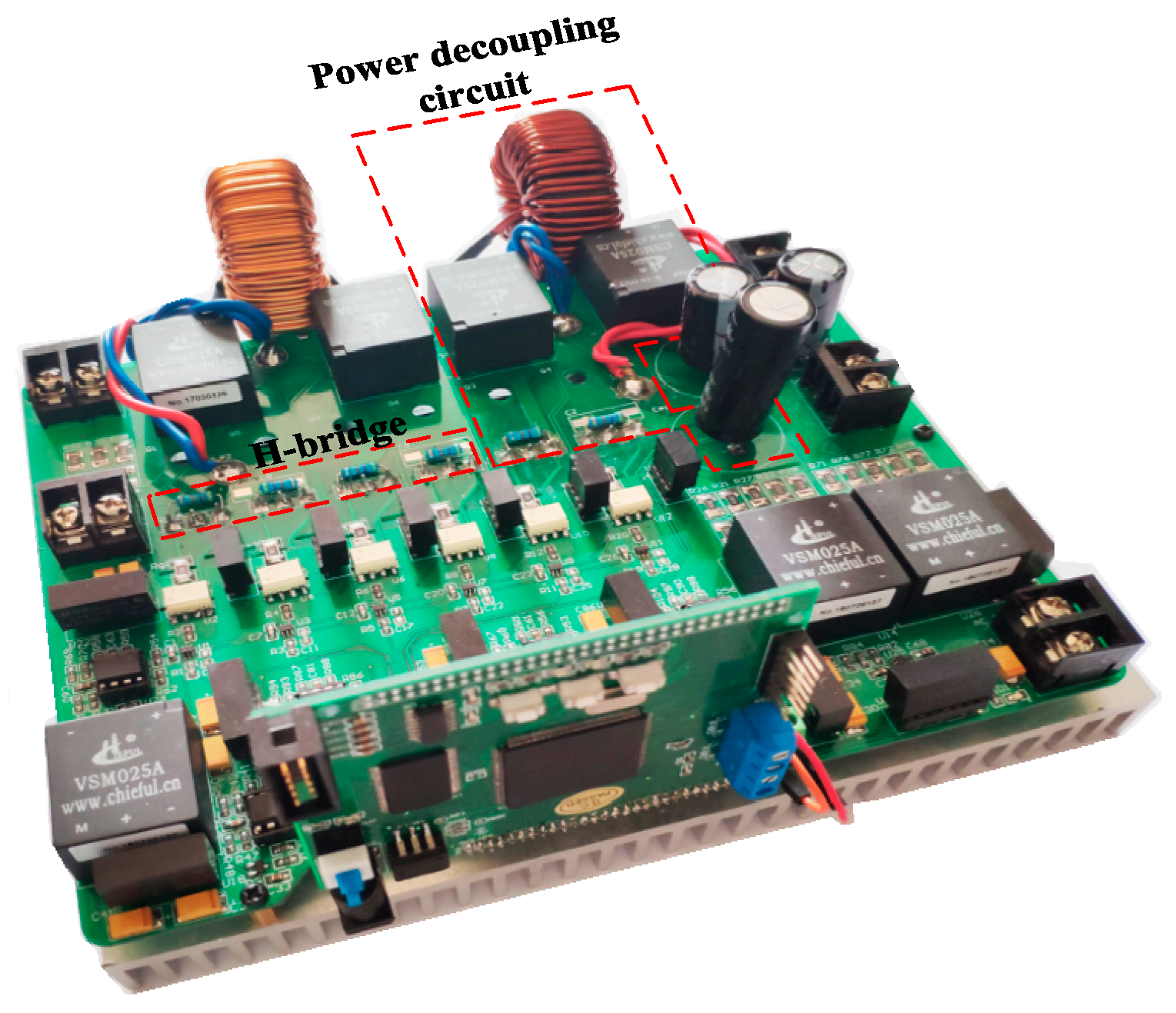

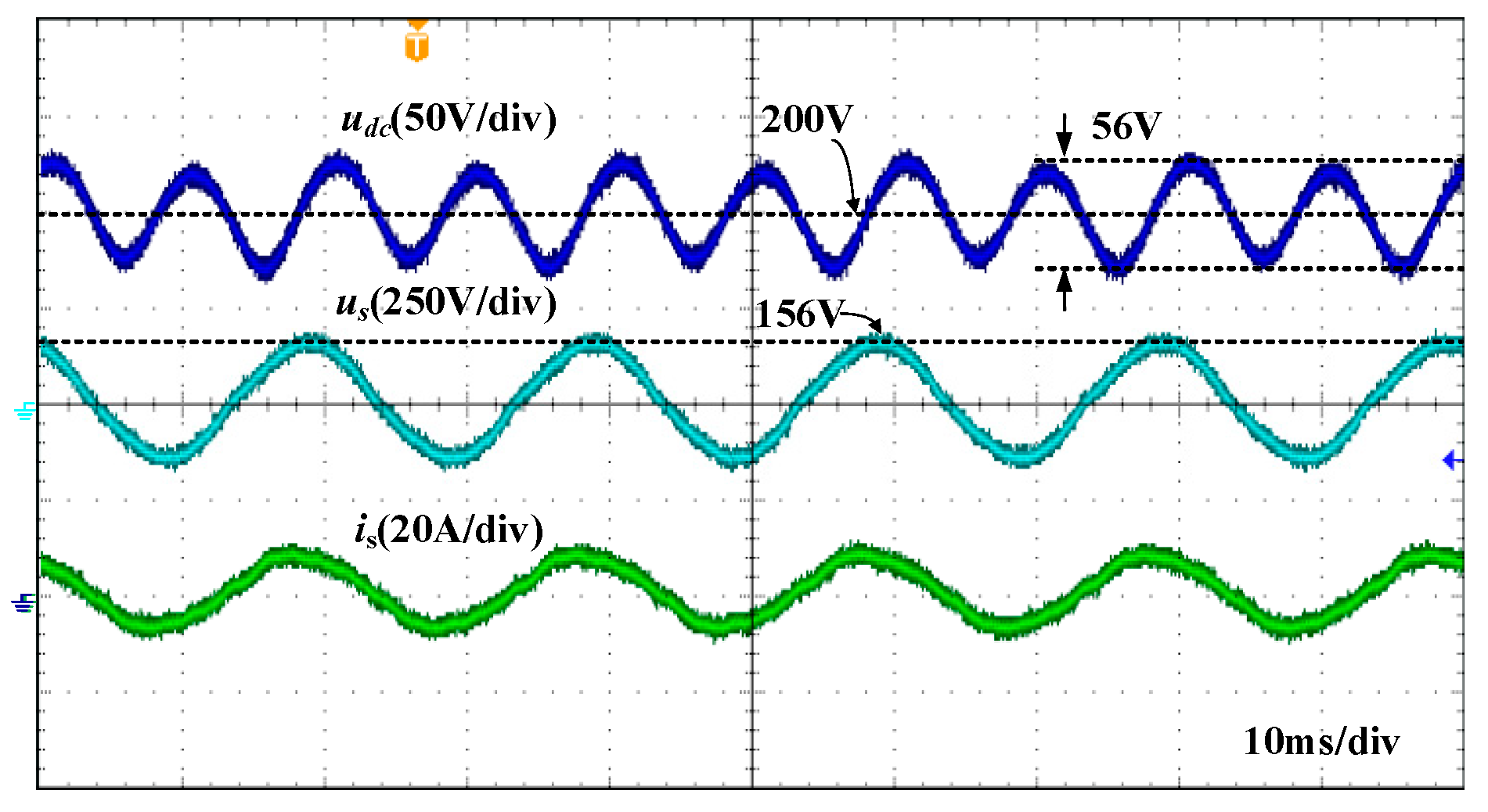

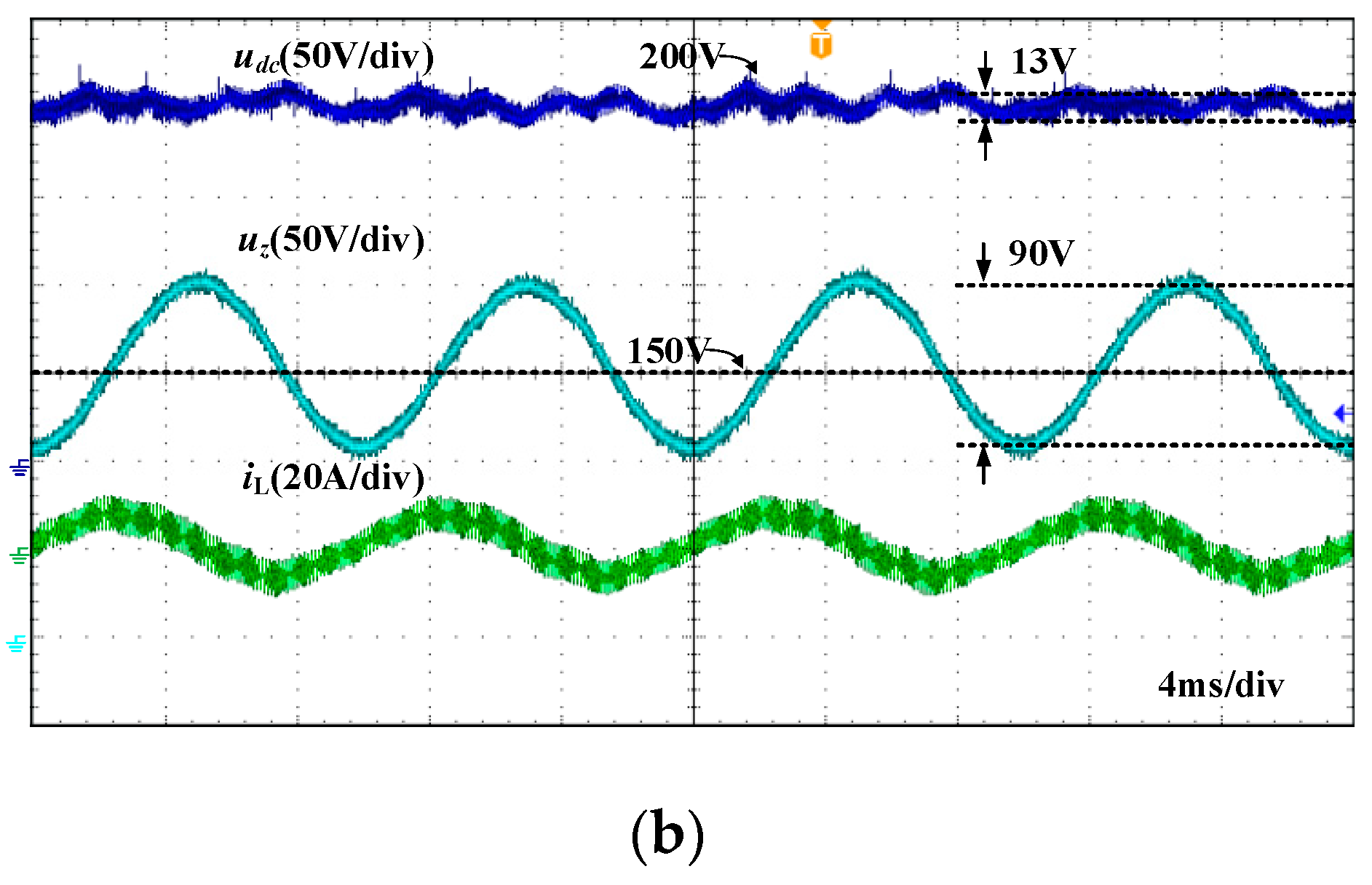

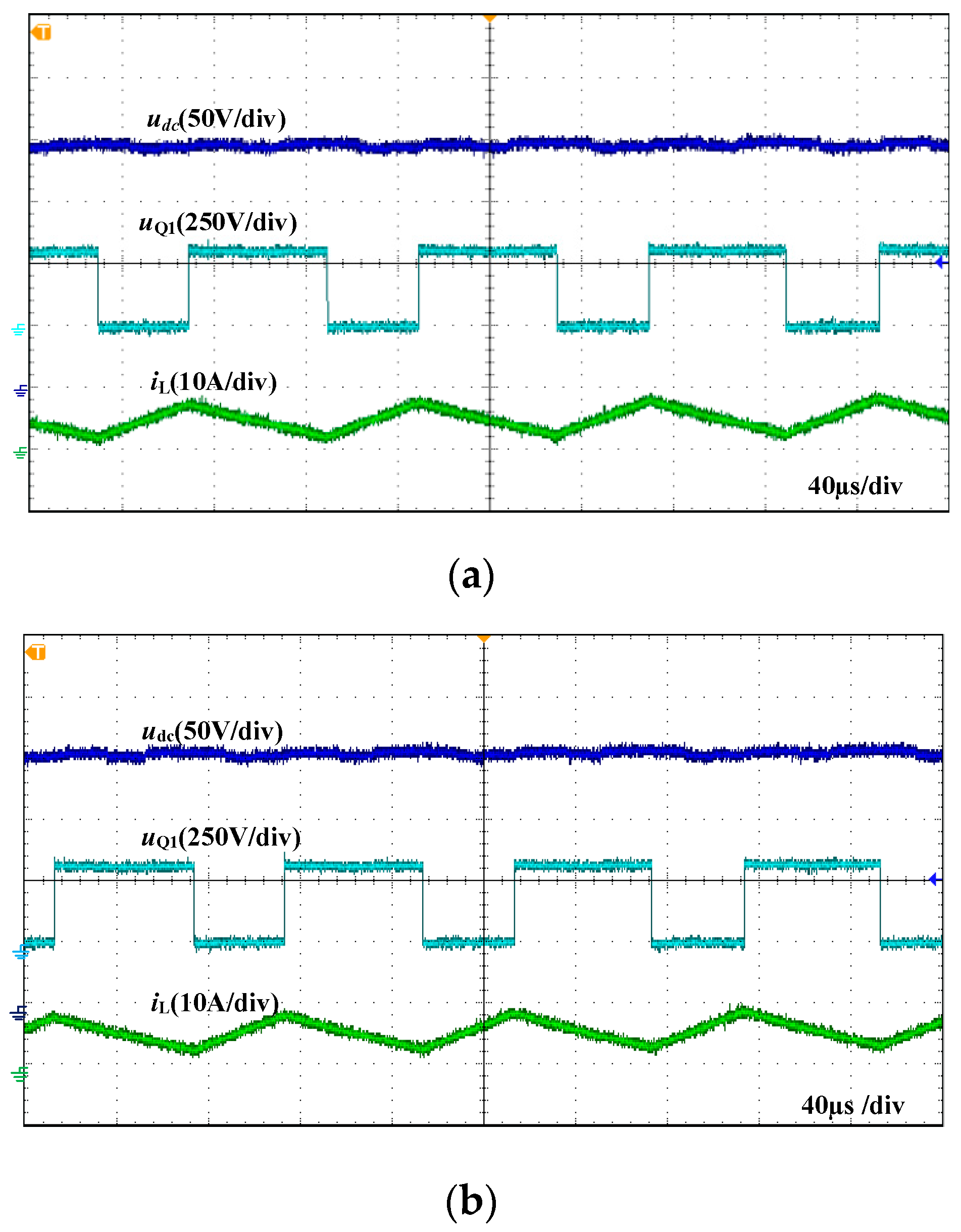

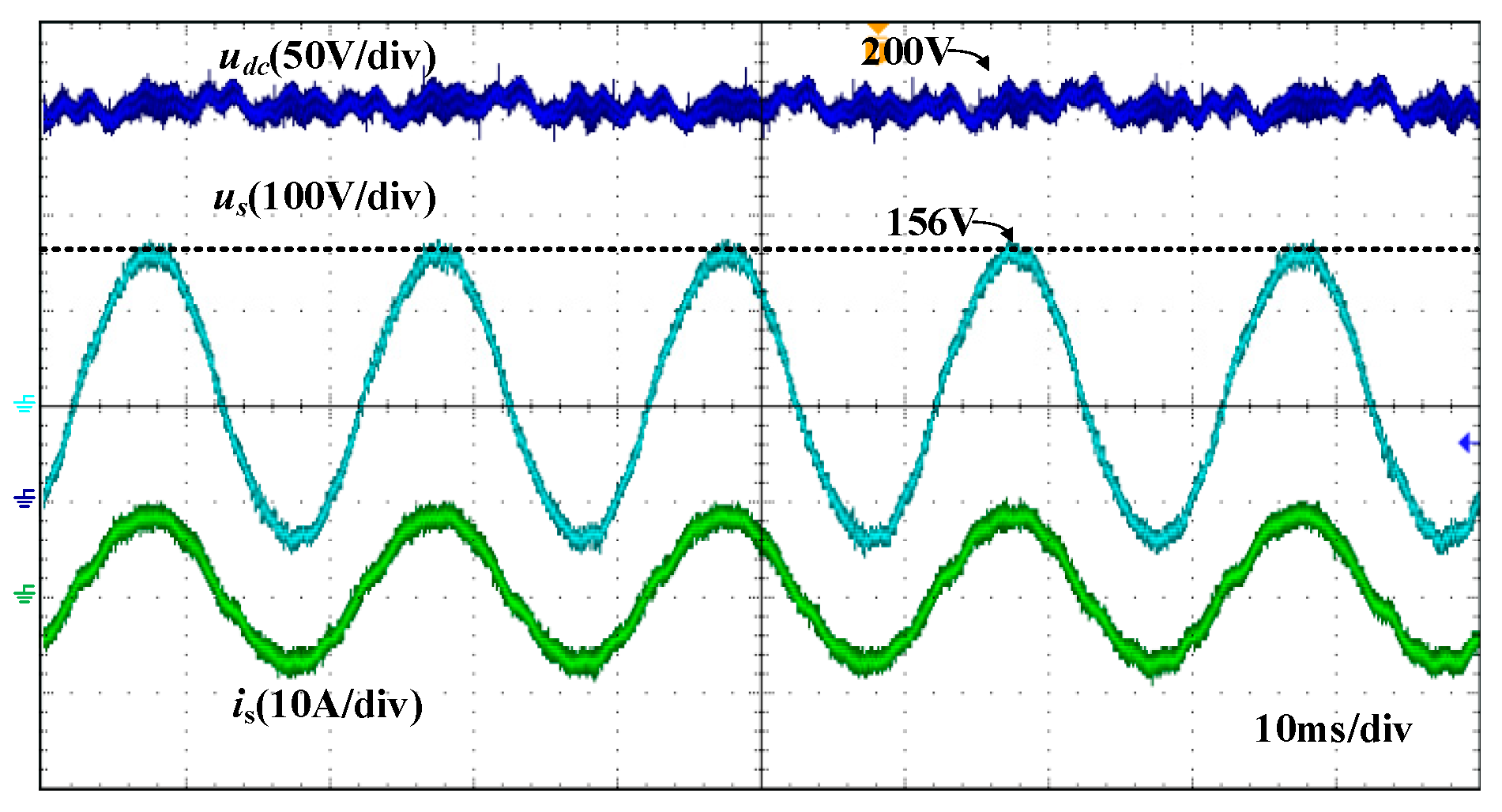

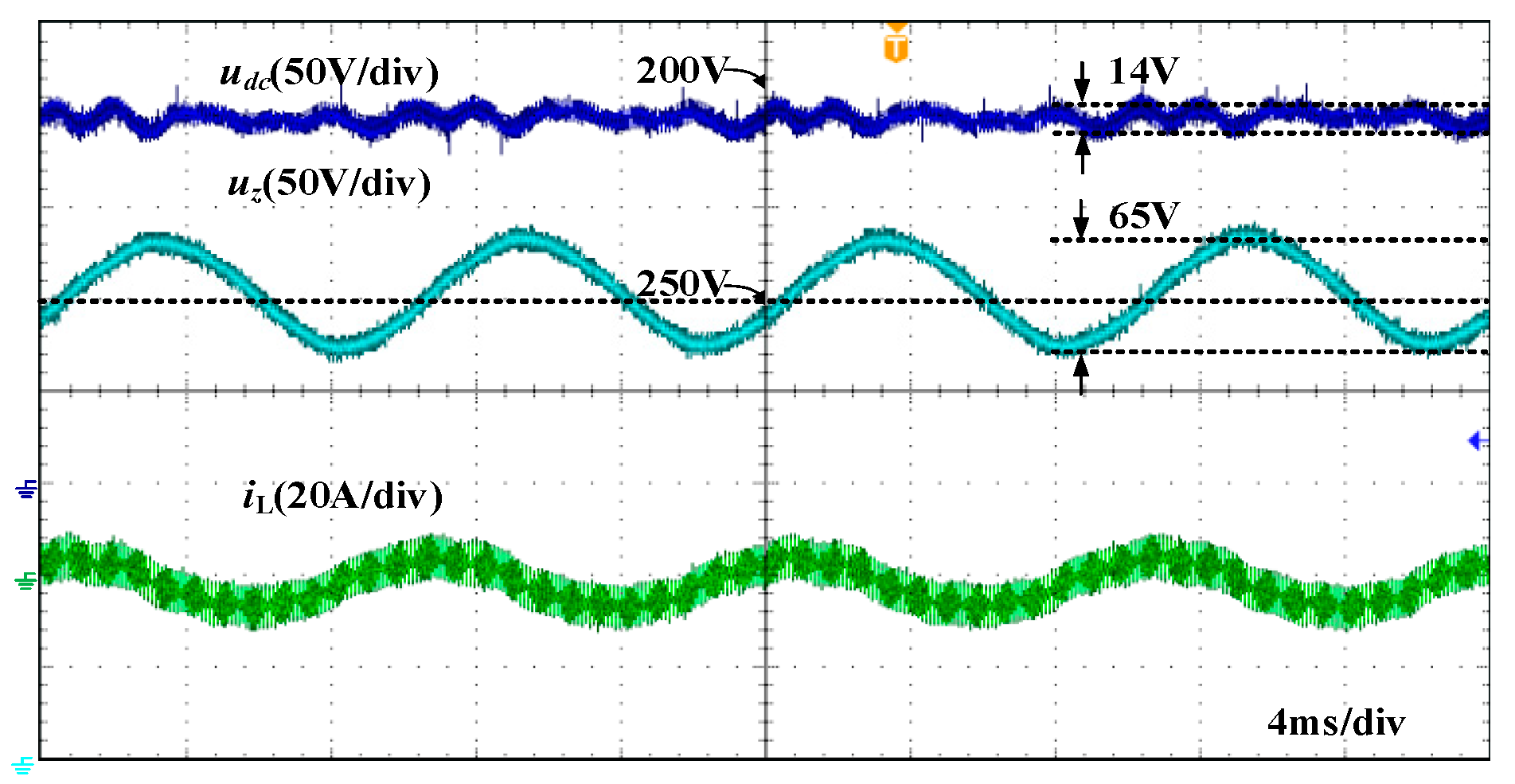

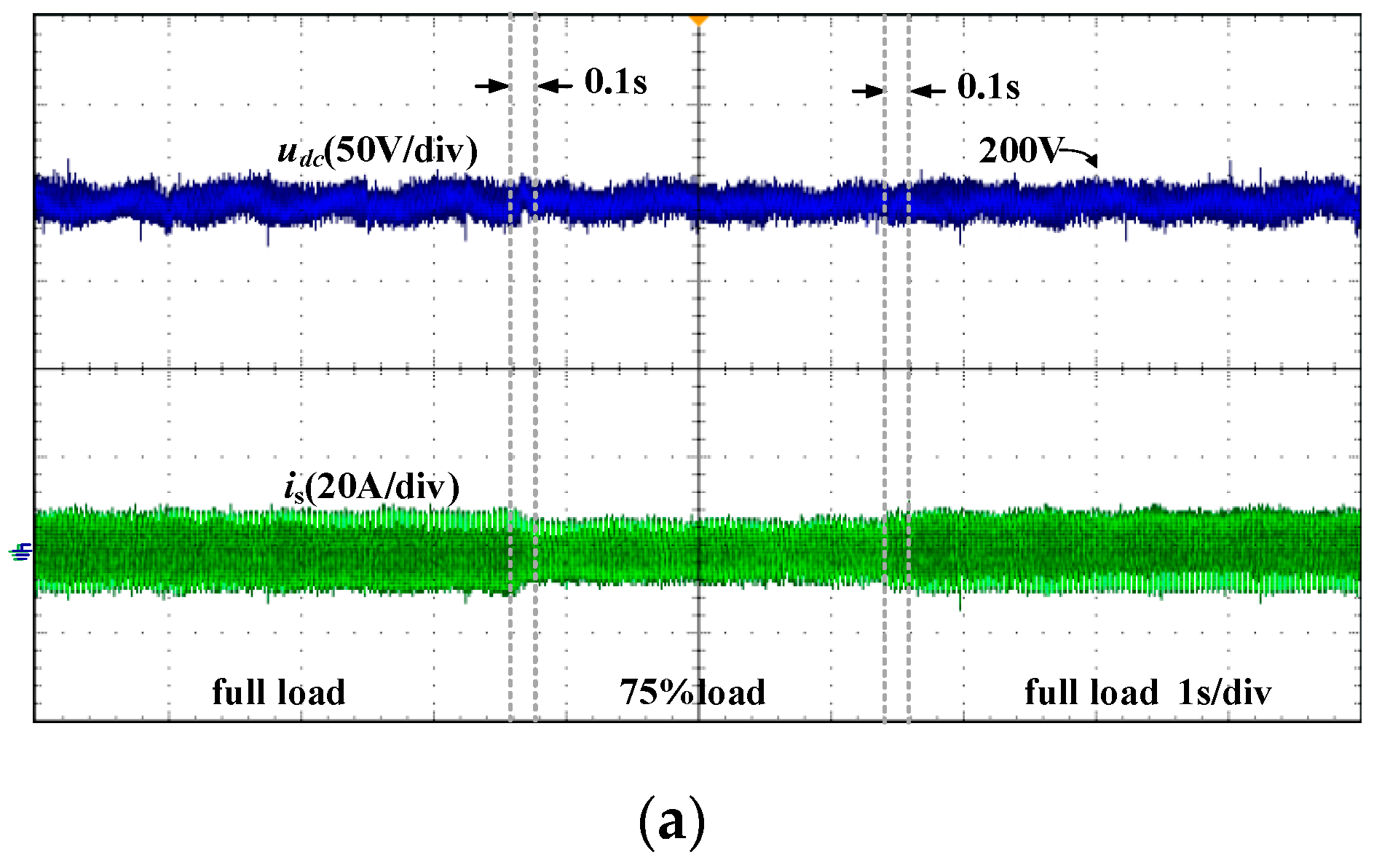

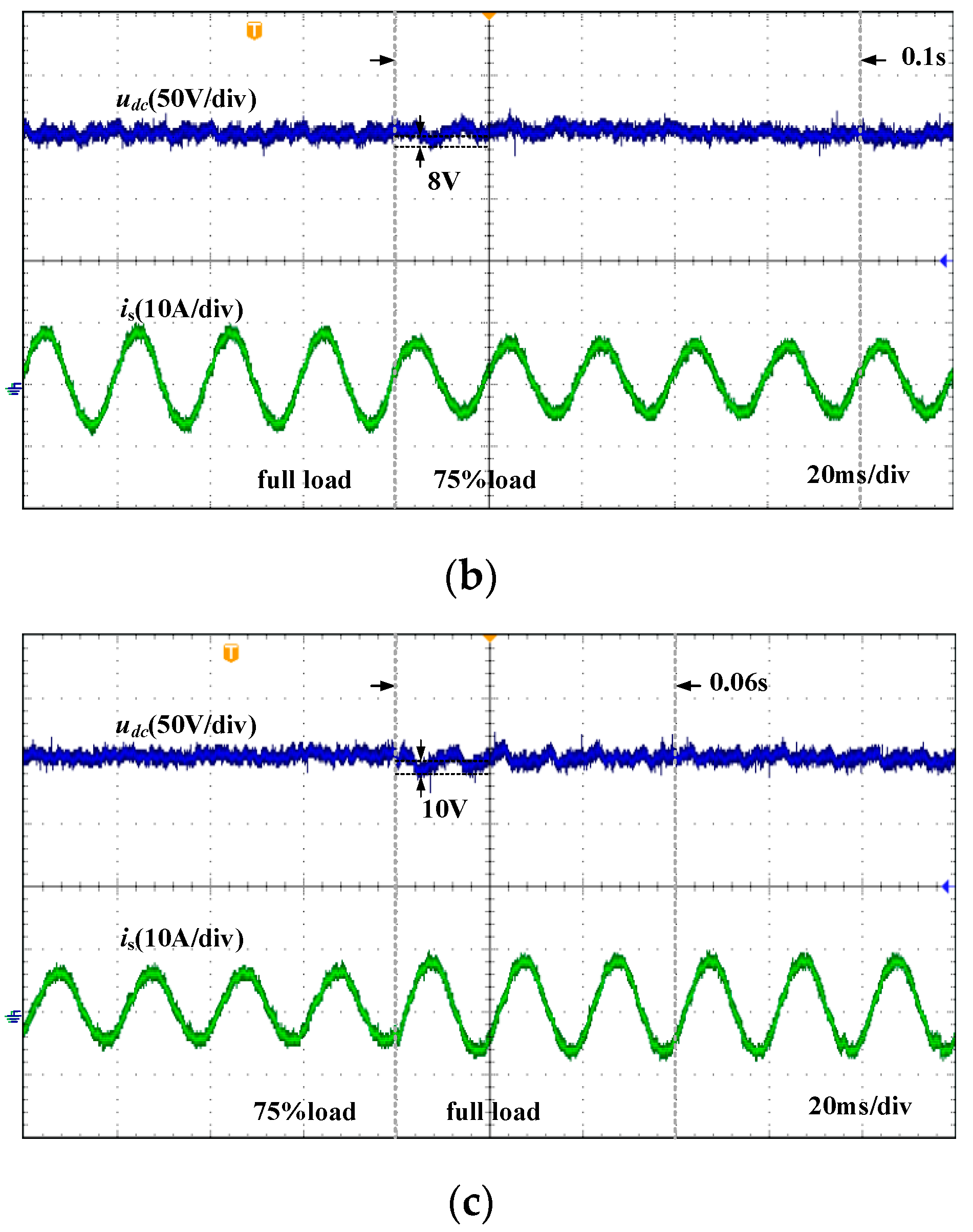

6.2. Experiment Verification

7. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Alves, W.C.; Morais, L.M.F.; Cortizo, P.C. Design of an Highly Efficient AC-DC-AC Three-Phase Converter Using SiC for UPS Applications. Electronics 2018, 7, 425. [Google Scholar] [CrossRef]

- Monteiro, V.; Afonso, J.A.; Ferreira, J.C.; Afonso, J.L. Vehicle Electrification: New Challenges and Opportunities for Smart Grids. Energies 2019, 12, 118. [Google Scholar] [CrossRef]

- Nguyen, M.-K.; Choi, Y.-O. Voltage Multiplier Cell-Based Quasi-Switched Boost Inverter with Low Input Current Ripple. Electronics 2019, 8, 227. [Google Scholar] [CrossRef]

- Nicolas-Apruzzese, J.; Lupon, E.; Busquets-Monge, S.; Conesa, A.; Bordonau, J.; García-Rojas, G. FPGA-Based Controller for a Permanent-Magnet Synchronous Motor Drive Based on a Four-Level Active-Clamped DC-AC Converter. Energies 2018, 11, 2639. [Google Scholar] [CrossRef]

- Pan, H.; Ding, M.; Bi, R.; Sun, L. Research on Cooperative Planning of Distributed Generation Access to AC/DC Distribution (Micro) Grids Based on Analytical Target Cascading. Energies 2019, 12, 1847. [Google Scholar] [CrossRef]

- Zeb, K.; Islam, S.U.; Din, W.U.; Khan, I.; Ishfaq, M.; Busarello, T.D.C.; Ahmad, I.; Kim, H.J. Design of Fuzzy-PI and Fuzzy-Sliding Mode Controllers for Single-Phase Two-Stages Grid-Connected Transformerless Photovoltaic Inverter. Electronics 2019, 8, 520. [Google Scholar] [CrossRef]

- Li, B.; Huang, S.; Chen, X. Performance Improvement for Two-Stage Single-Phase Grid-Connected Converters Using a Fast DC Bus Control Scheme and a Novel Synchronous Frame Current Controller. Energies 2017, 10, 389. [Google Scholar] [CrossRef]

- Zhang, J.; Ding, H.; Wang, B.; Guo, X.; Padmanaban, S. Active Power Decoupling for Current Source Converters: An Overview Scenario. Electronics 2019, 8, 197. [Google Scholar] [CrossRef]

- Li, B.; Zhou, L. Power Decoupling Method Based on the Diagonal Compensating Matrix for VSG-Controlled Parallel Inverters in the Microgrid. Energies 2017, 10, 2159. [Google Scholar] [Green Version]

- Hong, J.; Vilathgamuwa, M.; Yin, J.; Liu, Y.; Peng, J.; Jiang, H. Power Decoupling of a Single Phase DC-AC Dual Active Bridge Converter Based on an Integrated Bidirectional Buck/Boost Stage. Energies 2018, 11, 2746. [Google Scholar] [CrossRef]

- Ertasgin, G.; Whaley, D.M.; Ertugrul, N.; Soong, W.L. Analysis of DC Link Energy Storage for Single-Phase Grid-Connected PV Inverters. Electronics 2019, 8, 601. [Google Scholar] [CrossRef]

- Lu, N.; Yang, S.; Tang, Y. Ripple Current Reduction for Fuel Cell Powered Single-Phase Uninterruptible Power Supplies. IEEE Trans. Ind. Electron. 2017, 64, 6607–6617. [Google Scholar] [CrossRef]

- Yang, Y.; Zhou, K.; Wang, H.; Blaabjerg, F. Analysis and Mitigation of Dead-Time Harmonics in the Single-Phase Full-Bridge PWM Converter with Repetitive Controllers. IEEE Trans. Ind. Appl. 2018, 54, 5343–5354. [Google Scholar] [CrossRef]

- Mozaffari, K.; Amirabadi, M.; Deshpande, Y. A Single-Phase Inverter/Rectifier Topology with Suppressed Double-Frequency Ripple. IEEE Trans. Power Electron. 2018, 33, 9282–9295. [Google Scholar] [CrossRef]

- Liu, Y.; Sun, Y.; Su, M.; Zhou, M.; Zhu, Q.; Li, X. A Single-Phase PFC Rectifier with Wide Output Voltage and Low-Frequency Ripple Power Decoupling. IEEE Trans. Power Electron. 2018, 33, 5076–5086. [Google Scholar] [CrossRef]

- Huang, K.; Wang, Y.; Wai, R. Design of Power Decoupling Strategy for Single-Phase Grid-Connected Inverter Under Nonideal Power Grid. IEEE Trans. Power Electron. 2019, 34, 2938–2955. [Google Scholar] [CrossRef]

- Sun, Y.; Liu, Y.; Su, M.; Xiong, W.; Yang, J. Review of Active Power Decoupling Topologies in Single-Phase Systems. IEEE Trans. Power Electron. 2016, 31, 4778–4794. [Google Scholar] [CrossRef]

- Hu, H.; Harb, S.; Kutkut, N.; Batarseh, I.; Shen, Z.J. A Review of Power Decoupling Techniques for Microinverters with Three Different Decoupling Capacitor Locations in PV Systems. IEEE Trans. Power Electron. 2013, 28, 2711–2726. [Google Scholar] [CrossRef]

- Li, W.; Gu, Y.; Luo, H.; Cui, W.; He, X.; Xia, C. Topology Review and Derivation Methodology of Single-Phase Transformerless Photovoltaic Inverters for Leakage Current Suppression. IEEE Trans. Ind. Electron. 2015, 62, 4537–4551. [Google Scholar] [CrossRef]

- Sun, H.; Wang, H.; Qi, W. Automatic Power Decoupling Controller of Dependent Power Decoupling Circuit for Enhanced Transient Performance. IEEE Trans. Ind. Electron. 2019, 66, 1820–1831. [Google Scholar] [CrossRef]

- Li, S.; Qi, W.; Tan, S.; Hui, S.Y. Integration of an Active Filter and a Single-Phase AC/DC Converter with Reduced Capacitance Requirement and Component Count. IEEE Trans. Power Electron. 2016, 31, 4121–4137. [Google Scholar] [CrossRef]

- Watanabe, H.; Sakuraba, T.; Furukawa, K.; Kusaka, K.; Itoh, J. Development of DC to Single-Phase AC Voltage Source Inverter with Active Power Decoupling Based on Flying Capacitor DC/DC Converter. IEEE Trans. Power Electron. 2018, 33, 4992–5004. [Google Scholar] [CrossRef]

- Jamatia, A.; Gautam, V.; Sensarma, P. Power Decoupling for Single-Phase PV System Using Æuk Derived Microinverter. IEEE Trans. Ind. Appl. 2018, 54, 3586–3595. [Google Scholar] [CrossRef]

- Zhu, G.; Wang, H.; Liang, B.; Tan, S.; Jiang, J. Enhanced Single-Phase Full-Bridge Inverter with Minimal Low-Frequency Current Ripple. IEEE Trans. Ind. Electron. 2016, 63, 937–943. [Google Scholar] [CrossRef]

- Yao, W.; Loh, P.C.; Tang, Y.; Wang, X.; Zhang, X.; Blaabjerg, F. A Robust DC-Split-Capacitor Power Decoupling Scheme for Single-Phase Converter. IEEE Trans. Power Electron. 2017, 32, 8419–8433. [Google Scholar] [CrossRef]

- Xu, S.; Shao, R.; Chang, L.; Mao, M. Single-Phase Differential Buck–Boost Inverter with Pulse Energy Modulation and Power Decoupling Control. IEEE J. Sel. Topics Power Electron. 2018, 6, 2060–2072. [Google Scholar] [CrossRef]

- Zhong, Q.C.; Ming, W.L.; Cao, X.; Krstic, M. Control of Ripple Eliminators to Improve the Power Quality of DC Systems and Reduce the Usage of Electrolytic Capacitors. IEEE Access. 2016, 4, 2177–2187. [Google Scholar] [CrossRef]

- Xiao, S.; Li, X.; Zhang, H.; Balog, R.S. Active power decoupling method based on dual buck circuit with model predictive control. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 3089–3094. [Google Scholar]

- Li, X.; Xiao, S.; Zhang, H.; Balog, R.S.; Ge, B. Dual buck based power decoupling circuit for single phase inverter/rectifier. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6. [Google Scholar]

- Chao, K.; Cheng, P. Power decoupling methods for single-phase three-poles AC/DC converters. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition (ECCE), San Jose, CA, USA, 20–24 September 2009; pp. 3742–3747. [Google Scholar]

- Itoh, J.I.; Watanabe, H.; Koiwa, K.; Ohnuma, Y. Experimental verification of single-phase inverter with power decoupling function using boost-up chopper. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 3–5 September 2013; pp. 1–10. [Google Scholar]

- Wang, R.; Wang, F.; Boroyevich, D.; Burgos, R.; Lai, R.; Ning, P. A High Power Density Single Phase PWM Rectifier with Active Ripple Energy Storage. IEEE Trans. Power Electron. 2011, 26, 1430–1443. [Google Scholar] [CrossRef]

- Cao, X.; Zhong, Q.; Ming, W. Ripple Eliminator to Smooth DC-Bus Voltage and Reduce the Total Capacitance Required. IEEE Trans. Ind. Electron. 2015, 62, 2224–2235. [Google Scholar] [CrossRef]

| Parameters | Buck Type | Boost Type | Buck-Boost Type |

|---|---|---|---|

| Voltage uz of decoupling capacitor | <udc | >udc | adjustable |

| Decoupling capacitance Cz | relatively large | relatively small | adjustable |

| Voltage stress | udc | uz | udc+uz |

| Current stress | ir/d | ir | ir/d |

| efficiency | — | higher | — |

| Parameters | Values (Estimation Method and the Proposed Method) |

|---|---|

| Input voltage Us (Root mean square) | 110 V |

| DC bus rated voltage Udc | 200 V |

| Supply frequency | 50 Hz |

| Switching frequency of rectifier f | 10 KHz |

| Switching frequency of decoupling circuit fr | 10 KHz |

| AC side inductance Ls | 3.3 mH |

| DC bus capacitor C | 100 μF |

| Rated resistor load R | 75 Ω |

| Inductance of decoupling loop L | 1.2 mH |

| Capacitance of decoupling loop Cz | 150 μF |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Qiu, M.; Wang, P.; Bi, H.; Wang, Z. Active Power Decoupling Design of a Single-Phase AC–DC Converter. Electronics 2019, 8, 841. https://doi.org/10.3390/electronics8080841

Qiu M, Wang P, Bi H, Wang Z. Active Power Decoupling Design of a Single-Phase AC–DC Converter. Electronics. 2019; 8(8):841. https://doi.org/10.3390/electronics8080841

Chicago/Turabian StyleQiu, Mingjie, Ping Wang, Huakun Bi, and Zhishuang Wang. 2019. "Active Power Decoupling Design of a Single-Phase AC–DC Converter" Electronics 8, no. 8: 841. https://doi.org/10.3390/electronics8080841

APA StyleQiu, M., Wang, P., Bi, H., & Wang, Z. (2019). Active Power Decoupling Design of a Single-Phase AC–DC Converter. Electronics, 8(8), 841. https://doi.org/10.3390/electronics8080841