A Digital-Controlled SiC-Based Solid State Circuit Breaker with Soft Switch-Off Method for DC Power System

Abstract

1. Introduction

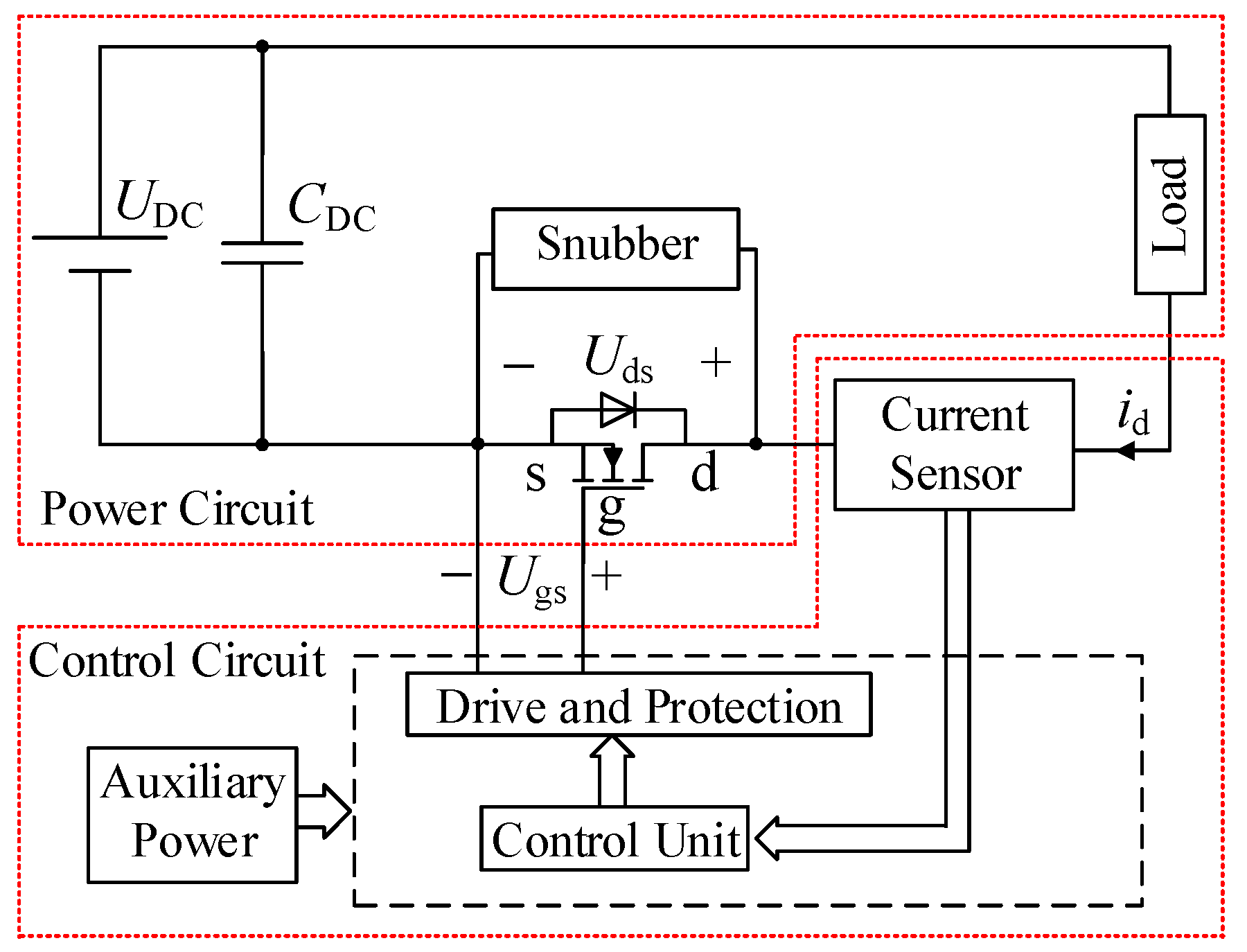

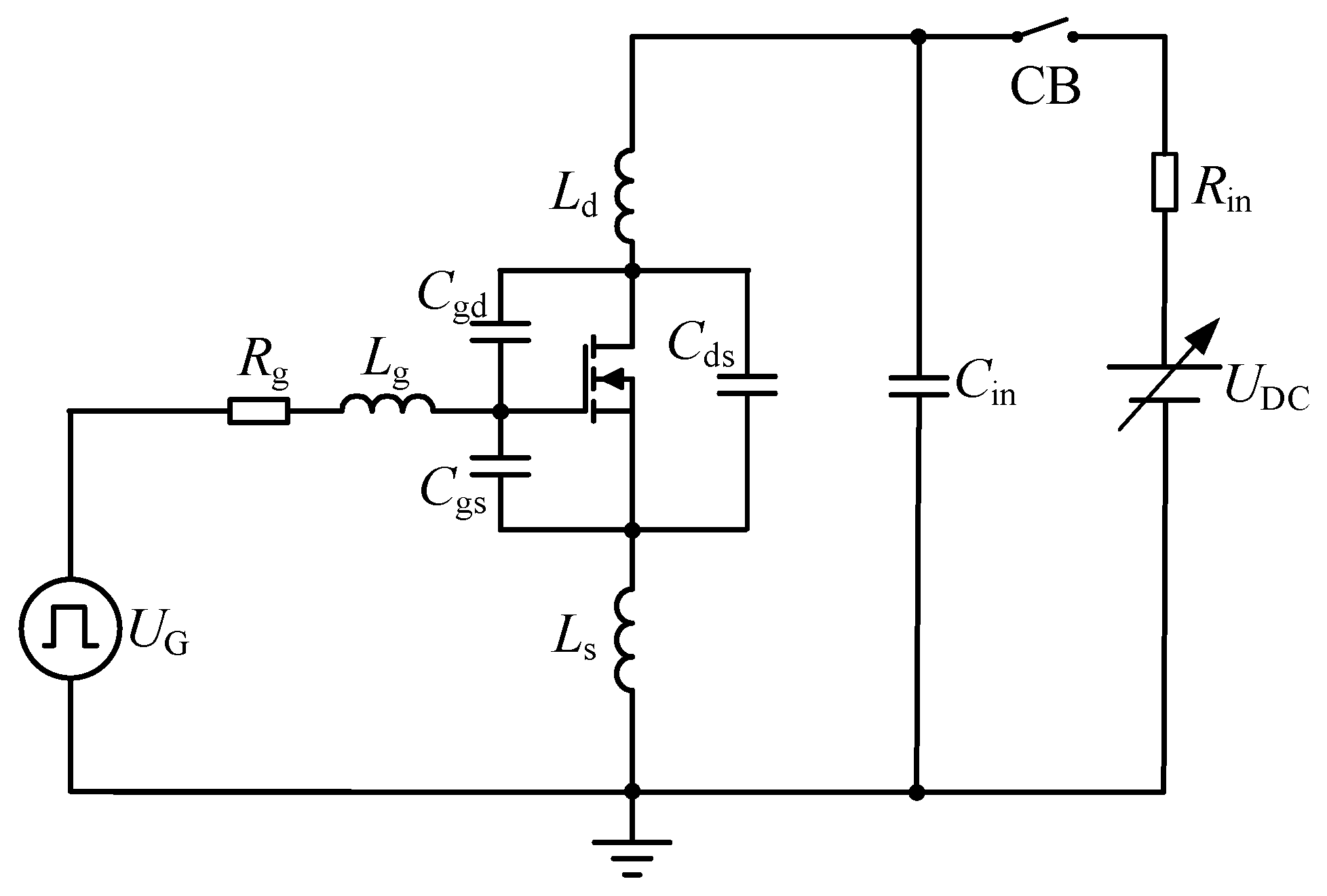

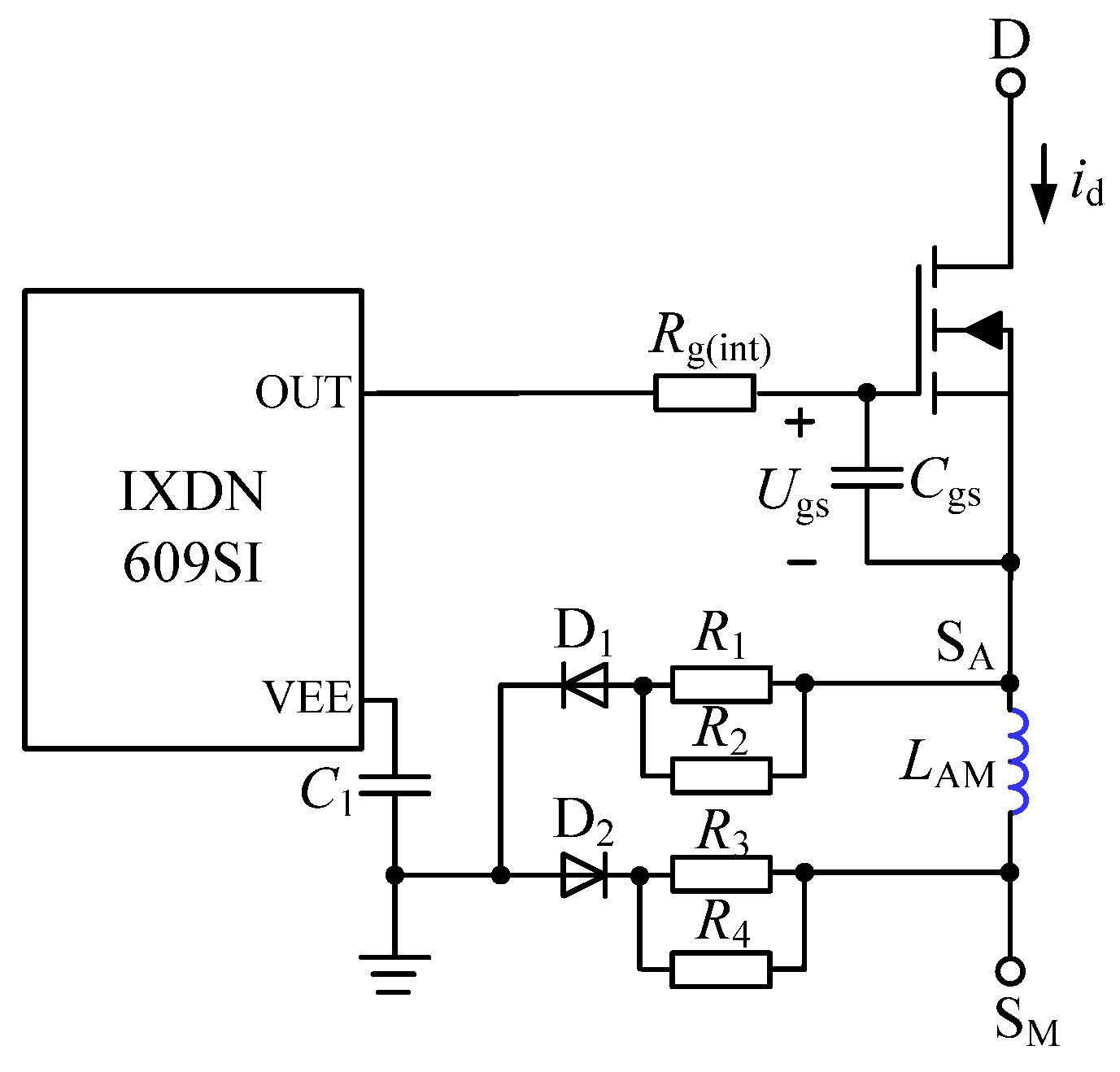

2. Circuit Topology and Operation Principle

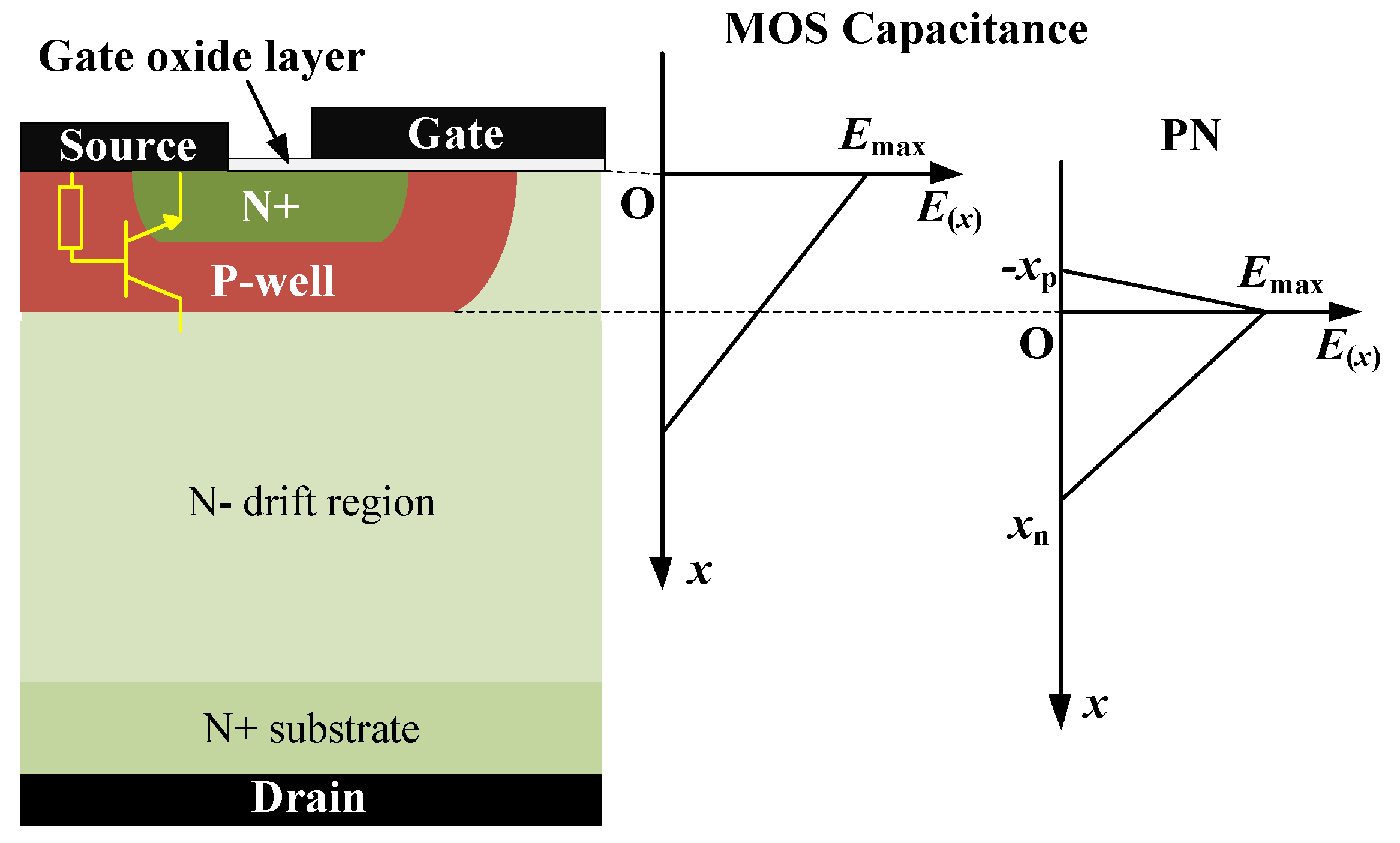

3. Short-Circuit Mechanism of Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)

3.1. The Short-Circuit Behavior of the Silicon Carbide (SiC) MOSFET

3.2. Analysis of Short-Circuit Capability

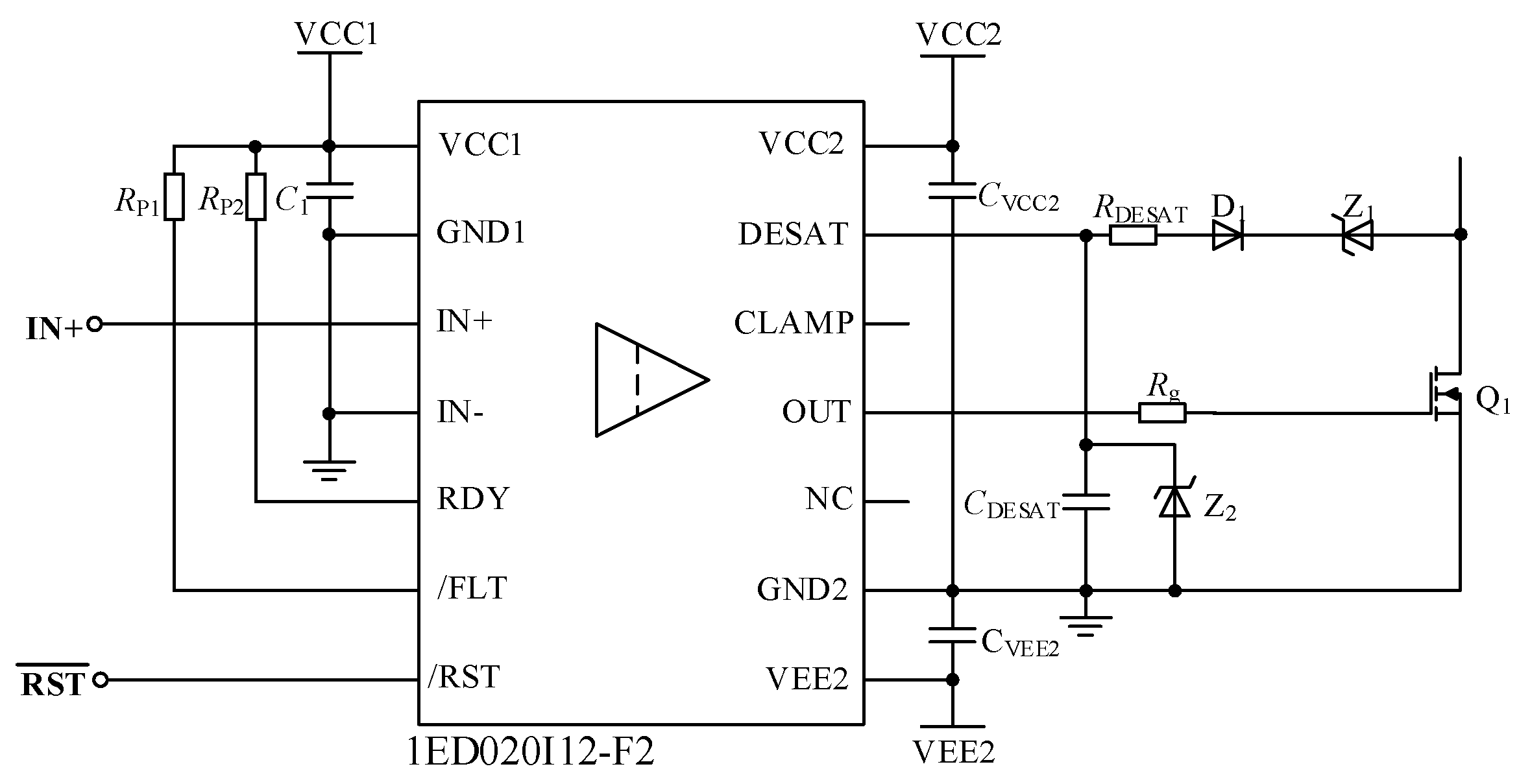

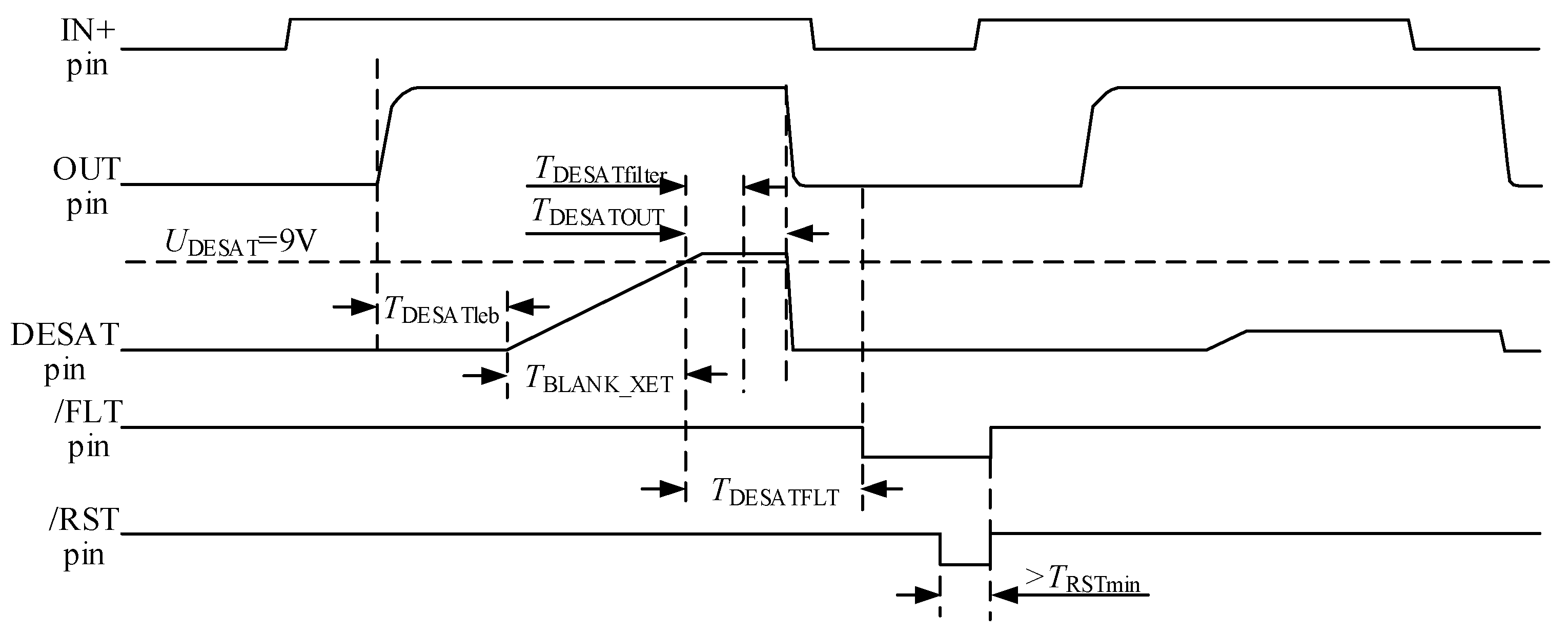

4. Short-Circuit Protection

4.1. Current Detection

4.2. Clamping the Gate-Source Voltage

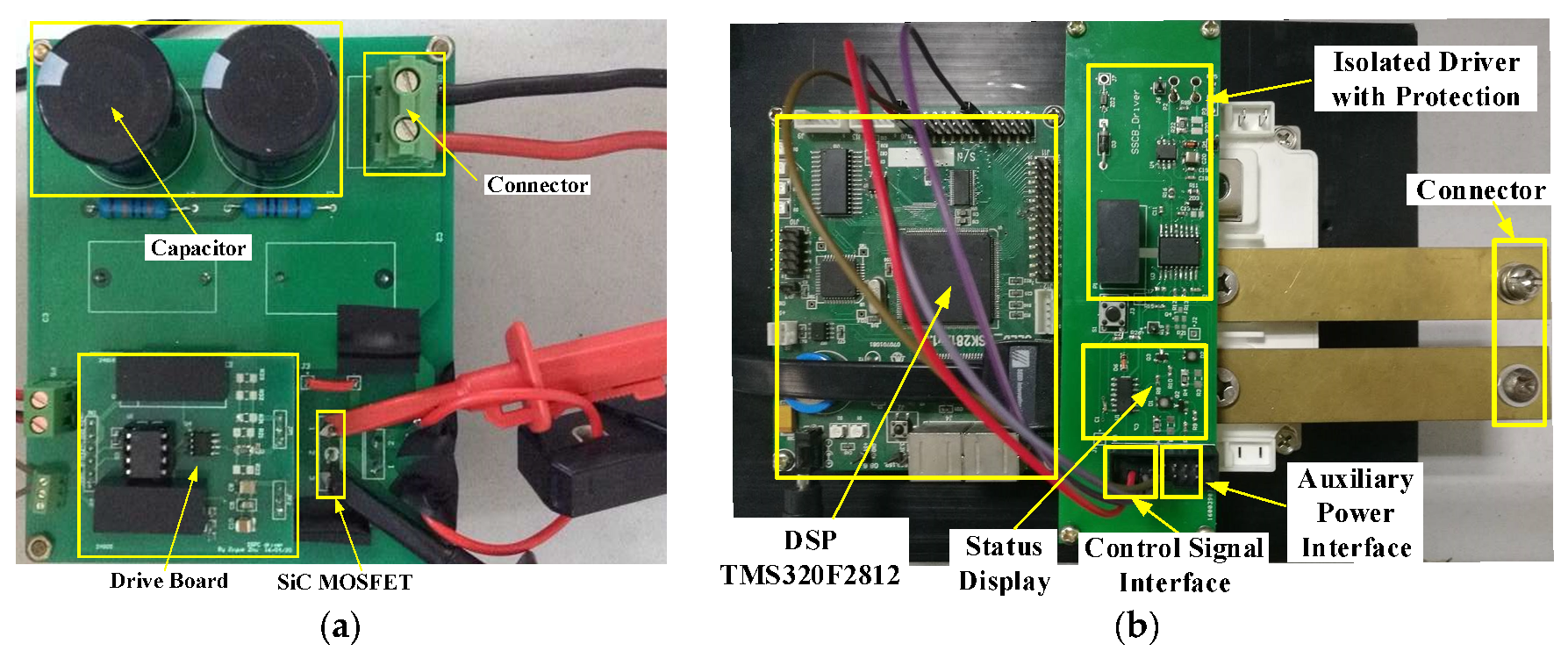

5. Experiment and Analysis

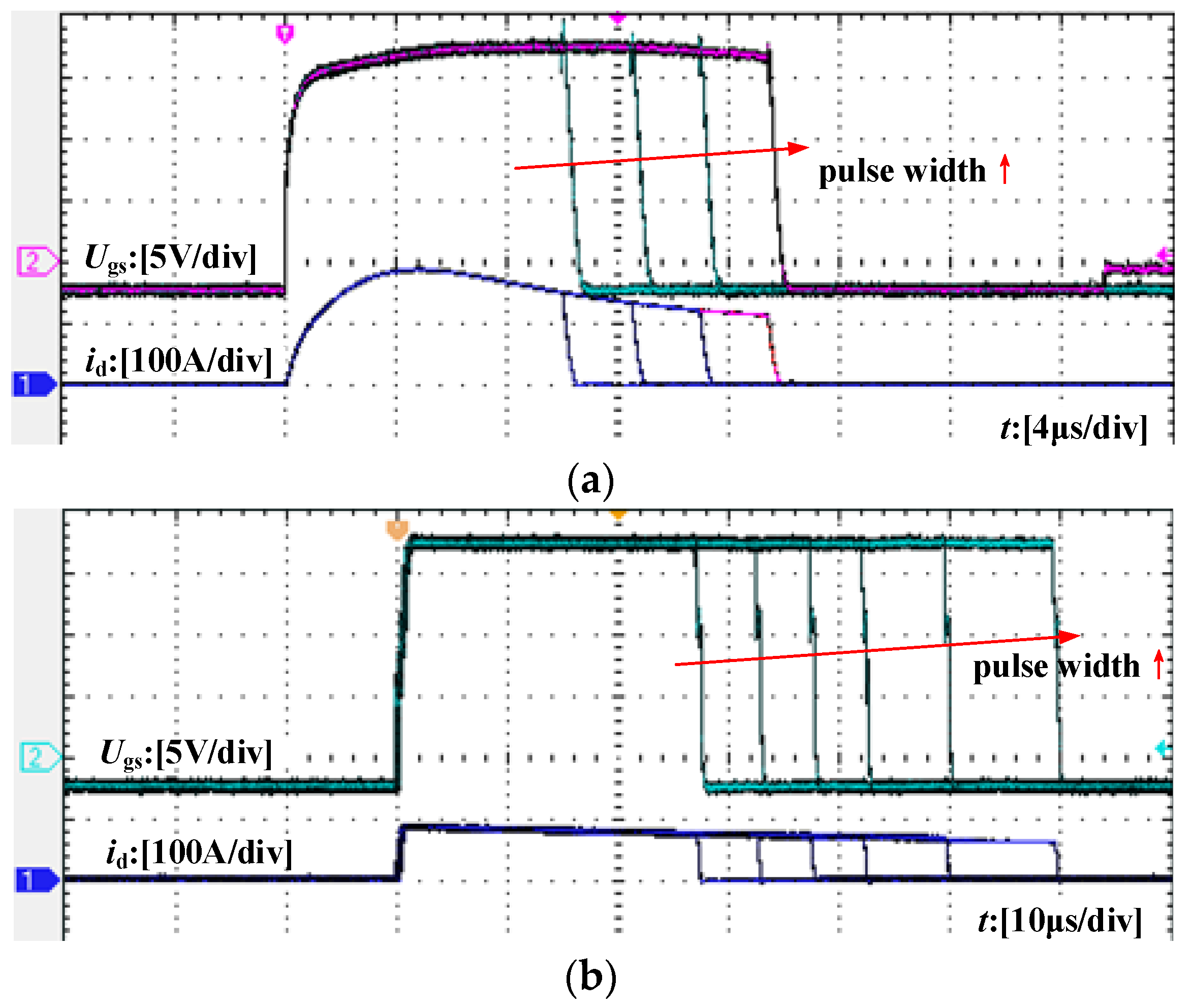

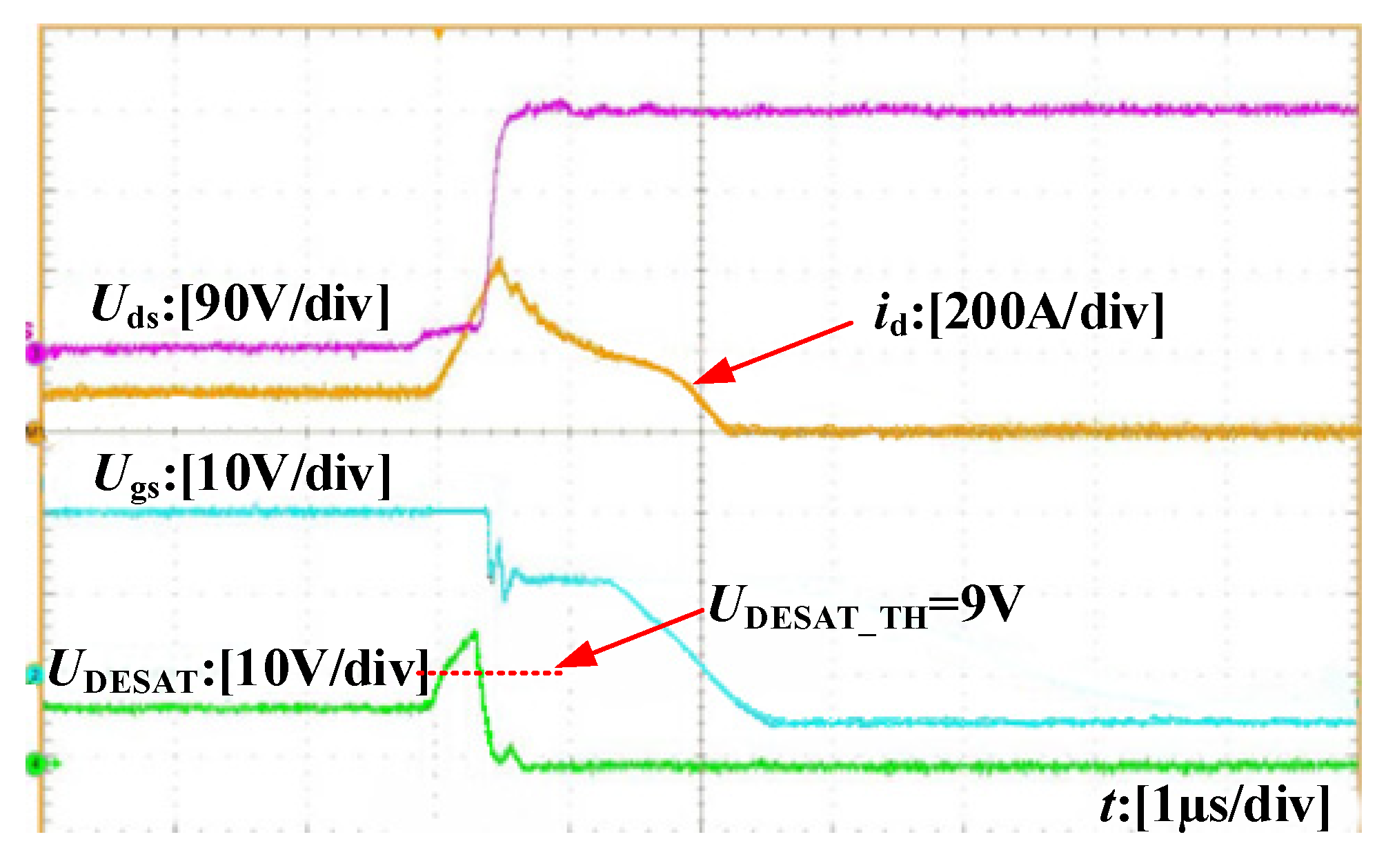

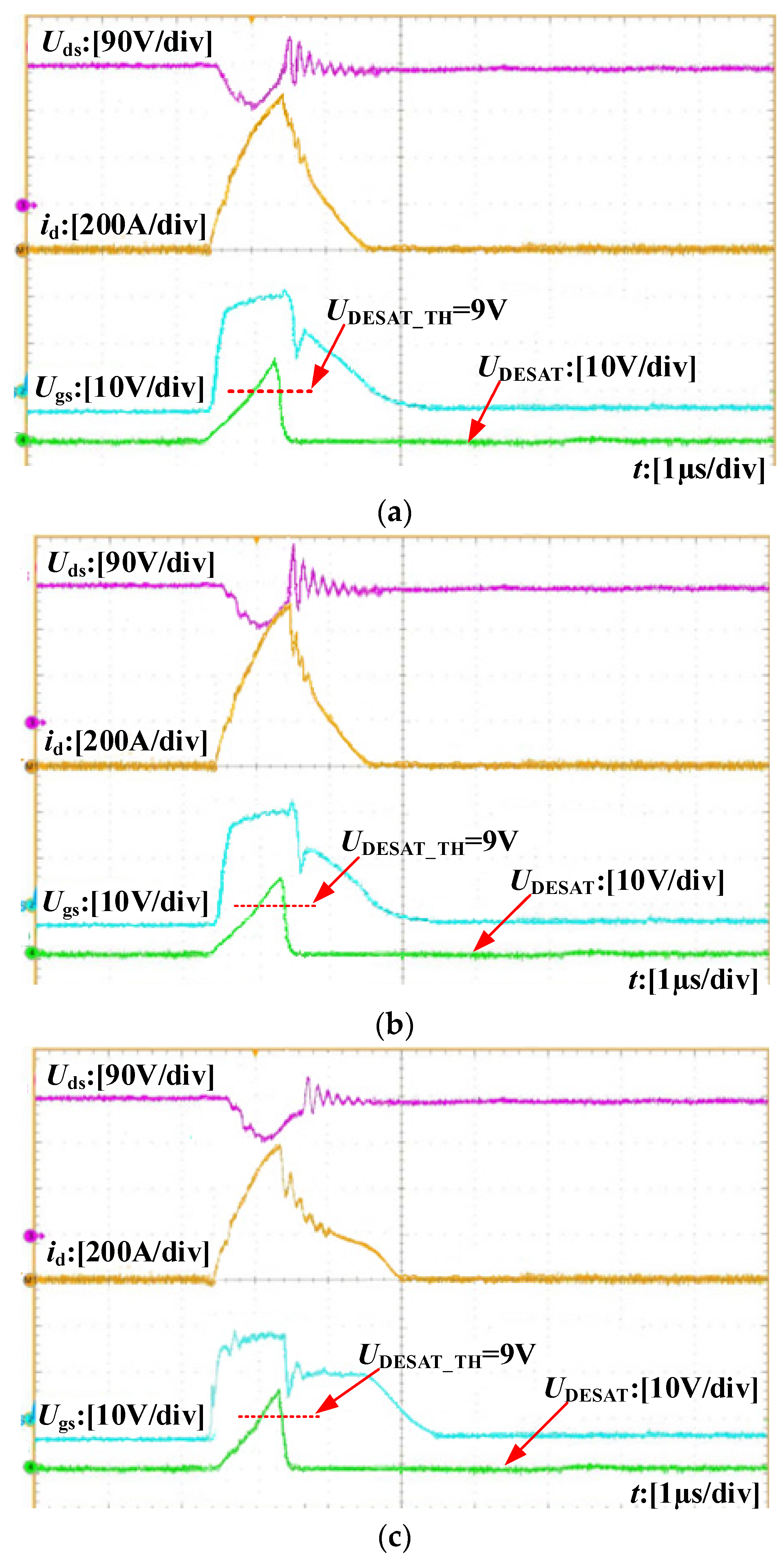

5.1. Short-Circuit Capability Test

5.2. Fault under Load (FUL) Condition Test of SSCB

5.3. Hard-Switching Fault (HSF) Condition Test of SSCB

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Javed, W.; Chen, D.; Farrag, M.E.; Xu, Y. System configuration, fault detection, location, isolation and restoration: A review on LVDC microgrid protections. Energies 2019, 12, 1001. [Google Scholar] [CrossRef]

- Nguyen, V.V.; Son, H.I.; Nguyen, T.T.; Kim, H.M.; Kim, C.K. A novel topology of hybrid HVDC circuit breaker for VSC-HVDC application. Energies 2017, 10, 1675. [Google Scholar] [CrossRef]

- Hernandez, J.C.; Sutil, F.S.; Vidal, P.G. Protection of a multiterminal DC compact node feeding electric vehicles on electric railway systems, secondary distribution networks, and PV systems. Turk. J. Electr. Eng. Comput. Sci. 2016, 24, 3123–3143. [Google Scholar] [CrossRef]

- Hernandez, J.C.; Bueno, P.G.; Sanchez-Sutil, F. Enhanced utility-scale photovoltaic units with frequency support functions and dynamic grid support for transmission systems. IET Renew. Power Gener. 2017, 11, 361–372. [Google Scholar] [CrossRef]

- Sanchez-Sutil, F.; Hernández, J.C.; Tobajas, C. Overview of electrical protection requirements for integration of a smart DC node with bidirectional electric vehicle charging stations into existing AC and DC railway grids. Electr. Power Syst. Res. 2015, 122, 104–118. [Google Scholar] [CrossRef]

- Pugliese, H.; Von Kannewurff, M. Discovering DC: A primer on DC circuit breakers, their advantages, and design. IEEE Ind. Appl. Mag. 2015, 19, 22–28. [Google Scholar] [CrossRef]

- Tan, K.; Liu, P.; Ni, X.; Peng, C.; Song, X.; Huang, A.Q. Performance evaluation of multiple Si and SiC solid state devices for circuit breaker application in 380VDC delivery system. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 983–989. [Google Scholar]

- Xun, Q.; Xun, B.; Li, Z. Application of SiC power electronic devices in secondary power source for aircraft. Renew. Sustain. Energy Rev. 2017, 70, 1336–1342. [Google Scholar] [CrossRef]

- Nawaz, M.; Ilves, K. Replacing Si to SiC: Opportunities and challenges. In Proceedings of the 2016 46th European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, 12–15 September 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 472–475. [Google Scholar]

- Mantooth, H.A.; Peng, K.; Santi, E. Modeling of wide bandgap power semiconductor devices—Part I. IEEE Trans. Electron Devices 2015, 62, 423–433. [Google Scholar] [CrossRef]

- Chow, T.P. Wide bandgap semiconductor power devices for energy efficient systems. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 402–405. [Google Scholar]

- Sun, J.; Xu, H.; Wu, X.; Yang, S.; Guo, Q.; Sheng, K. Short circuit capability and high temperature channel mobility of SiC MOSFETs. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 399–402. [Google Scholar]

- Guo, X.; Xun, Q.; Li, Z.; Du, S. Silicon carbide converters and MEMS devices for high-temperature power electronics: A critical review. Micromachines 2019, 10, 406. [Google Scholar] [CrossRef] [PubMed]

- Sun, J.; Xu, H.; Wu, X.; Sheng, K. Comparison and analysis of short circuit capability of 1200V single-chip SiC MOSFET and Si IGBT. In Proceedings of the China International Forum on Solid State Lighting: International Forum on Wide Bandgap Semiconductors China, Beijing, China, 15–17 November 2016; IEEE: Piscataway, NJ, USA, 2017; pp. 42–45. [Google Scholar]

- Zhang, X.; Sheh, G.; Gant, L.; Banerjee, S. In-Depth Study of Short-Circuit Robustness and Protection of 1200 V SiC MOSFETs. In Proceedings of the PCIM Europe 2018 International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 5–7 June 2018; VDE: Berlin, Germany, 2018; pp. 1–7. [Google Scholar]

- Urciuoli, D.P.; Veliadis, V.; Ha, H.C.; Lubomirsky, V. Demonstration of a 600-V, 60-A, bidirectional silicon carbide solid-state circuit breaker. In Proceedings of the 2011 Twenty-Sixth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Fort Worth, TX, USA, 6–11 March 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 354–358. [Google Scholar]

- Miao, Z.; Sabui, G.; Chen, A.; Li, Y.; Shen, Z.J.; Wang, J.; Shuai, Z.; Luo, A.; Yin, X.; Jiang, M. A self-powered ultra-fast DC solid state circuit breaker using a normally-on SiC JFET. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 767–773. [Google Scholar]

- Sato, Y.; Tanaka, Y.; Fukui, A.; Yamasaki, M.; Ohashi, H. SiC-SIT Circuit Breakers with Controllable Interruption Voltage for 400-V DC Distribution Systems. IEEE Trans. Power Electron. 2014, 29, 2597–2605. [Google Scholar] [CrossRef]

- Ren, Y.; Yang, X.; Zhang, F.; Wang, F.; Tolbert, L.M.; Pei, Y. A Single Gate Driver Based Solid-State Circuit Breaker Using Series Connected SiC MOSFETs. IEEE Trans. Power Electron. 2019, 34, 2002–2006. [Google Scholar] [CrossRef]

- Marroqui, D.; Blanes, J.M.; Garrigós, A.; Gutiérrez, R. Gutiérrez. Self-Powered 380V DC SiC Solid-State Circuit Breaker and Fault Current Limiter. IEEE Trans. Power Electron. 2019, 34, 9600–9608. [Google Scholar] [CrossRef]

- Pilvelait, B.; Gold, C.; Marcel, M. A High Power Solid State Circuit Breaker for Military Hybrid Electric Vehicle Applications. In Proceedings of the 2012 Ground Vehicle Systems Engineering and Technology Symposium (GVSETS), Arlington, VA, USA, 14–16 August 2012. [Google Scholar]

- Zhou, Y.; Feng, Y.; Liu, T.; Shen, Z.J. A Digital-Controlled SiC-Based Solid State Circuit Breaker with Soft-Start Function for DC Microgrids. In Proceedings of the 2018 9th IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Charlotte, NC, USA, 25–28 June 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1–7. [Google Scholar]

- Zhang, L.; Woodley, R.; Song, X.; Sen, S.; Zhao, X.; Huang, A.Q. High current medium voltage solid state circuit breaker using paralleled 15kV SiC ETO. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 1706–1709. [Google Scholar]

- Gu, C.; Wheeler, P.; Castellazzi, A.; Watson, A.J.; Effah, F. Semiconductor Devices in Solid-State/Hybrid Circuit Breakers: Current Status and Future Trends. Energies 2017, 10, 495. [Google Scholar] [CrossRef]

- Li, H.; Yu, R.; Zhong, Y.; Yao, R.; Liao, X.; Chen, X. Design of 400 V Miniature DC Solid State Circuit Breaker with SiC MOSFET. Micromachines 2019, 10, 314. [Google Scholar] [CrossRef] [PubMed]

- Pérez-Tomás, A.; Brosselard, P.; Godignon, P.; Millán, J.; Mestres, N.; Jennings, M.R.; Mawby, P.A. Field-effect mobility temperature modeling of 4H-SiC metal-oxide-semiconductor transistors. J. Appl. Phys. 2006, 100, 114508. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Tolbert, L.M.; Wang, F.; Blalock, B.J. Temperature-dependent short-circuit capability of silicon carbide power mosfets. IEEE Trans. Power Electron. 2015, 31, 1555–1566. [Google Scholar] [CrossRef]

- Nguyen, T.T.; Ahmed, A.; Thang, T.V.; Park, J.H. Gate Oxide Reliability Issues of SiC MOSFETs Under Short-Circuit Operation. IEEE Trans. Power Electron. 2015, 30, 2445–2455. [Google Scholar] [CrossRef]

- Bertelshofer, T.; März, A.; Bakran, M.M. A temperature compensated overcurrent and short-circuit detection method for SiC MOSFET modules. In Proceedings of the 2017 19th European Conference on Power Electronics and Applications (EPE’17 ECCE Europe), Warsaw, Poland, 11–14 September 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 1–10. [Google Scholar]

- Mocevic, S. Phase Current Sensor and Short-Circuit Detection based on Rogowski Coils Integrated on Gate Driver for 1.2 kV SiC MOSFET Half-Bridge Module. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 393–400. [Google Scholar]

- Maerz, A.; Bertelshofer, T.; Horff, R.; Bakran, M.M. Requirements of short-circuit detection methods and turn-off for wide band gap semiconductors. In Proceedings of the CIPS 2016 9th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 8–10 March 2016; VDE: Berlin, Germany, 2016; pp. 1–6. [Google Scholar]

- Infineon Technologies, No. 1ED020I12-F2 Datasheet. Available online: https://www.infineon.com/dgdl/Infineon-1ED020I12-F2-DS-v02_01-EN.pdf?fileId=db3a304330f68606013122ce5f3649cb (accessed on 22 July 2019).

- Awwad, A.E.; Dieckerhoff, S. Short-circuit evaluation and overcurrent protection for SiC power MOSFETs. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 1–9. [Google Scholar]

- Kreutzer, O.; Eckardt, B.; Maerz, M. Optimum gate driver design to reach SiC-MOSFET’s full potential—Speeding up to 200 kV/μs. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 41–46. [Google Scholar]

| Parameters | SiC MOSFET (SCH2080KE) | |

|---|---|---|

| Normal | Damaged | |

| Rgs/Rsg (Ω) | ∞/∞ | 0.8/0.8 |

| Rgd/Rdg (Ω) | ∞/∞ | ∞/∞ |

| Rds/Rsd (Ω) | ∞/∞ | ∞/∞ |

| UF (V) | 0.677 | 0.680 |

| Gate-source Voltage Vlamping | Zener Diode Clamping | Soft Turn-Off Circuit | |

|---|---|---|---|

| Short-circuit peak current (A) | 650 | 700 | 600 |

| Overshoot voltage (V) | 325 | 358 | 310 |

| Short-circuit protection time (µs) | 2 | 2 | 2.5 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Qin, H.; Mo, Y.; Xun, Q.; Zhang, Y.; Dong, Y. A Digital-Controlled SiC-Based Solid State Circuit Breaker with Soft Switch-Off Method for DC Power System. Electronics 2019, 8, 837. https://doi.org/10.3390/electronics8080837

Qin H, Mo Y, Xun Q, Zhang Y, Dong Y. A Digital-Controlled SiC-Based Solid State Circuit Breaker with Soft Switch-Off Method for DC Power System. Electronics. 2019; 8(8):837. https://doi.org/10.3390/electronics8080837

Chicago/Turabian StyleQin, Haihong, Yubin Mo, Qian Xun, Ying Zhang, and Yaowen Dong. 2019. "A Digital-Controlled SiC-Based Solid State Circuit Breaker with Soft Switch-Off Method for DC Power System" Electronics 8, no. 8: 837. https://doi.org/10.3390/electronics8080837

APA StyleQin, H., Mo, Y., Xun, Q., Zhang, Y., & Dong, Y. (2019). A Digital-Controlled SiC-Based Solid State Circuit Breaker with Soft Switch-Off Method for DC Power System. Electronics, 8(8), 837. https://doi.org/10.3390/electronics8080837