A Charge-Sharing-Based Two-Phase Charging Scheme for Zero-Crossing-Based Integrator Circuits

Abstract

1. Introduction

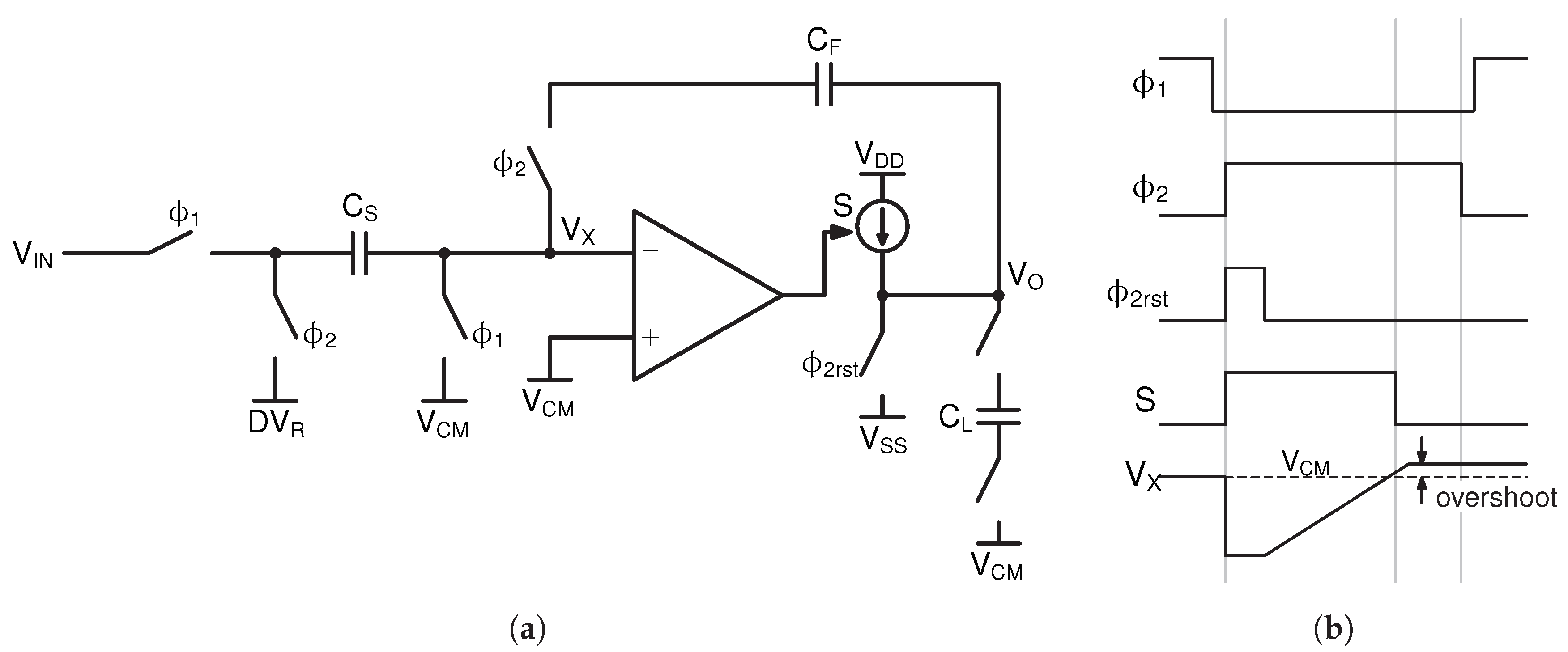

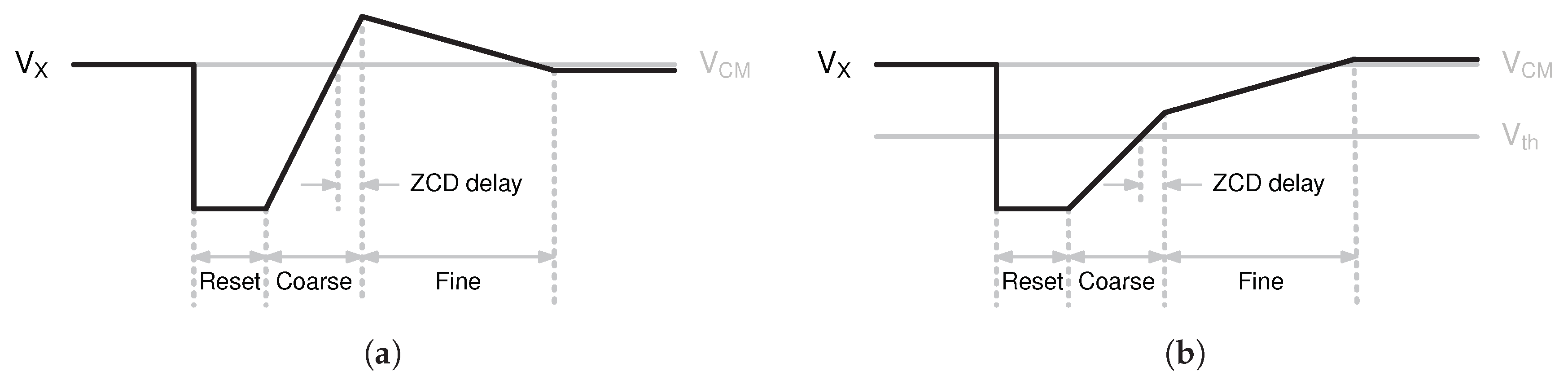

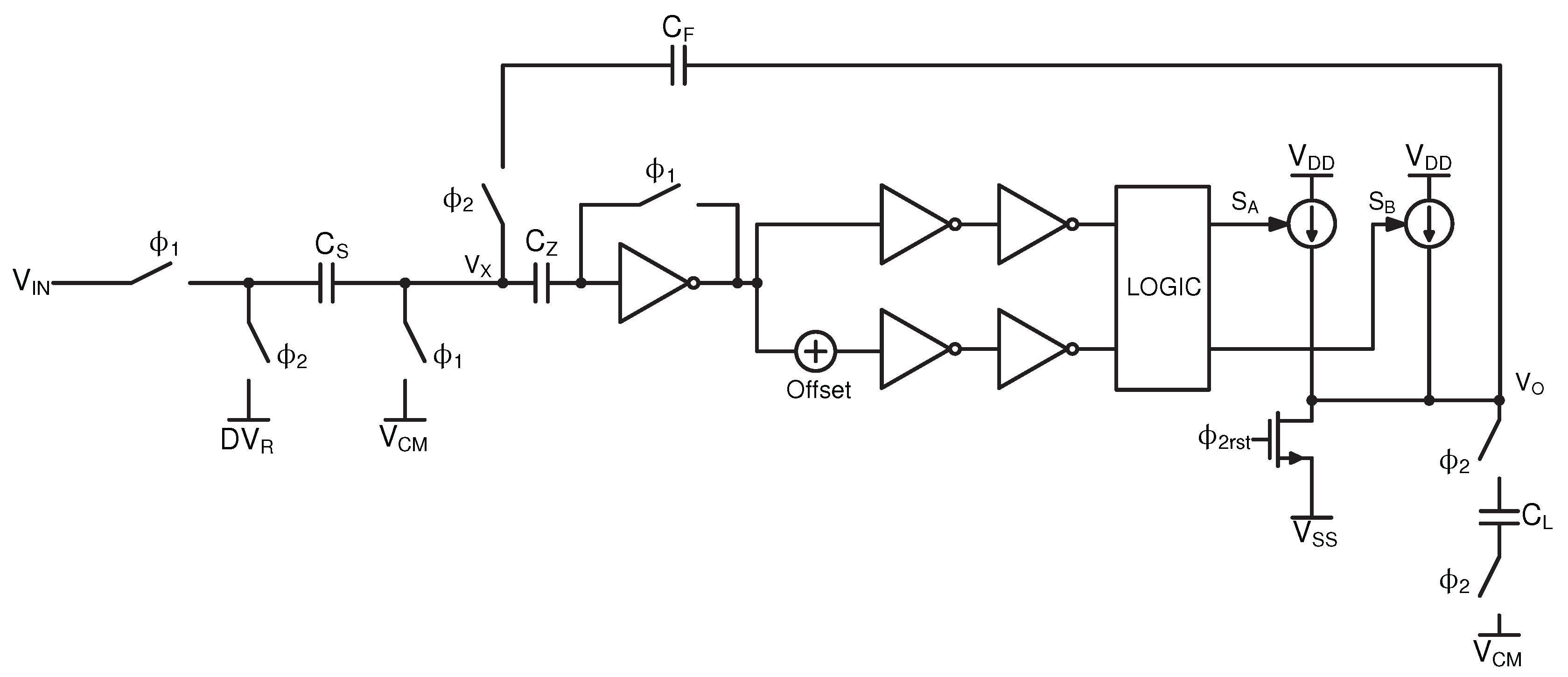

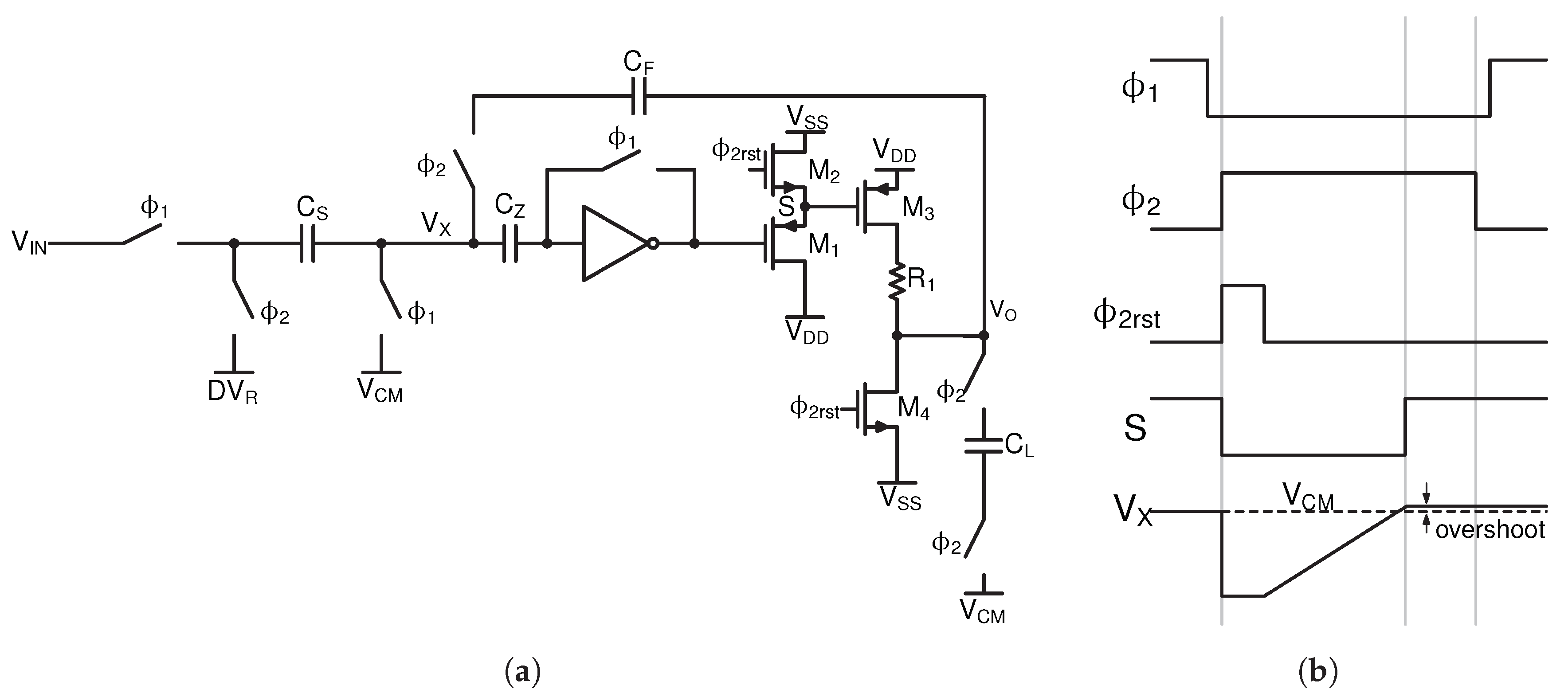

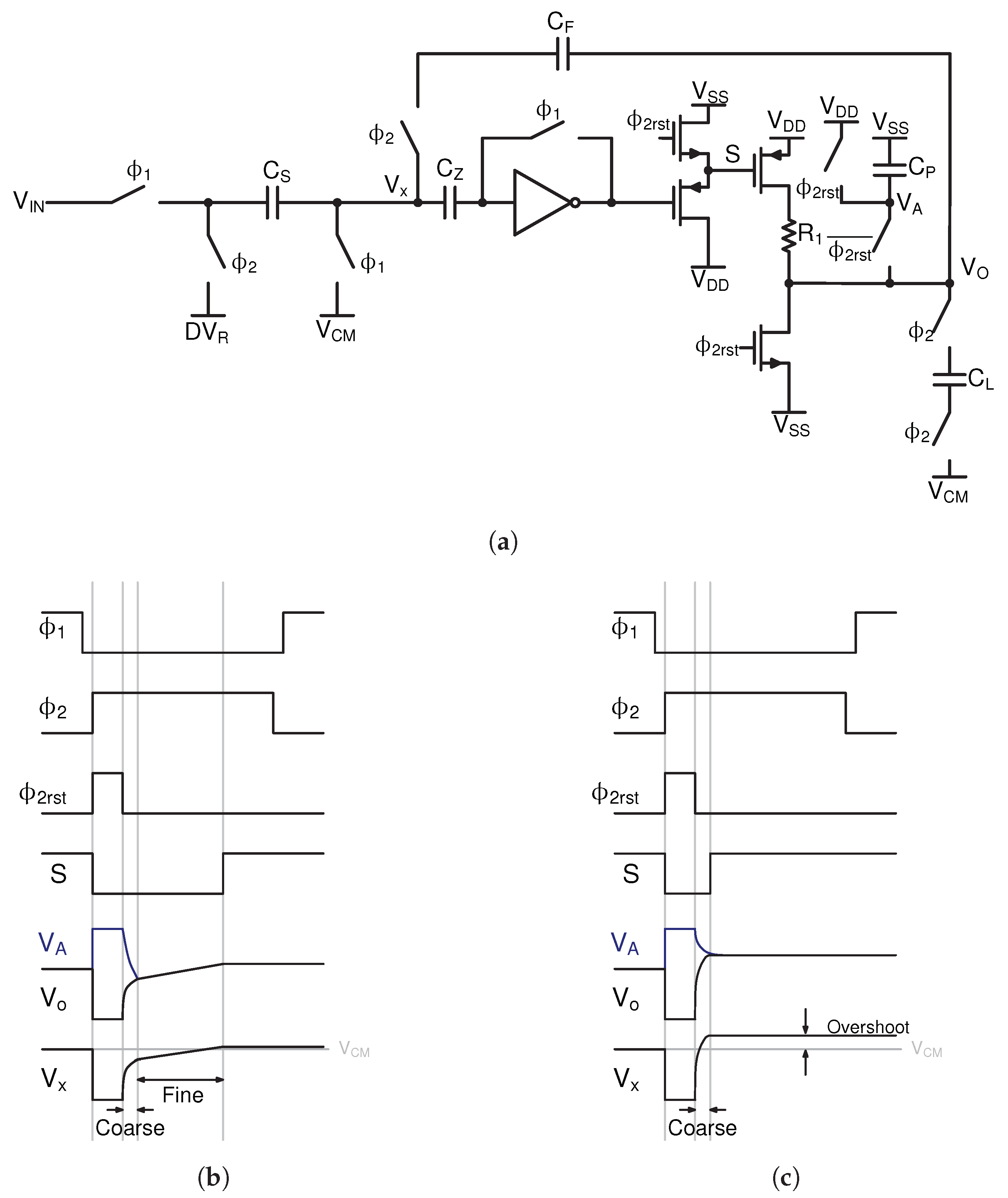

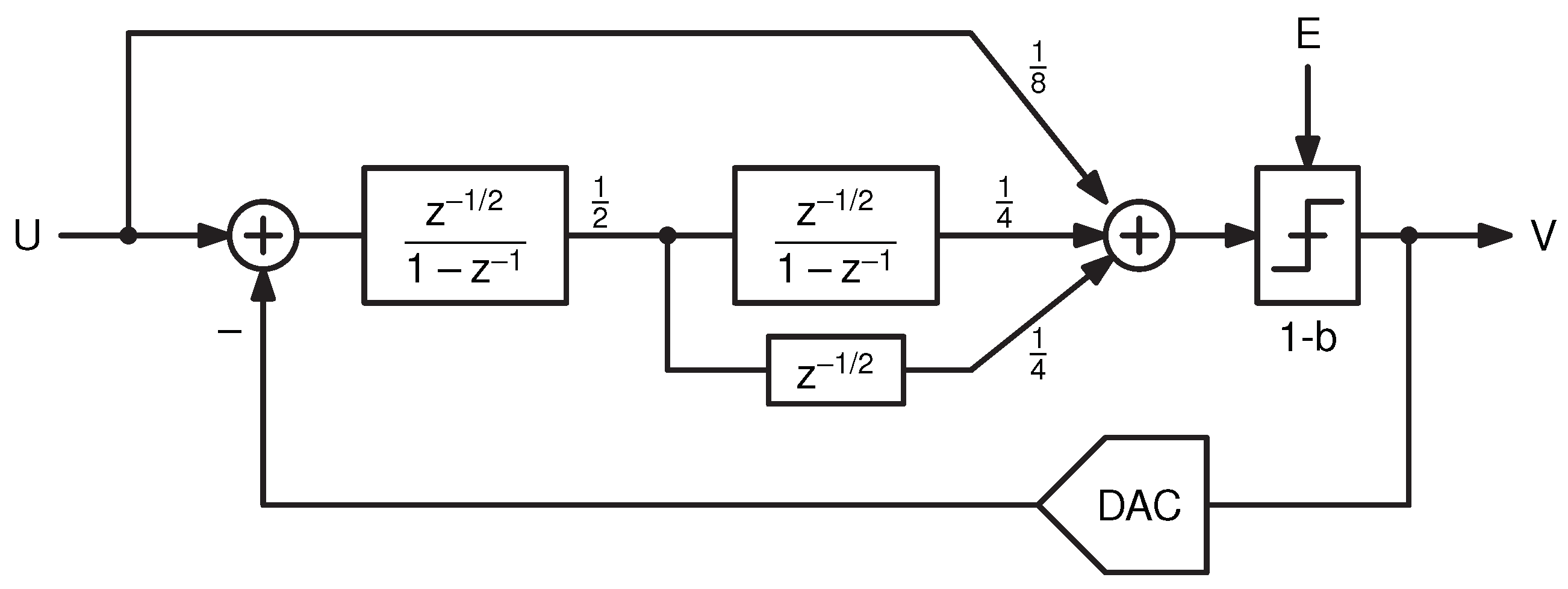

2. Proposed ZCBI Circuit

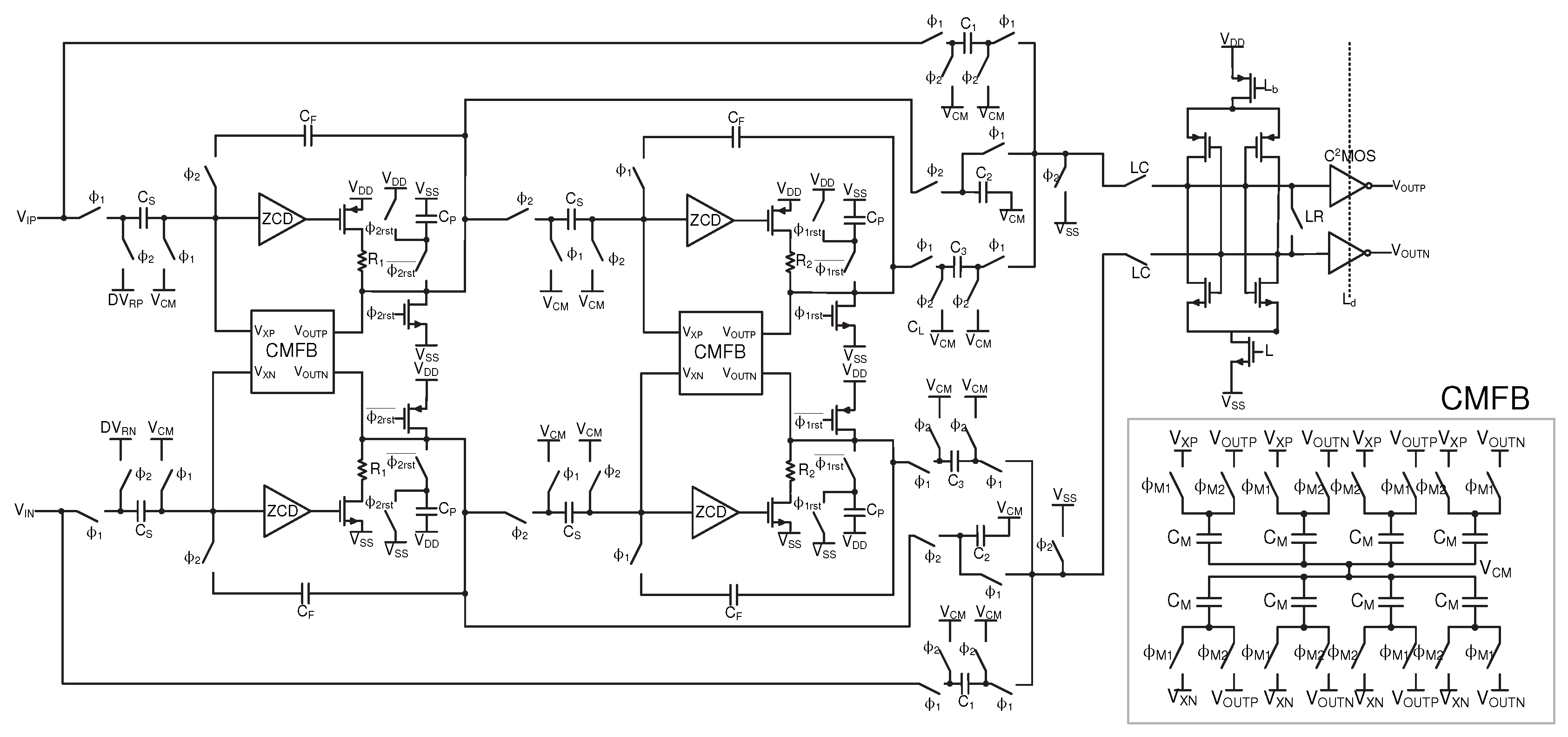

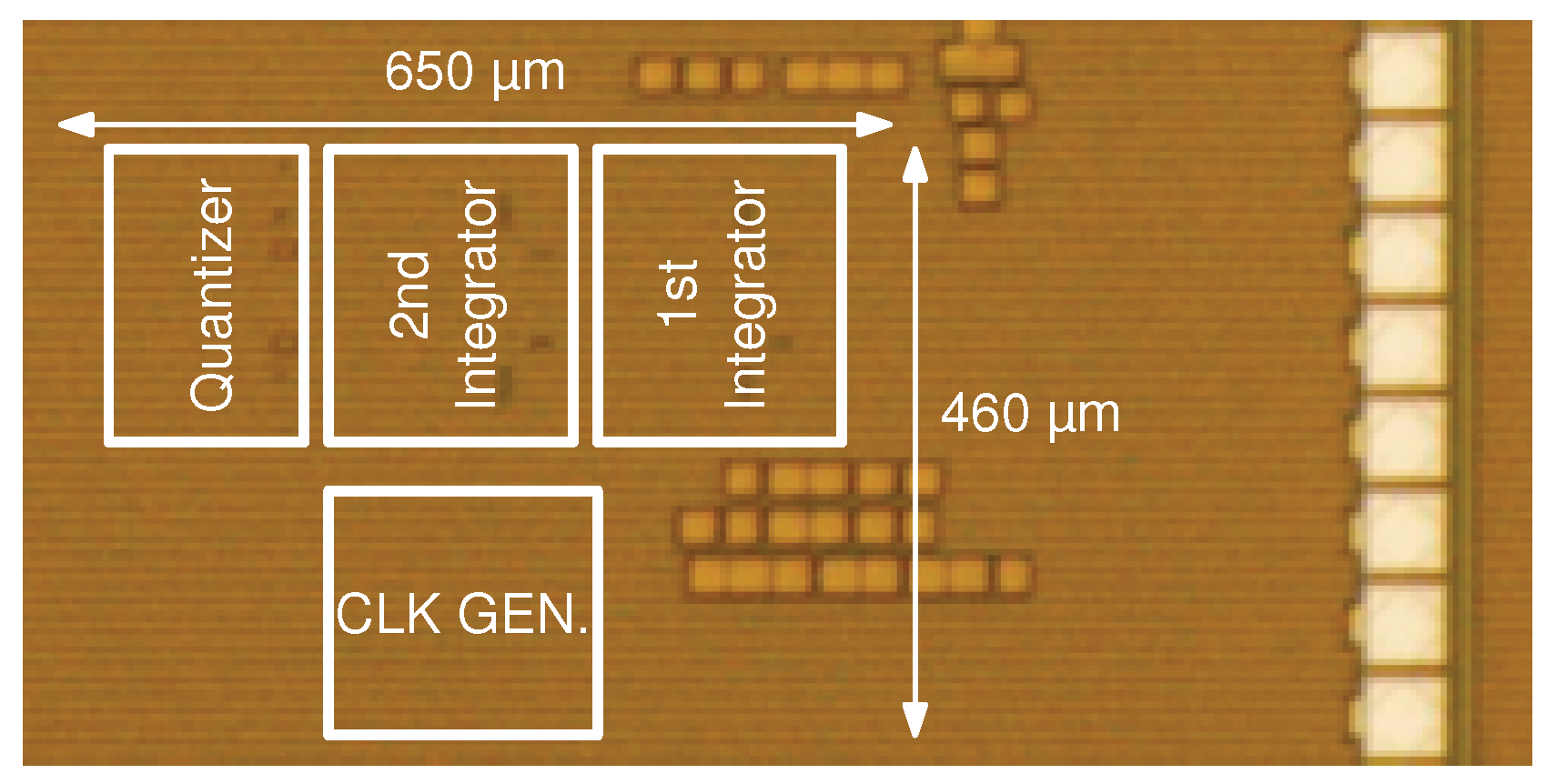

3. Circuit Implementation and Measurement Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Abbreviations

| OTA | Operational Transconductance Amplifier |

| ZCBI | Zero-Crossing-Based Integrator |

| ZCD | Zero-Crossing Detector |

| ADC | Analog-to-Digital Converter |

| DAC | Digital-to-Analog Converter |

| CMOS | Complementary Metal-Oxide-Semiconductor |

| OSR | Over-Sampling Ratio |

| SNR | Signal-to-Noise Ratio |

| SNDR | Signal-to-Noise-and-Distortion Ratio |

| FoM | Figure of Merit |

References

- Annema, A.-J.; Nauta, B.; van Langevelde, R.; Tuinhout, H. Analog circuits in ultra-deep-submicron CMOS. IEEE J. Solid-State Circuits 2005, 40, 132–143. [Google Scholar] [CrossRef]

- Murmann, B.; Nikaeen, P.; Connelly, D.J.; Dutton, R.W. Impact of Scaling on Analog Performance and Associated Modeling Needs. IEEE Trans. Electron. Devices 2006, 53, 2160–2167. [Google Scholar] [CrossRef]

- Chiu, Y.; Nikolic, B.; Gray, P.R. Scaling of analog-to-digital converters into ultra-deep-submicron CMOS. In Proceedings of the IEEE 2005 Custom Integrated Circuits Conference, San Jose, CA, USA, 18–21 September 2005; pp. 368–375. [Google Scholar] [CrossRef]

- Bult, K. Broadband communication circuits in pure digital deep sub-micron CMOS. In Proceedings of the 1999 IEEE International Solid-State Circuits Conference, Digest of Technical Papers, ISSCC, First Edition (Cat. No. 99CH36278), San Francisco, CA, USA, 17 February 1999; pp. 76–77. [Google Scholar] [CrossRef]

- Fiorenza, J.K.; Sepke, T.; Holloway, P.; Sodini, C.G.; Lee, H.-S. Comparator-Based Switched-Capacitor Circuits for Scaled CMOS Technologies. IEEE J. Solid-State Circuits 2006, 41, 2658–2668. [Google Scholar] [CrossRef]

- Mortazavi, S.Y.; Nabavi, A.; Amiri, P. High-accuracy Comparator-Based Switched-Capacitor structure. IEICE Electron. Expr. 2010, 7, 352–359. [Google Scholar] [CrossRef]

- Wulff, C.; Ytterdal, T. CBSC pipelined ADC with comparator preset, and comparator delay compensation. In Proceedings of the NORCHIP, Trondheim, Norway, 16–17 November 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Brooks, L.; Lee, H.-S. A Zero-Crossing-Based 8-bit 200 MS/s Pipelined ADC. IEEE J. Solid-State Circuits 2007, 42, 2677–2687. [Google Scholar] [CrossRef]

- Musah, T.; Moon, U.-K. Pseudo-differential zero-crossing-based circuit with differential error suppression. In Proceedings of the 2010 IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010; pp. 1731–1734. [Google Scholar] [CrossRef]

- Brooks, L.; Lee, H.-S. A 12b 50MS/s fully differential zero-crossing-based ADC without CMFB. In Proceedings of the 2009 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 8–12 February 2009; pp. 166–167. [Google Scholar] [CrossRef]

- Musah, T.; Kwon, S.; Lakdawala, H.; Soumyanath, K.; Moon, U.-K. A 630μW zero-crossing-based ΔΣ ADC using switched-resistor current sources in 45nm CMOS. In Proceedings of the 2009 IEEE Custom Integrated Circuits Conference, Rome, Italy, 13–16 September 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Wong, K.-F.; Sin, S.-W.; U, S.-P.; Martins, R.P. A modified charging algorithm for comparator-based switched-capacitor circuits. In Proceedings of the 52nd IEEE International Midwest Symposium on Circuits and Systems, Cancun, Mexico, 2–5 August 2009; pp. 86–89. [Google Scholar] [CrossRef]

- Huang, M.-C.; Liu, S.-I. A Fully Differential Comparator-Based Switched-Capacitor ΔΣ Modulator. IEEE Trans. Circuits Syst. Express Briefs 2009, 56, 369–373. [Google Scholar] [CrossRef]

- Yamamoto, K.; Carusone, A. A 1-1-1-1 MASH Delta-Sigma Modulator With Dynamic Comparator-Based OTAs. IEEE J. Solid-State Circuits 2012, 47, 1866–1883. [Google Scholar] [CrossRef]

- Min, D.-J.; Choi, S.Y.; Shim, J.H. A Low-Power 2nd-Order Delta-Sigma ADC with an Inverter- Based Zero-Crossing Detector. In Proceedings of the 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018; pp. 817–820. [Google Scholar] [CrossRef]

- Chen, C.; Tan, Z.; Pertijs, M.A.P. A 1V 14b self-timed zero-crossing-based incremental ΔΣ ADC. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 274–275. [Google Scholar] [CrossRef]

- Silva, J.; Moon, U.; Steensgaard, J.; Temes, G.C. Wideband low-distortion delta-sigma ADC topology. Electron. Lett. 2001, 37, 737. [Google Scholar] [CrossRef]

- Wu, L.; Keskin, M.; Moon, U.; Temes, G. Efficient common-mode feedback circuits for pseudo-differential switched-capacitor stages. In Proceedings of the 2000 IEEE International Symposium on Circuits and Systems, Emerging Technologies for the 21st Century. Proceedings (IEEE Cat No.00CH36353), Geneva, Switzerland, 28–31 May 2000; pp. 445–448. [Google Scholar] [CrossRef]

- Pavan, S.; Krishnapura, N.; Pandarinathan, R.; Sankar, P. A Power Optimized Continuous-Time ΔΣ ADC for Audio Applications. IEEE J. Solid-State Circuits 2008, 43, 351–360. [Google Scholar] [CrossRef]

| Technology | 180-nm CMOS |

| Sampling Frequency | 10 MHz |

| 1.8 V | |

| 0.9 V | |

| 0.4 V or 1.4 V | |

| , | 25 fF |

| , | 50 fF, 100 fF |

| , | 300 fF, 500 fF |

| Sub-Block | Power Consumption (µW) | Percentage (%) |

|---|---|---|

| 1st Integrator | 235 | 34.3 |

| 2nd Integrator | 229 | 33.5 |

| Adder | 5.6 | 0.8 |

| Quantizer | 5.7 | 0.8 |

| DAC | 0.9 | 0.1 |

| Clock Genrator | 151 | 22.1 |

| Ref. buffers, etc. | 56.8 | 8.4 |

| Total | 684 | 100 |

| [11] | [13] | [14] | [16] | This Work | |||

|---|---|---|---|---|---|---|---|

| Technology (nm) | 45 | 180 | 65 | 160 | 180 | 65 | 65 |

| Supply Voltage (V) | 1.1 | 1.8 | 1.2 | 1.0 | 1.8 | 1.2 | 1.2 |

| Sampling Frequency (MHz) | 50 | 2.56 | 40 | 0.014 | 10 | 10 | 50 |

| Oversampling Ratio | 30 | 64 | 8 | 1 | 32 | 32 | 32 |

| Bandwidth (kHz) | 833 | 20 | 2500 | 0.7 | 156 | 156 | 781 |

| Peak SNDR (dB) | 47.7 | 65.3 | 70.4 | N/A | 46.3 | 53.2 | 53.7 |

| Peak SNR (dB) | 52.5 | N/A | N/A | 81.8 | 50.1 | 56.3 | 56.5 |

| Dynamic Range (dB) | 54.3 | 71 | 71.3 | N/A | 56 | N/A | 56.5 |

| Power Consumption (µW) | 630 | 420 | 3730 | 20 | 684 | 274 | 312 |

| (dB) | 139 | 142 | 159 | 157 | 130 | 140.8 | 148 |

| (pJ/conv-step) | 1.91 | 6.98 | 0.276 | 1.48 | 13.2 | 2.35 | 0.5 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Min, D.-J.; Shim, J.H. A Charge-Sharing-Based Two-Phase Charging Scheme for Zero-Crossing-Based Integrator Circuits. Electronics 2019, 8, 821. https://doi.org/10.3390/electronics8070821

Min D-J, Shim JH. A Charge-Sharing-Based Two-Phase Charging Scheme for Zero-Crossing-Based Integrator Circuits. Electronics. 2019; 8(7):821. https://doi.org/10.3390/electronics8070821

Chicago/Turabian StyleMin, Dong-Jick, and Jae Hoon Shim. 2019. "A Charge-Sharing-Based Two-Phase Charging Scheme for Zero-Crossing-Based Integrator Circuits" Electronics 8, no. 7: 821. https://doi.org/10.3390/electronics8070821

APA StyleMin, D.-J., & Shim, J. H. (2019). A Charge-Sharing-Based Two-Phase Charging Scheme for Zero-Crossing-Based Integrator Circuits. Electronics, 8(7), 821. https://doi.org/10.3390/electronics8070821