A Multi-Inductor H Bridge Fault Current Limiter

Abstract

1. Introduction

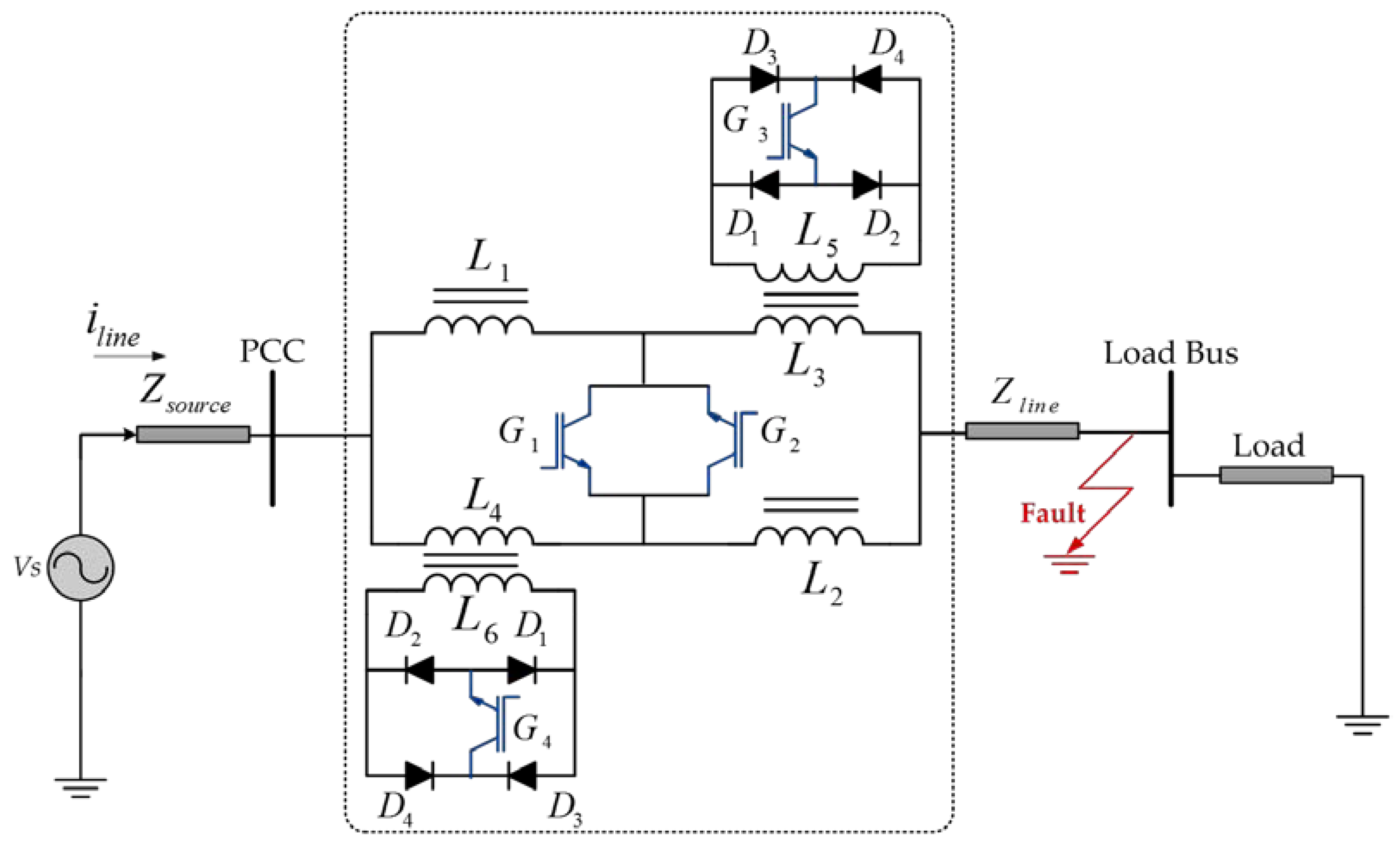

2. Proposed HBFCL Configuration

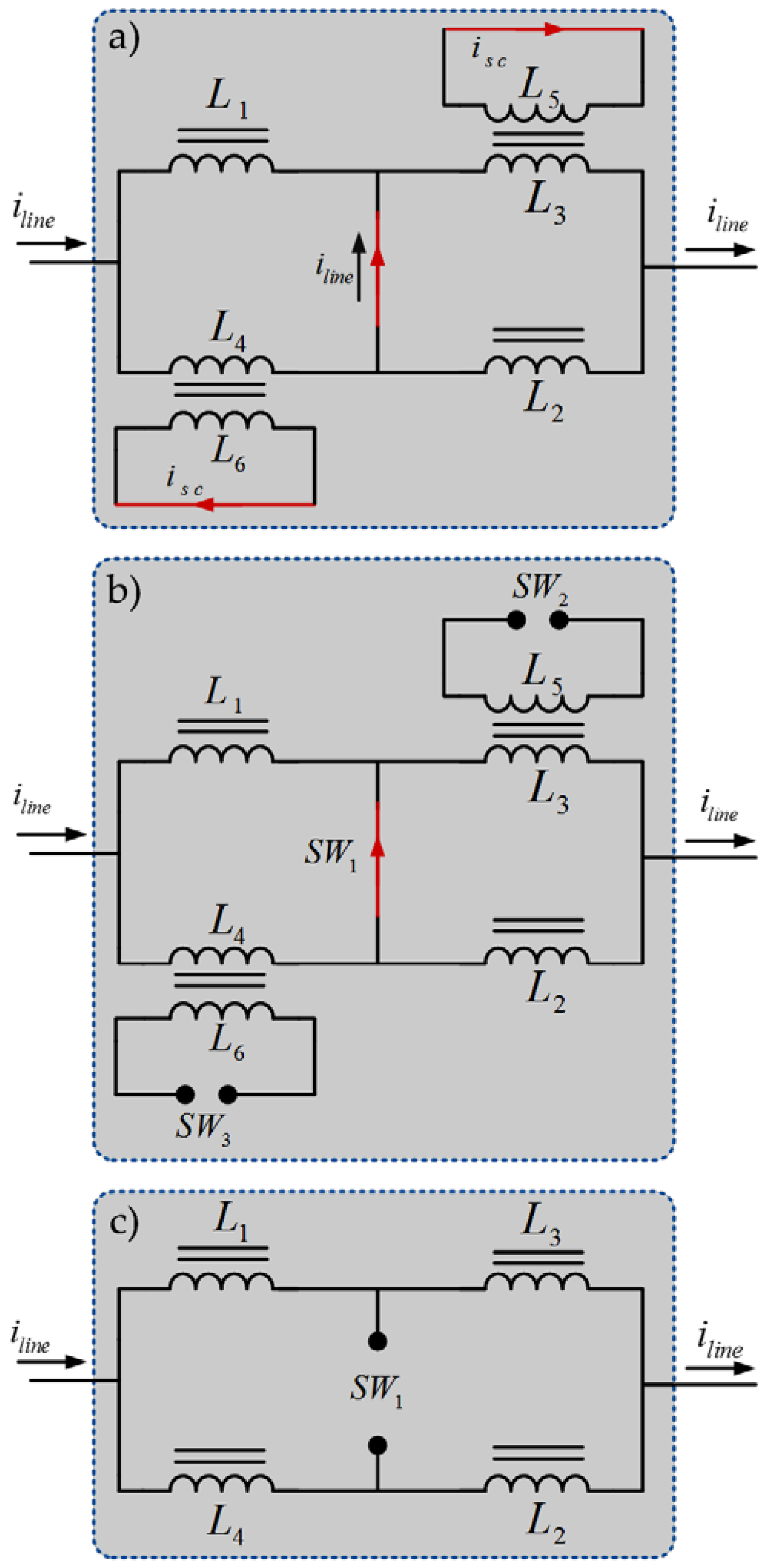

2.1. Normal Operation Mode

2.2. Pre-Limiting Mode

2.3. Fault Current Limiting Mode

3. Analytical Studies

3.1. Steady-State Mode

3.2. Pre-Fault Limiting Mode

3.3. Fault Current Limiting Dynamic Mode

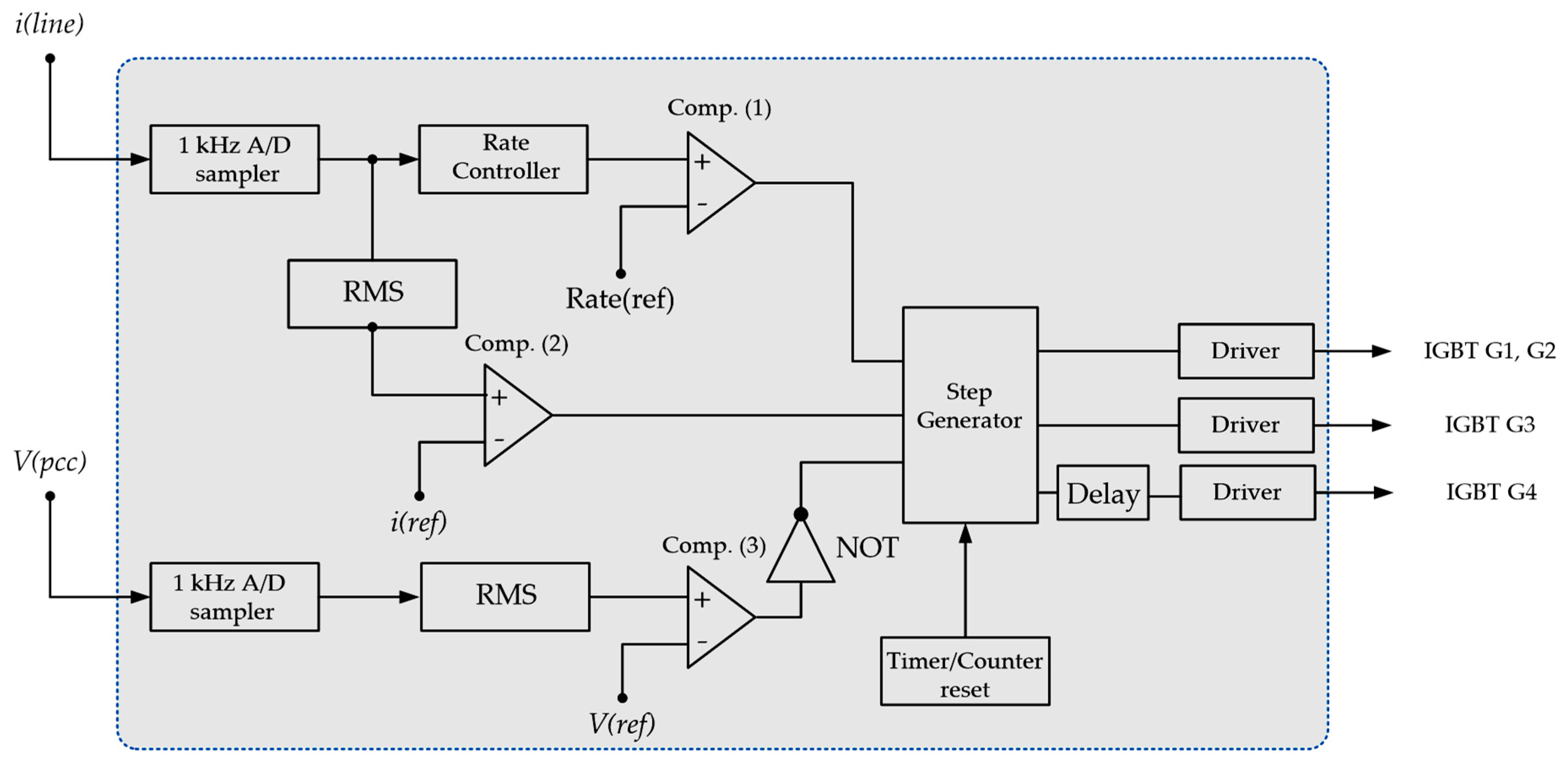

4. Control Strategy

5. Simulation Results

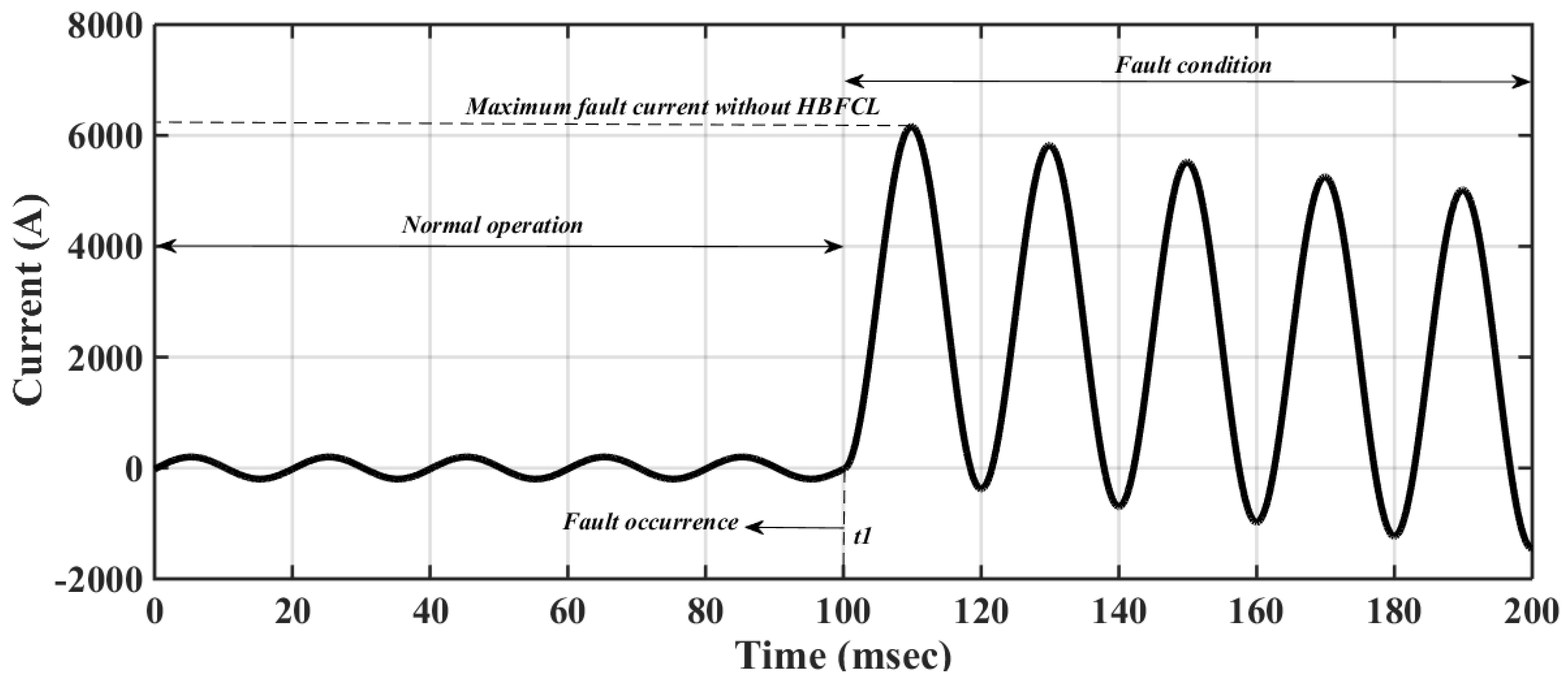

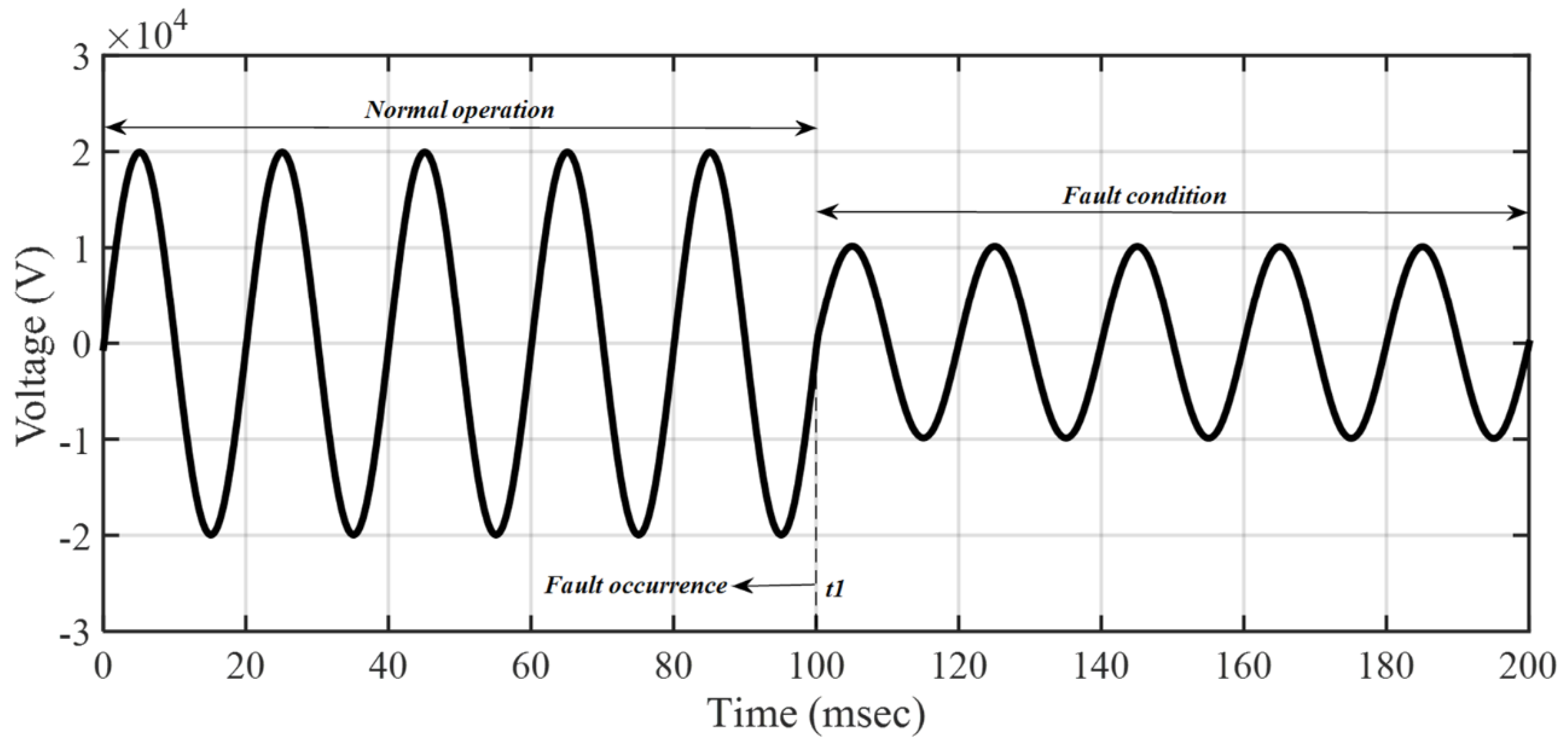

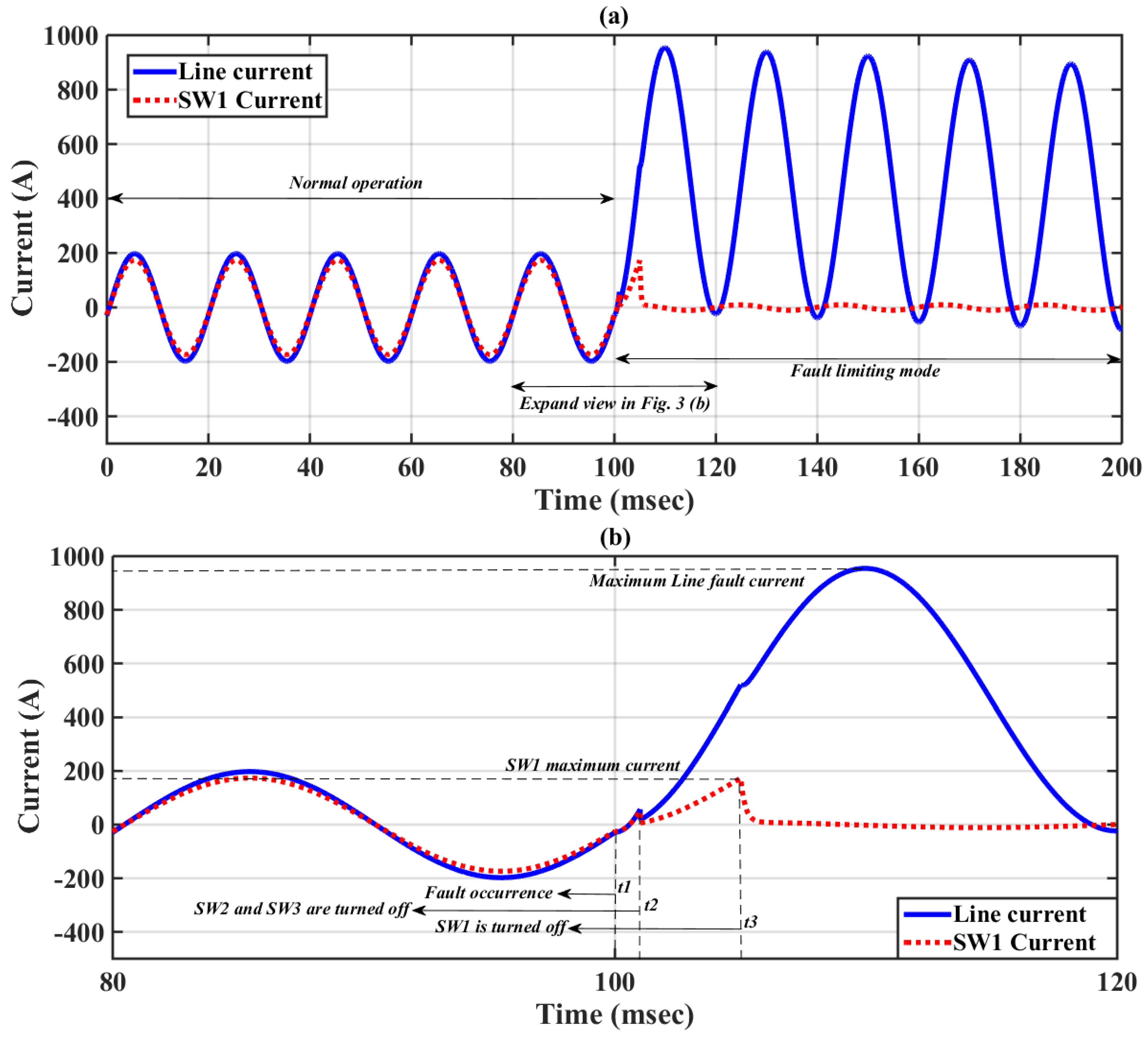

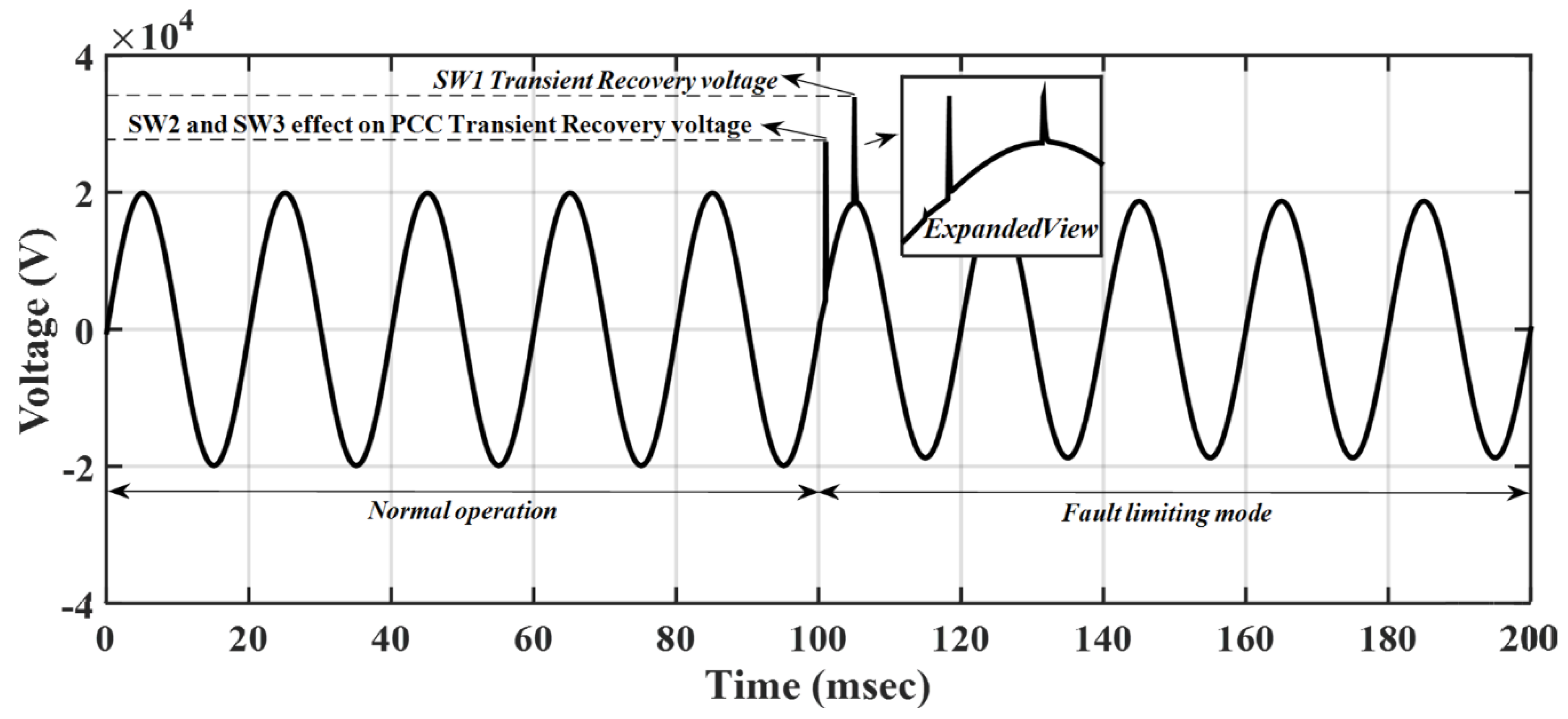

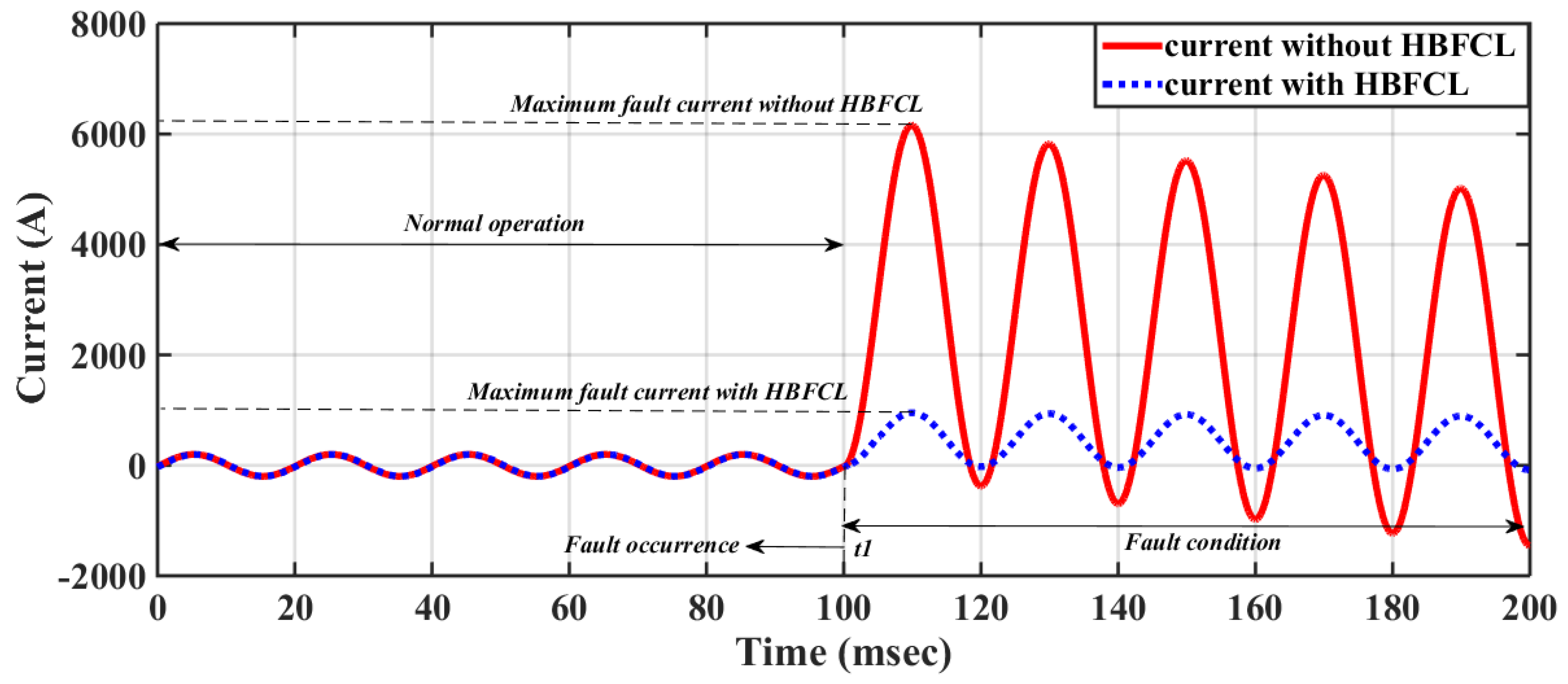

5.1. Fault Condition without HBFCL Effect

5.2. Fault Condition with HBFCL Effect

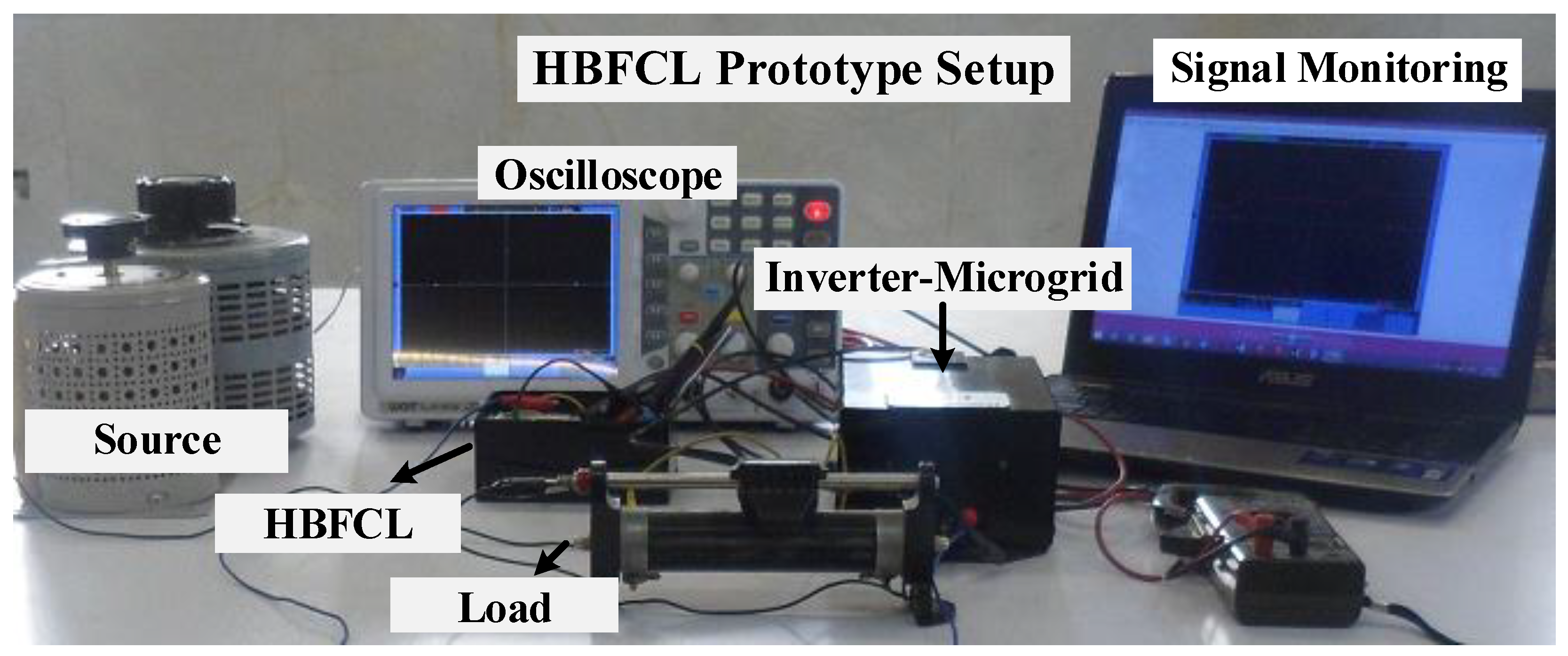

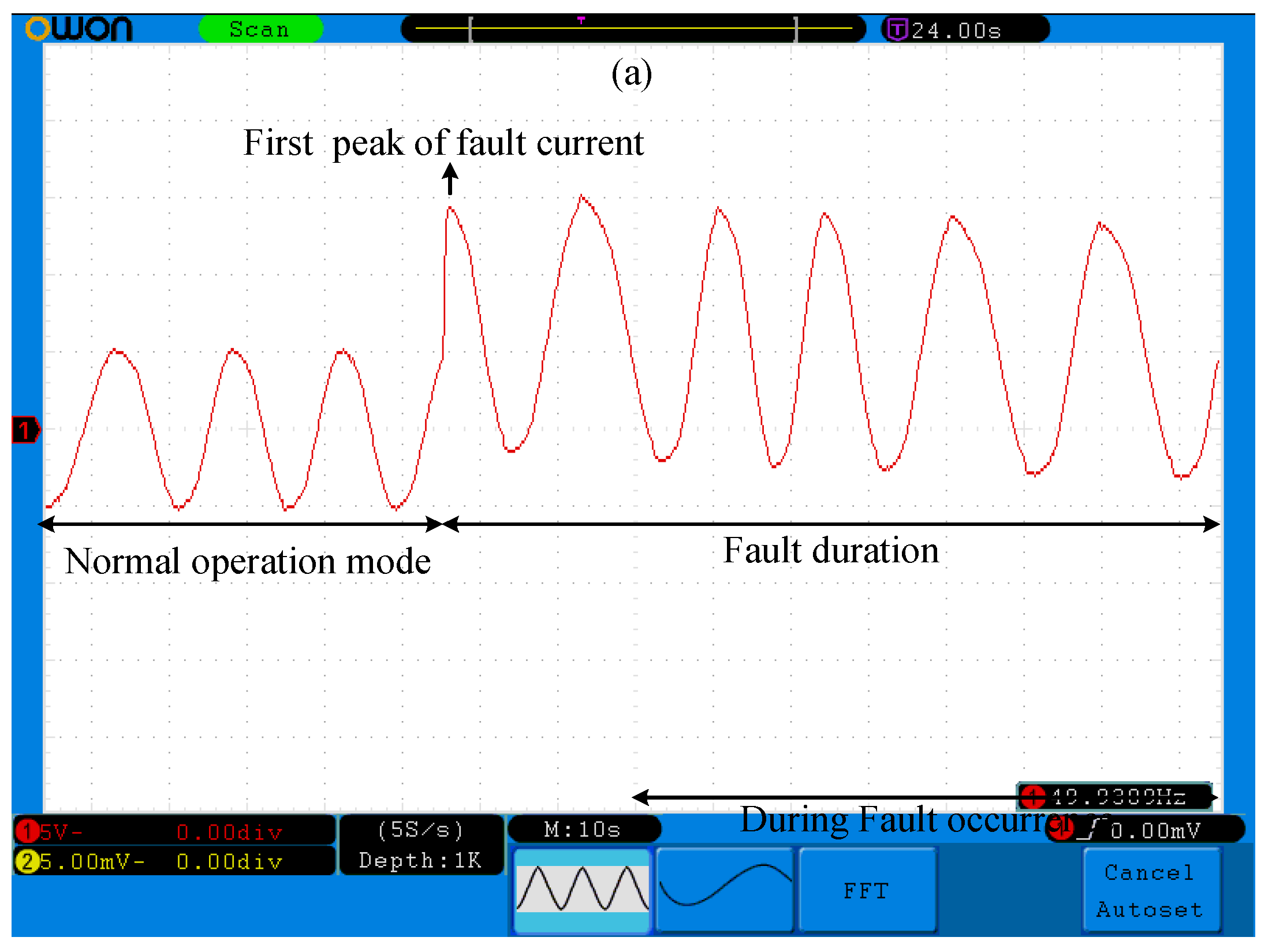

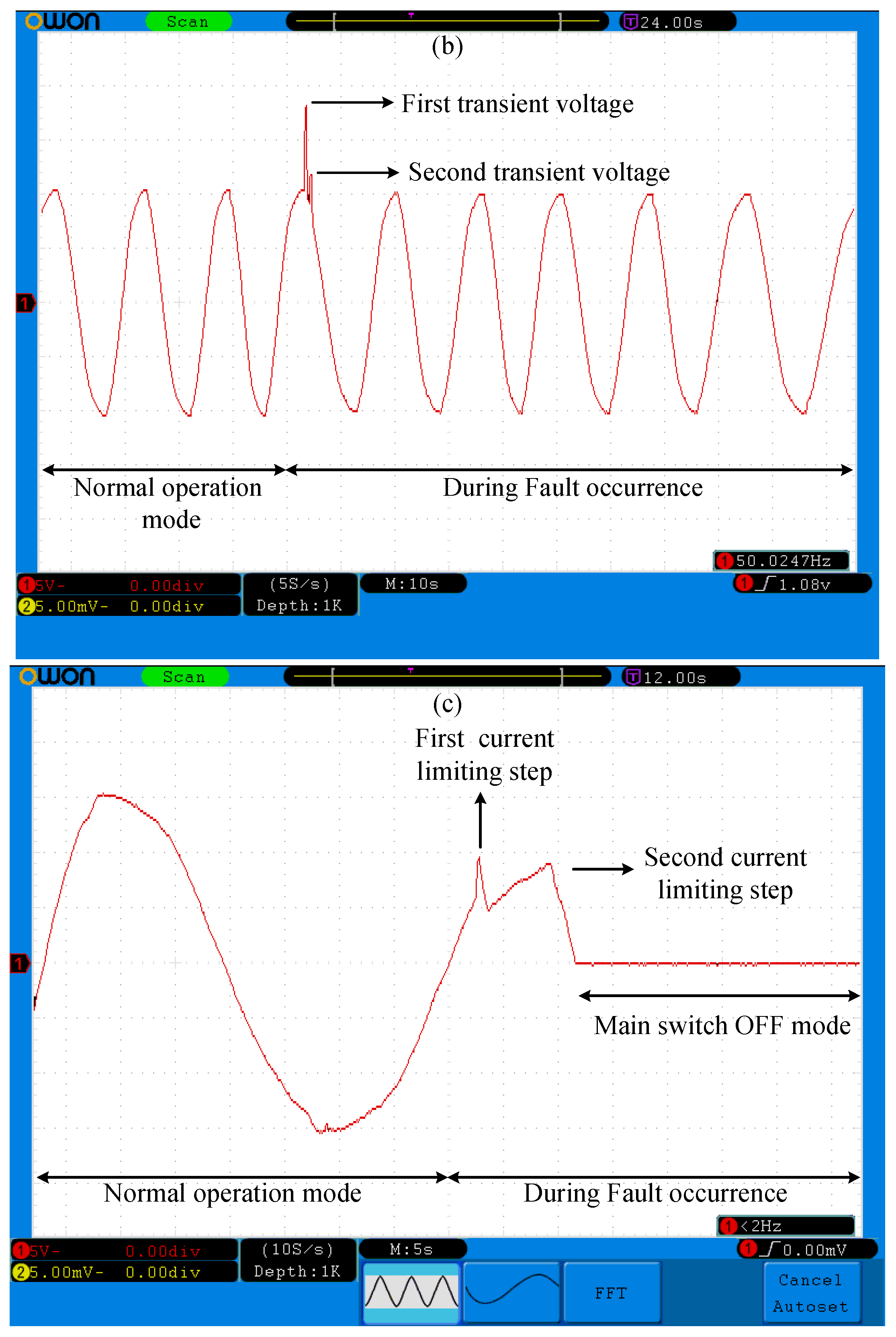

6. Simulation Results

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ueda, T.; Morita, M.; Arita, H.; Kida, Y.; Kurosawa, Y.; Yamagiwa, T. Solid-sate current limiter for power distribution system. IEEE Trans. Power Deliv. 1993, 8, 1796–1801. [Google Scholar] [CrossRef]

- Rouzbehi, K.; Zhu, J.; Zhang, W.; Gharehpetian, G.B.; Luna, A.; Rodriguez, P. Generalized voltage droop control with inertia mimicry capability—Step towards automation of multi-terminal HVDC grids. In Proceedings of the 2015 International Conference on Renewable Energy Research and Applications (ICRERA), Palermo, Italy, 22–25 November 2015; pp. 1556–1561. [Google Scholar]

- Hoshino, T.; Salim, K.M.; Nishikawa, M.; Muta, I.; Nakamura, T. DC reactor effect on bridge type superconducting fault current limiter during load increasing. IEEE Trans. Appl. Supercond. 2001, 11, 1944–1947. [Google Scholar] [CrossRef]

- Salim, K.M.; Hoshino, T.; Nishikawa, M.; Muta, I.; Nakamura, T. Preliminary experiments on saturated DC reactor type fault current limiter. IEEE Trans. Appl. Supercond. 2002, 12, 872–875. [Google Scholar] [CrossRef]

- Rouzbehi, K.; Candela, J.I.; Luna, A.; Gharehpetian, G.B.; Rodriguez, P. Flexible Control of Power Flow in Multiterminal DC Grids Using DC–DC Converter. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 1135–1144. [Google Scholar] [CrossRef]

- Rouzbehi, K.; Miranian, A.; Candela, J.; Luna, A.; Rodriguez, P. Instelligent voltage control in a dc micro-grid containing PV generation and energy storage. In Proceedings of the 2014 IEEE PES T&D Conference and Exposition, Chicago, IL, USA, 14–17 April 2014; pp. 1–5. [Google Scholar]

- Gromoll, B.; Ries, G.; Schmidt, W.; Kraemer, H.-P.; Seebacher, B.; Utz, B.; Nies, R.; Neumueller, H.-W.; Baltzer, E.; Fischer, S.; et al. Resistive fault current limiters with YBCO films 100 kVA functional model. IEEE Trans. Appl. Supercond. 1999, 9, 656–659. [Google Scholar] [CrossRef]

- Ye, L.; Lin, L.; Juengst, K.-P. Application Studies of Superconducting Fault Current Limiters in Electric Power Systems. IEEE Trans. Appl. Supercond. 2002, 12, 900–903. [Google Scholar]

- Hoshino, T.; Salim, K.M.; Nishikawa, M.; Muta, I.; Nakamura, T. Proposal of saturated DC reactor type superconducting fault current limiter (SFCL). Cryogenics 2001, 41, 469–474. [Google Scholar] [CrossRef]

- Shfaghatian, N.; Heidary, A.; Radmanesh, H.; Rouzbehi, K. Microgrids Interconnection to Upstream AC grid Using a Dual-function Fault Current Limiter and Power Flow Controller: principle and test results. IET Energy Syst. Integr. 2019. [Google Scholar] [CrossRef]

- Heidary, A.; Radmanesh, H.; Bakhshi, A.; Rouzbehi, K.; Pouresmaeil, E. A Compound Current Limiter and Circuit Breaker. Electronics 2019, 5, 551. [Google Scholar] [CrossRef]

- Radmanesh, H.; Heidary, A.; Fathi, S.H.; Gharehpetian, G.B. Dual Function Ferroresonance and Fault Current Limiter Based on DC Reactor. IET Gener. Transm. Distrib. 2016, 10, 2058–2065. [Google Scholar] [CrossRef]

- Radmanesh, H.; Fathi, S.H.; Gharehpetian, G.B.; Heidary, A. Bridge-Type Solid-State Fault Current Limiter Based on AC/DC Reactor. IEEE Trans. Power Deliv. 2016, 31, 200–209. [Google Scholar] [CrossRef]

- Heidary, A.; Radmanesh, H.; Fathi, S.H.; Khamse, H.R.R. Improving Transient Recovery voltage of circuit breaker using Fault Current Limiter. Res. J. Appl. Sci. Eng. Technol. 2012, 4, 5123–5128. [Google Scholar]

- Naderi, S.B.; Jafari, M.; Hagh, M.T. Parallel-Resonance-Type Fault Current Limiter. IEEE Trans. Ind. Electron. 2013, 60, 2538–2546. [Google Scholar] [CrossRef]

- Heidary, A.; Radmanesh, H.; Fathi, H.; Gharehpetian, G.B. Series transformer based diode-bridge-type solid state fault current limiter. Front. Inf. Technol. Electron. Eng. 2015, 16, 769–784. [Google Scholar] [CrossRef]

- Yamaguchi, H.; Kataoka, T. An Experimental Investigation of Magnetic Saturation of a Transformer Type Superconducting Fault Current Limiter. IEEE Trans. Appl. Supercond. 2009, 19, 1876–1879. [Google Scholar] [CrossRef]

- Kcilin, V.; Kovalcv, I.; Kmglov, S.; Stepanov, V.; Slmgaev, I.; Shchcrbzkov, V. Model of HTS Three-phase Saturated Core Fault Current Limiter. IEEE Trans. Appl. Supercond. 2000, 10, 836–839. [Google Scholar]

- Moscrop, J.W. Experimental Analysis of the Magnetic Flux Characteristics of Saturated Core Fault Current Limiters. IEEE Trans. Magn. 2013, 49, 874–882. [Google Scholar] [CrossRef]

- Commins, P.A.; Moscrop, J.W. Three Phase Saturated Core Fault Current Limiter Performance with a Floating Neutral. In Proceedings of the IEEE Electrical Power and Energy Conference, London, ON, Canada, 10–12 October 2012; pp. 249–254. [Google Scholar]

- Chen, X.; Chen, B.; Tian, C.; Yuan, J.; Liu, Y. Modeling and Harmonic Optimization of a Two-Stage Saturable Magnetically Controlled Reactor for an Arc Suppression Coil. IEEE Trans. Ind. Electron. 2012, 59, 2824–2831. [Google Scholar] [CrossRef]

- Moriconi, F.; de la Rosa, F.; Darmann, F.; Nelson, A.; Masur, L. Deployment of Saturated-Core Fault Current Limiters in Distribution and Transmission Substations. IEEE Trans. Appl. Supercond. 2011, 21, 1288–1293. [Google Scholar] [CrossRef]

- Xin, Y.; Gong, W.Z.; Niu, X.Y.; Gao, Y.Q.; Guo, Q.Q.; Xiao, L.X.; Cao, Z.J.; Hong, H.; Wu, A.G.; Li, Z.H.; et al. Manufacturing and Test of a 35 kV/90 MVA Saturated Iron-Core Type Superconductive Fault Current Limiter for Live-Grid Operation. IEEE Trans. Appl. Supercond. 2009, 19, 1934–1937. [Google Scholar] [CrossRef]

- Xin, Y.; Hong, H.; Wang, J.Z.; Gong, W.Z.; Zhang, J.Y.; Ren, A.L.; Zi, M.R.; Xiong, Z.Q.; Si, D.J.; Ye, F. Performance of the 35 kV/90 MVA SFCL in Live-Grid Fault Current Limiting Tests. IEEE Trans. Appl. Supercond. 2011, 21, 1294–1297. [Google Scholar] [CrossRef]

- Zheng, F.; Deng, C.; Chen, L.; Li, S.; Liu, Y.; Liao, Y. Transient Performance Improvement of Micro-grid by a Resistive Superconducting Fault Current Limiter. IEEE Trans. Appl. Supercond. 2015, 25. [Google Scholar] [CrossRef]

- Hwang, J.-S.; Khan, U.A.; Shin, W.-J.; Seong, J.-K.; Lee, J.-G.; Kim, Y.; Lee, B.-W. Validity Analysis on the Positioning of Superconducting Fault Current Limiter in Neighboring AC and DC Microgrid. IEEE Trans. Appl. Supercond. 2013, 23. [Google Scholar] [CrossRef]

- Abdolkarimzadeh, M.; Nazari-Heris, M.; Abapour, M.; Sabahi, M. A Bridge Type Fault Current Limiter for Energy Management of AC/DC Microgrids. IEEE Trans. Power Electron. 2017, 32, 9043–9050. [Google Scholar] [CrossRef]

- Heidary, A.; Radmanesh, H.; Rouzbehi, K.; Pou, J. A DC-Reactor Based Solid-State Fault Current Limiter for HVDC Applications. IEEE Trans. Power Deliv. 2019, 34, 720–728. [Google Scholar] [CrossRef]

- Eladawy, M.; Metwally, I.A. A Novel Five-Leg Design for Performance Improvement of Three-Phase Presaturated Core Fault-Current Limiter. IEEE Trans. Magn. 2018, 54. [Google Scholar] [CrossRef]

- Yan, S.; Tang, Y.; Ren, L.; Xu, Y.; Wang, Z.; Liang, S.; Zhang, Z. Design and Verification Test of a Flux-Coupling-Type Superconducting Fault Current Limiter. IEEE Trans. Magn. 2018, 54. [Google Scholar] [CrossRef]

- Tseng, H.-T.; Jiang, We.; Lai, J. A Modified Bridge Switch-Type Flux-Coupling Non-superconducting Fault Current Limiter for Suppression of Fault Transients. IEEE Trans. Power Deliv. 2018, 33, 2624–2633. [Google Scholar] [CrossRef]

| Symbol | Description | Value |

|---|---|---|

| VS | Source voltage | 20 kV |

| rs | Source resistance | 0.1 Ω |

| rline | Line resistance | 0.1 Ω |

| rf | Fault resistance | 0.01 Ω |

| LS | Source inductance | 10 mH |

| Lline | Line inductance | 10 mH |

| L1 | HBFCL first inductance | 0.1 H |

| L2 | HBFCL second inductance | 0.2 H |

| L3 | HBFCL third inductance | 0.2 H |

| L4 | HBFCL fourth inductance | 0.1 H |

| Symbol | Description | Value |

|---|---|---|

| VS | Source voltage | 20 kV |

| rs | Source resistance | 0.1 Ω |

| rline | Resistance | 0.1 Ω |

| rf | Resistance | 0.01 Ω |

| LS | Source inductance | 10 mH |

| Lline | Open core 30 turns inductor | 10 mH |

| L1 | E-I core inductor | 0.1 H |

| L2 | E-I core inductor | 50 mH |

| L3 | E-I core inductor | 0.1 H |

| L4 | E-I core inductor | 0.2 H |

| Rload | Variable 100 W resistor | 0–100 Ω |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Heidary, A.; Radmanesh, H.; Moghim, A.; Ghorbanyan, K.; Rouzbehi, K.; M. G. Rodrigues, E.; Pouresmaeil, E. A Multi-Inductor H Bridge Fault Current Limiter. Electronics 2019, 8, 795. https://doi.org/10.3390/electronics8070795

Heidary A, Radmanesh H, Moghim A, Ghorbanyan K, Rouzbehi K, M. G. Rodrigues E, Pouresmaeil E. A Multi-Inductor H Bridge Fault Current Limiter. Electronics. 2019; 8(7):795. https://doi.org/10.3390/electronics8070795

Chicago/Turabian StyleHeidary, Amir, Hamid Radmanesh, Ali Moghim, Kamran Ghorbanyan, Kumars Rouzbehi, Eduardo M. G. Rodrigues, and Edris Pouresmaeil. 2019. "A Multi-Inductor H Bridge Fault Current Limiter" Electronics 8, no. 7: 795. https://doi.org/10.3390/electronics8070795

APA StyleHeidary, A., Radmanesh, H., Moghim, A., Ghorbanyan, K., Rouzbehi, K., M. G. Rodrigues, E., & Pouresmaeil, E. (2019). A Multi-Inductor H Bridge Fault Current Limiter. Electronics, 8(7), 795. https://doi.org/10.3390/electronics8070795